# Vérification de descriptions VHDL par interprétation abstraite.

Charles Hymans

#### ▶ To cite this version:

Charles Hymans. Vérification de descriptions VHDL par interprétation abstraite. Analyse classique [math.CA]. Ecole Polytechnique X, 2004. Français. NNT: pastel-00000875

# HAL Id: pastel-00000875 https://pastel.hal.science/pastel-00000875

Submitted on 23 Jul 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

présentée à

# L'ÉCOLE POLYTECHNIQUE

Pour l'obtention du titre de DOCTEUR EN SCIENCES DE L'ÉCOLE POLYTECHNIQUE

Discipline Mathématiques et Informatique

par

#### CHARLES HYMANS

le 9 septembre 2004

# Vérification de composants VHDL par interprétation abstraite

Verification of VHDL descriptions by abstract interpretation

Président REINHARD WILHELM

Professeur, Universität des Saarlandes, Allemagne

Rapporteurs Kenneth L. McMillan

Senior Research Scientist, Cadence Berkeley Labs, États Unis

KWANGKEUN YI

Professeur, Seoul National University, Corée du Sud

Examinateurs Gilles Dowek

Professeur, École Polytechnique Manuel Hermenegildo

Professeur, Technical University of Madrid, Espagne,

& University of New Mexico, États Unis

Directeur de thèse RADHIA COUSOT

Directeur de recherche, CNRS

Hâtez-vous lentement; et, sans perdre courage, Vingt fois sur le métier remettez votre ouvrage : Polissez-le sans cesse et le repolissez; Ajoutez quelquefois, et souvent effacez.

Boileau, L'Art poétique

#### Remerciements

Je suis profondément reconnaissant à Kwangkeun Yi et Kenneth L. McMillan d'avoir accepté d'être rapporteurs de ma thèse. Je remercie Reinhard Wilhelm, Gilles Dowek et Manuel Hermenegildo de m'avoir fait l'honneur de participer à mon jury de thèse.

J'exprime ma sincère gratitude envers Radhia Cousot pour son patient encadrement depuis les premiers stages puis tout au long de cette thèse. Elle m'a donné la chance de travailler dans les meilleures conditions possibles. Je la remercie particulièrement pour son exigence de qualité scientifique, son ouverture sur le monde et sa compréhension.

Arnaud Venet a guidé mes premiers pas dans le monde de la recherche. Il m'a aidé dans mes choix les plus cruciaux. Je lui suis éternellement reconnaissant. Je remercie Patrick Cousot de m'avoir initié à la théorie de l'interprétation abstraite. Je remercie Christophe Blandin et Renaud Pacalet de m'avoir dévoilé les enjeux de la vérification de matériel et fourni des exemples à étudier.

Merci à mes formidables collègues de bureau Francesco Logozzo, Damien Massé et Élodie-Jane Sims. J'ai apprécié les moments d'intense réflexion que nous avons passés ensembles. Thank you to David Schmidt, Axel Simon and Eben Upton for brightening up the office we shared. Je remercie aussi les membres de la magic team à l'École Normale Supérieure et de l'équipe de ROPAS à la Seoul National University.

Merci à tous mes amis, en particulier à Denis Conduché et Xavier Rival pour leur amitié revigorante. Enfin, merci à ma famille et à Shinsuk pour leur soutien constant sans lequel cette thèse ne serait probablement pas.

# Contents

| 1        | Rés             | umé de la thèse                          | 9  |

|----------|-----------------|------------------------------------------|----|

|          | 1.1             | La vérification de matériel              | 9  |

|          | 1.2             | Objectif                                 | 9  |

|          | 1.3             | Résultats                                | 10 |

| <b>2</b> | $\mathbf{Intr}$ | oduction                                 | 13 |

|          | 2.1             | Semiconductors                           | 13 |

|          | 2.2             | Verification crisis                      | 15 |

|          | 2.3             | Motivation                               | 15 |

|          | 2.4             | Results                                  | 18 |

| 3        | Sem             | aantics                                  | 21 |

|          | 3.1             | Introduction                             | 21 |

|          | 3.2             | Related work                             | 22 |

|          | 3.3             | Syntax                                   | 23 |

|          | 3.4             | Intuition for the semantic model         | 25 |

|          | 3.5             | The kernel                               | 25 |

|          | 3.6             | More data types: integers and aggregates | 31 |

|          | 3.7             | Local variables, conversion functions    | 33 |

|          | 3.8             | Rising edges and clocks                  | 34 |

|          | 3.9             | Remaining statements                     | 35 |

|          |                 | 3.9.1 Suspension                         | 35 |

|          |                 | 3.9.2 Alternative                        | 35 |

|          |                 | 3.9.3 Display                            | 36 |

|          | 3.10            | A benign parallelism                     | 36 |

|          | 3.11            | Discussion                               | 39 |

| 4        | Abs             | tract Interpretation                     | 47 |

|          | 4.1             | Collecting semantics                     | 47 |

8 CONTENTS

|   | 4.2 | Abstract Interpretation                   |

|---|-----|-------------------------------------------|

|   | 4.3 | Abstract domain                           |

|   | 4.4 | Abstract semantics transformer            |

|   |     | 4.4.1 Expressions                         |

|   |     | 4.4.2 Sequential statements               |

|   |     | 4.4.3 Abstract simulation algorithm       |

|   |     | 4.4.4 Semantics transformer               |

|   | 4.5 | Example                                   |

|   | 4.6 | Loop unfolding                            |

|   | 4.7 | Recapitulation                            |

| 5 | Imr | plementation 73                           |

|   | 5.1 | Preprocessor                              |

|   | 5.2 | Abstract simulator                        |

|   | 5.3 | The back-end: a numerical domain          |

|   |     | 5.3.1 Boolean affine relationships        |

|   |     | 5.3.2 Constants                           |

|   |     | 5.3.3 Arrays                              |

|   | 5.4 | A trial run                               |

| 6 | Ree | d Solomon error correcting code 87        |

|   | 6.1 | Motivation                                |

|   | 6.2 | Reed Solomon                              |

|   | 6.3 | Encoder                                   |

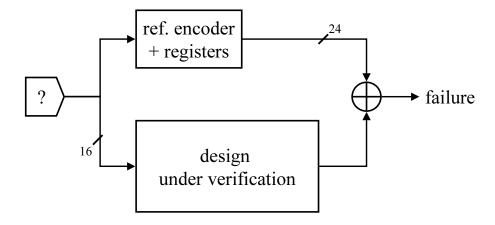

|   | 0.0 | 6.3.1 Verification harness                |

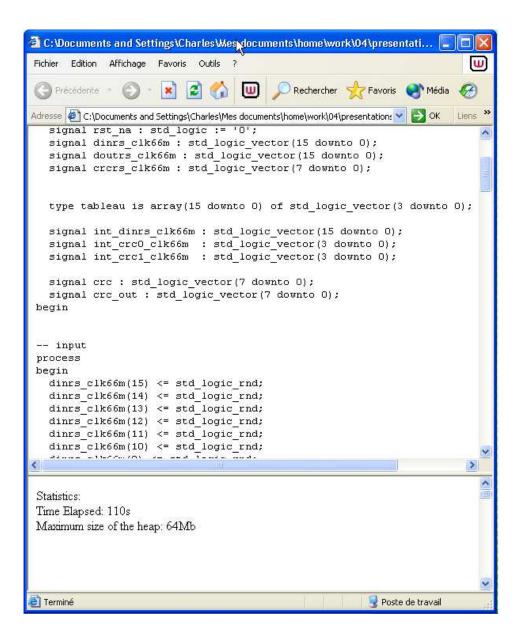

|   |     | 6.3.2 Results                             |

|   |     | 6.3.3 Coding style                        |

|   |     | 6.3.4 Combinational processes             |

|   | 6.4 | Decoder                                   |

|   |     | 6.4.1 Specification                       |

|   |     | 6.4.2 Inlining combinational processes 98 |

|   |     | 6.4.3 Debugging                           |

|   |     | 6.4.4 Statistics                          |

|   | 6.5 | Related work                              |

| 7 | Cor | iclusion 105                              |

# Chapitre 1

# Résumé de la thèse

#### 1.1 La vérification de matériel

Chaque année, les progrès réalisés dans la fabrication de semi-conducteurs permettent l'intégration d'un nombre sans cesse croissant de transistors sur une puce. Cette évolution est malheureusement concomitante d'une augmentation dramatique des coûts non-récurrents de fabrication : un jeu de masques atteint 2 millions de dollars en technologie 65nm. Ainsi, les concepteurs doivent impérativement assurer la correction de systèmes aux complexités sans cesse accrus. À cette fin, de 60% à 70% du temps de développement est dédié à la simulation. Cette tendance ne peut que s'accentuer d'où la nécessité de développer des outils automatiques d'aide à la validation.

À la différence de la simulation, les méthodes formelles de vérification peuvent être exhaustives. Elles permettent de montrer la conformité d'une description de circuit à sa spécification. Cependant, les méthodes formelles doivent, elles aussi, affronter l'effroyable complexité des descriptions. Ainsi, elles souffrent souvent du problème d'explosion des états.

### 1.2 Objectif

Nous étudions la faisabilité d'un outil de vérification automatique qui réunit trois caractéristiques : assurance de couverture, efficacité de calcul, et intégration dans le flot de conception. Afin d'établir des propriétés de la description, et non pas seulement de trouver des erreurs, l'outil doit être exhaustif. Il doit couvrir l'ensemble des exécutions possibles. L'efficacité est un point crucial. C'est cela qui, véritablement, déterminera l'acceptation

de la méthode par les ingénieurs de conception. Nous nous fixons l'objectif d'être au moins compétitif avec la simulation traditionnelle. Enfin, l'outil doit travailler à partir de la même description que celle qui est déjà utilisée pour la simulation et la synthèse. De cette manière, l'intégration dans le flot de conception classique est assurée.

La théorie de l'interprétation abstraite permet de concilier ces objectifs apparemment contradictoires. L'interprétation abstraite formalise la notion d'abstraction entre sémantiques de programme. Son application originelle est la conception d'analyses statiques. L'idée consiste à calculer une version approchée de la sémantique. La régularité de la sémantique approchée est exploitée en utilisant des représentations en machine concises et des algorithmes puissants. Il est ainsi possible d'obtenir efficacité de calcul sans pour autant sacrifier l'exhaustivité. Cependant, abstraire a un coût : une abstraction trop rude ne sera pas en mesure de démontrer la correction du programme. Tout l'art de l'interprétation abstraite consiste donc à trouver le compromis idéal entre efficacité et précision pour un domaine d'application donné.

#### 1.3 Résultats

Notre étude a pour objet le très répandu langage de description de matériel VHDL. Nous formalisons l'algorithme de simulation défini par le standard IEEE pour un noyau réaliste du langage. Chaque étape de calcul d'un simulateur événementiel est définie par une sémantique opérationnelle à la Plotkin. Essentiellement, une description VHDL se composée d'un nombre fini de processus exécutés en parallèle. La communication entre les processus s'effectue à travers une mémoire partagée, des signaux, et uniquement aux points de synchronisation. La synchronisation a lieu dès lors que tous les processus sont suspendus. À ce moment, la mémoire partagée est mise à jour, et certains processus sont réveillés par des événements de natures diverses: modification de la valeur d'un signal ou bien avancement du temps. Nous montrons que le parallélisme à la VHDL est bénin. Il est donc inutile d'explorer l'ensemble des entrelacements d'exécution de processus. On peut simplement se contenter de fixer leur ordre une fois pour toutes. Le sous-ensemble de VHDL traité manipule des entiers, de la logique standard (valeurs 0, 1 et U) et des tableaux statiquement alloués. Il contient du non-déterminisme par l'ajout de générateurs aléatoires et des fonctions de conversion d'un type de donnée à l'autre.

À partir de ce modèle mathématique, nous avons dérivé, systématiquement

par abstraction, une analyse statique pour VHDL. Cette analyse calcule une approximation supérieure de l'ensemble des états accessibles. Elle est paramétrée par le choix de l'abstraction de la mémoire. Ainsi, n'importe quel domaine numérique peut-être adopté et donnera lieu à un compromis original entre la précision des résultats et le coût du calcul. Nous avons évidemment réalisé la preuve de correction de l'analyse.

Enfin, nous présentons une instance possible de notre analyse statique. Elle est développée dans l'intention de valider des codes correcteurs d'erreurs linéaires. Le domaine numérique choisi est celui des égalités linéaires entre variables booléennes, doublé du domaine des constantes. Nous avons réalisé l'implémentation de l'analyse en OCaml. Il a aussi fallu écrire un préprocesseur qui traduit les descriptions VHDL dans le noyau. Ces prototypes nous ont donné l'occasion d'évaluer l'approche sur un cas concret. Nous avons appliqué l'analyse sur une description matérielle de code correcteur d'erreur de type Reed Solomon qui nous a été fourni par des partenaires industriels. Pour établir la correction du composant, il faut montrer que la composition encodage/corruption/décodage résulte bien en l'identité. Pour cela, nous comparons, automatiquement à l'aide de notre prototype, chaque composant avec une spécification de haut-niveau. Nous expliquons comment structurer cette spécification afin d'éviter l'explosion du nombre d'états générés par la présence de pipeline dans les composants. Les résultats sont remarquables: non seulement la vérification est un succès, mais de plus elle s'avère efficace. Ainsi, les performances de l'outil sont bien meilleures que le model checker VIS qui échoue par manque de mémoire. Notre prototype est aussi compétitif en terme de temps de calcul avec la simulation, tout en apportant évidemment une assurance beaucoup plus forte de correction.

Nous avons conçu et réalisé un outil de vérification automatique efficace, exhaustif et paramété. De plus, l'effort à consentir pour adjoindre à l'outil une abstraction différente est relativement réduit. Il suffit de modifier uniquement le domaine numérique en paramètre et il est inutile de se soucier de la sémantique de VHDL. Ce travail constitue une étape dans l'intégration d'outils formels aux flots de conception existants.

# Chapter 2

# Introduction

#### 2.1 Semiconductors

Digital cameras, voice over IP phones, harvester guidance systems, factory monitors, smart rifles, brake controllers and pacemakers, all these devices incorporate integrated circuits. According to [MED04], the market of the semiconductor industry totaled \$141 billion in 2003, while the electronic industry addressed a \$800 billion market. Are there more tangible proofs of the pervasive influence of semiconductors on our society? Innovation in semiconductors contributes to the evolution of many industrial sectors. For instance electronics equipment amounts for as much as 20% of the production cost of a car.

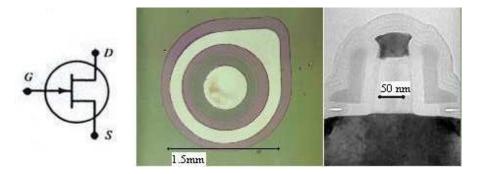

The formidable proliferation of hardware in the world began not even a century ago. Bell Labs researchers William Shockley, John Bardeen and Walter Brattain created the first transistor in 1947. Schematically, see Fig. 2.1, a transistor operates like a switch: when voltage is applied to the gate (G) then the current between the source (S) and the drain (D) flows, otherwise source and drain are disconnected. Transistors constitute the basic blocks of electronic circuits. The ability to integrate a whole circuit on a single silicon wafer was invented a decade later. In 1958, Jack Kilby, while working at Texas Instrument, built the first integrated circuit. In 1959, Jean Hoerni and Robert Noyce at Fairchild developed the fabrication process still in use today: planar technology, see Fig. 2.1. A set of masks, which can be thought of the negatives for the various layers of the circuit, is manufactured. Then, in a way similar to photography, light is used to transfer the shape of the masks onto the silicon substrate, see Fig. 2.2.

Since then, the semiconductor industry has been driven by an exponen-

Figure 2.1: Transistor schematics, first planar transistor (source: smithsonianchips.si.edu) and 90nm transistor (source: intel)

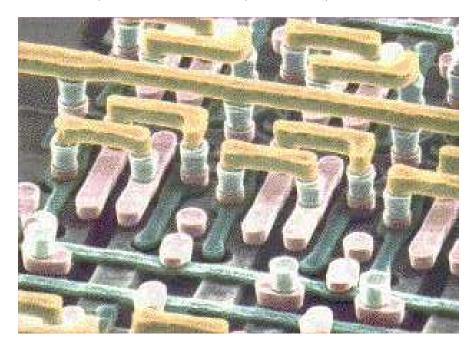

Figure 2.2: Interconnection structure of an SRAM (source: IBM Journal of R&D, Vol. 39, No. 4)

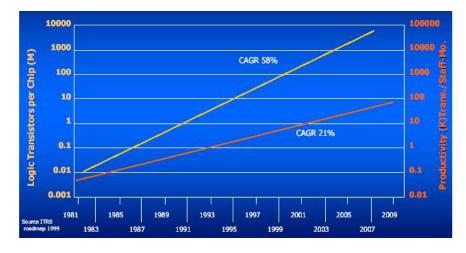

tial trend commonly known as Moore's law: the number of transistors per integrated circuits doubles every 18 months. In parallel to this evolution, the size and price of transistors have also decreased exponentially. Today, processors manufactured with the 90nm process, see Fig. 2.1, contain a few hundred million transistors. Over the years, integrated circuits with ever increasing functionality have created new applications and conquered new markets. These trends have allowed the semiconductor industry revenue to grow at an average of 14% per year [Jon03].

#### 2.2 Verification crisis

Unfortunately the integration of numerous transistors on a chip has a high cost. The investment necessary to build a semiconductor manufacturing plant is evaluated in billion dollars. More importantly, the cost of mask sets have reached prohibitive amounts: it exceeds the million dollars for the 90nm technology and almost tops 2 million dollars in 65nm. To offset such high initial investments chips manufactured with the latest technology must be sold in very high volumes [MP03].

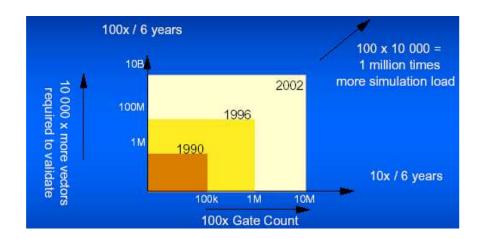

Even worse, designs should be error free before they are sent to fabrication: few companies can afford a million dollar re-spin. To ensure the correctness of their designs, engineers use simulation. Simulation accounts for 60% to 70% of the whole development time [MED02]. The number of engineers allocated to simulation outstrips the number of designers. Apparently, this proves not enough since almost as much as 50% of all designs go through more than one spin. The situation is bound to deteriorate as designs grow in size and complexity. Not only must the simulator handle bigger designs, it has to run more test-vectors so as to exercise a substantial fragment of all the behaviors, see Fig. 2.3. Largely because of the limitations of verification, the gap between what can be manufactured and what can be correctly designed quickly expands, see Fig. 2.4. According to the International Roadmap for Semiconductors [Int03], the cost of design is the greatest threat to continuation of the semiconductor roadmap. The situation is quickly becoming a crisis. There is a desperate need for new automatic tools that alleviate the task of verification.

#### 2.3 Motivation

In contrast to simulation, formal verification methods can be exhaustive. They provide the unique capability of proving the correctness of a design

Figure 2.3: Increasing load on simulation (source: ST)

Figure 2.4: Design productivity gap (source: [Int03])

with respect to its specifications. However, formal methods too must cope with the sheer complexity of designs and often suffer the well-known state-explosion problem.

We study the feasibility of a formal verification tool that displays three apparently irreconcilable characteristics:

- full coverage,

- efficiency,

- seamless integration.

The tool should be exhaustive. It must cover all possible executions so that it is possible to prove properties of a design. Obviously, it must be sound so as to never report incoherent results. Efficiency is crucial as it mostly determines the acceptance of alternative methods to simulation. At least, the tool should compete advantageously with simulation. In particular, this means we are striving for automation. Tools that require too much manual intervention tend to be difficult to manage but by experts. On top of that, we don't want to impose a modification of existing design flows. Hence, the tool must input the same hardware description that is already used for simulation and synthesis. As an additional benefit, this avoids semantics mismatches that occur when distinct descriptions are used for verification and synthesis.

The framework of abstract interpretation [Cou78, CC77] provides the means to achieve all these goals. Abstract interpretation formalizes the notion of abstraction between program semantics. One of its primary application lies in the design of static analyses that compute approximate but sound information about all behaviors of programs. Such analyses need not retain all the details of the exact semantics. Instead, they can use concise representations and powerful algorithms that take advantage of the regularity enjoyed by the approximate semantics. Abstraction is the key concept to obtain efficiency. Soundness ensures that the results of the analysis are trustworthy and that erroneous conclusions about the design can not be drawn.

Naturally, abstraction has a cost. Sometimes, the results are too unprecise to attest the absence of errors in the design. Hence, the craft of abstract interpretation is to attain the optimal tradeoff between efficiency and precision.

#### 2.4 Results

We design a static analysis for the popular hardware description language VHDL. It computes an approximation of the reachable states. We follow the methodology of abstraction interpretation.

First, we formalize the simulation algorithm for a realistic kernel of VHDL. We use the formalism of structural operational semantics. Very roughly, the semantics of an event-based simulator for VHDL works as follows. A VHDL description consists of a finite number of processes that are run concurrently. Communication between processes takes place through a shared memory, the signals, and at synchronization points only. Synchronization occurs after wait statements have suspended all processes. At this point, the simulator updates the shared memory and resumes the activity of some processes according to the events that just happened: a process was sensitive on a signal that was modified or time was advanced. We proved that the parallelism in VHDL is very weak. Indeed, it is useless to explore all possible interleaving of processes. It is sufficient to fix the order of execution of processes once and for all. The subset of VHDL that is considered manipulates standard multi-valued logic, integers and statically allocated arrays. Among others, it contains non-determinism thanks to random generators and functions that convert from one datatype to another.

The static analysis is systematically derived by abstraction from this mathematical model of the VHDL semantics. The abstract representation of sets of memories is left as a parameter of the analysis. Hence, any abstract numerical domain can be chosen and will lead to a distinct trade-off between the precision of the results and the cost of the analysis. We prove the soundness of the static analysis with respect to VHDL simulation semantics.

Then, we describe a possible instantiation of the analysis, which is tailored at the verification of linear error correcting codes. To represent sets of memories, we choose to combine the numerical domain of linear equalities with the domain of constants. We implemented a prototype of the resulting analysis in OCaml. We successfully applied the prototype to the verification of a Reed-Solomon error correcting code. The VHDL components were provided by industrial partners and were not originally written for the purpose of formal verification. The tool allows to automatically compare the description with high-level specifications. Because of the presence of a pipeline in the component, the tool could incur a state explosion problem. However, we explain how to structure the specifications so as to avoid this pitfall. The results of the experimentation are excellent: verification is a success and the tool proves to be efficient. It outperforms the BDD model checker VIS. It

2.4. RESULTS 19

is also competitive with industrial verification techniques since it completes in less time than what was allocated by the engineers for simulation.

This thesis is not specifically about a new semantics for VHDL; a new general framework for static analysis or new algorithms for manipulating linear constraints. It is rather about the holistic integration of these disparate techniques. The work presented in this thesis appeared as [Hym02a, Hym03, Hym04].

#### Organization of the thesis

Chapter 3 defines the simulation semantics of VHDL. Chapter 4 describes the design by abstract interpretation of a generic static analysis for VHDL. We show a possible instantiation of the analysis and explain the implementation choices of the tool in chapter 5. Eventually, chapter 6 presents the verification of a Reed Solomon encoder and decoder with our prototype.

# Chapter 3

# **Semantics**

#### 3.1 Introduction

Very High Scale/Speed Integrated Circuits Hardware Description Language, aka VHDL, is one of the most widely used hardware description languages. In the early 1980s, the US Department of Defense was facing a crisis: its suppliers all had different ways of documenting hardware. Since the documentations were bound to specific manufacturing technology, they were reaching obsolescence very quickly. Needless to say that interoperability was an inextricable nightmare. Hence, VHDL was initially created as a language to describe the behavior of hardware. The ability to simulate descriptions soon became apparent. Finally, logic synthesis tools made the language even more attractive and gave rise to the modern hardware design methodology. In 1987, VHDL was standardized as IEEE Std 1076 [IEE87]. The up-to-date revision is [IEE02]. IEEE standard 1164 [IEE93] adds an important complement to the language: it defines a data-type to allow the manipulation of multi-valued logic signals.

We favored VHDL for its wide acceptance in the industry. We could have equally opted for Verilog [IEE01]. We strongly believe that a similar methodology can be adopted to develop equally efficient verification tools for Verilog. However, the case study, that professional hardware engineers made available to us, was written in VHDL.

Today, engineers spend most of their time working with VHDL (or Verilog). Lower level descriptions, i.e. netlists in edif [EIA93] or blif [Uni92] formats, are manipulated mostly by automatic tools. Higher level descriptions are used to evaluate the impact of hardware (and software) architectural decision early in the design cycle [DBB<sup>+</sup>02]. Performance/cost estimation

[CMP<sup>+</sup>01], early power analysis [BJ03] and sometimes high-level synthesis [SM01] can all be performed at this level. System level languages and tools have not reached maturity yet and still constitute an active field of research. Among others, system level design languages include SystemC used as in the Metropolis framework [BWH<sup>+</sup>03], Esterel and Time Modeling Language with the Archan approach [MC03], and Kahn Process Networks and C for the SPADE methodology [vdWLGH99].

In order to reason about VHDL descriptions, their semantics must be properly defined. This is the goal of the chapter.

#### 3.2 Related work

Definitions of semantics for VHDL abound. This emphasizes the complexity of the IEEE standard [IEE02] which is subject to multiple interpretations. Semantics tend to vary according to their purpose, their presentation and the aspect of the language they concentrate on.

Goossens defines an operational semantics for a realistic yet manageable subset of VHDL in [Goo95]. The semantics is a formalization of the simulation algorithm as described in informal prose by the 1987 version of the VHDL IEEE standard. [TE01] provides an extension of this work to VHDL'93.

An interpreter for synchronous VHDL written in the pure functional language GOFER is presented in [BFK94]. A more complete but fairly complex implementation using evolving algebra pseudocode is given in [MBG94, BGM95]. The main purpose of interpreters is to palliate the imprecision of the IEEE standard by providing a reference implementation for simulators.

Van Tassel [Tas93] embeds an operational semantics of VHDL in HOL. Russinoff [Rus95a, Rus95b] presents the semantics of a relatively simple hardware description language close to VHDL and encodes it in the Boyer More logic. Formalization in the ACL2 logic of the simulation algorithm for a large and realistic subset of VHDL is described in [BG00, GB002, DB97]. These embeddings in proof assistants allow the further undertaking of formal proofs of correctness of VHDL descriptions. Furthermore, the formalization in ACL2 [GB002] immediately provides a symbolic simulator.

The compilation of VHDL descriptions into finite state machines for the purpose of symbolic model checking has been explored. Such compilation process is described in [LBPV94]. In [DB93, DB95, DSC98], designs are translated into finite state machines where one transition of the machine emulates one delta cycle. Encrenaz [Enc95] adopts a similar approach but

3.3. SYNTAX 23

```

process { | process }

(Parallel composition)

descr

ightarrow

process

command; { command; }

(Sequence)

command

lval := exp

(Variable assignment)

(Signal assignment)

lval \le exp

wait on sig_list

until exp for timeout

(Suspension)

while exp do process

(Iteration)

\Sigma_{i \in [1,n]} exp<sub>i</sub> -> process<sub>i</sub>

(Alternative)

display(x, ..., x)

(Display)

\rightarrow lvec_to_int(x, n, x)

\rightarrow int_to_lvec(x, n, x)

(Conversion functions)

\rightarrow x \mid lval[exp]

(Memory accesses)

lval

exp

ightarrow '0' | '1' | 'U'

n \in \mathbb{Z} \mid \mathsf{true} \mid \mathsf{false}

(Constants)

lval | op exp | exp op exp

lrnd() | rnd()

(Random generators)

rising\_edge(x)

(Edge detector)

op \rightarrow not \mid or \mid and

lnot | lxor | land

→ - | + | < | =</p>

```

where x is a variable or a signal identifier,  $sig\_list$  a possibly empty set of signal names and timeout a positive integer or the keyword ever (to denote the absence of timeout clause). The notation  $\{...\}$  reads "zero or more instances of the enclosed".

Figure 3.1: Syntax of mini-VHDL

uses petri nets as an intermediate representation.

Slightly more esoteric work include some denotational semantics [BFK95] and [FM95], a Hoare logic implemented in Prolog [BSK94], a compilatory semantics to the temporal logic of actions [Gol94].

Similar work has been done with the Verilog language [Gor95].

#### 3.3 Syntax

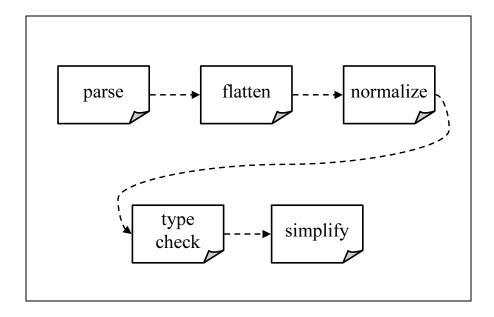

As specified by the standard [IEE02], the elaboration phase translates descriptions into an executable model. We have implemented a front-end to automatically perform this preliminary step. It first parses the source files. It instantiates all modules and produces a flat description. Then it normal-

izes the various VHDL statements so that they all fit a more concise syntax. At the same time, it renames all identifiers in order to safely hoist all definitions at the global scope. It then checks and propagates type information. At last, it scalarizes array assignments. For instance the following code:

```

a(i) := a(i) xor a(i + 1);

-- where the type of variable a is defined as

-- array(15 downto 0) of std_logic_vector(3 downto 0)

becomes:

a[i][3] := a[i][3] xor a[i + 1][3];

a[i][2] := a[i][2] xor a[i + 1][2];

a[i][1] := a[i][1] xor a[i + 1][1];

```

a[i][0] := a[i][0] xor a[i + 1][0];

All these transformations are very conventional: see for instance [WM95, App98] for a description of basic type checking, the VHDL IEEE standard [IEE02] describes hierarchy flattening and [SV00] explains the scalarisation process for Verilog.

Elaborated descriptions belong to mini-VHDL, the language whose abstract syntax is depicted in Fig. 3.1. A description consists of the parallel composition of a fixed number of sequential processes. Each process is a sequence of statements. A statement may either be a variable or signal assignment, a wait statement, a while loop, an alternative construct or a print statement. The descriptions manipulate std\_logics, booleans, integers and statically allocated multi-dimensional arrays. Of the std\_logic literals only '0', '1' and 'U' are actually used. Operators that expect arguments of the type std\_logic are prefixed by the letter 1 as in lnot, lxor and land. The rising\_edge is necessary to detect rising edges of clocks. Functions lvec\_to\_int and int\_to\_lvec convert an array of std\_logic to an integer and back. Even though these three functions are not basic VHDL but defined in external IEEE packages [IEE93], we consider them as primitive operators. We also incorporate random generators rnd and 1rnd to be able to inject non-determinism in a design. We chose this subset of the language because it allows to handle exactly all the features of the industrial case study we present later in chapter 6. Notice we lack any dynamically allocated datatypes. We also deliberately ban the delayed signal assignments (signal assignments with after clause). As a result, the exact layout of the memory is known at compile time.

#### 3.4 Intuition for the semantic model

The processes of a mini-VHDL description are run concurrently. Communication between processes happens through a shared memory (the signals) and only at some specific synchronization points. Once all processes are suspended, synchronization occurs: the memory is updated and the activity of some processes is resumed. We call a simulation cycle, the execution of the system between two consecutive synchronization points.

#### 3.5 The kernel

We give an operational semantics in the style of Plotkin [Plo81] to mini-VHDL. We introduce our semantics gradually. Let us start with a very limited kernel language that nevertheless embodies the essential paradigm of the VHDL language. It is reduced to only four statements:

Memory holding elements are restricted to signals of the type std $\log$ ic. We denote by Sig the set of all signals defined in the design.

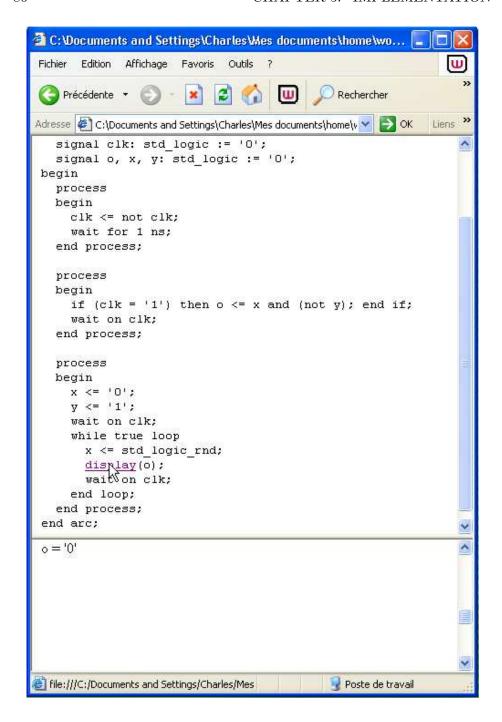

**Example 3.1.** We will illustrate our definitions on the following piece of code:

Figure 3.2: Semantics of expressions

This description manipulates signals from the set  $Sig = \{clk, x, y, o\}$ . It is made up of three processes. A clock generator toggles the clock signal every one unit of time. The middle process computes the output signal o from the input signals x and y on high edges of the clock. A testbench feeds values to the input signals.

We assume each program statement  ${}^lC$  is uniquely tagged with a label l. The label of the unique statement which follows  ${}^lC$  in the control flow graph of the enclosing process can be fetched with next(l). The current point of execution of an individual process is determined by a control point c. For running processes, the control point simply amounts to the label of the statement that has to be executed next. Whereas, the control point of a suspended process is augmented with a list of signals W and a duration t. The duration is either a strictly positive integer or  $\infty$  to indicate the absence of timeout. We denote by  $\mathcal P$  the set of all control points.

For each signal x, defined in the description, a global environment  $\rho$  stores its current and future value, respectively at address x and  $x^+$ . So the environment is a mapping from the set of all memory addresses  $\mathcal{A}$  to values in  $\mathbb{V}$ . At this point of the exposition,  $\mathbb{V}$  equates to the set of std\_logic values, that is  $\mathbb{L} = \{\text{'0'}, \text{'1'}, \text{'U'}\}$ .

We impose the syntactic restriction on descriptions that no signal can be assigned by more than one process. That way, it is sufficient to store only one future value for every signal. We could introduce resolution functions as defined in the standard (see section 2.4 in [IEE02]) at the price of a slight complexification of the semantics definition. It is also possible to emulate resolution functions with additional processes.

At last, a state of execution is a tuple  $(c_1, \ldots, c_n, \rho)$  of control points, followed by a global environment. We denote by  $\Sigma$ , the set of all possible states of execution.

An expression exp evaluates to a value  $v \in \mathbb{V}$  in an environment  $\rho$ , which we express by judgments of the form  $\rho \vdash exp \Longrightarrow v$ . The meaning of expressions is defined in Fig. 3.2 by structural induction in the classical way [Plo81]. Let us simply point out that the function lrnd() arbitrarily picks a std\_logic between '1' and '0'.

Figure 3.3 depicts the sequential execution of an individual process. Signal assignments schedule modifications of the shared memory for the next simulation cycle. The expression on the right-hand side of the statement is evaluated. Then, the resulting value is stored at the address that holds the future value of the assigned signal. Note that a subsequent assignment to the same signal before the next synchronization would replace this value. A

Figure 3.3: Sequential execution

$$\Pi - i \frac{(c_{i}, \rho) \rightharpoonup (c'_{i}, \rho')}{(c_{1}, \dots, c_{i}, \dots, c_{n}, \rho) \rightarrow (c_{1}, \dots, c'_{i}, \dots, c_{n}, \rho')}$$

$$\forall i : c_{i} = (l_{i}, W_{i}, t_{i}) \quad \exists i : wake(W_{i}, \rho)$$

$$\Delta \frac{\forall i : c'_{i} = \begin{cases} l_{i} & \text{if } wake(W_{i}, \rho) \\ c_{i} & \text{otherwise} \end{cases}}{(c_{1}, \dots, c_{n}, \rho) \rightarrow (c'_{1}, \dots, c'_{n}, \rho')}$$

$$\forall i : c_{i} = (l_{i}, W_{i}, t_{i}) \quad \forall i : \neg wake(W_{i}, \rho) \quad \exists i : t_{i} \neq \infty \\ t = \min\{t_{i} \neq \infty\}$$

$$\forall i : c'_{i} = \begin{cases} l_{i} & \text{if } t_{i} = t \\ (l_{i}, W_{i}, t_{i} - t) & \text{if } t_{i} \neq \infty \\ c_{i} & \text{otherwise} \end{cases}$$

$$\Theta \frac{(c_{1}, \dots, c_{n}, \rho) \rightarrow (c'_{1}, \dots, c'_{n}, \rho')}{(c_{1}, \dots, c'_{n}, \rho')}$$

Figure 3.4: Simulation algorithm

wait statement suspends the process. It augments the control point with the conditions that control the awakening. The process will resume its activity if an event occurs on some of the signals in the sensitivity list W or the timeout t is elapsed. The last two statements control the flow of execution and the corresponding rules are classical. Execution simply enters the body of the forever loop. The fact that execution returns to the head of the loop is implicitly encoded by the next function. For the guard statement, the point where execution is transferred depends on the evaluation of the boolean condition.

**Example 3.2.** The operational semantics for the individual processes of our running example 3.1 is:

$$\begin{array}{lll} \rightharpoonup & = & \{(1,\rho) \rightharpoonup (2,\rho)\} \cup \{(2,\rho) \rightharpoonup (3,\rho[\mathtt{clk}^+ \leftarrow [\![\mathtt{lnot}]\!](\mathtt{clk})]\} \\ & \cup \{(3,\rho) \rightharpoonup ((1,\emptyset,1),\rho)\} \cup \{(4,\rho) \rightharpoonup (5,\rho)\} \\ & \cup \{(5,\rho) \rightharpoonup (6,\rho) \mid \rho(\mathtt{clk}) = \mathtt{'1'}\} \cup \{(5,\rho) \rightharpoonup (7,\rho) \mid \rho(\mathtt{clk}) \neq \mathtt{'1'}\} \\ & \cup \{(6,\rho) \rightharpoonup (7,\rho[\mathtt{o}^+ \leftarrow [\![\mathtt{land}]\!](\mathtt{x},[\![\mathtt{lnot}]\!](\mathtt{y})])\} \\ & \cup \{(7,\rho) \rightharpoonup ((4,\{\mathtt{clk}\},\infty),\rho)\} \\ & \cup \{(8,\rho) \rightharpoonup (9,\rho[\mathtt{x}^+ \leftarrow \mathtt{'0'}])\} \cup \{(9,\rho) \rightharpoonup (10,\rho[\mathtt{y}^+ \leftarrow \mathtt{'1'}])\} \\ & \cup \{(10,\rho) \rightharpoonup ((11,\{\mathtt{clk}\},\infty),\rho)\} \cup \{(11,\rho) \rightharpoonup (12,\rho)\} \\ & \cup \{(12,\rho) \rightharpoonup (13,\rho[\mathtt{x}^+ \leftarrow v]) \mid v = \mathtt{'0'} \lor v = \mathtt{'1'}\} \\ & \cup \{(13,\rho) \rightharpoonup ((11,\{\mathtt{clk}\},\infty),\rho)\} \end{array}$$

Now, the three rules of Fig. 3.4 are enough to completely characterize the simulation algorithm of our kernel language. Processes are run concurrently as long as possible thanks to the first rule. Successive steps of execution with the first rule between the application of one of the last two rules constitutes a simulation cycle.

Once all processes are suspended, one of the rules  $\Delta$  or  $\Theta$  applies. The first rule is taken whenever an event has occurred on some of the signals in the sensitivity list of one of the processes.

$$wake(W, \rho) = \exists x \in W : \rho(x) \neq \rho(x^+)$$

.

The  $\Delta$  rule revives any process which satisfies the predicate wake. Then, the shared memory is updated, so that signal assignments encountered during the previous simulation cycle now take effect:

$$\forall x \in Sig : update(\rho)(x) = \rho(x^+)$$

.

| $c_1$             | $c_2$                           | $c_3$                          | ${\tt clk/clk^+}$ | $x/x^+$ | $y/y^+$ | $o/o^+$ |

|-------------------|---------------------------------|--------------------------------|-------------------|---------|---------|---------|

| 1                 | 4                               | 8                              | '0'/'0'           | '0'/'0' | '0'/'0' | '0'/'0' |

| 2                 | 4                               | 8                              | ,0,/,0,           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| 3                 | 4                               | 8                              | ,0,/,1,           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| $1, \emptyset, 1$ | 4                               | 8                              | ,0,/,1,           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| $1, \emptyset, 1$ | 5                               | 8                              | ,0,/,1,           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| $1, \emptyset, 1$ | 7                               | 8                              | ,0,/,1,           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | 8                              | '0'/'1'           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | 9                              | ,0,/,1,           | ,0,/,0, | ,0,/,0, | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | 10                             | '0'/'1'           | ,0,/,0, | 0'/'1'  | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{\mathtt{clk}\}, \infty$   | $11,\{\mathtt{clk}\},\infty$   | '0'/'1'           | ,0,/,0, | 0,/,1,  | ,0,/,0, |

| $1, \emptyset, 1$ | 4                               | 11                             | '1'/'1'           | '0'/'0' | '1'/'1' | '0'/'0' |

| $1, \emptyset, 1$ | 5                               | 11                             | '1'/'1'           | ,0,/,0, | 1,/,1,  | ,0,/,0, |

| $1, \emptyset, 1$ | 6                               | 11                             | '1'/'1'           | ,0,/,0, | 1,/,1,  | ,0,/,0, |

| $1, \emptyset, 1$ | 7                               | 11                             | '1'/'1'           | ,0,/,0, | 1,/,1,  | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | 11                             | 1,/,1,            | ,0,/,0, | 1,/,1,  | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{\mathtt{clk}\}, \infty$   | 12                             | 1,/,1,            | ,0,/,0, | 1,/,1,  | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | 13                             | '1'/'1'           | '0'/'1' | '1'/'1' | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | $11, \{\mathtt{clk}\}, \infty$ | '1'/'1'           | '0'/'1' | '1'/'1' | '0'/'0' |

| 1                 | $4, \{ \mathtt{clk} \}, \infty$ | $11, \{\mathtt{clk}\}, \infty$ | '1'/'1'           | '1'/'1' | '1'/'1' | '0'/'0' |

| 2                 | $4, \{\mathtt{clk}\}, \infty$   | $11, \{\mathtt{clk}\}, \infty$ | '1'/'1'           | '1'/'1' | 1'/'1'  | ,0,/,0, |

| 3                 | $4, \{ \mathtt{clk} \}, \infty$ | $11, \{\mathtt{clk}\}, \infty$ | '1'/'0'           | '1'/'1' | '1'/'1' | ,0,/,0, |

| $1, \emptyset, 1$ | $4,$ {clk}, $\infty$            | $11, \{\mathtt{clk}\}, \infty$ | '1'/'0'           | '1'/'1' | '1'/'1' | '0'/'0' |

| $1, \emptyset, 1$ | 4                               | 11                             | '0'/'0'           | '1'/'1' | '1'/'1' | '0'/'0' |

| $1, \emptyset, 1$ | 5                               | 11                             | '0'/'0'           | '1'/'1' | '1'/'1' | '0'/'0' |

| $1, \emptyset, 1$ | 7                               | 11                             | ,0,/,0,           | '1'/'1' | '1'/'1' | ,0,/,0, |

| $1, \emptyset, 1$ | $4, \{ { m clk} \}, \infty$     | 11                             | ,0,/,0,           | '1'/'1' | '1'/'1' | '0'/'0' |

| $1, \emptyset, 1$ | $4, \{ { m clk} \}, \infty$     | 12                             | ,0,/,0,           | '1'/'1' | '1'/'1' | '0'/'0' |

| $1, \emptyset, 1$ | $4, \{ \mathtt{clk} \}, \infty$ | 13                             | ,0,/,0,           | '1'/'1' | 1,/,1,  | ,0,/,0, |

| 1, Ø, 1           | $4,\{{\tt clk}\},\infty$        | $11, \{ { m clk} \}, \infty$   | '0'/'0'           | '1'/'1' | '1'/'1' | '0'/'0' |

Table 3.1: A run of the simulation algorithm

In this case, no physical time has elapsed. In the VHDL phraseology, the next cycle will be a delta cycle. Delta cycles are the way for an event driven simulation to emulate the instantaneous propagation of electricity through wires.

The  $\Delta$  rule has the priority over the last one, which advances the simulation time by the smallest timeout. All the processes for which the timeout has just expired resume their execution. It may be that neither the delta nor the time-advance rule are fired. This happens when all sensitive signals remain unmodified and all processes wait for ever, in which case the execution is simply blocked. However, simulation usually runs forever.

The initial configuration  $s_0$  of a description  ${}^{l_1}P_1 | \dots | {}^{l_n}P_n$  is of the form  $(l_1, \dots, l_n, \rho_0)$ . It is entirely determined by the initial environment  $\rho_0$  where current and future values of signals must coincide. By default std\_logic signals begin with the 'U' value and integers are initially equal to 0. However, different initial value may be specified in the description.

**Example 3.3.** We tabulate, see table 3.1, the first four cycles of a possible simulation run for the code introduced in example 3.1. All signals are given the initial value '0'.

#### 3.6 More data types: integers and aggregates

Mini-VHDL descriptions not only handle std\_logic values but also integer and multi-dimensional arrays:

$$\beta = \inf \mid \operatorname{std\_logic}$$

$\tau = \beta \mid \tau[l \dots u]$ .

We denote by  $x : \tau$  the fact that signal x has been defined with the particular type  $\tau$ . The set of addresses that are created to store the values of a signal are defined recursively. To build the address of an individual cell, its indices are simply concatenated to the name of the signal:

$$\begin{cases} @(x,\beta) = \{x\} \\ @(x,\tau[l\dots u]) = \{a.i \mid a \in @(x,\tau), l \le i \le u\} . \end{cases}$$

For any set X, we define  $X^+$ , to be  $\{x^+ \mid x \in X\}$ . The set of all addresses allocated to store the current and future value of signals is:

$$\mathcal{A}|_{Sig} = \{a \in @(x,\tau) \mid x \in Sig, x : \tau\}$$

$$\mathcal{A} = \mathcal{A}|_{Sig} \cup \mathcal{A}|_{Sig}^{+}.$$

The domain of the global environment now incorporates all these new addresses. In addition to std\_logics, its range also contains integers:

$$V = \mathbb{L} \cup \mathbb{Z}$$

$$\rho : \mathcal{A} \to V.$$

**Example 3.4.** If the only signal defined in the description is an array b of type  $\operatorname{std\_logic}[1 \dots 3][0 \dots 3]$ , then the set of memory locations is:

$$\mathcal{A} = \{ \mathtt{b}.1.0, \mathtt{b}.1.0^+, \mathtt{b}.1.1, \mathtt{b}.1.1^+, \mathtt{b}.1.2, \mathtt{b}.1.2^+, \mathtt{b}.1.3, \mathtt{b}.1.3^+, \\ \mathtt{b}.2.0, \mathtt{b}.2.0^+, \mathtt{b}.2.1, \mathtt{b}.2.1^+, \mathtt{b}.2.2, \mathtt{b}.2.2^+, \mathtt{b}.2.3, \mathtt{b}.2.3^+, \\ \mathtt{b}.3.0, \mathtt{b}.3.0^+, \mathtt{b}.3.1, \mathtt{b}.3.1^+, \mathtt{b}.3.2, \mathtt{b}.3.2^+, \mathtt{b}.3.3, \mathtt{b}.3.3^+ \} \, .$$

The evaluation of expressions that manipulate integers is nothing but usual:

We introduce the judgment  $\rho \vdash_L lval \implies a : \tau$  that evaluates left values to memory addresses and also returns their type:

$$\begin{array}{c} \underline{x:\tau} \\ \hline \rho \vdash_L x \Longrightarrow x:\tau \\ \hline \\ \underline{\rho \vdash_L lval \Longrightarrow a:\tau[l\dots u] \quad \rho \vdash exp \Longrightarrow i \quad \quad l \leq i \leq u} \\ \hline \\ \rho \vdash_L lval [exp] \Longrightarrow a.i:\tau \end{array}$$

Notice that this semantics checks that every index lies within correct bounds. An out-of-bounds would block the execution. At last, the semantics of memory accesses and signal assignments are modified accordingly as follows:

$$\frac{\rho \vdash_L \mathit{lval} \Longrightarrow a : \tau}{\rho \vdash \mathit{lval} \Longrightarrow \rho(a)}$$

$$\operatorname{sig} \frac{{}^l\mathit{lval} \mathrel{<=} \mathit{exp} \quad \rho \vdash_L \mathit{lval} \Longrightarrow a : \beta \quad \rho \vdash \mathit{exp} \Longrightarrow v}{(l,\rho) \rightharpoonup (next(l), \rho[a^+ \leftarrow v])}$$

During the update of the memory, the future value of each scalar signal and of each element of signal array replaces its corresponding current value:

$$update(\rho)(a) = \begin{cases} \rho(a^+) & a \in \mathcal{A}|_{Sig} \\ \rho(a) & \text{otherwise} \end{cases}$$

#### 3.7 Local variables, conversion functions

We allow variables in mini-VHDL descriptions as long as their use is confined to individual processes. Shared variables, as introduced in the '93 version of the standard, are risky as they possibly make the outcome of a computation depend on the order into which processes are executed.

The domain of global environments is extended with the addresses for the variables Var defined in the description:

$$\mathcal{A}|_{Var} = \{a \in @(x,\tau) \mid x \in Var, x : \tau\}$$

$$\mathcal{A} = \mathcal{A}|_{Var} \cup \mathcal{A}|_{Sig} \cup \mathcal{A}|_{Sig}^{+}.$$

Variables are assigned in an identical way to what happens with classical programming languages:

$$\operatorname{var} \frac{{}^{l} \operatorname{\textit{lval}} := \operatorname{\textit{exp}} \quad \rho \vdash_{L} \operatorname{\textit{lval}} \Longrightarrow a : \beta \quad \rho \vdash \operatorname{\textit{exp}} \Longrightarrow v}{(l, \rho) \rightharpoonup (\operatorname{\textit{next}}(l), \rho[a \leftarrow v])}$$

Integer variables are particularly helpful to control iterations of while loops. Let us recall the behavior of loops:

Variables also play the rôle of intermediate storage when converting between integers and vectors of std\_logic. We have two conversion functions: lvec\_to\_int behaves somewhat like the conv\_integer of the official VHDL package std\_logic\_unsigned, and int\_to\_lvec is found in the std\_logic\_arith package under the name conv\_std\_logic\_vector. The argument n denotes the length of the array y. So we assume that y: std\_logic[0...n-1]. This is checked during the preliminary typing phase. The semantics of the conversion functions is developed in figure 3.5. By convention the left-most cell of the array contains the strongest bit.

**Example 3.5.** At this point we have enough definitions to ascribe a semantics to a piece of code like the following:

$$\forall i \in [0, n-1] : \rho(y.i) \in \{\text{'0', '1'}\} \qquad \varepsilon_i = \begin{cases} 1 & \text{if } \rho(y.i) = \text{'1'} \\ 0 & \text{otherwise} \end{cases}$$

$$v = \sum_{i=1}^{i=n} 2^{n-i} \varepsilon_i$$

$$(l, \rho) \rightharpoonup (next(l), \rho[x \leftarrow v])$$

$$v = \rho(x) \qquad \forall i \in [1, n] : \varepsilon_i = \begin{cases} \text{'1'} & \text{if } (v/2^{n-i})\%2 = 1 \\ \text{'0'} & \text{if } (v/2^{n-i})\%2 = 0 \end{cases}$$

$$\rho' = \rho[y.0 \leftarrow \varepsilon_0] \dots [y.(n-1) \leftarrow \varepsilon_{n-1}]$$

$$(l, \rho) \rightharpoonup (next(l), \rho')$$

Figure 3.5: Conversion functions

```

int_to_lvec(i, 4, tmp);

a[i][0] <= tmp[0];

a[i][1] <= tmp[1];

a[i][2] <= tmp[2];

a[i][3] <= tmp[3];

i := i + 1;</pre>

```

When this program terminates, the future value of the  $i^{\text{th}}$  element of array a contains the binary representation of i.

### 3.8 Rising edges and clocks

As explained in section 3.5, for each signal, we store the current value and the value that is scheduled for the next simulation cycle. In addition, for some signals, it is necessary to retain the value they had during the previous simulation cycle. We denote by Clk the set of all such signals. Designs are synchronized on the edges of clocks. Hence, the unique purpose of the previous value is to detect rising edges, that is transitions from '0' to '1'.

Let us update one last time the definition of the set of memory addresses

and the memory update during synchronization:

$$\mathcal{A}|_{Clk} = \{a \in @(x,\tau) \mid x \in Clk, x : \tau\}$$

$$X^{-} = \{x^{-} \mid x \in X\}$$

$$\mathcal{A} = \mathcal{A}|_{Var} \cup \mathcal{A}|_{Sig} \cup \mathcal{A}|_{Sig}^{+} \cup \mathcal{A}|_{Clk}^{-} \cup \mathcal{A}|_{Clk} \cup \mathcal{A}|_{Clk}^{+}$$

$$\begin{cases} update(\rho)(a) = \rho(a^{+}) & a \in \mathcal{A}|_{Sig} \cup \mathcal{A}|_{Clk} \\ update(\rho)(a^{-}) = \rho(a) & a \in \mathcal{A}|_{Clk} \\ update(\rho)(a) = \rho(a) & \text{otherwise} . \end{cases}$$

We describe the semantics of the rising\_edge operator below:

$$v = \begin{cases} \text{true} & \text{if } \rho(x^{-}) = \text{'0'} \land \rho(x) = \text{'1'} \\ \text{false otherwise} \end{cases}$$

$$\rho \vdash \text{rising\_edge}(x) \Longrightarrow v$$

#### 3.9 Remaining statements

#### 3.9.1 Suspension

The VHDL full suspension statement is slightly richer than the one introduced in section 3.5. In addition to the sensitivity list W and the timeout t, a boolean condition b is another argument of the wait statement. The semantics of wait becomes:

wait wait on

$$W$$

until  $b$  for  $t$   $c = (next(l), W, b, t)$   $(l, \rho) \rightharpoonup (c, \rho)$

For a suspended process to wake up when some signal in the list W, the condition b must evaluate to true in the environment after it has been updated. The revised  $\Delta$  and  $\Theta$  rules appear in Fig. 3.6.

#### 3.9.2 Alternative

The alternative construct, introduced by Dijkstra in [Dij75], is somewhat similar to the selection statement. It picks arbitrarily one of the guarded processes whose guard evaluates to true and runs it:

$$\frac{{}^{l}\Sigma_{i\in[1,n]}b_{i} \rightarrow {}^{l}P_{i} \qquad \rho \vdash b_{j} \Longrightarrow \mathtt{true}}{(l,\rho) \rightharpoonup (l_{j},\rho)}$$

$$\forall i: c_{i} = (l_{i}, W_{i}, b_{i}, t_{i}) \qquad \rho' = update(\rho)$$

$$\exists i: wake(W_{i}, b_{i}, \rho, \rho') \qquad \forall i: c'_{i} = \begin{cases} l_{i} & \text{if } wake(W_{i}, b_{i}, \rho, \rho') \\ c_{i} & \text{otherwise} \end{cases}$$

$$\Delta \frac{(c_{1}, \dots, c_{n}, \rho) \rightarrow (c'_{1}, \dots, c'_{n}, \rho')}{(c_{1}, \dots, c'_{n}, \rho')}$$

$$\forall i: c_{i} = (l_{i}, W_{i}, b_{i}, t_{i}) \qquad \rho' = update(\rho) \qquad \forall i: \neg wake(W_{i}, b_{i}, \rho, \rho')$$

$$\exists i: t_{i} \neq \infty \qquad \qquad \forall i: c'_{i} = \begin{cases} l_{i} & \text{if } t_{i} = t \\ (l_{i}, W_{i}, b_{i}, t_{i} - t) & \text{if } t_{i} \neq \infty \\ c_{i} & \text{otherwise} \end{cases}$$

$$\Theta \frac{(c_{1}, \dots, c_{n}, \rho) \rightarrow (c'_{1}, \dots, c'_{n}, \rho')}{(c_{1}, \dots, c'_{n}, \rho')}$$

$$wake(W, b, \rho, \rho') = (\exists x \in W: \rho(x) \neq \rho'(x)) \land (\rho' \vdash b \Longrightarrow \text{true})$$

Figure 3.6: Synchronization rules

#### 3.9.3 Display

The display command outputs the value of signals and variables to the screen. However, here, it appears not to do much, since we decide not to model screen outputs in our semantics. It proves useful later as a means to report results of the analysis.

show

$$\frac{l \operatorname{display}(\boldsymbol{x}, \ldots, \boldsymbol{x})}{(l, \rho) \rightharpoonup (next(l), \rho)}$$

## 3.10 A benign parallelism

To account for the concurrency in VHDL, we adopted an interleaving model: according to the  $\Pi$  rule, processes can run in any possible order. It can be computationally very expensive to fully explore all the interleaved executions of processes. Fortunately, this is not necessary. In fact, VHDL's parallelism is very weak. It is sufficient to fix a particular ordering for the execution of processes. We replace the  $\Pi$  rule by the more restrictive  $\Psi$  rule which always evaluates the left-most awake process first:

$$\Psi - i \frac{\forall j < i : c_j = (l_j, W_j, b_j, t_j) \quad (c_i, \rho) \rightharpoonup (c'_i, \rho')}{(c_1, \dots, c_i, \dots, c_n, \rho) \rightarrow (c_1, \dots, c'_i, \dots, c_n, \rho')}$$

Figure 3.7: Free swap.

Figure 3.8: Non blocking.

In VHDL, processes modify distinct portion of the memory, so the order into which processes are run during the simulation cycle does not matter. This fact ensures the previous optimization of the semantics is safe.

To prove this claim, we concentrate on the transition relations  $\stackrel{\Pi}{\longrightarrow}$  and  $\stackrel{\Psi}{\longrightarrow}$  respectively induced by the  $\Pi$  and  $\Psi$  rules only. We wish to show that the order of execution of the processes does not affect the set of states that are reached at synchronization points. On the contrary to [Goo95], we can not rely on the determinism of VHDL to deduce the confluence of  $\stackrel{\Pi}{\longrightarrow}$ . Operators rnd() and lrnd() make mini-VHDL intrinsically non-determinist. Because of the while loop, the relation  $\stackrel{\Pi}{\longrightarrow}$  is not necessarily noetherian either.

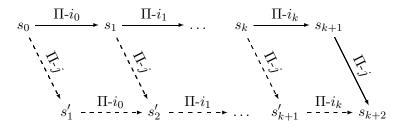

So, it appears we have no choice but to exploit the independence of processes in their concurrent execution. The intuition is formalized by the two properties that are illustrated in Fig. 3.7 and 3.8. First, consecutive execution steps of two distinct processes can be freely swapped:

#### Lemma 3.1.

$$\forall s, u, v : s \xrightarrow{\Pi \text{-} i} u \wedge u \xrightarrow{\Pi \text{-} j} v \Rightarrow \exists u' : s \xrightarrow{\Pi \text{-} j} u' \wedge u' \xrightarrow{\Pi \text{-} i} v .$$

Second, performing one step of a process does not eliminate the possibility of executing another:

#### Lemma 3.2.

$$\forall s, s', u : s \xrightarrow{\Pi - i} s' \wedge s \xrightarrow{\Pi - j} u \wedge i \neq j \Rightarrow \exists u' : s' \xrightarrow{\Pi - j} u'.$$

The proofs of these two lemmas is immediate by inspection of the various cases that define the operational semantics.

We can now state the theorem that warrants the soundness of the optimized version of our semantics. The maximal execution of the transition relations  $\stackrel{\Pi}{\longrightarrow}$  and  $\stackrel{\Psi}{\longrightarrow}$  exactly yield the same set of final<sup>1</sup> states:

#### Theorem 3.1.

$$\forall s : \{s' \mid s \xrightarrow{\Pi} s'\} = \{s' \mid s \xrightarrow{\Psi} s'\}.$$

*Proof.* The fact that  $\{s' \mid s \xrightarrow{\Psi} ! s'\} \subseteq \{s' \mid s \xrightarrow{\Pi} ! s'\}$  is straightforward, since  $\xrightarrow{\Psi}$  is a restriction of  $\xrightarrow{\Pi}$ .

For the converse inclusion, we must establish that if  $s \xrightarrow{\Pi} s'$ , then  $s \xrightarrow{\Psi} s'$ . This is proved by induction on the length of the derivation of  $\xrightarrow{\Pi}$  from s to s'.

- The base case is trivial, since s is terminal and s = s',

- For the induction step, consider the derivation:

$$s_0 \xrightarrow{\Pi - i_0} s_1 \dots \xrightarrow{\Pi - i_n} s_{n+1}$$

.

We set j to be the index of the process that would be executed from  $s_0$  with  $\xrightarrow{\Psi}$ . More precisely, j is such that there exists some state s' and  $s_0 \xrightarrow{\Psi - j} s'$ .

Now, let k be the smallest integer such that  $i_k = j$ . It necessarily exists. Indeed, if it doesn't then repetitive application of lemma 3.2 allows us to establish that there is  $s_{n+2}$  and  $s_{n+1} \xrightarrow{\Pi - j} s_{n+2}$ . This is clearly impossible, since  $s_{n+1}$  is terminal.

If we can show that there exists a derivation:

$$s_0 \xrightarrow{\Pi - j} s'_1 \dots \xrightarrow{\Pi} s_{n+1}$$

,

whose first step is to execute process j, then we can apply the induction hypothesis and conclude that  $s_0 \stackrel{\Psi}{\longrightarrow} ! s_{n+1}$ .

To build this derivation, the idea is to exchange the  $\Pi$ -j step between state  $s_k$  and  $s_{k+1}$  with the one occurring between  $s_0$  and  $s'_1$ . This is

<sup>&</sup>lt;sup>1</sup>Notation  $s \to s'$  stands for  $s \to s' \land s \not\to s'$

done by degrees thanks to lemma 3.1. We prove by induction on k that if:

$$\begin{cases} s_0 \xrightarrow{\Pi - i_0} s_1 \dots \xrightarrow{\Pi - i_{k-1}} s_k \land \forall l \in [0, k[: i_l \neq j] \\ s_k \xrightarrow{\Pi - j} s_{k+1}, \end{cases}$$

then, there exists  $s_0 \xrightarrow{\Pi - j} s_1' \xrightarrow{\Pi - i_0} s_2' \dots \xrightarrow{\Pi - i_{k-1}} s_{k+1}$ . This is trivial for the base case. For the induction step, by lemma (3.1), we can swap the two last transitions. It comes that there is  $s_{k+1}'$  such that  $s_k \xrightarrow{\Pi - j} s_{k+1}' \xrightarrow{\Pi - i_k} s_{k+2}$ . We can then apply the induction hypothesis to complete the construction. This argumentation is pictured below:

### 3.11 Discussion

We recapitulate the domains of the semantics definition, the evaluation of expressions, the sequential execution of processes and the formalisation of the simulation algorithm in Fig. 3.9, 3.10, 3.11, 3.12, 3.13 and 3.14.

This formalization of the simulation algorithm is the basis to the verification tool that is developed in the next chapters. The tool is designed so as to be sound with respect to this particular semantics. Hence, we here make the implicit assumption that synthesis tools that translate VHDL descriptions into physical hardware are coherent with the same semantics. We believe this choice to be acceptable since we strived to be consistent with the only official reference of the VHDL language, that is the IEEE standard. We hope that synthesis tools comply with the same interpretation of the standard as us. If this is not the case, then even when verification succeeds, the final hardware can not be certified correct. Let me back up this claim with a small VHDL example:

if

$$(x = '0')$$

then

```

y <= '1';

else

y <= '0';

end if;</pre>

```

Now, suppose signal x is initialized by the simulator with the value 'U'. Then it is correct to state that y takes the value '0'. However, this piece of code is probably compiled into a multiplexor gate. So, post-synthesis the signal x initially takes one of the value '0' or '1' which results in y being either '0' or '1' too. A similar argument is made in [Fos02] with a Verilog example.

Gaps between semantics allow bugs with daunting consequences to lurk unnoticed through the design flow. So, in practice, it is of the uttermost importance that the various tools that manipulate the design have a common interpretation of its semantics. To convince oneself this is indeed the case is an orthogonal matter, see for instance [Riv04]. This difficult yet necessary task far exceeds the scope of the thesis. Thus, the convenient assumption that synthesis tools are consistent with our view of semantics, is needed to separate concerns.

Alternatively, we could have introduced a simple ad-hoc hardware description language that would suit our verification goals best. We feel this approach is not realistic as it ignores issues that could be lost in potential over-simplifications. Also, hardware engineers work with VHDL models and use VHDL synthesizers. If we want to demonstrate that integration into existing design practice is feasible, we believe it is necessary to work from the same input. Hopefully, we can confine ourselves to the fraction of the language that is actually used by engineers. To aim at providing a formal semantics for whole VHDL is unrealistic. The formalization would be so complex as to become useless. To our relief, the subset we have identified in actual hardware designs seems reasonable. It lends itself well to concise and relatively simple semantics definitions.

We nevertheless believe the essential characteristics of VHDL are present in our semantics. Hence, the semantics embeds a sufficient amount of complexity so as to be realistic for our feasibility study. Also, minor discrepancies can be corrected later and the design of our verification tool can be readily adapted.

$$l \text{ and } (l, W, b, t) \in \mathcal{P}$$

$$\beta = \text{ int } | \text{ std\_logic}$$

$$\tau = \beta | \tau[l \dots u]$$

$$\begin{cases} @(x, \beta) = \{x\} \\ @(x, \tau[l \dots u]) = \{a.i \mid a \in @(x, \tau), l \leq i \leq u\} \end{cases}$$

$$\mathcal{A}|_{Var} = \{a \in @(x, \tau) \mid x \in Var, x : \tau\}$$

$$\mathcal{A}|_{Sig} = \{a \in @(x, \tau) \mid x \in Sig, x : \tau\}$$

$$\mathcal{A}|_{Clk} = \{a \in @(x, \tau) \mid x \in Clk, x : \tau\}$$

$$\mathcal{A} = \mathcal{A}|_{Var} \cup \mathcal{A}|_{Sig} \cup \mathcal{A}|_{Sig}^+ \cup \mathcal{A}|_{Clk}^- \cup \mathcal{A}|_{Clk}^+ \cup \mathcal{A}|_{Clk}^+$$

$$\mathbb{L} = \{`0`, `1`, `U`\}$$

$$\mathbb{V} = \mathbb{L} \cup \mathbb{Z}$$

$$\rho : \mathcal{A} \to \mathbb{V}$$

Figure 3.9: Control points, types, memory locations, values and environments

Figure 3.10: Operators

$$\begin{array}{c} \underline{x:\tau} \\ \hline \rho \vdash_L x \Longrightarrow x:\tau \\ \hline \\ \rho \vdash_L lval \Longrightarrow a:\tau[l\dots u] \quad \rho \vdash exp \Longrightarrow i \quad l \leq i \leq u \\ \hline \\ \rho \vdash_L lval [exp] \Longrightarrow a.i:\tau \end{array}$$

Figure 3.11: Left values

Figure 3.12: Evaluation of expressions

$$\operatorname{sig} \frac{{}^{l}\operatorname{Ival} \mathrel{<=} \operatorname{exp} \quad \rho \vdash_{L}\operatorname{Ival} \Longrightarrow a : \beta \quad \rho \vdash \operatorname{exp} \Longrightarrow v}{(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho[a^{+} \leftarrow v])}$$

$$\operatorname{var} \frac{{}^{l}\operatorname{Ival} := \operatorname{exp} \quad \rho \vdash_{L}\operatorname{Ival} \Longrightarrow a : \beta \quad \rho \vdash \operatorname{exp} \Longrightarrow v}{(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho[a \leftarrow v])}$$

$$\operatorname{wait} \frac{{}^{l}\operatorname{wait} \text{ on } W \text{ until } b \text{ for } t \quad c = (\operatorname{next}(l),W,b,t)}{(l,\rho) \rightharpoonup (c,\rho)}$$

$$\operatorname{enter} \frac{{}^{l}\operatorname{while} b \text{ do } {}^{l}C; P \quad \rho \vdash b \Longrightarrow \operatorname{true}}{(l,\rho) \rightharpoonup (l',\rho)}$$

$$\operatorname{choose} \frac{{}^{l}\Sigma_{i \in [1,n]}b_{i} \rightarrow {}^{l}P_{i} \quad \rho \vdash b_{j} \Longrightarrow \operatorname{true}}{(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho)}$$

$$\operatorname{choose} \frac{{}^{l}\Sigma_{i \in [1,n]}b_{i} \rightarrow {}^{l}P_{i} \quad \rho \vdash b_{j} \Longrightarrow \operatorname{true}}{(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho)}$$

$$\operatorname{show} \frac{{}^{l}\operatorname{display}(x, \ldots, x)}{(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho)}$$

$${}^{l}\operatorname{lvec\_to\_int}(y, n, x)$$

$$\forall i \in [0,n-1] : \rho(y.i) \in \{`0`, `'1`\} \quad \varepsilon_{i} = \begin{cases} 1 & \text{if } \rho(y.i) = `'1`} \\ 0 & \text{otherwise} \end{cases}$$

$$v = \sum_{i=1}^{l-n} 2^{n-i}\varepsilon_{i}$$

$$(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho[x \leftarrow v])$$

$${}^{l}\operatorname{int\_to\_lvec}(x, n, y)$$

$$v = \rho(x) \quad \forall i \in [1,n] : \varepsilon_{i} = \begin{cases} `1' & \text{if } (v/2^{n-i})\%2 = 1 \\ `0' & \text{if } (v/2^{n-i})\%2 = 0 \end{cases}$$

$$\rho' = \rho[y.0 \leftarrow \varepsilon_{0}] \ldots [y.(n-1) \leftarrow \varepsilon_{n-1}]$$

$$(l,\rho) \rightharpoonup (\operatorname{next}(l),\rho')$$

Figure 3.13: Sequential process execution

$$\Psi - i \frac{\forall j < i : c_j = (l_j, W_j, b_j, t_j) \qquad (c_i, \rho) \rightharpoonup (c'_i, \rho')}{(c_1, \dots, c_i, \dots, c_n, \rho) \rightarrow (c_1, \dots, c'_i, \dots, c_n, \rho')}$$

$$\forall i : c_i = (l_i, W_i, b_i, t_i) \qquad \rho' = update(\rho)$$

$$\exists i : wake(W_i, b_i, \rho, \rho') \qquad \forall i : c'_i = \begin{cases} l_i & \text{if } wake(W_i, b_i, \rho, \rho') \\ c_i & \text{otherwise} \end{cases}$$

$$(c_1, \dots, c_n, \rho) \rightarrow (c'_1, \dots, c'_n, \rho')$$

$$\forall i : c_i = (l_i, W_i, b_i, t_i) \qquad \rho' = update(\rho) \qquad \forall i : \neg wake(W_i, b_i, \rho, \rho')$$

$$\exists i : t_i \neq \infty \qquad \qquad \forall i : c'_i = \begin{cases} l_i & \text{if } t_i = t \\ (l_i, W_i, b_i, t_i - t) & \text{if } t_i \neq \infty \\ c_i & \text{otherwise} \end{cases}$$

$$(c_1, \dots, c_n, \rho) \rightarrow (c'_1, \dots, c'_n, \rho')$$

$$\begin{cases} update(\rho)(a) = \rho(a^+) & a \in \mathcal{A}|s_{ig} \cup \mathcal{A}|C_{lk} \\ update(\rho)(a^-) = \rho(a) & \text{otherwise} \end{cases}$$

$$wake(W, b, \rho, \rho') = (\exists x \in W : \rho(x) \neq \rho'(x)) \land (\rho' \vdash b \Longrightarrow \text{true})$$

Figure 3.14: Simulation algorithm

## Chapter 4

# **Abstract Interpretation**

## 4.1 Collecting semantics

To show the absence of errors in a VHDL design, we need to estimate the states that are reachable from some initial configuration  $s_0$ :

$$\mathcal{O} = \{ s \mid s_0 \to^* s \} .$$

This set can be equivalently expressed as the least fixpoint of the continuous function  $\mathbb{F}$  on the complete lattice of set of states  $(\wp(\Sigma), \emptyset, \Sigma, \cup, \cap)$  where:

$$\mathbb{F}(X) = \{s_0\} \cup \{s' \mid \exists s \in X : s \to s'\} .$$

Unfortunately, because of the excessive size of the state space, the computation of this fixpoint often turns out to be too expensive.

## 4.2 Abstract Interpretation

We follow the methodology of abstract interpretation [Cou78, CC77, Cou81, CC92] to design a tool that computes a superset of the reachable states. We proceed in two steps. First, we need to choose our representation for sets of states. In other words, we must pick an abstract domain. In our case, the abstract domain is a complete partial order  $(D^{\sharp}, \sqsubseteq, \bot, \sqcup)$ . The meaning of an element of  $D^{\sharp}$  is given, in terms of set of states, thanks to a monotonic concretization function:

$$\gamma:D^{\sharp}\to\wp(\Sigma)$$

.

The bottom element  $\perp$  provides us with an abstraction of the empty set and the abstract join  $\sqcup$  computes an upper-bound of two elements in  $D^{\sharp}$ .

Second, we systematically derive from  $\mathbb F$  a monotonic function that operates on the abstract domain:

$$\mathbb{F}^{\sharp}: D^{\sharp} \to D^{\sharp}$$

.

The abstract operator  $\mathbb{F}^{\sharp}$  must be sound. Namely the application of  $\mathbb{F}^{\sharp}$  yields a result that contains all the states obtained when applying  $\mathbb{F}$ :

$$\mathbb{F} \circ \gamma \subset \gamma \circ \mathbb{F}^{\sharp}$$

.

This local soundness condition ensures that the least fixpoint of  $\mathbb{F}^{\sharp}$  is a sound over-approximation of the reachable states:

#### Theorem 4.1 (Soundness).

$$\mathrm{lfp}_{\emptyset}\mathbb{F} \subseteq \gamma(\mathrm{lfp}_{\perp}\mathbb{F}^{\sharp})$$

.

*Proof.* Let  $\mathbb{F}_n$  and  $\mathbb{F}_n^{\sharp}$  respectively be the  $n^{\text{th}}$  iterate from  $\emptyset$  and  $\bot$  of  $\mathbb{F}$  and  $\mathbb{F}^{\sharp}$ . We prove by induction, that for all integer n,  $\mathbb{F}_n \subseteq \gamma(\mathbb{F}_n^{\sharp})$ . The base case is immediate since  $\emptyset \subseteq \gamma(\bot)$ . Suppose we know  $\mathbb{F}_n \subseteq \gamma(\mathbb{F}_n^{\sharp})$ , then by monotonicity of  $\mathbb{F}$ , it comes that  $\mathbb{F}(\mathbb{F}_n) \subseteq \mathbb{F}(\gamma(\mathbb{F}_n^{\sharp}))$ . We deduce thanks to the local correctness that  $\mathbb{F}_{n+1} \subseteq \gamma(\mathbb{F}^{\sharp}(\mathbb{F}_n^{\sharp}))$ . This ends the induction.

Since  $\gamma$  is monotonic, we may establish that  $\gamma(\mathbb{F}_n^{\sharp}) \subseteq \gamma(\bigsqcup_n \mathbb{F}_n^{\sharp})$ . So we have that  $\mathbb{F}_n \subseteq \gamma(\bigsqcup_n \mathbb{F}_n^{\sharp})$ . By definition of the least upper bound, it is also true that:

$$\bigcup_{n} \mathbb{F}_{n} \subseteq \gamma(\bigsqcup_{n} \mathbb{F}_{n}^{\sharp}) .$$

On one hand, since  $\mathbb{F}$  is a continuous map on the complete lattice of set of states, by Kleene's theorem [Kle52], it comes that:

$$\mathrm{lfp}_{\emptyset}\mathbb{F} = \bigcup_{n} \mathbb{F}_{n} .$$

On the other hand, the constructive version of Tarski's fixpoint theorem [CC79a], guarantees the existence of the least fixpoint of the monotonic map  $\mathbb{F}^{\sharp}$  on the complete partial order  $(D^{\sharp}, \sqsubseteq, \bot, \sqcup)$ . By a simple induction one checks that  $\coprod_n \mathbb{F}_n^{\sharp} \sqsubseteq \operatorname{lfp}_{\bot} \mathbb{F}^{\sharp}$ . By monotonicity of  $\gamma$ , we have:

$$\gamma(\bigsqcup_{n} \mathbb{F}_{n}^{\sharp}) \subseteq \gamma(\mathrm{lfp}_{\perp} \mathbb{F}^{\sharp})$$

.

We have established the following sequence of inequalities:

$$\operatorname{lfp}_{\emptyset}\mathbb{F} = \bigcup_{n} \mathbb{F}_{n} \subseteq \gamma(\bigsqcup_{n} \mathbb{F}_{n}^{\sharp}) \subseteq \gamma(\operatorname{lfp}_{\perp} \mathbb{F}^{\sharp}).$$

We conclude by transitivity.

When the abstract domain is of finite height, the constructive version of Tarski's theorem [CC79a] yields a naive algorithm to obtain the abstract semantics. It suffices to compute the successive iterates  $\bot$ ,  $\mathbb{F}^{\sharp}(\bot)$ ,  $\mathbb{F}^{\sharp}(\mathbb{F}^{\sharp}(\bot))$ , ... until stabilization.

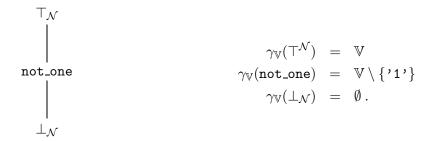

#### 4.3 Abstract domain

We suppose we are given an abstract numerical domain to describe sets of environments. A numerical domain is a complete partial order  $(\mathcal{N}, \sqsubseteq_{\mathcal{N}}, \bot_{\mathcal{N}}, \sqcup_{\mathcal{N}})$ . The meaning of its elements is given in terms of sets of environments by a monotonic concretization function:

$$\gamma_{\mathcal{N}}: (\mathcal{N}, \sqsubseteq_{\mathcal{N}}) \longrightarrow (\wp(\mathcal{A} \to \mathbb{V}), \subseteq)$$

.

The abstract bottom and join operators must be such that:

$$\emptyset = \gamma_{\mathcal{N}}(\bot_{\mathcal{N}})$$

$$\gamma_{\mathcal{N}}(X) \cup \gamma_{\mathcal{N}}(Y) \subseteq \gamma_{\mathcal{N}}(X \sqcup_{\mathcal{N}} Y) .$$

We abstract a set of states by a function Y that maps each tuple of program points to an abstract environment:

$$Y: \mathcal{P}^n \to \mathcal{N}$$

.

This mapping represents all the states  $(c_1, \ldots, c_n, \rho)$  for which the environment  $\rho$  satisfies the constraints associated to the program points  $(c_1, \ldots, c_n)$ :

$$\gamma(Y) = \{(c_1, \dots, c_n, \rho) \mid \rho \in \gamma_{\mathcal{N}}(Y(c_1, \dots, c_n))\}.$$

Monotonicity of  $\gamma$  is readily checked. The abstract domain  $(\mathcal{P}^n \to \mathcal{N}, \sqsubseteq, \bot, \sqcup)$  is a complete partial order whose operations are the pointwise extensions of the ones on the numerical domain  $\mathcal{N}$ .

#### 4.4 Abstract semantics transformer

#### 4.4.1 Expressions

There is no way we can reference the future value of signals or the past value of clocks with the current syntax of expressions. In order to have access to any single memory location, we extend the syntax of left values in the following manner:

While the semantics of modifiers future and past is:

$$egin{aligned}

ho dash_L \ \mathit{loc} &\Longrightarrow a : au \

ho dash_L \ \mathit{future(loc)} &\Longrightarrow a^+ : au \ \end{matrix}$$

$egin{aligned}

ho dash_L \ \mathit{loc} &\Longrightarrow a : au \ \end{matrix}$

$egin{aligned}

ho dash_L \ \mathit{past(loc)} &\Longrightarrow a^- : au \end{aligned}$

We can now safely replace any  $rising\_edge(x)$  by the semantically equivalent:

$$past(x) = 0$$

, and  $x = 1$ .

It will also be helpful to generate arbitrary integers, so that we add the integer random generator irnd():

$$\frac{i \in \mathbb{Z}}{\rho \vdash \text{irnd()} \Longrightarrow i}$$

#### 4.4.2 Sequential statements

The equations in Fig. 4.1 specify the abstract semantics for each sequential statement in the language. They rely on the existence of a few primitives that manipulate the numerical domain  $\mathcal{N}$ : assign undertakes assignments, select asserts boolean conditions and get\_val returns the value of an expression when possible,  $\Omega$  otherwise. Each operation must obey a soundness condition:

$$\begin{cases} \rho[a \leftarrow v] \, \middle| \, \rho \in \gamma_{\mathcal{N}}(R) \wedge \rho \vdash_{L} \mathit{lval} \Longrightarrow a \\ \rho \vdash \mathit{exp} \Longrightarrow a \end{cases} \subseteq \gamma_{\mathcal{N}}(\mathsf{assign}_{\mathit{lval} \leftarrow \mathit{exp}}(R))$$

$$\{ \rho \, | \, \rho \in \gamma_{\mathcal{N}}(R) \wedge \rho \vdash \mathit{exp} \Longrightarrow \mathsf{true} \} \subseteq \gamma_{\mathcal{N}}(\mathsf{select}_{\mathit{exp}}(R))$$

$$\{ v \, | \, \exists \rho \in \gamma_{\mathcal{N}}(R) \wedge \rho \vdash \mathit{exp} \Longrightarrow v \} \subseteq \gamma_{\mathcal{V}}(\mathsf{get\_val}_{\mathit{exp}}(R))$$