## Modulateur Sigma Delta Passe-Haut et son application au convertisseur Sigma Delta à l'entrelacement temporel

van Tam Nguyen

#### ► To cite this version:

van Tam Nguyen. Modulateur Sigma Delta Passe-Haut et son application au convertisseur Sigma Delta à l'entrelacement temporel. domain\_other. Télécom ParisTech, 2004. English. NNT: . pastel-00000929

## HAL Id: pastel-00000929 https://pastel.hal.science/pastel-00000929

Submitted on 3 Feb 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# $\begin{array}{l} \textbf{High-Pass } \Delta \Sigma \ \textbf{Modulator} \\ \textbf{and its Application to} \\ \textbf{Time-Interleaved} \ \Delta \Sigma \ \textbf{Converter} \end{array}$

Van Tam Nguyen

COMELEC Departement

Ecole Nationale Supérieure des Télécommunications

## Remerciements

Cette thèse a été effectuée au sein du département Communications et électronique de l'Ecole Nationale Supérieure des Télécommunications. Je tiens tout particulièrement à remercier mes deux directeurs de thèse Monsieur Patrick Loumeau et Monsieur Jean-François Naviner de m'avoir accueilli et accordé une totale confiance au cours de son développement. Le sujet était très ambitieux, et ils m'ont permis par leur connaissance et leur lucidité sur le sujet, de mener à bien cette recherche.

J'exprime toute ma gratitude à Monsieur Pierre Duhamel, Directeur de Recherche de CNRS, pour avoir accepté de présider le Jury de thèse.

Je suis très honoré que Monsieur le Professeur José Luis Huertas et Monsieur le Professeur Denis Flandre, aient acceptés d'être les deux rapporteurs de cette thèse. Je les remercie de cet engagement dans cette lourde tâche, d'autant que je sais leur emploi du temps extrêmement chargé.

Mes remerciements s'adressent également à François Barbara, Ingénieur de Schlumberger, d'avoir bien voulu d'examiner ce travail et pour les échanges que j'ai pu avoir avec lui.

J'associe toutes les personnes qui font partie du département à ces remerciements et plus particulièrement Monsieur Hervé Petit pour ses apports constructifs et son aide pour le banc de test, Monsieur Jean-François Naviner pour son aide à l'utilisation et la gestion des outils de conception et Madame Patricia Desgreys pour son aide au développement des modèles en VHDL-AMS. Je ne peux omettre Monsieur Karim Benkalaia pour son aide à la conception de la carte de test du circuit et Monsieur Jacky Porte pour son aide de l'utilisation de l'outil OCEANE, ainsi que Madame Chantal Cadiat pour sa disponibilité et sa gentillesse.

Comment oublier tous les thésards et les stagiaires avec qui j'ai partagé de longs moments et surtout un projet commun. Leur confort et leur présence ont tout

#### Remerciements

simplement rendu agréable ces années de thèse. J'adresse mes amitiés et renouvelle mes remerciements à Frédéric, mon partenaire du projet, ainsi que Bilal, Elisabeth, Elisabette, Kae, Sabeur, Mohamed, David, Richard, Nesrine, Sonia et Maryam. J'espère que nous gardons le contact par la suite.

Je pense enfin à toute ma famille, et en particulier mes parents, mon frère et ma sœur, qui m'ont donné le courage de faire cette thèse. Un remerciement spécial pour mon épouse Nguyên, qui m'a soutenu tout au long de ce travail, et qui a su apporter avec talent et enthousiasme les touches finales à ce manuscrit. Cette thèse est donc aussi la leur.

#### **Projet SPRING**

Ma thèse est effectuée dans le cadre d'un projet de recherche européen intitulé SPRING. Ce projet est coordonné par Schlumberger Industries (France) avec la participation de trois partenaires universitaires:

- Université Catholique de Louvain (UCL Belgique);

- Centro Nacional de Microelectronica (CNM Espagne);

- Ecole Nationale Supérieure des Télécommunications (ENST France).

Ce projet propose la création d'un réseau de recherches et de formation recueillant les partenaires universitaires (CNM, ENST, et UCL) et l'industrie (Schlumberger) pour établir et échanger les connaissances. Le réseau s'est concentré sur le transfert des technologies entre les partenaires (à travers les thèse doctorales) et sur la formation mutuelle et complémentaire de tous les partenaires.

Cette thèse a donc la privilège d'être suivie et encadrée par des industriels, avec leurs points de vue réalistes et critiques dans les différentes phases de son dévellopement. Je tiens donc à remercier Messieurs Lionel Beneteau, François Barbara, Matthias Sicard et Gilles Picard qui ont participé activement au bon déroulement de cette thèse.

Le rapport de thèse fait partie des deliverables du projet. C'est la raison pour laquelle il est écrit en anglais.

## Résumé

Le convertisseur analogique-numérique fondé sur le principe de modulation  $\Sigma\Delta$  est capable de fournir une très haute résolution. Bien qu'il nécessite un suréchantillonnage, il est peu sensible aux imperfections des composants. Le modulateur  $\Sigma\Delta$ classique est donc très populaire pour les applications de bande étroite demandant une très haute résolution.

Dans cette thèse, nous nous sommes intéressés à l'extension des applications du modulateur  $\Sigma\Delta$  vers une bande passante plus large. Nous avons tout d'abord étudié l'architecture parallèle basant sur la modulation  $\Sigma\Delta$  et proposé une nouvelle architecture basant sur la modulation  $\Sigma\Delta$  passe-haut et l'entrelacement temporel permettant de réduire de façon significative le problème caractéristique du parallélisme, à savoir la disparité entre les canaux.

Nous avons ensuite étudié le modulateur  $\Sigma\Delta$  passe-haut et proposé une implémentation en technique des capacités commutées. Ce nouveau modulateur, contrairement au modulateur classique, est complètement immune au bruit de basse fréquence et peut être utilisé non seulement dans une architecture parallèle, mais aussi de façon autonome.

Nous avons aussi modélisé la plupart de non-idéalités du modulateur en VHDL-AMS pour finalement arriver à une méthodologie de conception descendante qui permet de dériver les spécifications de tous les blocs du circuit à partir de performance visée pour le système complet. L'implémentation d'un modulateur  $\Sigma\Delta$  passehaut d'ordre 2 et un convertisseur  $\Sigma\Delta$  passe-haut en combinant avec l'entrelacement temporel a été réalisée en technologie CMOS 0,35  $\mu$ m.

Enfin, notre travail nous a permis de démontrer non seulement l'avantage du modulateur  $\Sigma\Delta$  passe-haut, mais aussi un perspective prometteur du modulateur  $\Sigma\Delta$  parallèle pour les applications de très large bande.

## Abstract

The analog-to-digital converter based on the  $\Delta\Sigma$  modulation is capable of providing a very high resolution. Although it requires an oversampling, it is not sensitive to the imperfections of the components. The conventional  $\Delta\Sigma$  modulator is thus very popular for narrowband applications requiring a very high resolution.

In this thesis, we consider the extension of the  $\Delta\Sigma$  modulators towards wideband applications. First, we studied parallel architectures basing on the  $\Delta\Sigma$  modulation and proposed a new architecture basing on the high-pass  $\Delta\Sigma$  modulation and timeinterleaved allowing to reduce significantly the characteristic problem of parallelism, namely the channel mismatch.

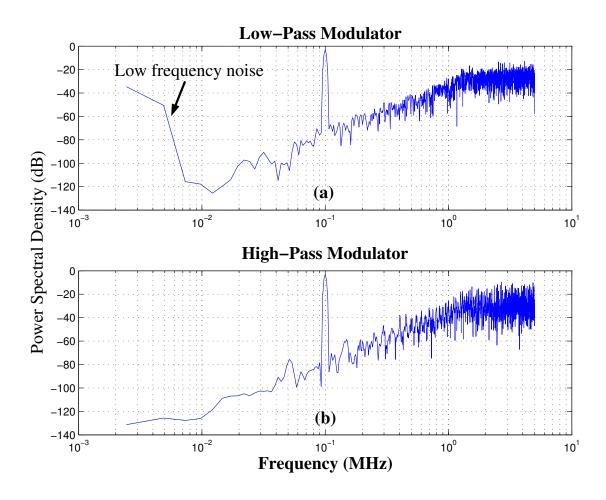

We then studied the high-pass  $\Delta\Sigma$  modulator and proposed an implementation in switched-capacitor technique. This new modulator, contrary to the conventional modulator, is completely immune to the low frequency noise and can be used not only in a parallel architecture, but also as stand-alone modulator.

We also modelled the main non-idealities of the  $\Delta\Sigma$  modulator in VHDL-AMS for finally arriving at a top-down design methodology which makes it possible to derive the specifications of all the circuit blocks from the performance aimed for the complete system. The implementation of a high-pass second order  $\Delta\Sigma$  modulator and a time-interleaved high-pass  $\Delta\Sigma$  converter was carried out in 0.35  $\mu$ m CMOS technology.

Finally, our work allowed us to demonstrate, not only the advantages of the highpass  $\Delta\Sigma$  modulator, but also a promising prospect of the parallel  $\Delta\Sigma$  modulators for the wide band applications.

# Contents

|   | Ren  | ierciements                               |

|---|------|-------------------------------------------|

|   | Rési | $\operatorname{Im}\acute{\mathrm{e}}$     |

|   | Abs  | tract                                     |

|   | Con  | tents                                     |

|   | List | of Figures                                |

|   | List | of Tables                                 |

|   | List | ngs                                       |

|   | Abb  | reviations                                |

| 1 | Intr | roduction 1                               |

|   | 1.1  | Motivations and Objectives                |

|   | 1.2  | Organization                              |

| 2 | Ana  | alog-to-Digital Converter Architectures 5 |

|   | 2.1  | Introduction                              |

|   | 2.2  | Flash Converter    5                      |

|   | 2.3  | Successive Approximation ADC              |

|   | 2.4  | Pipeline Converter                        |

|   | 2.5  | Time-Interleaved ADC                      |

|   | 2.6  | Hybrid Filter Bank ADC                    |

|   |      |                                           |

#### CONTENTS

| 2.7                                           | $\Delta\Sigma$ Converter                                                                                                                                  | 14                                                                                                         |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 2.8                                           | Conclusion                                                                                                                                                | 15                                                                                                         |

| Hig                                           | h-Pass Delta Sigma Modulator                                                                                                                              | 17                                                                                                         |

| 3.1                                           | Introduction                                                                                                                                              | 17                                                                                                         |

| 3.2                                           | Conventional $\Delta\Sigma$ Modulator                                                                                                                     | 19                                                                                                         |

| 3.3                                           | Presence of Low Frequency Noise                                                                                                                           | 27                                                                                                         |

| 3.4                                           | Principle of high-pass $\Delta\Sigma$ Modulator                                                                                                           | 30                                                                                                         |

| 3.5                                           | Performance of high-pass $\Delta\Sigma$ Modulator                                                                                                         | 34                                                                                                         |

| 3.6                                           | Switched-Capacitor Basis Block Implementation                                                                                                             | 38                                                                                                         |

| 3.7                                           | Modulator Stability                                                                                                                                       | 42                                                                                                         |

| 3.8                                           | Conclusion                                                                                                                                                | 50                                                                                                         |

| Tin                                           | ne-Interleaved $\Delta\Sigma$ Converter                                                                                                                   | 53                                                                                                         |

|                                               |                                                                                                                                                           | •                                                                                                          |

| 4.1                                           | Introduction                                                                                                                                              | 53                                                                                                         |

| <ul><li>4.1</li><li>4.2</li></ul>             | Introduction                                                                                                                                              | 53<br>54                                                                                                   |

|                                               |                                                                                                                                                           |                                                                                                            |

| 4.2                                           | Architecture                                                                                                                                              | 54<br>58                                                                                                   |

| 4.2                                           | Architecture                                                                                                                                              | 54<br>58                                                                                                   |

| 4.2                                           | Architecture                                                                                                                                              | 54<br>58<br>59<br>61                                                                                       |

| 4.2                                           | Architecture                                                                                                                                              | 54<br>58<br>59<br>61<br>63                                                                                 |

| 4.2                                           | Architecture                                                                                                                                              | <ul> <li>54</li> <li>58</li> <li>59</li> <li>61</li> <li>63</li> <li>66</li> </ul>                         |

| 4.2                                           | Architecture                                                                                                                                              | <ul> <li>54</li> <li>58</li> <li>59</li> <li>61</li> <li>63</li> <li>66</li> </ul>                         |

| <ul><li>4.2</li><li>4.3</li></ul>             | Architecture                                                                                                                                              | <ul> <li>54</li> <li>58</li> <li>59</li> <li>61</li> <li>63</li> <li>66</li> <li>68</li> <li>71</li> </ul> |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul> | Architecture                                                                                                                                              | <ul> <li>54</li> <li>58</li> <li>59</li> <li>61</li> <li>63</li> <li>66</li> <li>68</li> <li>71</li> </ul> |

|                                               | <ol> <li>2.8</li> <li>Hig</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>Tim</li> </ol> | 2.8       Conclusion                                                                                       |

#### CONTENTS

| 5 | Des | ign M  | ethodology with VHDL-AMS      | 87  |

|---|-----|--------|-------------------------------|-----|

|   | 5.1 | Introd | uction                        | 87  |

|   | 5.2 | VHDL   | -AMS Overview                 | 88  |

|   | 5.3 | Top-D  | own Methodology with VHDL-AMS | 90  |

|   | 5.4 | Comp   | onent models                  | 93  |

|   |     | 5.4.1  | Clock Jitter Noise            | 94  |

|   |     | 5.4.2  | Switch Noise                  | 96  |

|   |     | 5.4.3  | Operational Amplifier Noise   | 97  |

|   |     | 5.4.4  | White Noise Model             | 98  |

|   |     | 5.4.5  | 1/f Noise Model               | 101 |

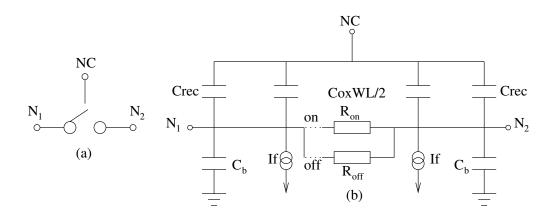

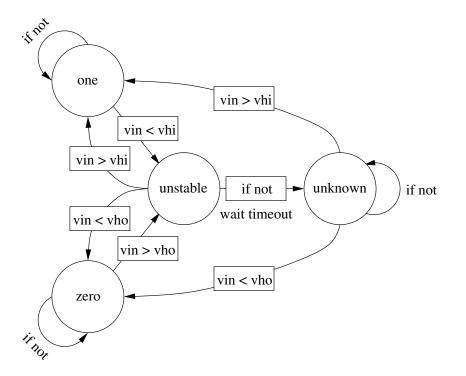

|   |     | 5.4.6  | Switch Model                  | 102 |

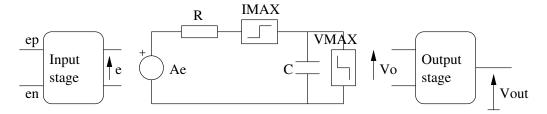

|   |     | 5.4.7  | Operational Amplifier Model   | 105 |

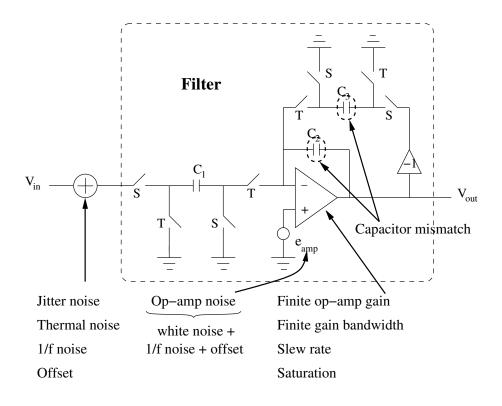

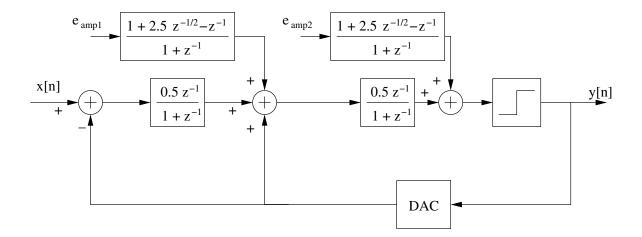

|   |     | 5.4.8  | Complete Filter Model         | 108 |

|   |     | 5.4.9  | Comparator                    | 109 |

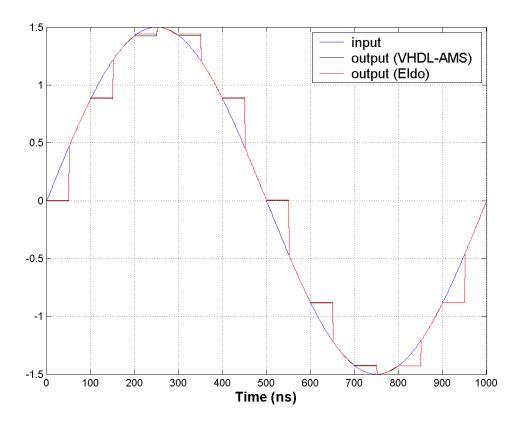

|   | 5.5 | Simula | ation Results                 | 109 |

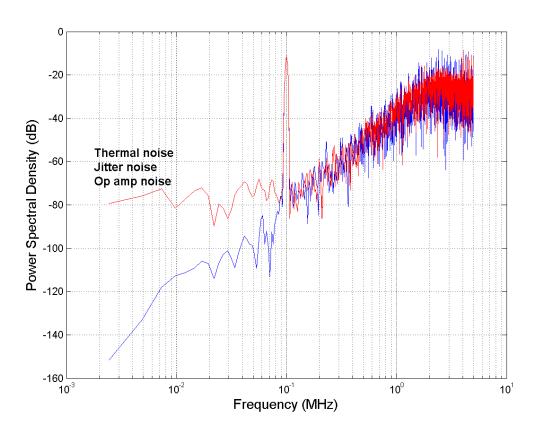

|   |     | 5.5.1  | Noise Effect                  | 110 |

|   |     | 5.5.2  | Nonideality Effect            | 115 |

|   |     | 5.5.3  | Block Specification Summary   | 118 |

|   | 5.6 | Conclu | usion                         | 118 |

| 6 | Imp | olemen | tation                        | 121 |

|   | 6.1 | Introd | uction                        | 121 |

|   | 6.2 | Switch | ned-Capacitor High-Filter     | 122 |

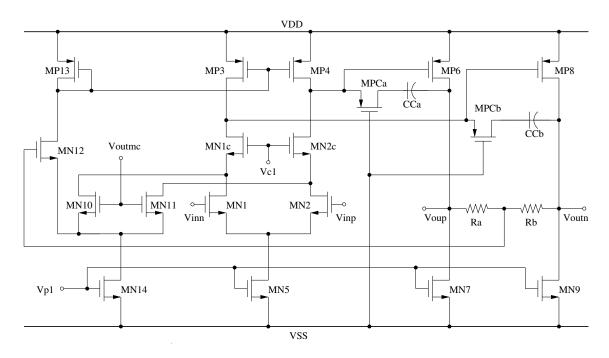

|   | 6.3 | Circui | t Design                      | 123 |

|   |     | 6.3.1  | Operational Amplifier         | 123 |

|   |     | 6.3.2  | Switch                        | 131 |

|   |     |        |                               |     |

|              |     | 6.3.3   | Capacitors                                                       | . 132 |

|--------------|-----|---------|------------------------------------------------------------------|-------|

|              |     | 6.3.4   | Comparator                                                       | . 133 |

|              |     | 6.3.5   | Chopper                                                          | . 135 |

|              |     | 6.3.6   | Clock Generator                                                  | . 137 |

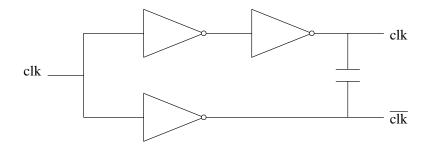

|              |     | 6.3.7   | Clock Buffer                                                     | . 137 |

|              |     | 6.3.8   | Real Inband Noise Effect                                         | . 137 |

|              | 6.4 | Conclu  | ision                                                            | . 141 |

| 7            | Lay | out an  | d Test Setup                                                     | 143   |

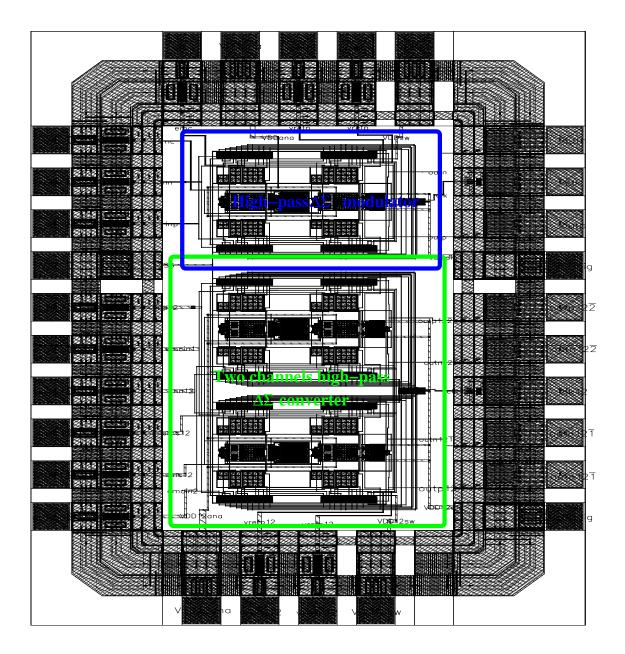

|              | 7.1 | Layou   | t                                                                | . 143 |

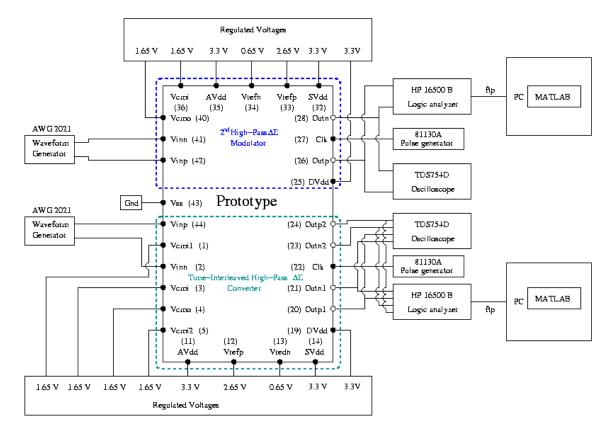

|              | 7.2 | Test S  | $\operatorname{etup}$                                            | . 145 |

| 8            | Con | clusio  | ns                                                               | 147   |

|              | 8.1 | Summ    | ary                                                              | . 147 |

|              | 8.2 | Sugges  | stions                                                           | . 148 |

| A            | Opt | imal F  | ilter of Time-Interleaved $\Delta\Sigma$ Converter               | 153   |

| в            | PDI | F Estir | nation Method and VHDL-AMS Listing                               | 155   |

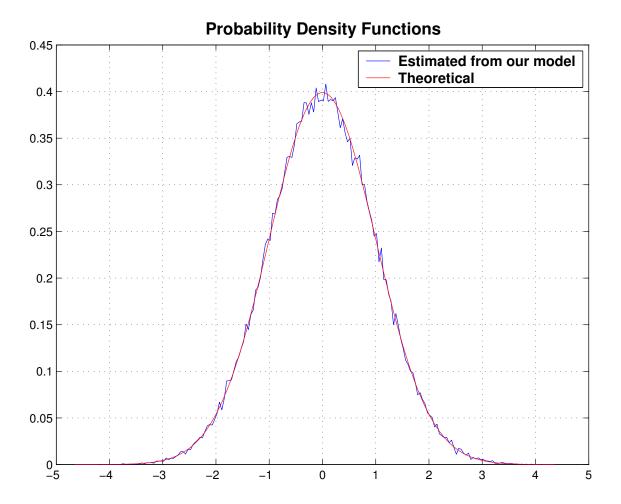

|              | B.1 | PDF e   | estimation method                                                | . 155 |

|              | B.2 | VHDL    | -AMS Listing                                                     | . 156 |

| $\mathbf{C}$ | Rés | umé ét  | tendu                                                            | 161   |

|              | C.1 | Archit  | ecture des CANs                                                  | . 161 |

|              | C.2 | Modul   | ateur $\Sigma\Delta$ passe-haut                                  | . 162 |

|              | C.3 | Conve   | rtisseurs $\Sigma\Delta$ combinant avec l'entrelacement temporel | . 164 |

|              | C.4 | Métho   | dologie de conception avec VHDL-AMS                              | . 166 |

|              | C.5 | Implér  | nentation                                                        | . 168 |

| Bibliog | graphy                                  | 173   |

|---------|-----------------------------------------|-------|

| C.7     | Conclusions                             | . 171 |

| C.6     | Conception des masques et carte de test | 168   |

# List of Figures

| 2.1 | 3-bit flash ADC                                                                                                                                                                                         | 6  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Semi-flash ADC                                                                                                                                                                                          | 8  |

| 2.3 | Successive approximation ADC structure                                                                                                                                                                  | 9  |

| 2.4 | Pipeline ADC structure                                                                                                                                                                                  | 10 |

| 2.5 | Time-interleaved ADC structure.                                                                                                                                                                         | 12 |

| 2.6 | Hybrid filter bank ADC architecture                                                                                                                                                                     | 13 |

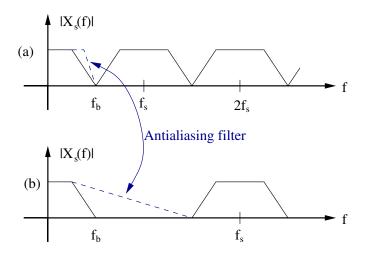

| 3.1 | Conventional pulse code modulation (PCM), including analog an-<br>tialiasing filter for curtaining the aliasing noise in the encoder and<br>for smoothing the output from the decoder.                  | 19 |

| 3.2 | Oversampling pulse code modulation. The modulation and demodu-<br>lation occur at sufficiently high sampling rate that digital filters can<br>provide most for the antialiasing and smoothing functions | 20 |

| 3.3 | An analog signal that has been (a) sampled at the Nyquist rate, and (b) oversampled.                                                                                                                    | 20 |

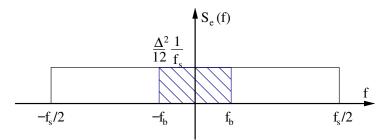

| 3.4 | Power spectral density of quantization noise when the input signal is oversampled                                                                                                                       | 21 |

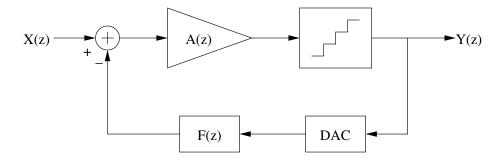

| 3.5 | General structure of a feedback modulator                                                                                                                                                               | 22 |

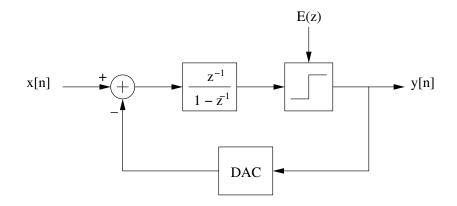

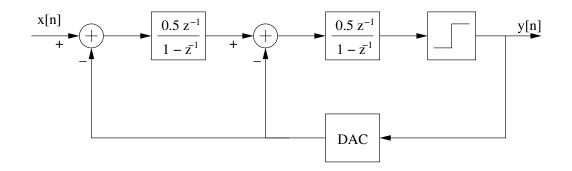

| 3.6 | First-order low-pass $\Delta\Sigma$ modulator                                                                                                                                                           | 25 |

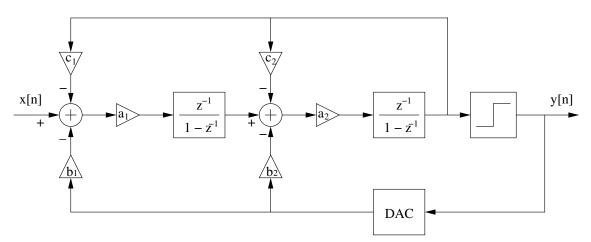

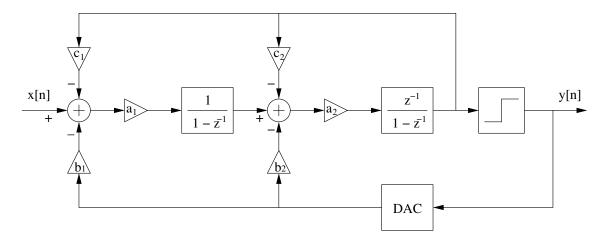

| 3.7 | Second-order low-pass $\Delta\Sigma$ modulator with Boser's structure                                                                                                                                   | 26 |

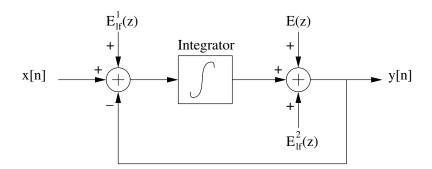

| 3.8 | First-order $\Delta\Sigma$ modulator model with low frequency noise                                                                                                                                     | 28 |

|     |                                                                                                                                                                                                         |    |

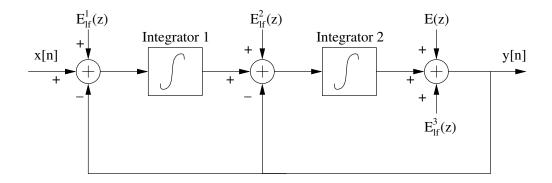

| 3.9  | Second-order $\Delta\Sigma$ modulator model with low frequency noise                                                                                             | 29 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

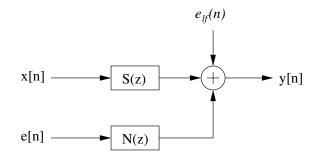

| 3.10 | Conventional $\Delta\Sigma$ modulator model in the presence of the low frequency noise.                                                                          | 29 |

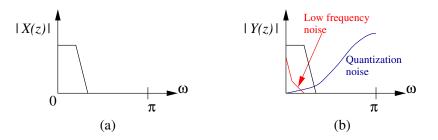

| 3.11 | Spectrum representation of different signals in $\Delta\Sigma$ modulator. (a):<br>input signal; (b): output signal in the presence of the low frequency<br>noise | 30 |

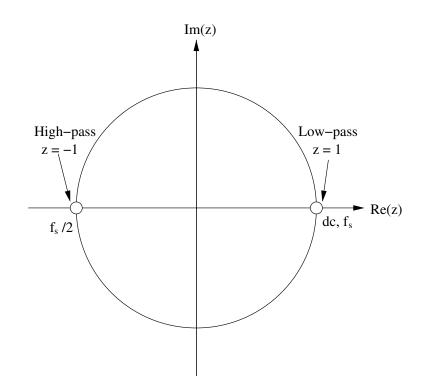

| 3.12 | Locations of zeros of the noise transfer function in the z-plane                                                                                                 | 31 |

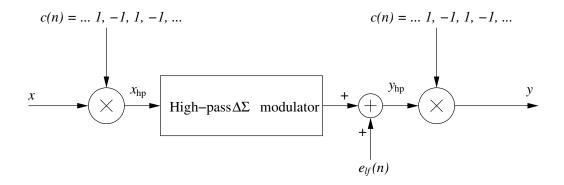

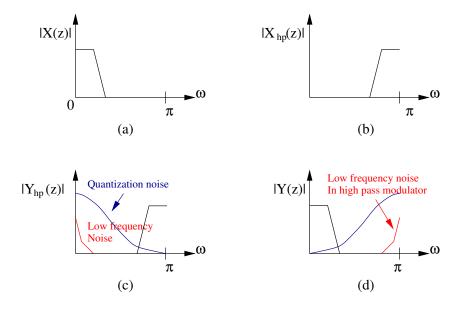

| 3.13 | Chopper stabilized high-pass $\Delta \Sigma$ modulator in the presence of the low frequency noise                                                                | 32 |

| 3.14 | Evolution of the input signal in the frequency domain                                                                                                            | 32 |

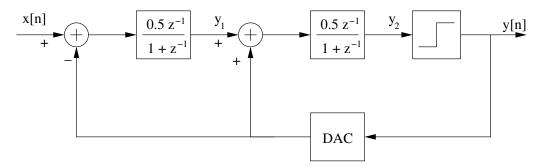

| 3.15 | Second-order high-pass $\Delta \Sigma$ modulator.                                                                                                                | 34 |

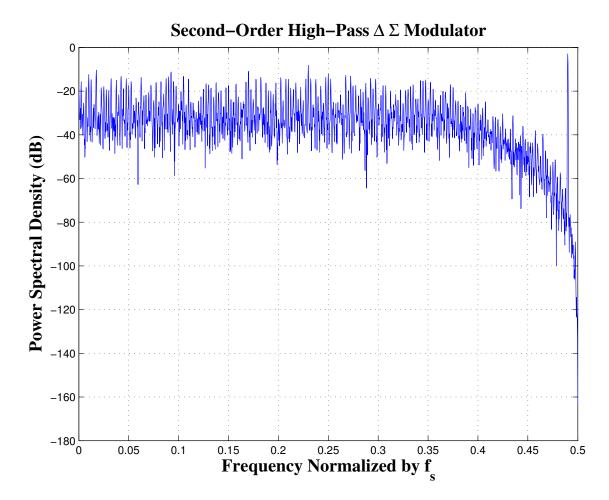

| 3.16 | Undecimated spectrum of digital output signal of second-order high-<br>pass $\Delta\Sigma$ modulator.                                                            | 36 |

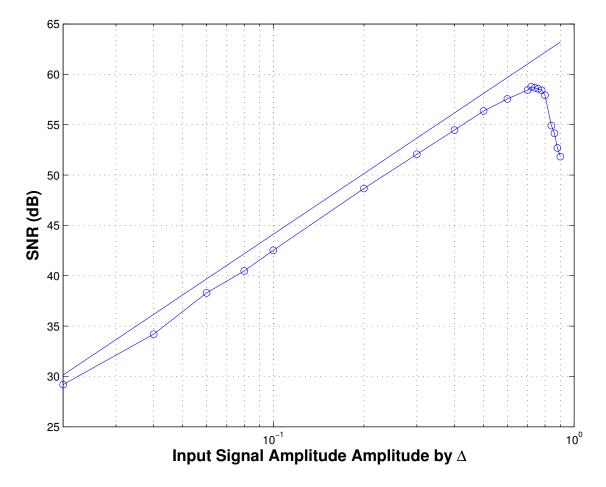

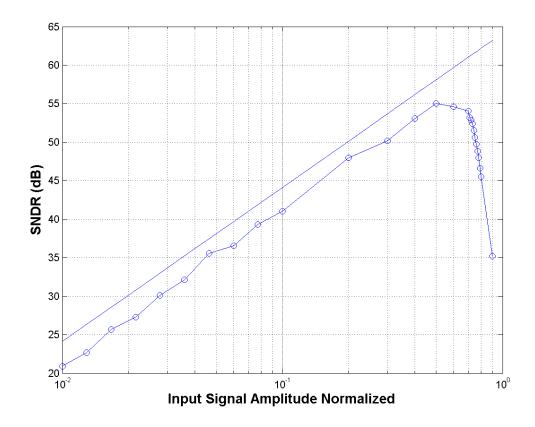

| 3.17 | SNR versus input signal level of the second-order high-pass $\Delta \Sigma$ modulator                                                                            | 37 |

| 3.18 | Output spectrum of the low-pass $\Delta\Sigma$ modulator (a) and output spectrum of the chopper stabilized $\Delta\Sigma$ modulator.                             | 38 |

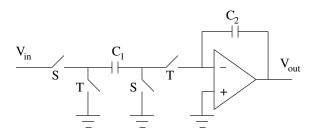

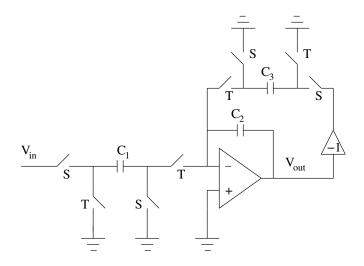

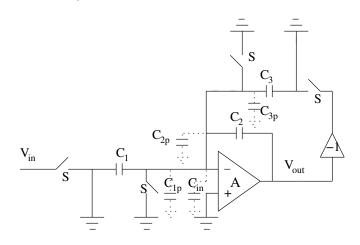

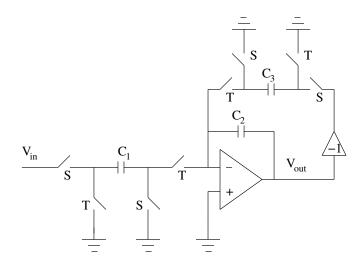

| 3.19 | Parasitic-insensitive non-inverting SC integrator                                                                                                                | 39 |

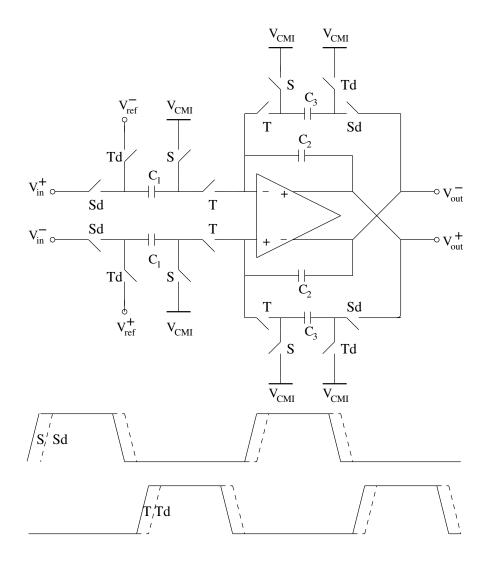

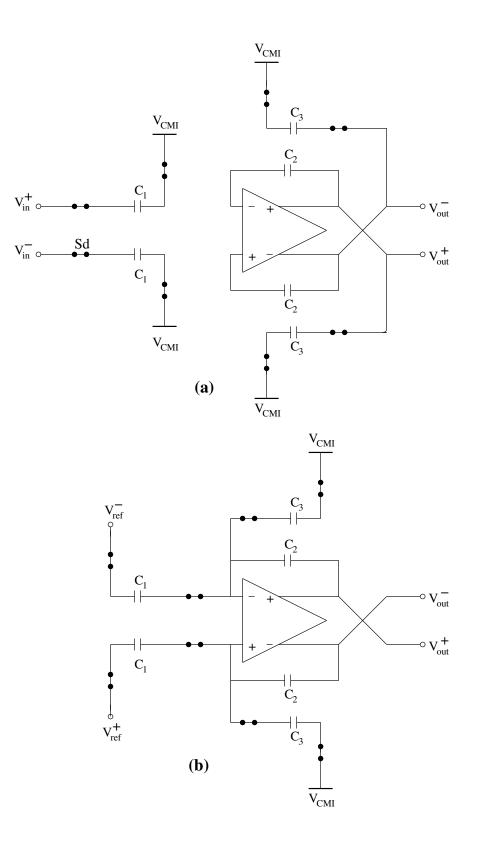

| 3.20 | SC implementation of the high-pass filter                                                                                                                        | 40 |

| 3.21 | SC implementation of the high-pass filter with different parasitic ca-<br>pacitors                                                                               | 40 |

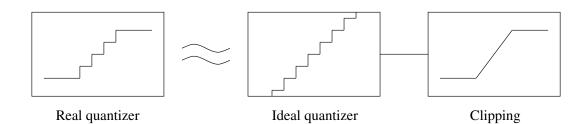

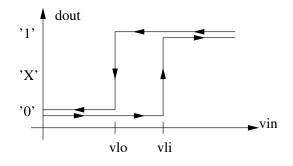

| 3.22 | Real quantizer model                                                                                                                                             | 43 |

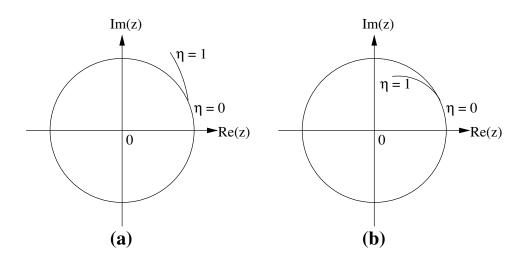

| 3.23 | Locations of poles of the noise transfer function in the z-plane. (a): stable modulator; (b): unstable modulator. $\ldots \ldots \ldots \ldots \ldots$           | 44 |

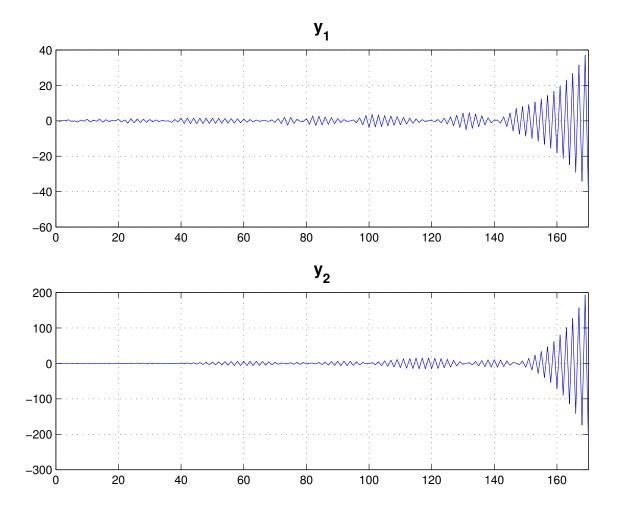

| 3.24 | Divergence of internal states when the modulator is unstable. $y_1$ :<br>output of the first high-pass filter, $y_2$ : output of the second high-pass<br>filter  | 46 |

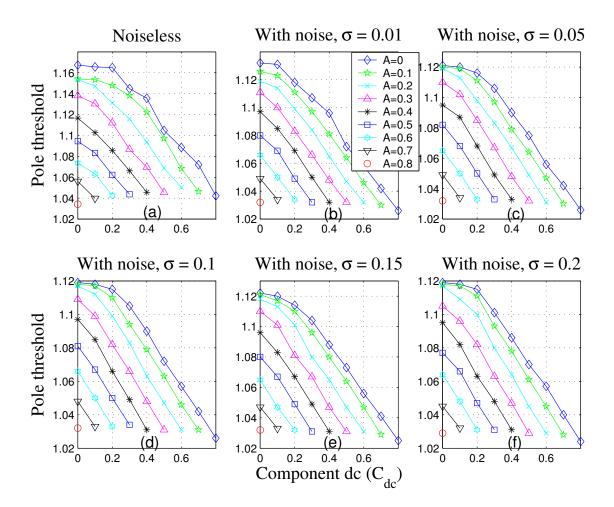

| 3.25 | Threshold of the pole in the high-pass filter assuring the stability of the high-pass $\Delta\Sigma$ modulator.                                                  | 48 |

|      |                                                                                                                                                                  |    |

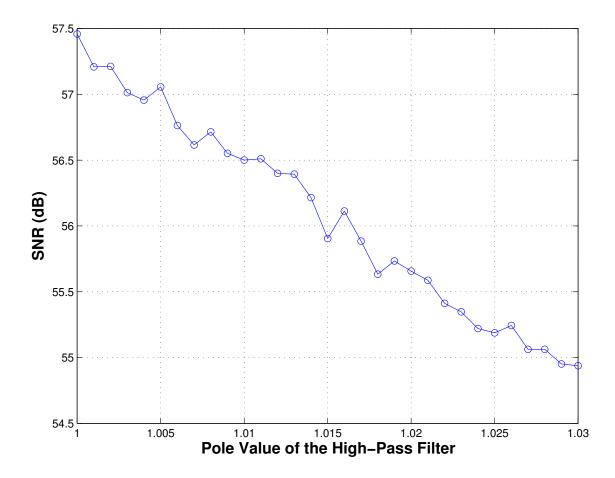

| 3.26 | Signal-to-noise ratio of the second-order high-pass $\Delta\Sigma$ modulator versus the pole of the high-pass filter.                                                                                                                                 | 49 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

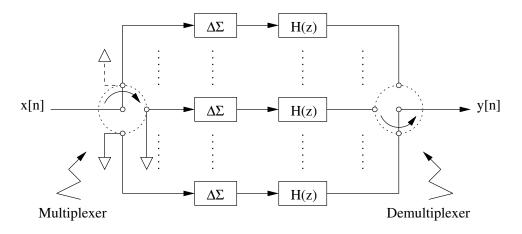

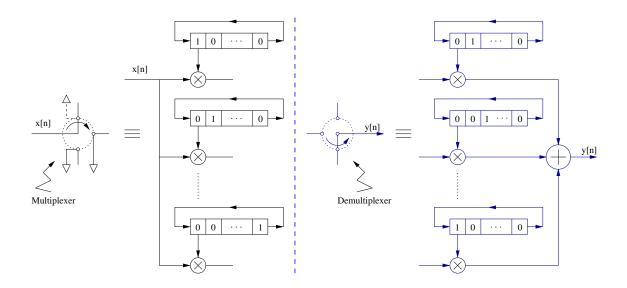

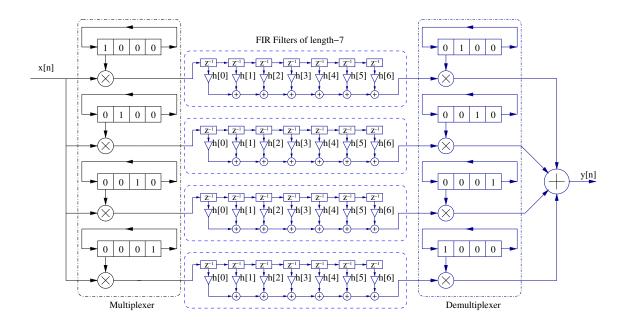

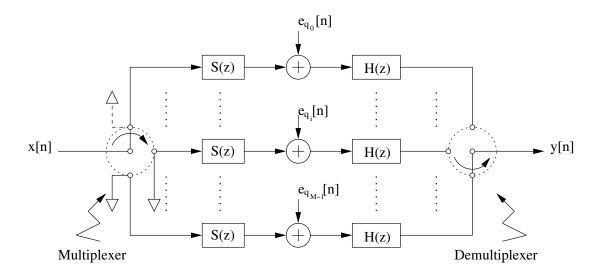

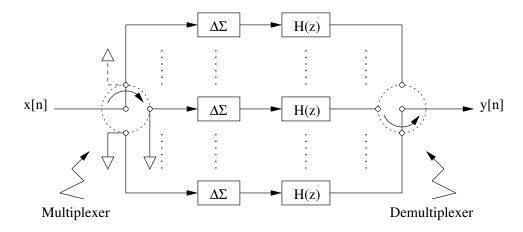

| 4.1  | Architecture of time-interleaved $\Delta\Sigma$ converter                                                                                                                                                                                             | 55 |

| 4.2  | Equivalent multiplication models of the multiplexer and demultiplexer<br>with $M-1$ delays of the demultiplexer relative to the multiplexer in<br>the time-interleaved $\Delta\Sigma$ converter.                                                      | 56 |

| 4.3  | An example of the processing performed by a four channels time-<br>interleaved $\Delta\Sigma$ converter in the absence of quantization error with<br>three delays of the demultiplexer relative to the multiplexer                                    | 57 |

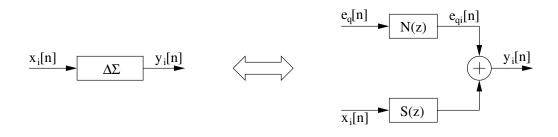

| 4.4  | Linear model of $\Delta\Sigma$ modulator                                                                                                                                                                                                              | 58 |

| 4.5  | The time-interleaved $\Delta\Sigma$ ADC quantization model                                                                                                                                                                                            | 58 |

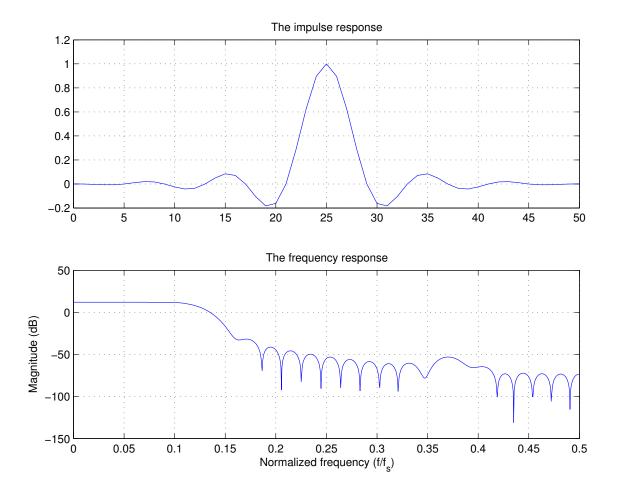

| 4.6  | The impulse response and frequency response of an optimal channel filter for a time-interleaved $\Delta\Sigma$ converter employing four channels of fourth-order $\Delta\Sigma$ modulators.                                                           | 65 |

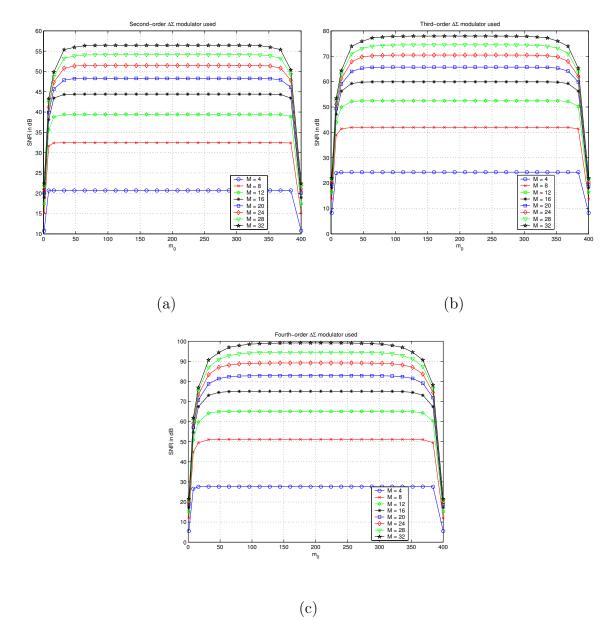

|      | (a)                                                                                                                                                                                                                                                   | 67 |

|      | (b)                                                                                                                                                                                                                                                   | 67 |

|      | (c)                                                                                                                                                                                                                                                   | 67 |

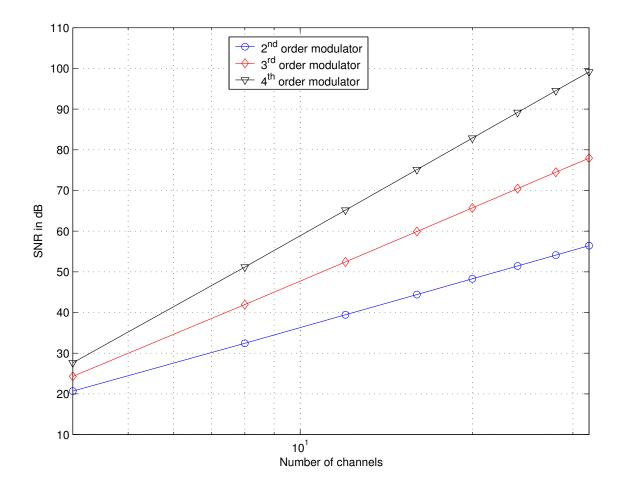

| 4.7  | The ideal DR in dB of the time-interleaved $\Delta\Sigma$ converter versus $m_0$ ,<br>with $M = 4, 8, \dots, 30$ , for (a) second-order, (b) third-order, and (c)<br>fourth-order $\Delta\Sigma$ modulators. The length-401 channel filters are used. | 67 |

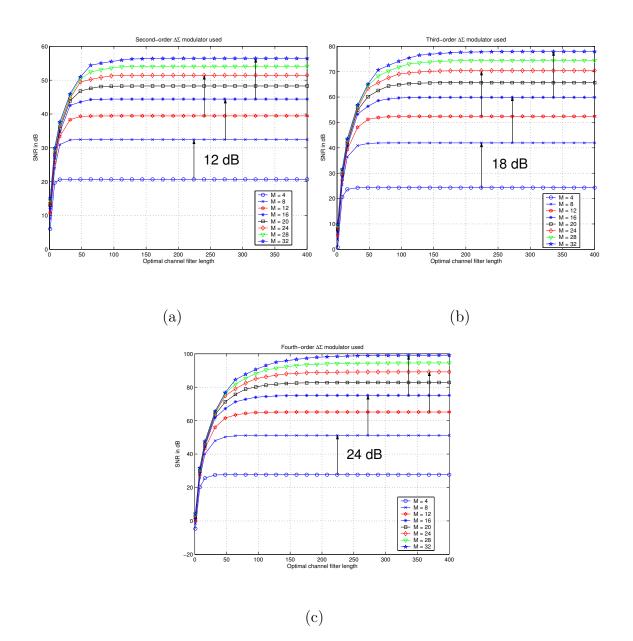

|      | (a)                                                                                                                                                                                                                                                   | 69 |

|      | (b)                                                                                                                                                                                                                                                   | 69 |

|      | (c)                                                                                                                                                                                                                                                   | 69 |

| 4.8  | The ideal DR in dB of the time-interleaved $\Delta\Sigma$ converter versus channel filter length, N, with $M = 4, 8, \dots, 30$ for (a) second-order, (b) third-order, and (c) fourth-order $\Delta\Sigma$ modulators.                                | 69 |

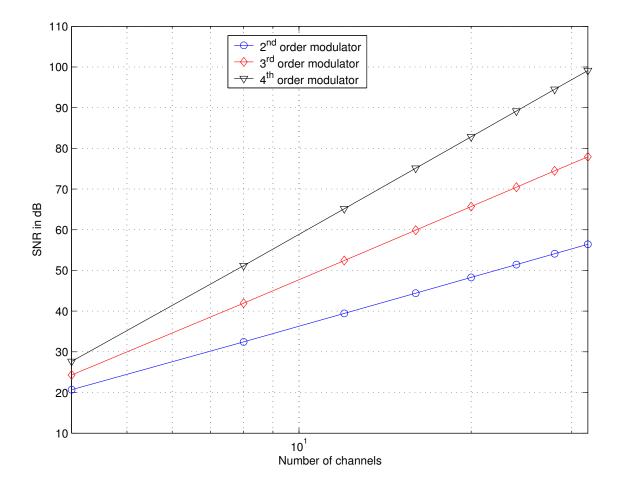

| 4.9  | The ideal DR of the time-interleaved $\Delta\Sigma$ converter for optimal channel filter versus the number of channels on a log scale                                                                                                                 | 70 |

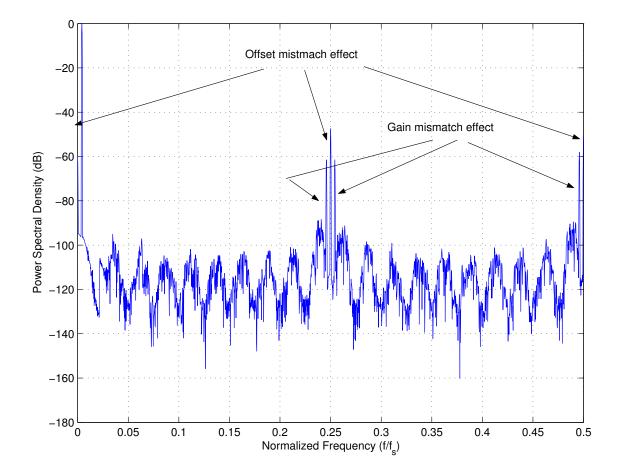

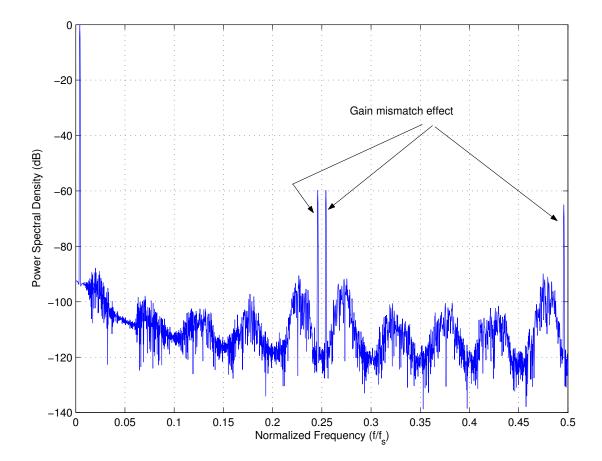

| 4.10 | Output spectrum of time-interleaved fourth-order $\Delta \Sigma$ ADC with four channels in the presence of the channel mismatch.                                                                                                                                                          | 72 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

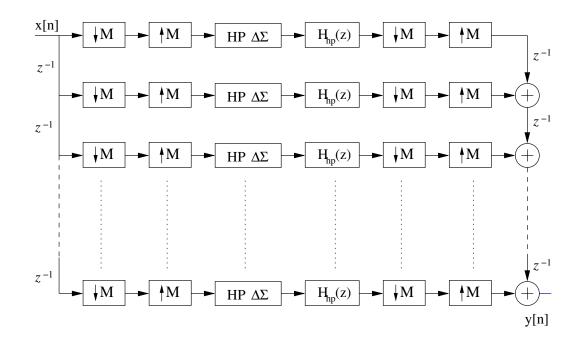

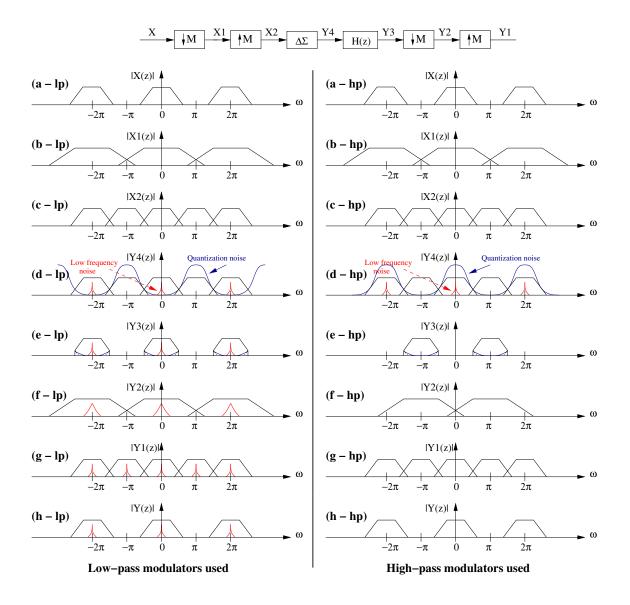

| 4.11 | Diagram of the time-interleaved high-pass $\Delta\Sigma$ ADC. Multi-cadence system presentation.                                                                                                                                                                                          | 74 |

| 4.12 | Frequency domain presentation of time-interleaved $\Delta\Sigma$ ADC                                                                                                                                                                                                                      | 76 |

| 4.13 | Output signal spectrum of the time-interleaved fourth-order high-pass $\Delta\Sigma$ ADC employing four channels in the presence of the channel mismatch.                                                                                                                                 | 78 |

| 4.14 | Interleaved high-pass $\Delta \Sigma$ ADC architecture with adaptive channel gain equalization.                                                                                                                                                                                           | 79 |

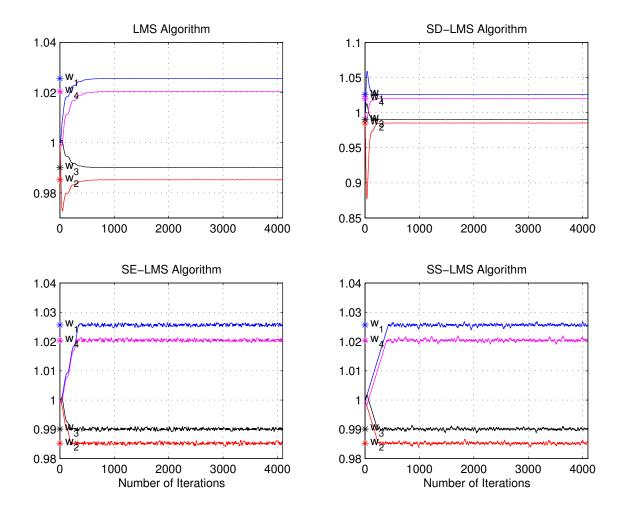

| 4.15 | Magnitude of the weights as they converge to the final value                                                                                                                                                                                                                              | 81 |

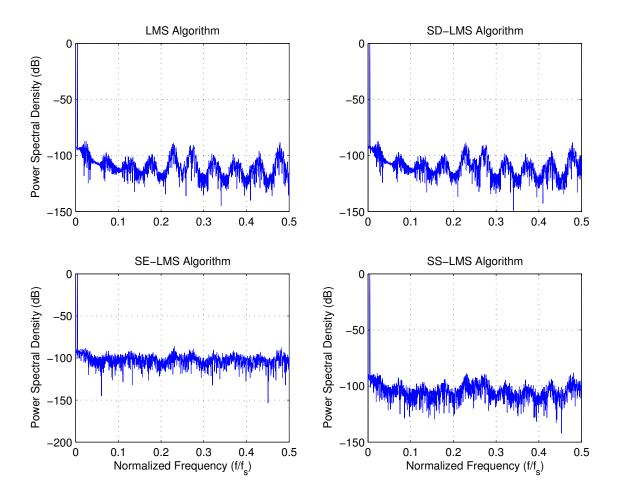

| 4.16 | Output signal spectrum with four algorithms                                                                                                                                                                                                                                               | 82 |

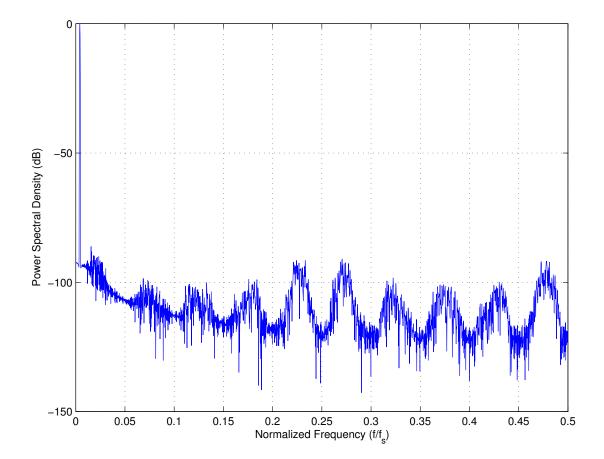

| 4.17 | Output signal spectrum of the time-interleaved high-pass $\Delta\Sigma$ ADC with adaptive channel gain equalization                                                                                                                                                                       | 84 |

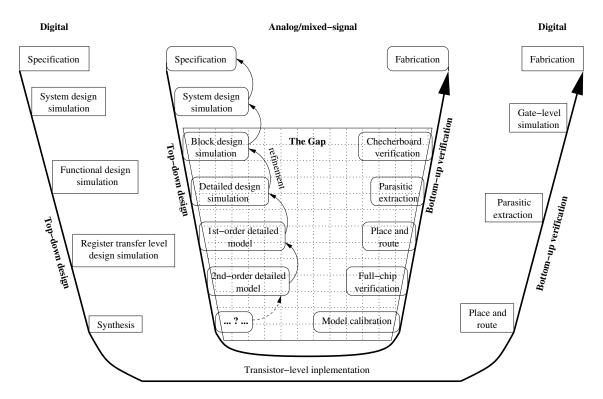

| 5.1  | Design process: the entire digital design process is already fully auto-<br>mated, but analog and mixed-signal design is hindered by the "Gap",<br>which reflects a lack of tool support for the design process between<br>system-level specification and transistor-level implementation | 91 |

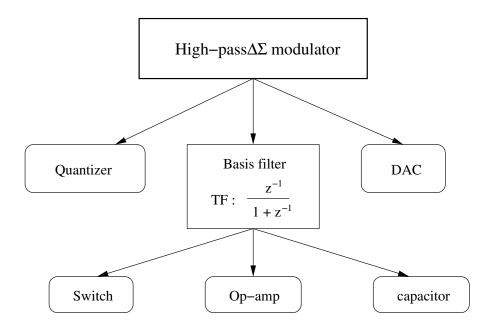

| 5.2  | Elementary blocks building the high-pass $\Delta\Sigma$ modulator using SC techniques                                                                                                                                                                                                     | 94 |

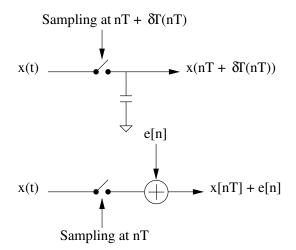

| 5.3  | Discrete model of the sampling process when the sampling time $nT$ is perturbed by a random process $\delta T(t)$ .                                                                                                                                                                       | 95 |

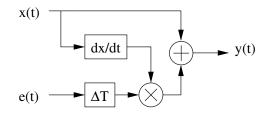

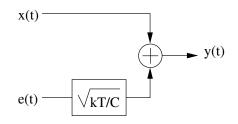

| 5.4  | Model of a random sampling jitter : $x(t)$ is the input signal, $e(t)$ is white noise with mean value, 0, and standard deviation, 1                                                                                                                                                       | 96 |

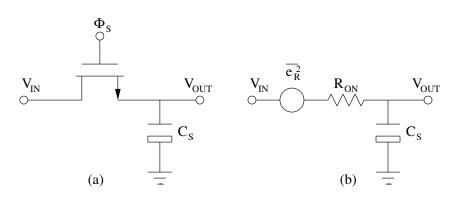

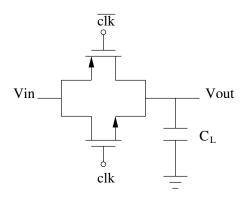

| 5.5  | (a) MOS S/H, and (b) its equivalent noisy circuit when $\Phi_S$ is high                                                                                                                                                                                                                   | 96 |

| 5.6  | Thermal noise model : $x(t)$ is the input signal, $e(t)$ is white noise with mean value, 0, and standard deviation, 1                                                                                                                                                                     | 97 |

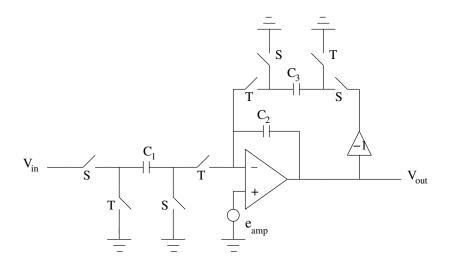

| 5.7  | Non-differential representation of the high-pass filter with an input, $V_{in}$ , and an input-referred amplifier noise source, $e_{amp}$ .                                                                                                                                               | 98 |

| 6.7  | CMOS Switch                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

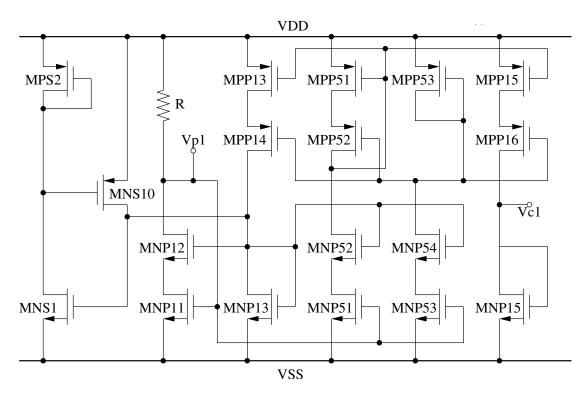

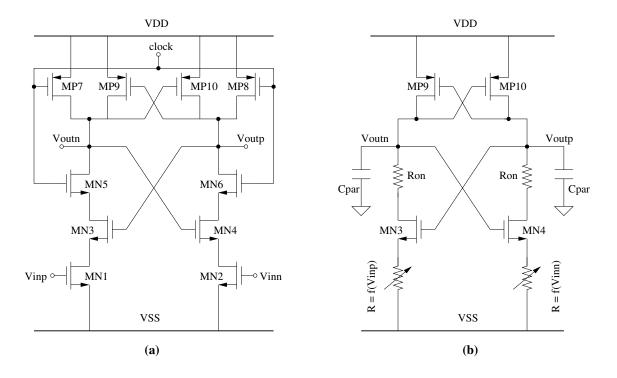

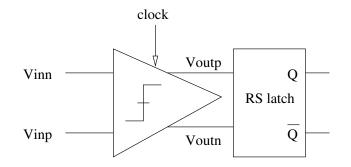

| 6.8  | Dynamic latch used as the comparator core (a) and simplified repre-<br>sentation of the latch in the active phase $(clock = VDD)$ (b) 133                                                               |

| 6.9  | Complete comparator                                                                                                                                                                                     |

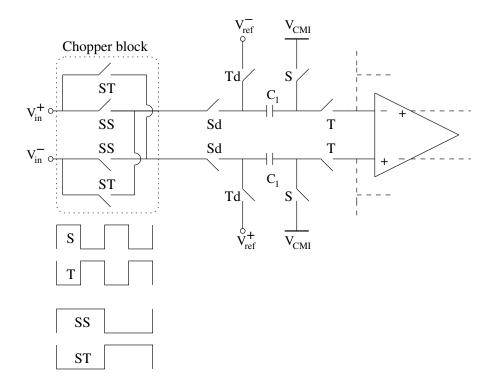

| 6.10 | Implementation of chopper block                                                                                                                                                                         |

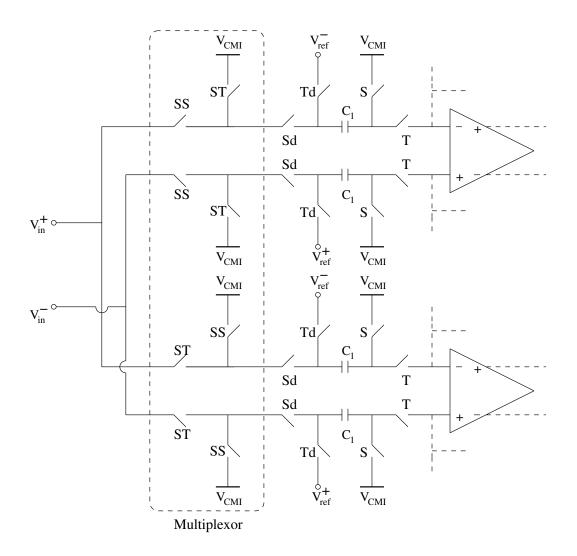

| 6.11 | Implementation of multiplexor                                                                                                                                                                           |

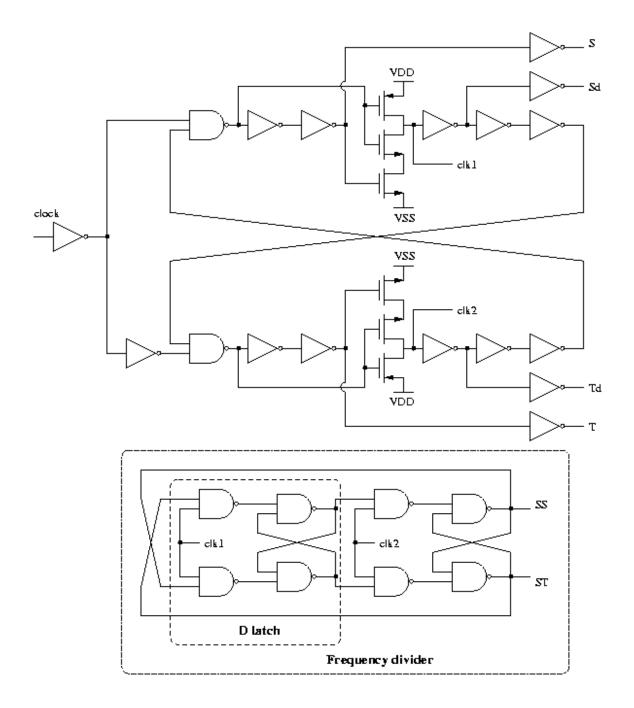

| 6.12 | Clock generator                                                                                                                                                                                         |

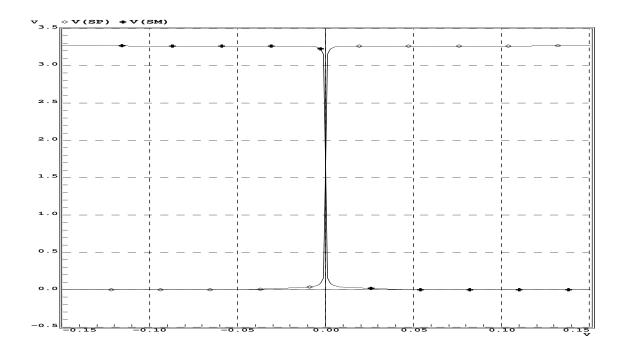

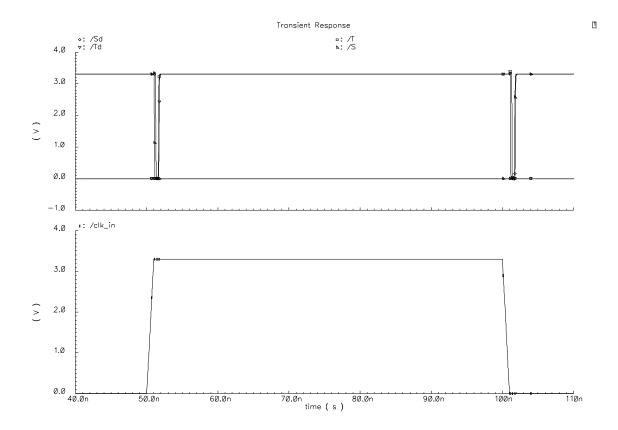

| 6.13 | Clock phases                                                                                                                                                                                            |

| 6.14 | Clock buffer                                                                                                                                                                                            |

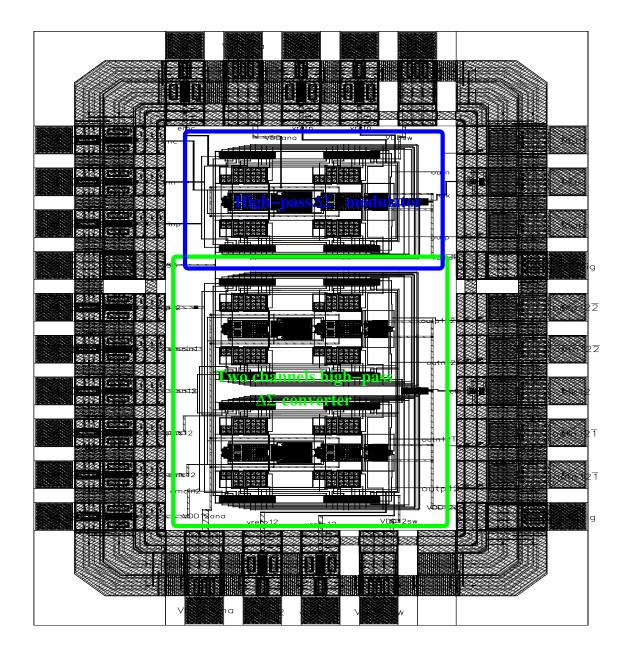

| 7.1  | Layout of the second-order high-pass $\Delta\Sigma$ modulator and a two channels time-interleaved second-order high-pass $\Delta\Sigma$ converter                                                       |

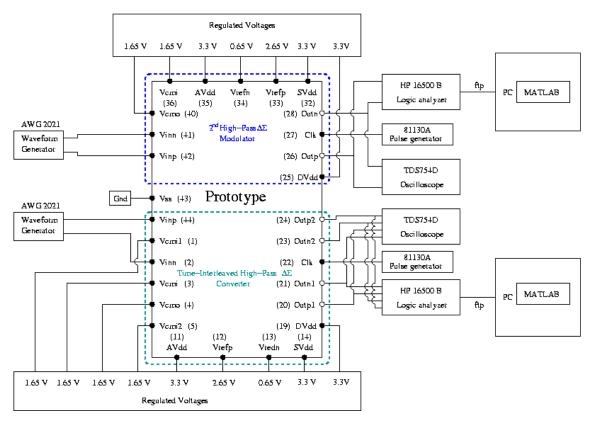

| 7.2  | Diagram of test setup                                                                                                                                                                                   |

| 8.1  | New implementation of second-order high-pass $\Delta\Sigma$ modulator based<br>on Boser's structure of low-pass second-order $\Delta\Sigma$ modulator 149                                               |

| 8.2  | New implementation of second-order high-pass $\Delta\Sigma$ modulator based<br>on classical second-order low-pass $\Delta\Sigma$ modulator                                                              |

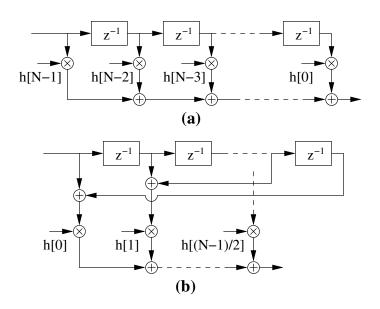

| A.1  | (a) : FIR filter; (b) Symmetric FIR filter                                                                                                                                                              |

| C.1  | Implémentation en capacités commutées du bloc de base du modula-<br>teur $\Sigma\Delta$ passe-haut                                                                                                      |

| C.2  | Architecture du convertisseur $\Sigma\Delta$ en combinant avec l'entrelacement<br>temporel                                                                                                              |

| C.3  | La dynamique idéale du convertisseur $\Sigma\Delta$ en combinant avec l'entrelacement<br>temporel avec des filtres de canal idéaux en fonction du nombre de<br>canaux pour trois modulateurs différents |

| C.4  | Dessin de masque du modulateur $\Sigma\Delta$ passe-haut d'ordre 2 et du convertisseur $\Sigma\Delta$ passe-haut en conbinant avec l'entrelacement temporel. 169                                        |

| C.5 | Diagramme de l | a carte de | test |  |  |  |  |  |  |  |  |  | 17 | 0 |

|-----|----------------|------------|------|--|--|--|--|--|--|--|--|--|----|---|

|     |                |            |      |  |  |  |  |  |  |  |  |  |    |   |

# List of Tables

| 2.1 | Truth table for flash converter in Figure 2.1                                                                                                   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | The minimal filter length of the optimal channel filter allowing to attain an DR equal to the ideal DR minus 1 dB                               |

| 4.2 | Step size value for LMS, SD-LMS, SE-LMS and SS-LMS algorithms 80                                                                                |

| 4.3 | $DR(dB)$ of ADC with different algorithms $\ldots \ldots \ldots \ldots \ldots \ldots 83$                                                        |

| 5.1 | Modelling space covered by VHDL-AMS                                                                                                             |

| 5.2 | Simulation parameters                                                                                                                           |

| 5.3 | Threshold of parameters representing jitter noise, switch noise and amplifier noise                                                             |

| 5.4 | High-pass modulator SNDR performance versus the on-resistance of the switch                                                                     |

| 5.5 | Low-pass modulator SNDR performance versus the static gain and<br>the slew-rate of the amplifier                                                |

| 5.6 | High-pass modulator SNDR performance versus the static gain and<br>the slew-rate of the amplifier. "x" means that the modulator is unstable.117 |

| 5.7 | High-pass modulator SNDR performance versus the transition fre-<br>quency to sampling frequency ratio                                           |

| 5.8 | High-pass $\Delta\Sigma$ modulator SNDR performance versus capacitor mis-<br>match                                                              |

| 5.9 | Specification summary                                                                                                                           |

#### LIST OF TABLES

| 6.1 | Transistor sizes of the operational amplifier                                                                                                                                           |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6.2 | Transistor sizes of the bias circuit                                                                                                                                                    |  |

| 6.3 | Operational amplifier performances                                                                                                                                                      |  |

| 6.4 | Transistor sizes of the dynamic latch                                                                                                                                                   |  |

| 7.1 | Expected performance of the high-pass second-order modulator 146 $$                                                                                                                     |  |

| C.1 | Spécifications des différents paramètres de nonidéalité pour obtenir<br>une performance de moins 3 dB de la performance idéale d'un mod-<br>ulateur $\Sigma\Delta$ passe-haut d'ordre 2 |  |

| C.2 | Performance du modulateur $\Sigma\Delta$ passe-haut d'ordre 2                                                                                                                           |  |

# Listings

| 5.1 | White noise generator in VHDL-AMS                                                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Simple model of switch in VHDL-AMS where only on-resistance and off-resistance are taken into account                                  |

| 5.3 | Simple model of op-amp in VHDL-AMS where only static gain and saturation are taken into account                                        |

| B.1 | Model of switch in VHDL-AMS where on-resistance, off-resistance, parasitic capacitances and leakage current are taken into account 156 |

| B.2 | Model of comparator with hysteresis in VHDL-AMS                                                                                        |

# Abbreviations

|  | ADC                 | Analog-to-Digital Converter                                       |

|--|---------------------|-------------------------------------------------------------------|

|  | DAC                 | Digital-to-Analog Converter                                       |

|  | DEA                 | Differential and Algebraic Equation                               |

|  | $\Delta\Sigma$      | Delta Sigma                                                       |

|  | DR                  | Dynamic Range                                                     |

|  | DSPF                | Detailed Standard Parasitics File                                 |

|  | DUT                 | Device Under Test                                                 |

|  | FIR                 | Finite Impulse Response                                           |

|  | HDL                 | Hardware Description Language                                     |

|  | IIR                 | Infinite Impulse Response                                         |

|  | LMS                 | Least Mean Square                                                 |

|  | LTI                 | Linear Time Invariant                                             |

|  | OCEANE              | Outils pour la Conception et l'Enseignement des circuits intégrés |

|  | OCEANE              | ANalogiquEs                                                       |

|  | Op-amp              | Operational amplifier                                             |

|  | OSR                 | Oversampling ratio                                                |

|  | PDF                 | Probability Density Function                                      |

|  | $\Pi \Delta \Sigma$ | Pi Delta Sigma                                                    |

|  | $\mathbf{SC}$       | Switched-Capacitor                                                |

|  | SDL                 | Schematic Driven Layout                                           |

|  | SD-LMS              | Sign-Data Least Mean Square                                       |

|  | SE-LMS              | Sign-Error Least Mean Square                                      |

|  | SFDR                | Spurious Free Dynamic Range                                       |

|  | S/H                 | Sample-and-Hold                                                   |

|  |                     |                                                                   |

| SNDR     | Signal-to-Noise and Distortion Ratio                     |

|----------|----------------------------------------------------------|

| SNR      | Signal-to-Noise Ratio                                    |

| SS-LMS   | Sign-Sign Least Mean Square                              |

| VHDL     | Very high speed integrated circuits Hardware Description |

| VIIDL    | Language                                                 |

| VHDL-AMS | VHDL-Analog and Mixed-Signal                             |

| VLSI     | Very Large Scale Integration                             |

## Chapter 1

# Introduction

## **1.1** Motivations and Objectives

Analog-to-Digital Converters (ADC) are key components in almost all modern communication systems. High speed and high resolution ADCs are required in many applications, such as advanced radar systems, multi-beam adaptive digital beamforming array transceivers, smart radios for wireless communications, anti-jam global positioning system receivers, wide-bandwidth modems, and software radios.

Nowadays, there exist a lot of techniques that allow a very high precision conversion, such as the analog-to-digital conversion based on the delta-sigma ( $\Delta\Sigma$ ) modulation and oversampling [1]. However, the process of converting the analog signal to a digital one often limits the overall system speed. In contrast, there are other techniques that provide a very high speed conversion but have just an average or even low resolution, such as flash converter or time-interleaved converter.

Associating the high speed and the high resolution in one ADC has been long time a tough challenge in the research of analog-to-digital conversion techniques. Conventionally, one seeks to improve one of these two properties while trying to keep the other. Recently, a number of research teams [2, 3, 4] have involved in exploiting the  $\Delta\Sigma$  ADC for converters that provide both high speed and high resolution. It is not an easy task and so far the result has not been very satisfying. The converters investigated are the  $\Pi\Delta\Sigma$  [3] and the time-interleaved  $\Delta\Sigma$  [4]. But as in any parallel architecture, these two suffer from the channel mismatch. In this work, we will attempt to improve the efficiency of parallel  $\Delta\Sigma$  converter, especially by minimizing the effect of channel mismatch.

Theoretical study of parallel  $\Delta\Sigma$  converters during the first years of this research reveals that the high-pass  $\Delta\Sigma$  modulator has good potential to eliminate efficiently the channel offset, especially in time-interleaved  $\Delta\Sigma$  converters. It follows that a simple digital channel equalization technique would minimize effectively the channel gain mismatch effect.

At this stage, the high-pass  $\Delta\Sigma$  modulator must be deeply investigated.

The principle of  $\Delta\Sigma$  modulation was discovered long time ago and during the last ten years the converters based on this principle have become very popular. However, this popularity does not concern the "high-pass  $\Delta\Sigma$  modulator". The reason may lie in its difficult implementation and the uncertainty about its stability and performance in the presence of circuit nonidealities.

Persuaded by its potentials, our research is focused on the high-pass  $\Delta\Sigma$  modulator. Our objectives consist of studying its principle, its performance and stability, and then comparing it to low-pass modulators to show out its superiority.

To fulfil these objectives, our task consists of implementing the high-pass  $\Delta\Sigma$  modulator and analyzing the circuit nonideality effect on its performance.

## 1.2 Organization

This dissertation is organized into eight chapters, including this introduction. The next chapter briefly reviews some of the prominent architectures of ADC, their principle of operation, advantages and drawbacks and their field of application.

Chapter 3 presents the high-pass delta sigma ( $\Delta\Sigma$ ) modulator. Its advantages and drawbacks compared to those of the low-pass one are made obvious. An switched-capacitor (SC) implementation of the building block of high-pass  $\Delta\Sigma$  modulator, referred to as high-pass filter, is studied. The stability of the high-pass modulator is also investigated. Critical parameters ensuring the modulator stability are demonstrated.

Chapter 4 is devoted to the time-interleaved  $\Delta\Sigma$  converter. The advantage of using high-pass  $\Delta\Sigma$  modulators in such an architecture, is demonstrated. A dig-

ital channel equalization technique minimizing the effect of channel mismatch, is proposed.

Chapter 5 presents a top-down design methodology with VHDL-AMS, the modelling, determination of nonideality effect and simulation of  $\Delta\Sigma$  modulator in VHDL-AMS.

Chapter 6 proposes an implementation example of a second-order high-pass  $\Delta\Sigma$  modulator and a two channels time-interleaved second-order high-pass  $\Delta\Sigma$  converter in a 0.35  $\mu$ m CMOS process.

Chapter 7 presents the layout of the prototype, the test setup and the expected performance of the high-pass modulator.

Finally, Chapter 8 concludes the dissertation with a summary of results as well as suggestions for further exploration.

## Chapter 2

# Analog-to-Digital Converter Architectures

## 2.1 Introduction

A lot of research has been done on the implementation of ADCs. Many techniques for doing analog-to-digital conversion have been developed. In this chapter, some of the prominent architectural styles are presented and compared. Each architecture has its advantages and disadvantages, and each one has a set of applications for which it is the best solution.

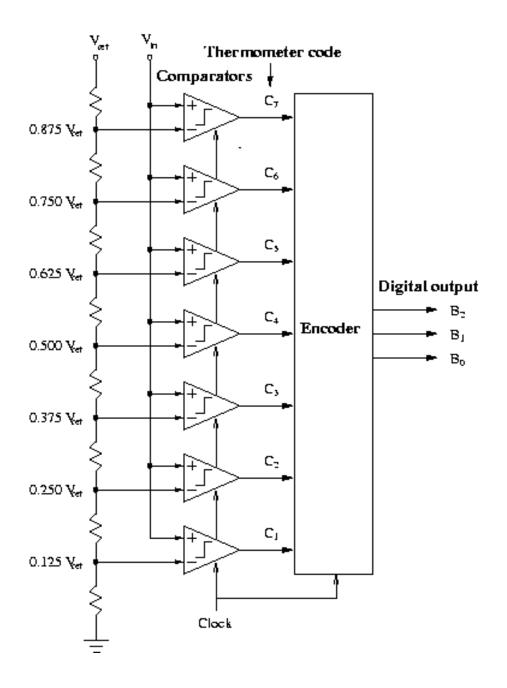

## 2.2 Flash Converter

The flash converter [5, 6, 7, 8, 9, 10, 11], also known as fully parallel architecture, is fundamentally the fastest architecture. It is also conceptually the easiest to understand. An *n*-bit flash ADC consists of an array of  $2^n - 1$  comparators and a set of  $2^n - 1$  reference values. The set of reference values is generally generated from a resistor string and a reference source,  $V_{ref}$ . Each comparator samples the input signal and compares the signal to one of the reference values. It then generates an output indicating whether the input signal is larger or smaller than the reference assigned to itself. The set of  $2^n - 1$  comparator outputs that results is often referred to as a thermometer code. This name is derived from the fact that if the comparator outputs are listed in a column and ordered according to the reference

Figure 2.1: 3-bit flash ADC

values associated with the comparator that produced them, the ones would all be at the bottom, and the zeros all at the top as shown in Table 2.1. The level of the boundary between ones and zeros would indicate the value of the signal, much as the level of mercury in a mercury thermometer indicates the temperature.

A simple 3-bit flash ADC is shown in Figure 2.1. The encoder converts the thermometer code produced by the comparators to a binary code as shown in the truth table in Table 2.1. As seen from the figure, the comparators all operate in parallel. Thus, the conversion speed is limited only by the speed of the comparator or the sampler. For this reason, the flash ADC is capable of high speed.

The two primary drawbacks of the flash ADC are the large hardware requirement and the sensitivity to comparator offsets. As mentioned above,  $2^n - 1$  comparators are required. For this reason, a high resolution flash ADC requires a large circuit area and dissipates high power. The required comparator offset voltage for a flash ADC with *n* bit resolution is less than  $1/2^n$  relative to the reference voltage value. At high resolutions, this required comparator offset becomes very small. Because comparators with small offsets are difficult to design and expensive to build and because so many comparators are required, ADCs with resolutions higher than 8-bit rarely use the flash architecture.

|                                         | $C_7$ | $C_6$ | $C_5$ | $C_4$ | $C_3$ | $C_2$ | $C_1$ | $B_2$ | $B_1$ | $B_0$ |

|-----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| $V_{in} < 0,125 V_{ref}$                | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| $0.125V_{ref} < V_{in} < 0,25V_{ref}$   | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 1     |

| $0.25V_{ref} < V_{in} < 0,375V_{ref}$   | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | 1     | 0     |

| $0.375 V_{ref} < V_{in} < 0,50 V_{ref}$ | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 1     | 1     |

| $0.50V_{ref} < V_{in} < 0,625V_{ref}$   | 0     | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 0     | 0     |

| $0.625 V_{ref} < V_{in} < 0,75 V_{ref}$ | 0     | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     |

| $0.75V_{ref} < V_{in} < 0.875V_{ref}$   | 0     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     |

| $0.875 V_{ref} < V_{in}$                | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

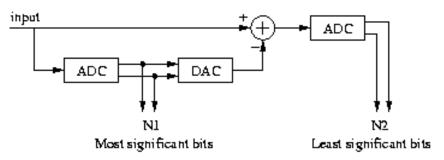

Table 2.1: Truth table for flash converter in Figure 2.1

To decrease hardware requirement, i.e. to reduce the number of comparators, two-step flash architecture, also known as semi-flash architecture, can be used. A two-step flash ADC [12, 13, 14, 15, 16] as shown in Figure 2.2 consists of two stages, each containing a flash ADC. In this type of ADC, the conversion does not happen all at once as in the flash ADC. Here, the conversion takes, as indicated in its name, two steps. During the first one, the most significant bits of the digital output are determined by the first stage flash ADC. Then a DAC converts this digital result back to an analog signal to be subtracted from the input signal. This residue is then sent to the second stage flash ADC which determines the least significant bits of the digital output. The conversion time for a two-step flash ADC is longer than for a simple flash, but it is still very fast. Furthermore, the two-step flash ADC requires only  $2 \times 2^{n/2}$  comparators. Thus, it saves hardware. As a result, two-step flash ADCs are often used in the 10-bit resolution range.

Figure 2.2: Semi-flash ADC

The folding ADC architecture [17, 18, 19, 20, 21] is a popular subset of the two-step flash architecture. In this architecture, the DAC and differencing blocks are replaced by an analog preprocessing circuit called a folding circuit. The folding circuit has a triangular input-output characteristic. The output of this block can be used as the input to a fine ADC that determines the least significant bits of the digital output.

Decreasing even more the hardware requirement is the goal of subranging architecture. A subranging ADC [22, 23, 24, 25, 26, 27, 28, 29] is a multi-step converter architecture that includes two-step flash ADCs and other ADCs that extend the concept of the two-step flash ADC to a larger number of steps. By breaking the conversion process into multiple steps, fewer comparators are required at the cost of the longer conversion time. Each stage is responsible for resolving some part of the digital output word and delivering a residue to the following stage. The conversion time required increases while the hardware required decreases with the number of stages. Thus, there is a trade-off between speed and hardware. The comparators in the front stages need not be very accurate, but the comparators in the last stage must be accurate to the full resolution of the ADC. From their principle, the flash converters are limited to 6- or 8-bit, which is insufficient for instrumentation. This handicap is negligible in digital oscilloscopy: certain manufacturers use 6-bit converters, which are enough to describe the vertical axis of screen with a resolution higher than 2%. They are also used for DVD and hard disks readers. For the applications requiring high but not extreme speeds, we can use semi-flash or multi-step converters, which use much less comparators and preserve an interesting speed of conversion, with a resolution capable to reach 12-bit.

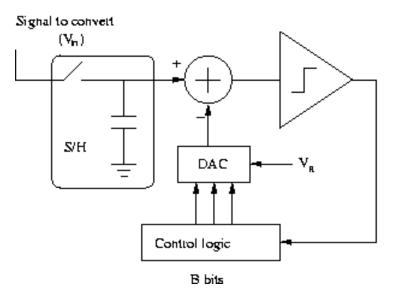

### 2.3 Successive Approximation ADC

Figure 2.3: Successive approximation ADC structure

A successive approximation ADC [30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 50, 51, 52], also known as a binary search ADC, is a special type of subranging ADC that uses a DAC to produce an analog signal that approximates the input sample. By adjusting the DAC until its output matches the input sample, a digital code representing the analog input can be generated. A successive approximation ADC consists of only one stage containing a S/H, an ADC, a DAC, and a digital processor that controls the DAC. An example of a successive approximation ADC is shown in the block diagram in Figure 2.3. In this example, the ADC consists of a single comparator. The operation of the successive approximation ADC is as follows. The control logic is initialized, and this initializes the output of the DAC. A sample of the input signal is taken by the S/H circuit,

and the initial DAC output is subtracted from the input sample. The difference is quantized by the comparator which instructs the control logic to either increase or decrease the DAC output. The new DAC output is again subtracted from the input sample, and the process repeats until the desired accuracy is obtained. This single comparator successive approximation ADC resolves one bit per cycle.

The advantage of this converter is a very little hardware requirement. Without considering the S/H, no amplifier is required, and only a single comparator is needed. By calibrating or trimming the DAC, very high resolution can be obtained. But its disadvantage is that the number of cycles required per sample is proportional to the number of bits. Therefore, this converter architecture is slower than a flash.

Concerning their applications, these components are very popular, from digital audio to data acquisition card and also in micro controllers.

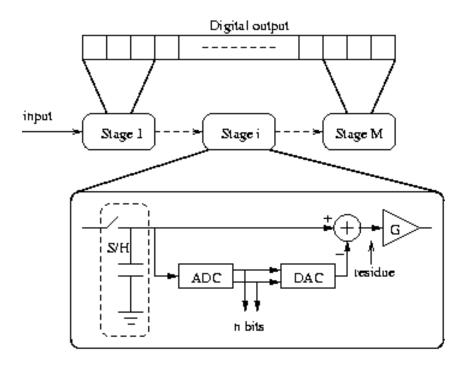

### 2.4 Pipeline Converter

Figure 2.4: Pipeline ADC structure

A pipelined ADC [53, 54, 55, 56, 57, 58, 59, 60, 61, 62, 63, 64, 65, 66, 67, 68, 69] is another type of subranging ADC which improves the throughput rate and tolerance to comparator errors. The block diagram in Figure 2.4 shows its structure. The pipelined ADC is similar to the subranging ADC with the exception that a sampleand-hold (S/H) circuit and amplifier has been added to each stage. The S/H circuit is used by the first stage to sample the input. Subsequent stages use a S/H circuit to sample the residue from the previous stage. This feature allows each stage of the pipeline to begin processing a new sample as soon as its residue is sampled by the following stage. Thus, the throughput rate is independent of the number of stages in the pipeline. Because of this feature, pipelined ADCs can generally operate at much higher sampling rates than other subranging ADCs.

Although the throughput rate is independent of the number of stages in the pipeline, conversion time for any given sample is proportional to the number of stages in the pipeline. This is because the signal must work its way through all of the stages before the complete output word is generated. This delay can be an issue if the pipelined ADC is part of a feedback system.

The amplifier is used to amplify the residue before passing it on to the next stage. By doing this, the resolution requirements for the following stages are relaxed. One significant implication of this is that the comparators in the last stages of the pipeline need not be accurate to the full ADC resolution as they are required to be in other subranging ADCs.

The disadvantage of adding the gain blocks is that they tend to be the dominant source of power dissipation in the ADC. Therefore, pipelined ADCs tend to dissipate more power than subranging ADCs. But like the other subranging ADCs, pipelined ADCs can achieve high resolutions with relatively little hardware. Furthermore, mismatches can be eliminated by self-calibration techniques.

In raison of their tolerance to comparator offsets and the ability of the pipeline stages to operate in parallel, pipelined ADCs are well suited for high resolution applications where high speed is required.

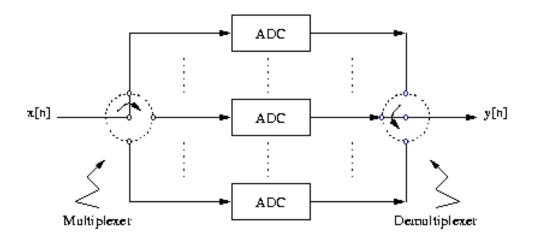

#### 2.5 Time-Interleaved ADC

When even higher conversion speed is desired, parallelism can be applied. Figure 2.5 shows a system view of the architecture for parallel pipeline ADC. The parallelism has been initially used with Nyquist converter [70, 71, 72, 73, 74, 75, 76, 77]. This

technique consists of implementing identical ADCs in parallel and then activating ADCs one by one with some delays. If N channels are used, each channel is operated at frequency of  $f_s/N$ , where  $f_s$  is the system overall sampling frequency. A multiplexer and a demultiplexer are used at the input and the output of the system. This way, throughput of the system is increased by N times at the cost of increasing hardware. Since a DAC reference can be shared by all the channels, the hardware requirement increases less than the first order linear dependence. Sharing DAC reference is also desired to improve the matching of the channels.

Figure 2.5: Time-interleaved ADC structure.

The most critical problem that needs to be solved in parallel structure is how to improve the matching between channels. This directly affects the highest resolution we can achieve [78, 79]. Calibration techniques have been investigated to minimize the effect of channel mismatch [71, 79, 80, 81, 82, 83]. Another problem of this kind of converter is the clock jitter which modifies both the overall quantization noise and signal. To solve this problem, an additional sampler operating at N times higher than the others, can be used as shown in [84].

The throughput rate of time-interleaved converter can reach some gigasamples per second. However, the resolution is very limited. It cannot exceed 8-bit. The time-interleaved converter is thus used in the very high speed applications, for example digital oscilloscopy.

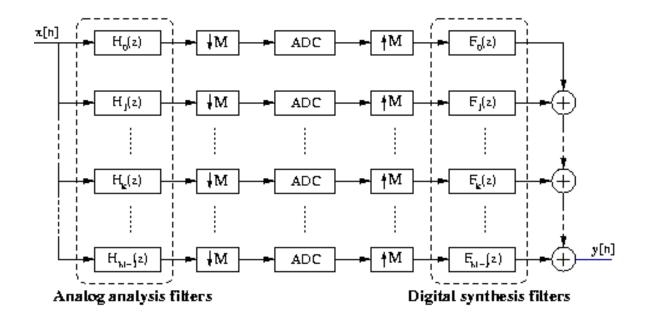

Figure 2.6: Hybrid filter bank ADC architecture.

#### 2.6 Hybrid Filter Bank ADC

Using a hybrid filter bank for ADC is an unconventional application of the hybrid filter bank architecture that improves the speed and resolution of the conversion over the standard time-interleaved conversion technique [2, 85, 86, 87]. Hybrid filter bank ADC uses analog analysis filter to allocate a frequency band to each ADC in the array and digital synthesis filter to reconstruct the digitized signal as shown in Figure 2.6. The time-interleaved ADC architecture is just a particular case of the hybrid filter bank ADC architecture where analog analysis and digital synthesis filters are replaced with delays. The hybrid filter bank ADC significantly improves the speed and resolution of the conversion by attenuating the effect of the mismatches between the converters in array, which otherwise severely limit the resolution of the system. This advantage raises from the isolation of the converters in array from each other, what the time-interleaved system cannot do. The hybrid filter bank is expected to provide analog-to-digital conversion with resolution between 10 and 14-bit at a speed from 50 to 300 megasamples per second [86, 87].

However this kind of converter has some drawbacks. The major one is the complexity of the analog analysis filters. A particular strategy must be found to avoid high-order filter. Algorithms of iterative design to calculate successively the filter transfer function could be considered [86, 87]. The jitter problem is a delicate one and must be investigated more deeply.

Applications of high speed, high resolution ADC include direct digital receivers for wireless communications application, radar receivers, test equipment such as oscilloscopes, spectrum analyzers, networks analyzers, digital and pattern generators, modem and medical imaging systems.

### **2.7** $\Delta\Sigma$ Converter

Currently, the analog-to-digital conversion using oversampling and  $\Delta\Sigma$  modulation techniques [1, 88, 89, 90], provides the highest resolution ADCs. The operation of this kind of converter is based on a  $\Delta\Sigma$  modulator which repeatedly samples the input and performs a few bits quantization of the error between the signal and its estimate. By sampling the signal many times, errors due to the coarse quantization and noise are averaged out. The quantized data is then digitally post filtered and decimated to attenuate the quantization noise power under the desired level. While the performance of the converters, in terms of resolution and speed, is primarily determined by the analogical modulator, the filter of decimation determines surface and consumption. A more detailed overview of conventional  $\Delta\Sigma$  modulator and an investigation of high-pass  $\Delta\Sigma$  modulator will be presented in Chapter 3.

In parallel with analog-to-digital conversion, other applications of the  $\Delta\Sigma$  modulation have been developed. Realizing the modulator thanks to a digital stage, and filtering the resulting signal by an analog low-pass filter, carry out a DAC having performance as good as that of the best conventional DAC [91, 92]. Other operations can be realized thanks to the  $\Delta\Sigma$  modulation [93]. For example, we can produce FIR [56, 94] or IIR [95] filters without multiplier, adaptive filters [96], amplitude modulator [97] or PLL [98].

A major drawback of  $\Delta\Sigma$  ADC is its limited conversion bandwidth. This is because of oversampling requirement. Recently,  $\Delta\Sigma$  ADC with low sampling ratio that uses conventional  $\Delta\Sigma$  ADCs in parallel to extend the conversion bandwidth of the overall ADC, was introduced [3, 4]. A time-interleaved  $\Delta\Sigma$  converter is a particular case of the parallel  $\Delta\Sigma$  converter. As any parallel architecture, this one suffers from channel mismatch. This problem will be minimized by using highpass  $\Delta\Sigma$  modulators and channel equalization technique. This will be presented in Chapter 4.

## 2.8 Conclusion

Various ADC architectures have been presented. Their principle of operation, advantages and drawbacks, and also their application field have been discussed. All the converters can be gathered into three large families: the flash, the pipeline and the  $\Delta\Sigma$  converters.

The flash converters are certainly the fastest. They can currently reach a speed of some gigasamples per second. However, they have a relatively low precision which does not exceed 8-bit.

The pipeline converters are an intermediate solution between the high speed and high resolution conversion. Thanks to digital calibration techniques, this kind of converter can currently have a relatively high resolution that can reach 14-bit. An advantage of the pipeline converters is that they are able to give a precision at desired sampling frequency, provided that this desired resolution is not very high. Some authors announce that the precision of the pipeline converter can be comparable with that of the  $\Delta\Sigma$  converter thanks to digital calibration.

The  $\Delta\Sigma$  converters are certainly the most precise. They can have a resolution of 24-bit. Apart from high resolution, they have other attractive properties, especially high dynamics, high linearity and low sensitivity to circuit imperfections. The major drawback of these converters is the limited bandwidth because of oversampling. Because of their many interesting properties, much research has been involved in order to increase the passband of the input signal using the  $\Delta\Sigma$  modulation like parallel  $\Delta\Sigma$  converter. But it still remains in the field of research.

Like the parallel  $\Delta\Sigma$  converters, the converters using the hybrid filter bank are promising. But again, they is still in the field of research. Only time-interleaved converter is already industrialized.

## Chapter 3

# High-Pass Delta Sigma Modulator

## 3.1 Introduction

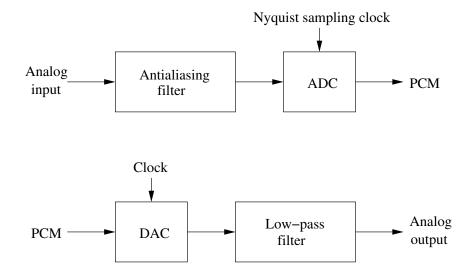

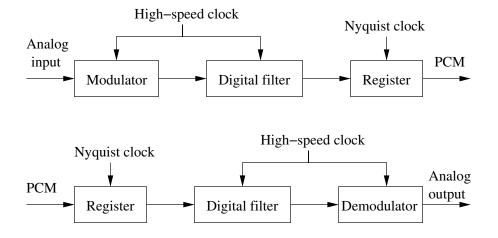

High resolution low cost ADCs have been widely used in the application areas of instrumentation, measurement, telecommunications, digital signal processing, and consumer electronics, etc. Primarily because of advances in Very Large Scale Integration (VLSI) technologies, among different types of ADCs, that based on oversampling and  $\Delta\Sigma$  modulation has become more and more attractive in applications requiring high precise analog-to-digital conversion with narrow bandwidth [1, 88, 89, 90]. Their popularity derives from their reduced analog processing and relaxed sensitivity to analog circuit errors in comparison with other analog-to-digital conversion approaches. These advantages come at the expense of a relatively large amount of digital processing and the requirement that much of the circuitry must run at clock speeds that are significantly higher than the analog-to-digital conversion rate. Although they employ complicated digital circuitry, their relatively simple analog circuitry tends to be robust with respect to nonideal circuit behavior [1, 99, 100]. They generally do not require the trimmed components necessary in conventional high precision ADCs. Consequently, high precision  $\Delta\Sigma$  ADC can be implemented using high density VLSI processes optimized for digital circuitry wherein analog accuracy tends to be sacrificed in favor of increased circuit density and speed. This allows integration of the ADC with others digital signal processing components. Such integration gives rise to smaller, more reliable and less expensive system.

Typically,  $\Delta\Sigma$  ADCs consist of a  $\Delta\Sigma$  modulator followed by a digital decimation

filter. The  $\Delta\Sigma$  modulator samples the input signal at many times the Nyquist rate (process referred to as oversampling) and performs very coarse analog-to-digital conversion at the resulting narrow-band sequence. Through the use of coarse digitalto-analog conversion and feedback, the quantization error introduced by the coarse quantizer is spectrally shaped (process referred to as quantization noise shaping) so that its power resides primarily outside the signal band. The digital decimation filter removes the out-of-band portion of the quantization error and reduces the output rate to the Nyquist rate of the input signal.

Oversampling, in conjunction with quantization noise shaping and decimation filtering, thus results in the effect of high precision ADC despite the use of coarse ADC and DAC. In particular, 1-bit ADC and 1-bit DAC are often used which have the added benefit that static errors in their analog levels only affect the gain and offset of the overall system. Moreover, other types of errors originated from nonideal circuit behavior such as analog noise are at least partially removed by the decimating filter. Oversampling also permits the use of simple, low-order analog antialiasing filters because much of the required antialiasing functionality can be included in the digital decimation filter.