# Application du corrélateur "Five-Port" aux PLLs, à la récupération de porteuse et à un MODEM de télécommunications dans la bande 1,8 - 5,5 GHz

Fernando Rangel de Sousa

#### ▶ To cite this version:

Fernando Rangel de Sousa. Application du corrélateur "Five-Port" aux PLLs, à la récupération de porteuse et à un MODEM de télécommunications dans la bande 1,8 - 5,5 GHz. domain\_other. Télécom ParisTech, 2004. English. NNT: . pastel-00000987

### HAL Id: pastel-00000987 https://pastel.hal.science/pastel-00000987v1

Submitted on 3 Feb 2005

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Ecole Doctorale d'Informatique, Télécommunications et Electronique de Paris

# Thèse

présentée pour obtenir le grade de Docteur de l'Ecole Nationale Supérieure des Télécommunications de Paris

Spécialité: Électronique et Communications

# Fernando Rangel de Sousa

Application du corrélateur « Five-Port » aux PLLs, à la récupération de porteuse et à un MODEM de télécommunications dans la bande 1,8 - 5,5 GHz

Soutenue le 18 octobre 2004 devant le jury composé de:

| Raymond QUÉRÉ         | Université de Limoges             | Président          |

|-----------------------|-----------------------------------|--------------------|

| Vicent GIORDANO       | Institut FEMTO-ST                 | Rapporteur         |

| Serge TOUTAIN         | Université de Nantes              | Rapporteur         |

| Robert WEIGEL         | Université de Erlangen (Alemagne) | Examinateur        |

| Raimundo C. S. FREIRE | UFCG (Brésil)                     | Examintaeur        |

| Eric BERGEAULT        | ENST Paris                        | Examinateur        |

| Francisco M. DE ASSIS | UFCG (Brésil)                     | Examinateur        |

| Bernard HUYART        | ENST Paris                        | Directeur de thèse |

### Remerciements

Cette thèse a été réalisée au sein du laboratoire de radio-fréquences et microondes du département Communications et Électronique de l'École Nationale Supérieure des Télécommunications de Paris dans le cadre d'un accord de coopération CAPES/COFECUB entre la France et le Brésil. Ainsi, je voudrais commencer par remercier les personnes responsables pour l'établissement de cet accord à l'ENST, les Professeurs Jean François Naviner et Patrick Loumeau, et à l'UFCG, les Professeurs Raimundo Calros Silvério Freire et Francisco Marcos de Assis.

Je voudrais exprimer ma gratitude à la *Coordenação de Aperfeiçoamento de Pessoal de Nível Superior* (CAPES) pour l'aide financière qui m'a été accordée durant ces quatre ans de thèse et qui m'a bien permis de réussir ce travail de recherche.

Je tiens à remercier vivement mon directeur de thèse Bernard Huyart d'avoir accepté de diriger ce travail. Ses avis toujours sincères et cohérents m'ont permis d'enrichir ma vision sur le métier de chercheur. De toutes ses vertus, celles qui m'ont touché le plus sont sa simplicité, sa disponibilité (même pendant sont repos dominical), sa compétence technique et sa capacité d'entendre les esprits pas toujours très cartésiens. Je l'admire aussi par sa passion des Six-Ports!

J'exprime toute ma gratitude à Raymond Quéré pour avoir accepté de présider le jury et je remercie Serge Toutain et Vincent Giordano pour l'honneur qu'ils m'ont fait en acceptant le rôle difficile de rapporteur. Je dis ma reconnaissance à Robert Weigel qui est venu d'Allemagne et à Raimundo Freire et Francisco M. Assis qui sont venus du Brésil pour participer à

la commission d'examen de cette thèse. Merci également à Eric Bergeault d'avoir bien voulu examiner ce travail.

Je voudrais remercier à tous ceux qui ont accepté de relire tout ou partie de ce manuscrit, en particulier Aida, Antoine (Spy) Khy, Ghalid Abib et Haroun Romdane.

Que soient également remerciés les membres du laboratoire RFM Jean Christophe Cousin, Eric Bergeault et Xavier Begaud pour les remarques et conseils; Cédric Ware pour ses blagues et ses soutiens informatique, linguistique et astronomique; Danielle Childz, Marie Baquero, Chantal Cadiat, Stéphane Bonenfant et Florence Besnard qui m'ont facilité la vie administrative; Alain Croulleboius pour le support mécanique et Karim pour les circuits imprimés.

Je remercie en spécial les collégues de bureau qui ont su construire au cours de ces années une ambiance très agréable, respectueuse et surtout décontractée : Robson Nunes de Lima, Joseph Désiré, Nour Murad, Carlos Palavicini, Anne Claire Lepage et Judson Braga.

Merci aussi à tous les thésards et stagiaires que j'ai rencontré au cours de ces années pour l'ambiance très agréable (la liste n'est pas exhaustive, donc, pardonne-moi celui qui n'a pas été cité) : Beatriz, Guillaume, Gabriel, Olivier, Juan, Souheil , Sarah, Yem, Frederic, Ghassam, Christophe, Sabine, Ivan, Daniel, Leocarlos, Alireza, Palavicini, Ghalid, Judson, De Lima, Spy Khy, Akiko, André, Lourdiane, Haroun, Ludovic, Kais, Elizabeth, Tarik, ...

Aos professores Raimundo Freire, Gurdip Singh Deep e Misael Elias de Morais, gostaria de expressar meus sinceros agradecimentos por terem me iniciado nesta carreira de pesquisador. Seus conselhos e críticas me permitiram redigir artigos científicos posteriormente aceitos em veículos de comunicação de grande renome.

Sou profundamente grato a José Agostinho de Sousa, meu pai, por ter me dado a oportunidade de seguir meus próprios caminhos. Seus valores humanos são o que julgo portar de melhor em minha personalidade. Enfim, agradeço a minha família pelo apoio incondicional em todos os meus empreendimentos.

É a minha esposa Aida a quem reservo o mais especial reconhecimento. Foi com você

Aida, que dividi as alegrias e angústias nestes quatro anos em Paris. Era você a única pessoa com quem podia contar incondicionamemte e fico imaginando como teria sido difícil chegar até aqui sem tuas ponderações, teu carinho e tua dedicação. Serei eternamente grato por tua companhia, por tuas escolhas, por tuas renúncias, enfim por ser minha verdadeira companheira. Acho que em breve poderemos começar a colher os frutos destes sacrifícios feitos ao longo deste últimos anos.

Merci beaucoup!

### Résumé

Le corrélateur *« five-port »* est un dispositif qui calcule précisément le rapport complexe entre deux signaux hyperfréquences à partir de la mesure des valeurs de puissance aux sorties d'un circuit interférométrique à cinq accès. Son application est connue dans les systèmes radars, les systèmes de détermination de la direction d'arrivée de signaux RF, les démodulateurs homodynes et, comme nous proposons dans ce travail, dans les boucles à verrouillage de phase et de récupération de porteuse.

Tandis que les corrélateurs cartésiens classiques projettent le vecteur représentant le signal à démoduler sur une base composée de deux vecteurs orthogonaux, le corrélateur *« five-port »* effectue cette projection sur une « base » à trois vecteurs décalés en phase idéalement de 120°. Grâce à la redondance introduite par le troisième vecteur, le corrélateur *« five-port »* se présente moins sensible aux désappariements de phase et d'amplitude, fournit une variable permettant d'estimer les produits inter-modulation d'ordre pair et peut fonctionner dans une bande de fréquences large.

Cette thèse apporte quelques contributions au domaine de la radiocommunication mobile, notamment aux émetteurs-récepteurs multi-bande et multi-mode. Le premier apport original est l'application de la technique *«five-port »* aux boucles à verrouillage de phase reconfigurables. Cette application est exploitée par la suite dans une boucle de récupération de porteuse multi-mode. Ensuite nous proposons une méthode de caractérisation originale mise en place pour calibrer les corrélateurs *«five-port »*. Finalement nous proposons et évaluons une nouvelle architecture d'émetteur-récepteur fondée sur une base à trois vecteurs.

### **Abstract**

The five-port correlator accurately computes the complex ratio between two radiofrequency signals from the power values measured at the output of a five-port interferometer circuit. Its application has been reported in radars, DOA systems, direct conversion receivers and, as we propose in this work, in PLLs and carrier recovery loops.

Whereas classic cartesian correlators project a vector representing a modulated signal over an orthogonal basis, the five-port correlator performs this projection over a *basis* composed of three vectors ideally phase-shifted of 120°. Thanks to the redundancy added by the third vector, the five-port correlator is less sensible to phase and amplitude imbalances, allows for the estimation of the IM2 products and operates in a wider frequency band.

This PhD research contributes to the mobile radiocommunication area, in particular to the multi-mode and multi-band transceivers. The first contribution is the application of the five-port technique to reconfigurable phase-locked loops. Secondly, these reconfigurable loops are exploited in a multi-mode carrier recovery loop. Then, we present an original five-port characterization method. Finally, we propose and evaluate a novel transceiver architecture based on a three-vector basis.

# Table des matières

| 1 | Le c | orrélate | eur d'ondes «five-port »                                              | 5  |

|---|------|----------|-----------------------------------------------------------------------|----|

|   | 1.1  | Introdu  | action                                                                | 5  |

|   | 1.2  | Le réfl  | ectomètre « six-port »                                                | 6  |

|   |      | 1.2.1    | Les équations régissant le comportement du réflectomètre « six-port » | 7  |

|   | 1.3  | Le cor   | rélateur « five-port »                                                | 9  |

|   |      | 1.3.1    | Le modèle du corrélateur « five-port »                                | 11 |

|   |      | 1.3.2    | L'influence des variations de $V_{OL}$ sur les mesures                | 15 |

|   |      | 1.3.3    | L'influence de l'accès redondant sur les mesures                      | 19 |

|   | 1.4  | Conclu   | usion                                                                 | 24 |

| 2 | Cara | actérisa | tion des corrélateurs <i>« five-port »</i>                            | 27 |

|   | 2.1  | Introdu  | action                                                                | 27 |

|   | 2.2  | Descri   | ption de la Méthode                                                   | 30 |

|   |      | 2.2.1    | Solution analytique de $s_M = Cv_M + D$                               | 30 |

|   |      | 2.2.2    | Détermination des paramètres du corrélateur                           | 32 |

|   | 2.3  | Validat  | tion de la méthode                                                    | 37 |

|   |      | 2.3.1    | Description des simulations                                           | 38 |

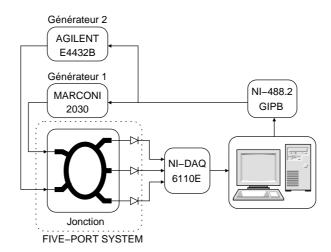

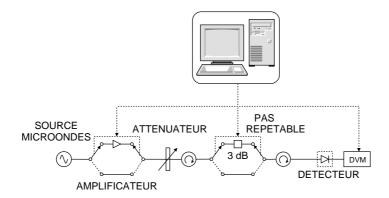

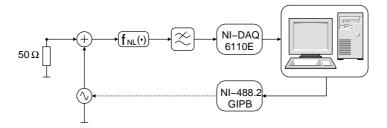

|   |      | 2.3.2    | Description du montage expérimental                                   | 39 |

|   |      | 2.3.3    | Résultats                                                             | 39 |

|   | 2.4  | Conclu   | asion                                                                 | 43 |

| 3 | La d | létectio | n quadratique                                                        | 45  |

|---|------|----------|----------------------------------------------------------------------|-----|

|   | 3.1  | Introd   | uction                                                               | 45  |

|   | 3.2  | Linéar   | risation de détecteurs                                               | 48  |

|   |      | 3.2.1    | Le modèle du détecteur                                               | 49  |

|   | 3.3  | Le dét   | ecteur quadratique à diode                                           | 51  |

|   | 3.4  | Conclu   | usion                                                                | 54  |

| 4 | Trai | tement   | numérique                                                            | 57  |

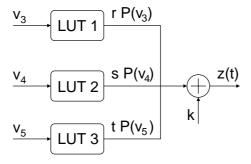

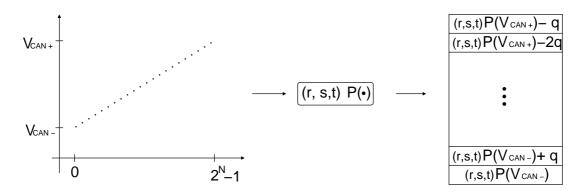

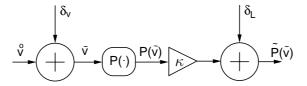

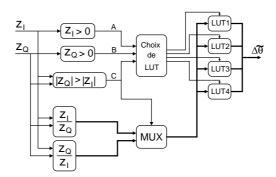

|   | 4.1  | La con   | nstruction des LUTs                                                  | 59  |

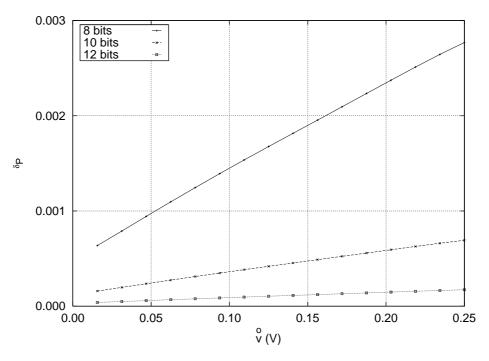

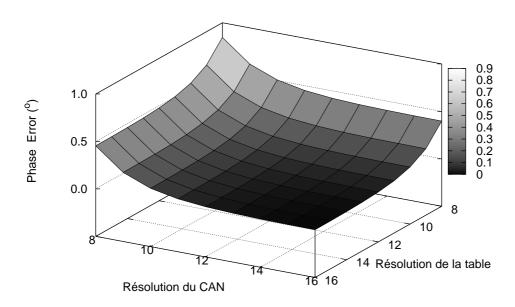

|   | 4.2  | L'influ  | nence de la numérisation sur les mesures                             | 61  |

|   |      | 4.2.1    | Erreurs dues à la résolution finie des CANs                          | 62  |

|   |      | 4.2.2    | Erreurs dues à la troncature et à la quantification des LUTs         | 63  |

|   |      | 4.2.3    | Incertitude totale sur la phase et le module                         | 63  |

|   | 4.3  | Valida   | tion de la théorie                                                   | 65  |

|   | 4.4  | Conclu   | usion                                                                | 73  |

| 5 | PLI  | 4        |                                                                      | 75  |

|   | 5.1  | Rappe    | l sur les boucles à verrouillage de phase                            | 78  |

|   |      | 5.1.1    | Oscillateur contrôlé en tension (VCO de l'anglais voltage controlled |     |

|   |      |          | oscillator)                                                          | 79  |

|   |      | 5.1.2    | Comparateurs de phase                                                | 84  |

|   |      | 5.1.3    | Les filtres de boucle                                                | 85  |

|   |      | 5.1.4    | Acquisition                                                          | 100 |

|   | 5.2  | La PL    | L avec le détecteur de phase « five-port »                           | 102 |

|   |      | 5.2.1    | Comparateur de phase avec un corrélateur « five-port »               | 102 |

|   |      | 5.2.2    | Caractéristiques du VCO                                              | 119 |

|   |      | 5.2.3    | Implantation du Filtre de boucle en DSP                              | 122 |

|   | 5.3  | Descri   | ption du montage expérimental                                        | 123 |

|      |    |     |     | `   |    |

|------|----|-----|-----|-----|----|

| TABL | FΙ | DES | MAT | IFR | FS |

| v | ı | ı | ı |

|---|---|---|---|

| Л | ı | ı | ı |

|   | 5.4  | Résultats de mesure                                                          | 125  |

|---|------|------------------------------------------------------------------------------|------|

|   |      | 5.4.1 Résultats de mesure de la PLL d'ordre 1                                | 126  |

|   |      | 5.4.2 Résultats de mesure de la PLL avec correcteur proportionnel et intégra | 1127 |

|   | 5.5  | Conclusion                                                                   | 135  |

| 6 | Récu | pération de Porteuse                                                         | 137  |

|   | 6.1  | Boucle de récupération de porteuse reconfigurable pour les récepteurs «five- |      |

|   |      | port »                                                                       | 140  |

|   |      | 6.1.1 Détecteur de phase pour une boucle de récupération de porteuse BPSE    | X141 |

|   |      | 6.1.2 Réalisation du détecteur de phase dans un système «five-port »         | 142  |

|   | 6.2  | Résultats expérimentaux                                                      | 143  |

|   | 6.3  | Conclusion                                                                   | 149  |

| 7 | Mod  | ulateur-Démodulateur <i>« five-port »</i>                                    | 151  |

|   | 7.1  | Introduction                                                                 | 151  |

|   | 7.2  | La nouvelle architecture                                                     | 153  |

|   | 7.3  | Mise en application de l'architecture d'émetteur-récepteur                   | 157  |

|   |      | 7.3.1 Prototype en micro-ruban                                               | 158  |

|   |      | 7.3.2 Prototype en technologie AsGa                                          | 166  |

|   | 7.4  | Conclusion                                                                   | 176  |

| A | VCC  |                                                                              | 195  |

|   | A.1  | Paramètres définissant la performance d'un VCO                               | 196  |

|   | A.2  | Le modèle de Lesson pour le bruit de phase des oscillateurs                  | 198  |

| В | Résu | ıltats de la PLL                                                             | 201  |

| C | Mod  | ulateur à cinq accès                                                         | 209  |

|   | C.1  | Préliminaires                                                                | 210  |

|   | C.2   | La fon   | ction modulation                                                      | 213  |

|---|-------|----------|-----------------------------------------------------------------------|------|

|   |       | C.2.1    | Deux bases vectorielles capables de représenter un signal sur un plan | 214  |

|   | C.3   | Structu  | res qui réalisent un modulateur à cinq accès                          | 216  |

|   |       | C.3.1    | Parallèle non-isolée                                                  | 216  |

|   |       | C.3.2    | Parallèle semi-isolée                                                 | 218  |

|   |       | C.3.3    | Série semi-isolée                                                     | 220  |

|   |       | C.3.4    | Parallèle isolée                                                      | 220  |

|   |       | C.3.5    | Parallèle isolée avec des circulateurs                                | 221  |

|   |       | C.3.6    | Série isolée avec des circulateurs                                    | 226  |

|   |       | C.3.7    | Conclusions partielles                                                | 226  |

| D | Lista | age de p | orogrammes                                                            | 231  |

|   | D.1   | Progra   | mmes en MATLAB                                                        | 231  |

|   |       | D.1.1    | Calibrage du corrélateur                                              | 231  |

|   |       | D.1.2    | Linearization des détecteurs de puissance                             | 234  |

|   | D.2   | Progra   | mmes en C++                                                           | 236  |

|   |       | D.2.1    | Classes pour le contrôle des instruments                              | 236  |

|   |       | D.2.2    | Classes pour l'acquisition de donnée                                  | 243  |

|   | D.3   | Progra   | mmes en Assembler                                                     | 252  |

|   |       | D.3.1    | Code pour la boucle à verrouillage de phase (correcteur proportionnel | )252 |

| E | Déve  | eloppen  | nent des équations                                                    | 263  |

|   | E.1   | Métho    | de de calibrage                                                       | 264  |

|   | E.2   | Erreur   | s sur la magnitude et sur la phase dûs à la numérisation              | 268  |

|   |       | E 2 1    | Dérivé de l'équation de Potter                                        | 269  |

# Table des figures

| 1.1  | Schéma de principe du réflectomètre « six-port »                                           | 7  |

|------|--------------------------------------------------------------------------------------------|----|

| 1.2  | Détermination de $\Gamma_2$ à partir de l'intersection de trois cercles                    | 9  |

| 1.3  | Schéma synoptique du corrélateur «five-port »                                              | 10 |

| 1.4  | Modèle de la jonction hyperfréquences du corrélateur « five-port »                         | 11 |

| 1.5  | Modèle complet du corrélateur « five-port »                                                | 12 |

| 1.6  | Réponse fréquentielle du filtre passe-bas                                                  | 13 |

| 1.7  | Projection de $\vec{z}$ sur la base $[\vec{\nu_3} \ \vec{\nu_4} \ \vec{\nu_5}]^T$          | 14 |

| 1.8  | Modèle du corrélateur simulé « five-port »                                                 | 16 |

| 1.9  | Valeurs de z(t) autour de sa valeur nominale $0,001e^{j\frac{\pi}{4}}$ lorsque l'amplitude |    |

|      | de l'oscillateur local varie de $\pm 20\%$                                                 | 17 |

| 1.10 | Variations sur les valeurs des composantes réelle et imaginaire de $z(t)$ autour           |    |

|      | de sa valeur nominale $0,001e^{j\frac{\pi}{4}}$ lorsque l'amplitude de l'oscillateur local |    |

|      | varie de $\pm 20\%$                                                                        | 18 |

| 1.11 | Circuit «five-port » avec un seul déphaseur                                                | 20 |

| 1.12 | Circuit du corrélateur « five-port » mettant au point une base triphasée                   | 21 |

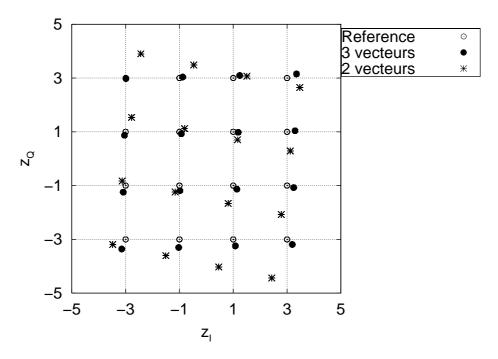

| 1.13 | Constellations 16QAM                                                                       | 24 |

| 2.1  | Schéma synoptique système mis au point pour caractériser le corrélateur                    |    |

|      | <i>« five-port »</i>                                                                       | 31 |

| 2.2  | Tensions mesurées aux sorties des détecteurs de puissance                                  | 34 |

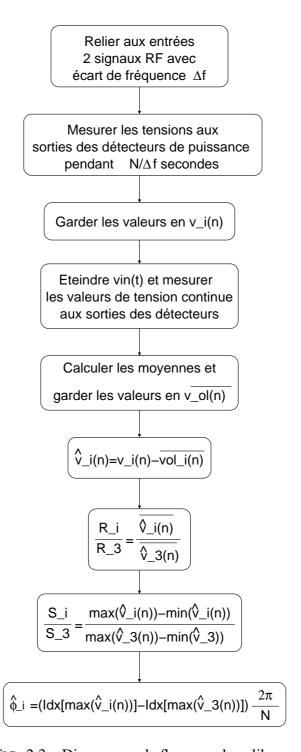

| 2.3  | Diagramme de flux pour le calibrage                                                        | 38 |

| 2.4  | Montage expérimental utilisé pour valider la méthode de calibrage                  | 40 |

|------|------------------------------------------------------------------------------------|----|

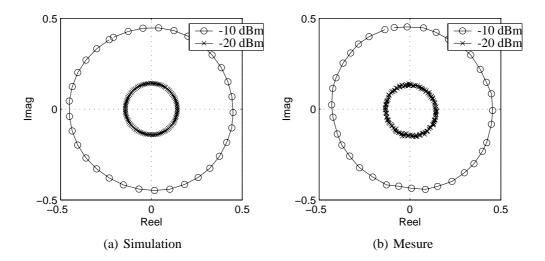

| 2.5  | Représentation complexe des valeurs calculées de $z(t)$ obtenues à partir de       |    |

|      | données de simulation et de mesure                                                 | 41 |

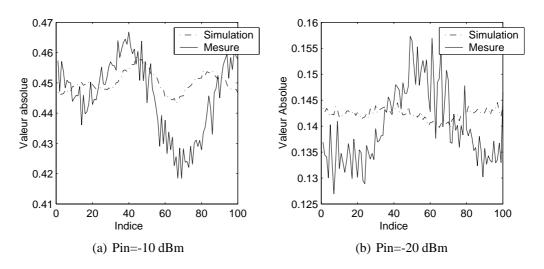

| 2.6  | Valeurs absolues de $z(t)$                                                         | 42 |

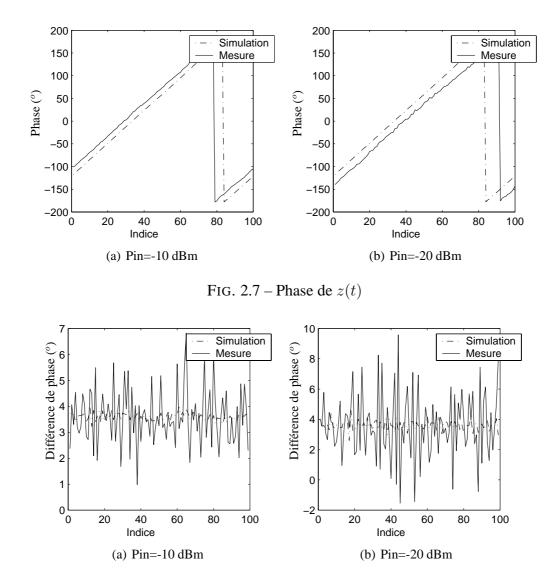

| 2.7  | Phase de $z(t)$                                                                    | 43 |

| 2.8  | Dérivée de la phase de $z(t)$                                                      | 43 |

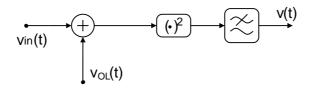

| 3.1  | Diagramme de principe d'un détecteur quadratique idéal                             | 45 |

| 3.2  | Diagramme de principe d'un détecteur quadratique réel                              | 46 |

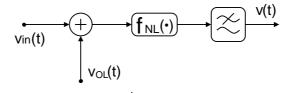

| 3.3  | Montage utilisé par Potter pour la linéarisation des détecteurs quadratiques .     | 47 |

| 3.4  | Montage adopté pour la linéarisation des détecteurs quadratiques                   | 48 |

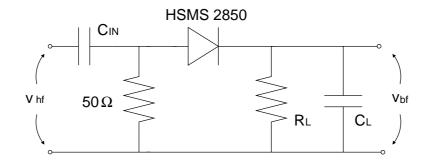

| 3.5  | Schéma du détecteur quadratique basé sur une diode                                 | 52 |

| 3.6  | Modèle équivalent du détecteur quadratique à diode                                 | 52 |

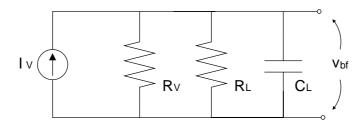

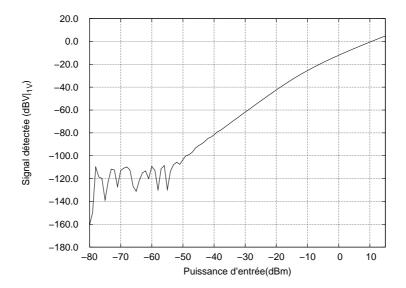

| 3.7  | Tension observée à la sortie du détecteur quadratique lorsqu'un signal à 2         |    |

|      | GHz, dont la puissance varie entre -80 dBm et +15 dBm, est appliqué à              |    |

|      | l'entrée                                                                           | 54 |

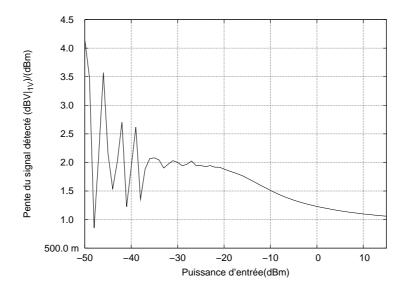

| 3.8  | Pente de la tension observée à la sortie du détecteur quadratique lorsqu'un        |    |

|      | signal à 2 GHz, dont la puissance varie entre -80 dBm et +15 dBm, est ap-          |    |

|      | pliqué à l'entrée.                                                                 | 55 |

| 3.9  | Tension observée à la sortie du détecteur quadratique avant et après linéarisation |    |

|      | lorsqu'un signal à 2 GHz, dont la puissance varie entre -80 dBm et +15 dBm,        |    |

|      | est appliqué à l'entrée.                                                           | 56 |

| 3.10 | Pente de la tension observée à la sortie du détecteur quadratique avant et         |    |

|      | après linarisation lorsqu'un signal à 2 GHz, dont la puissance varie entre -80     |    |

|      | dBm et +15 dBm, est appliqué à l'entrée                                            | 56 |

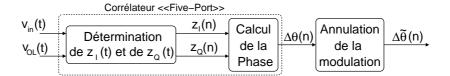

| 4.1  | Schéma synoptique du traitement numérique du corrélateur «five-port » lorsque      |    |

|      | les LUTs sont utilisées                                                            | 59 |

| 4.2  | Branche du circuit d'interface entre le détecteur quadratique et le circuit de         |    |

|------|----------------------------------------------------------------------------------------|----|

|      | traitement numérique du corrélateur « five-port »                                      | 60 |

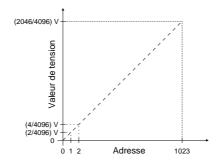

| 4.3  | Procédure de construction des tables de correspondance                                 | 60 |

| 4.4  | Illustration des erreurs de quantification ajoutées aux tensions mesurées et           |    |

|      | aux puissances estimées                                                                | 61 |

| 4.5  | Erreur maximale sur la puissance estimée en fonction de la tension mesurée             |    |

|      | pour trois valeurs de résolution de CAN : 8, 10 et 12 bits                             | 64 |

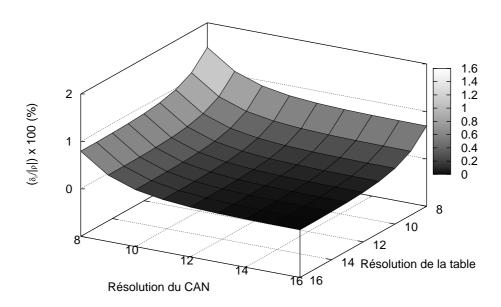

| 4.6  | Incertitude sur la phase de $\vec{z}$ en fonction des résolutions du CAN et des tables | 66 |

| 4.7  | Incertitude relative sur le module de $\vec{z}$ en fonction des résolutions du CAN     |    |

|      | et des tables                                                                          | 67 |

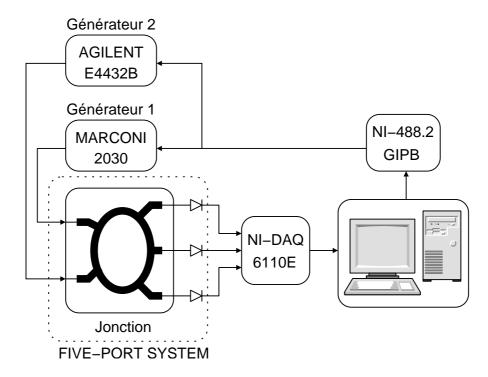

| 4.8  | Diagramme du montage utilisé pour effectuer les mesures                                | 68 |

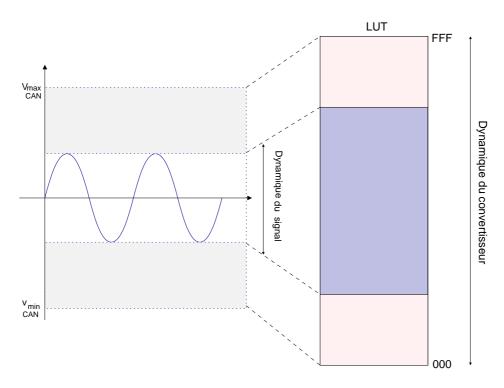

| 4.9  | Dynamiques du signal et du convertisseur analogique numérique                          | 69 |

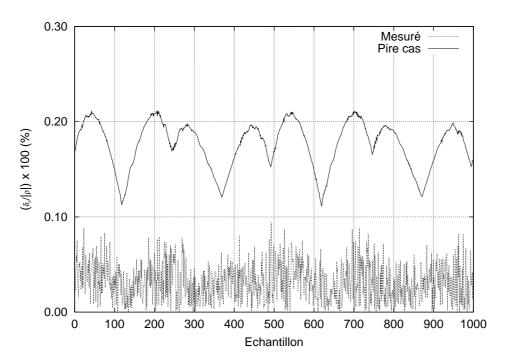

| 4.10 | Module de $\vec{z(t)}$ pour un signal de dynamique de 82,3 mV                          | 71 |

| 4.11 | Module de $\vec{z(t)}$ pour un signal de dynamique de 162,8 mV                         | 71 |

| 4.12 | Phase de $z(t)$ pour un signal de dynamique 82,3 mV                                    | 72 |

| 4.13 | Phase de $z(t)$ pour un signal de dynamique 162,8 mV                                   | 72 |

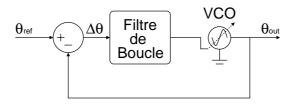

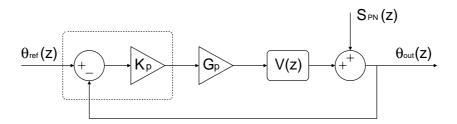

| 5.1  | Schéma élémentaire d'une boucle à verrouillage de phase                                | 75 |

| 5.2  | Schéma élémentaire d'un synthétiseur de fréquence                                      | 76 |

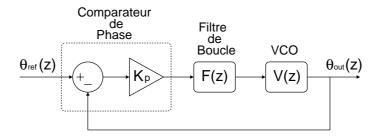

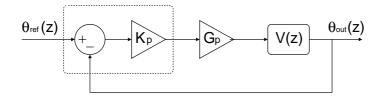

| 5.3  | Modèle linéaire de la boucle à verrouillage de phase en domaine de $z$                 | 78 |

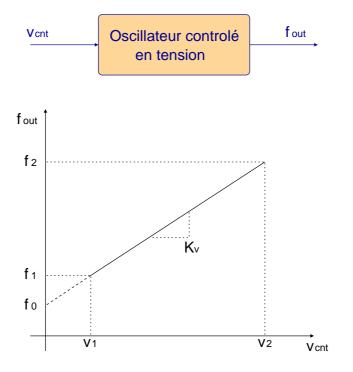

| 5.4  | Définition d'un oscillateur contrôlé en tension                                        | 79 |

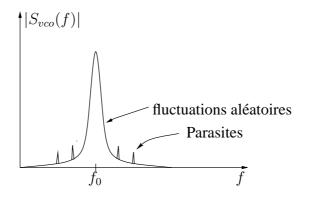

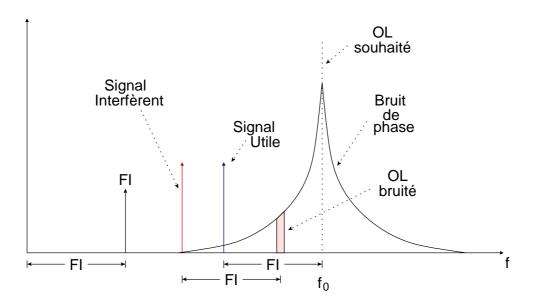

| 5.5  | Spectre du signal de sortie d'un oscillateur                                           | 81 |

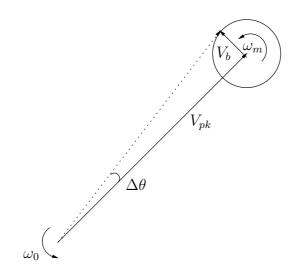

| 5.6  | Représentation vectorielle du signal de sortie d'un oscillateur                        | 82 |

| 5.7  | Effet du bruit de phase dans un canal de télécommunication                             | 82 |

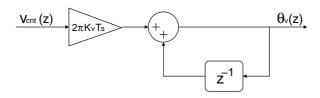

| 5.8  | Modèle du VCO                                                                          | 83 |

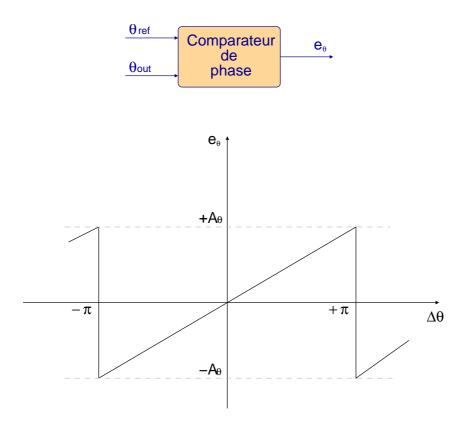

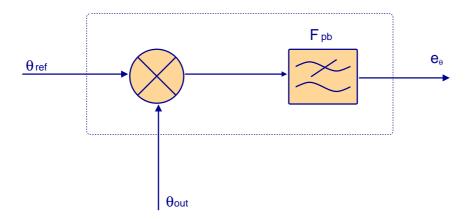

| 5.9  | Comparateur de phase                                                                   | 85 |

| 5.10 | Comparateur de phase à base d'un circuit mélangeur                                     | 85 |

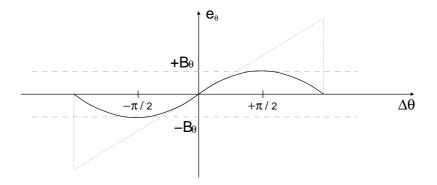

| 5.11 | Réponse du comparateur de phase à mélangeur                                               | 86 |

|------|-------------------------------------------------------------------------------------------|----|

| 5.12 | Modèle linéaire d'une PLL d'ordre 1                                                       | 87 |

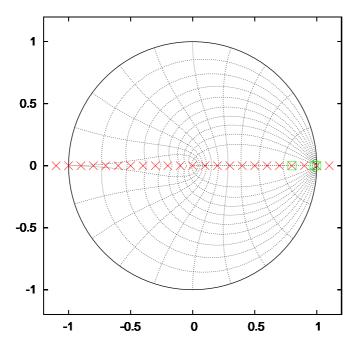

| 5.13 | Lieu de racines (×) pour $-0, 1 < K < 2, 1$ . Les trois points en évidence ( $\square$ )  |    |

|      | équivalent à K=0,002, K=0,02 et K=0,2 respectivement                                      | 87 |

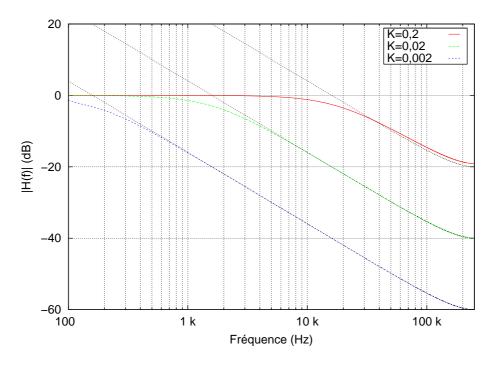

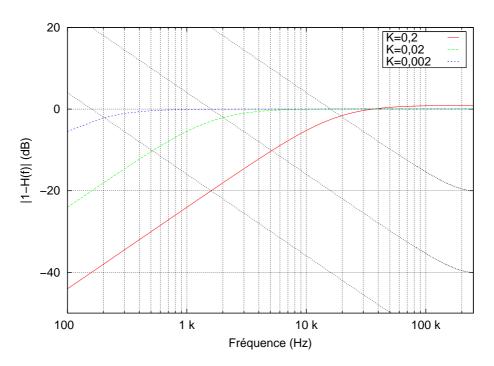

| 5.14 | Réponse fréquentielle de la PLL avec correcteur proportionnel où $100\ Hz <$              |    |

|      | $f < 250 \ kHz,  f_s = 1/T_s = 500 \ kHz$ et $K = 0, 2,  K = 0, 02$ , $K = 0, 002$        | 88 |

| 5.15 | Modèle de la PLL d'ordre 1 prenant en compte le bruit de phase du VCO .                   | 89 |

| 5.16 | Réponse au bruit de phase du VCO avec correcteur proportionnel, $100\ Hz <$               |    |

|      | $f < 250 \ kHz, f_s = 1/T_s = 500 \ kHz \ {\rm et} \ K = 0, 2, K = 0, 02, K = 0, 002 \ .$ | 90 |

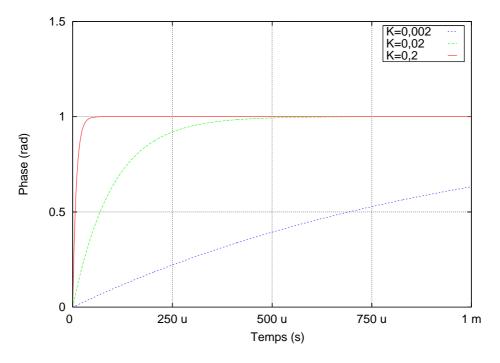

| 5.17 | Réponse de la boucle à verrouillage de phase d'ordre 1 à un écart de phase .              | 91 |

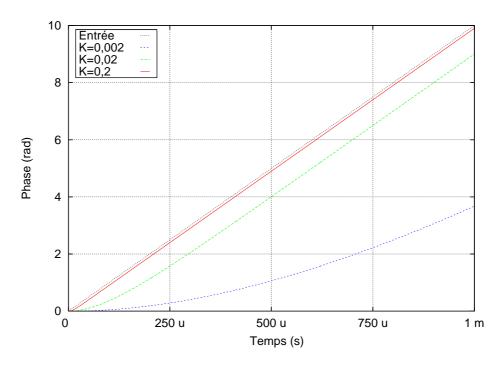

| 5.18 | Réponse de la boucle à verrouillage de phase d'ordre 1 à une pente de phase               |    |

|      | de valeur $10 \times 10^3$                                                                | 92 |

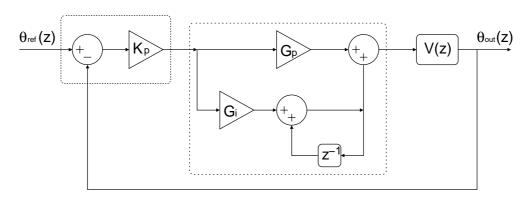

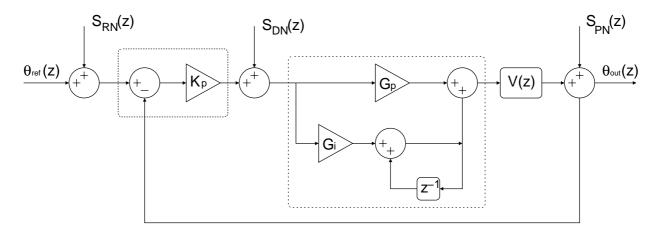

| 5.19 | Diagramme de bloc de la boucle à verrouillage de phase comprenant un cor-                 |    |

|      | recteur proportionnel et intégral                                                         | 92 |

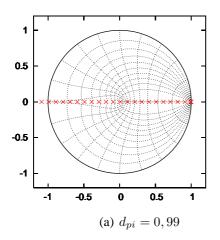

| 5.20 | Lieu des racines de la fonction de transfert de la boucle à verrouillage de               |    |

|      | phase avec correcteur proportionnel et intégral lorsque le zéro du filtre est             |    |

|      | 0,9 et 0,99                                                                               | 94 |

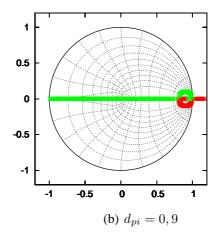

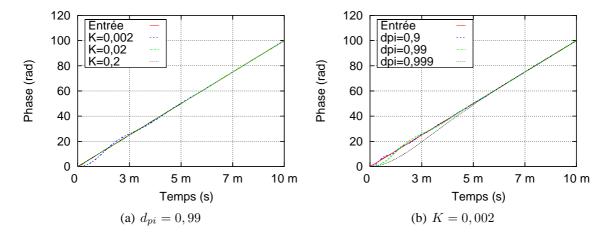

| 5.21 | Réponse de la PLL lorsque un échelon de phase est appliqué à l'entrée pour                |    |

|      | deux cas : a) zéro du filtre constant et gain de la boucle variable ; b)gain de           |    |

|      | la boucle constant et zéro du filtre variable                                             | 95 |

| 5.22 | Réponse de la PLL lorsque une pente de phase de $10x10^3$ est appliquée à                 |    |

|      | l'entrée pour deux cas : a) zéro du filtre constant et gain de la boucle variable ;       |    |

|      | b)gain de la boucle constant et zéro du filtre variable                                   | 95 |

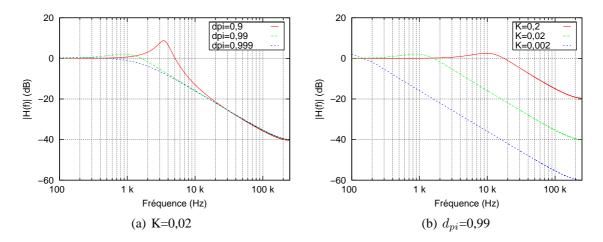

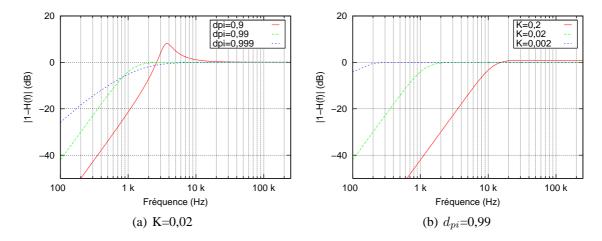

| 5.23 | Réponse fréquentielle de la boucle à verrouillage de phase avec correcteur                |    |

|      | proportionnel et intégral pour 100 Hz $<$ f $<$ 250 kHz et $f_s$ =500 kHz dans            |    |

|      | les conditions suivantes : a)K=0,02 et $d_{pi}$ =0,9, 0,99 et 0,99 ; b) $d_{pi}$ =0,99 et |    |

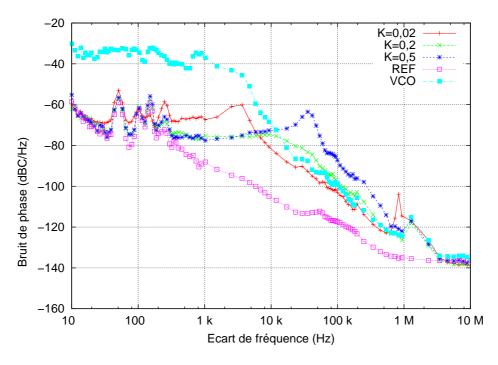

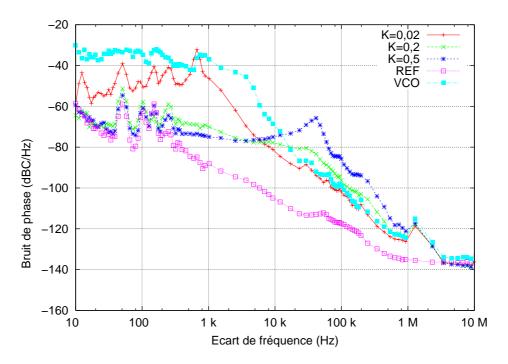

|      | K=0,2, 0,02 et 0,002                                                                      | 97 |

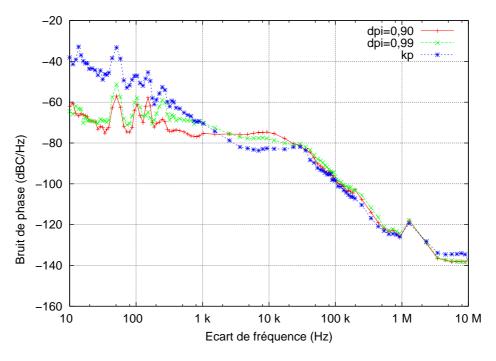

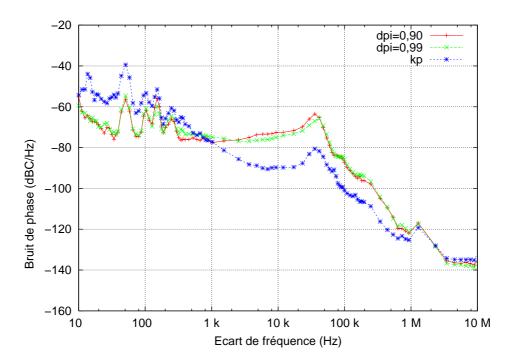

| 5.24 | Réponse fréquentielle de la boucle à verrouillage de phase avec correcteur                                          |     |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

|      | proportionnel et intégral en fonction du bruit de phase de l'oscillateur pour                                       |     |

|      | $100\mathrm{Hz} < \mathrm{f} < 250\mathrm{kHz}$ et $f_s = 500\mathrm{kHz}$ dans les conditions suivantes : a)K=0,02 |     |

|      | et $d_{pi}$ =0,9, 0,99 et 0,99.; b) $d_{pi}$ =0,99 et K=0,2, 0,02 et 0,002                                          | 98  |

| 5.25 | Schéma synoptique de la boucle à verrouillage de phase avec correcteur pro-                                         |     |

|      | portionnel et intégral considérant le bruit de phase du VCO, le bruit de phase                                      |     |

|      | de la source et le bruit ajouté par le comparateur de phase                                                         | 99  |

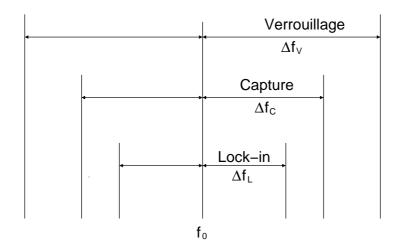

| 5.26 | Acquisition en fréquence                                                                                            | 100 |

| 5.27 | Schéma synoptique de la boucle à verrouillage de phase utilisant un corrélateur                                     |     |

|      | « five-port » comme comparateur de phase                                                                            | 103 |

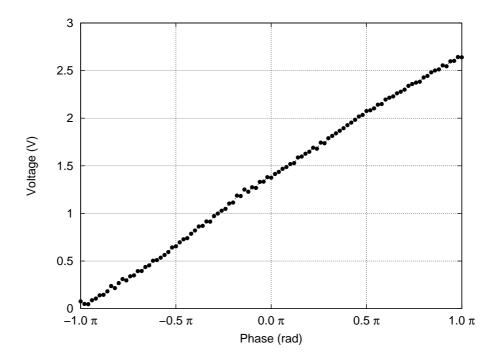

| 5.28 | Caractéristique mesurée du comparateur de phase                                                                     | 104 |

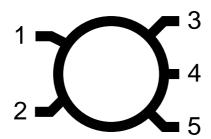

| 5.29 | Anneau à cinq branches                                                                                              | 105 |

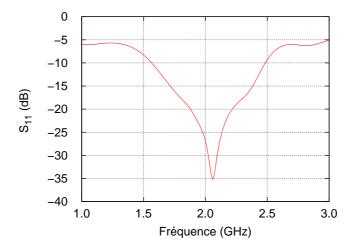

| 5.30 | Module du coefficient de réflexion mesuré à l'entrée 1 de l'anneau à cinq                                           |     |

|      | branches                                                                                                            | 106 |

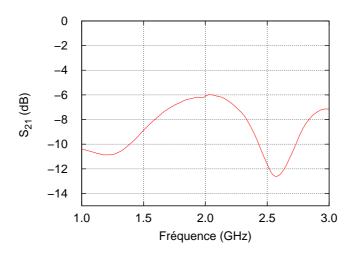

| 5.31 | Module du coefficient $S_{21}$ de l'anneau à cinq branches                                                          | 106 |

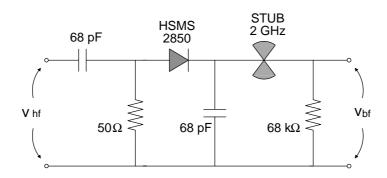

| 5.32 | Détecteur de puissance du comparateur de phase «five-port »                                                         | 107 |

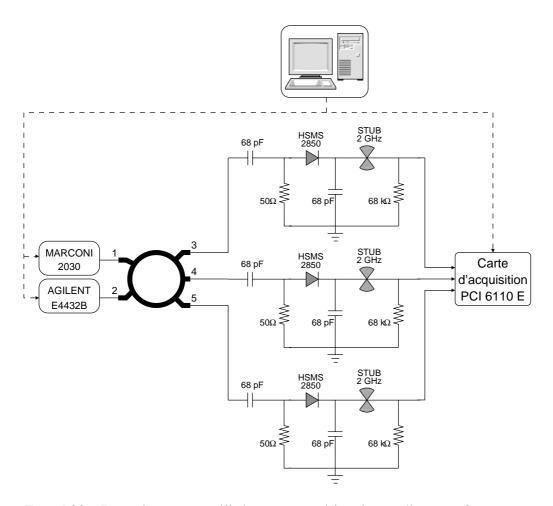

| 5.33 | Banc de mesure utilisé pour caractériser le corrélateur « five-port »                                               | 109 |

| 5.34 | Valeurs et rapports de tension mesurés aux sorties des détecteurs de puis-                                          |     |

|      | sance avant et après correction entre -20 dBm et +10 dBm                                                            | 110 |

| 5.35 | Tensions mesurées aux sorties des détecteurs de puissance pendant la procédure                                      | ;   |

|      | de caractérisation du corrélateur «five-port »                                                                      | 111 |

| 5.36 | Schéma synoptique du montage expérimental                                                                           | 111 |

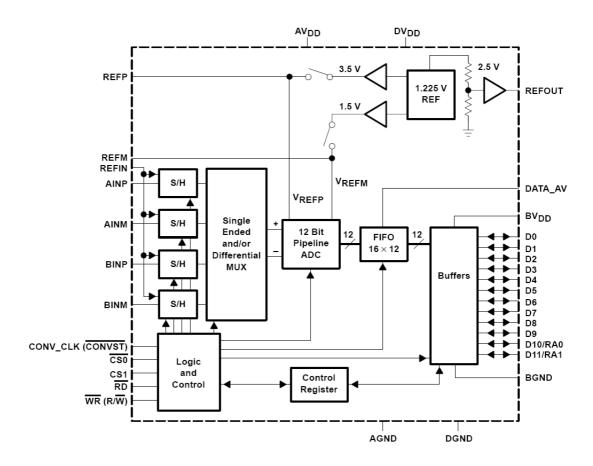

| 5.37 | Diagramme de blocs du convertisseur THS1206                                                                         | 112 |

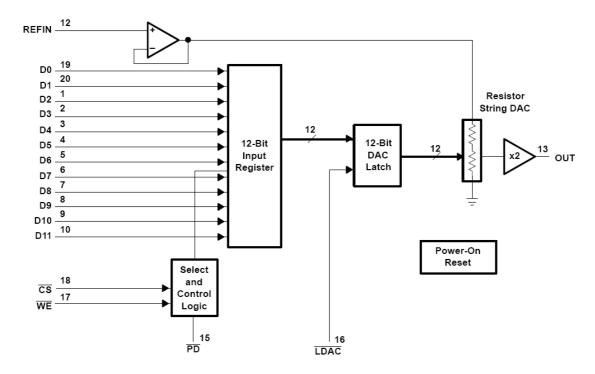

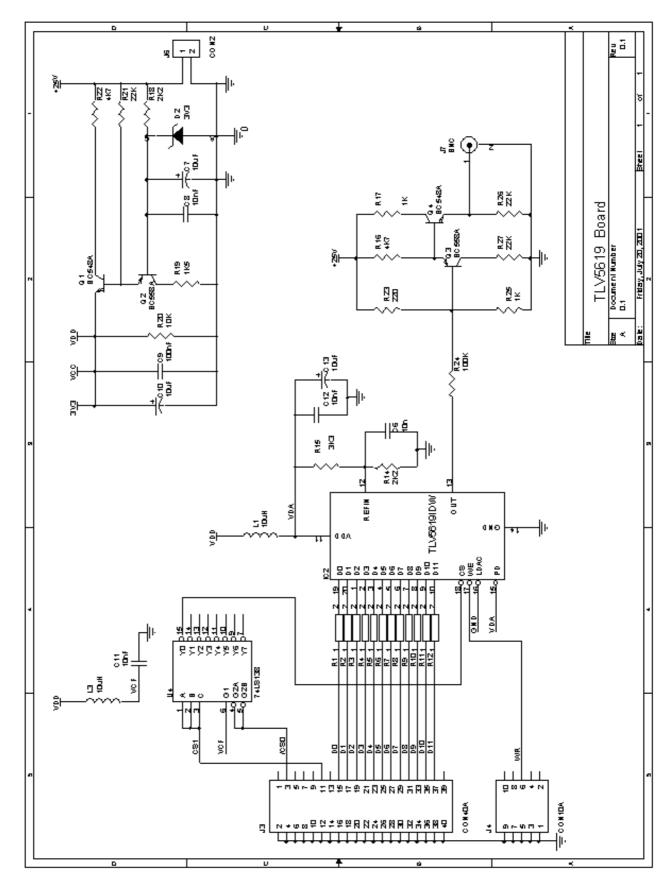

| 5.38 | Diagramme de blocs du convertisseur TLV5619                                                                         | 113 |

| 5.39 | Circuit de la carte de conversion de numérique en analogique                                                        | 114 |

| 5.40 | Layout de la carte de conversion de numérique en analogique                                                         | 115 |

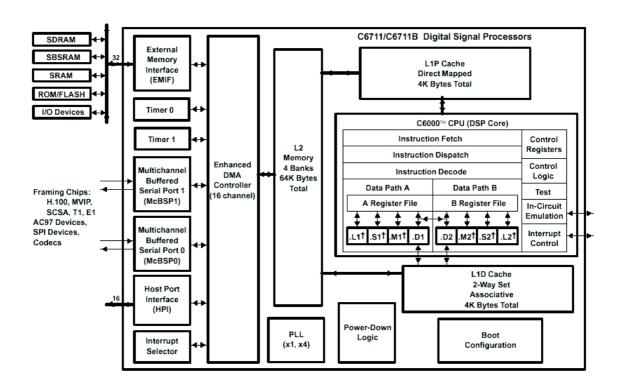

| 5.41 | Le diagramme de blocs du DSP TMS320C6711                                                                            | 116 |

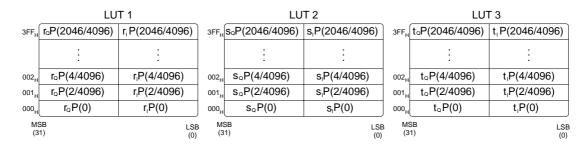

| 5.42 | Tables de valeurs de tension entre $0$ et $\frac{2046}{4096}$ V corrigées par la fonction de |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | Potter (3.3) et normalisées par des constantes de calibrage                                  | 117 |

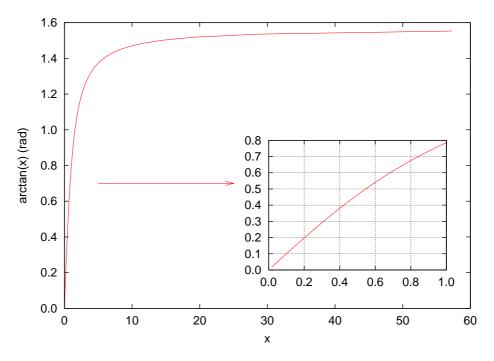

| 5.43 | Fonction $\arctan(x)$ pour $0 < \arctan(x) < \frac{\pi}{2} \dots \dots \dots \dots$          | 118 |

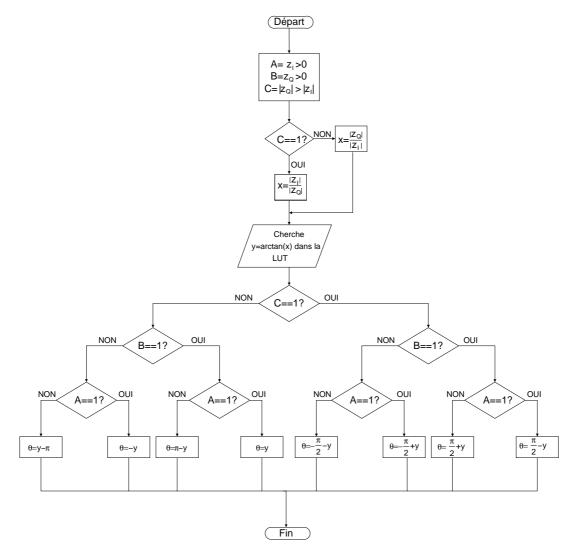

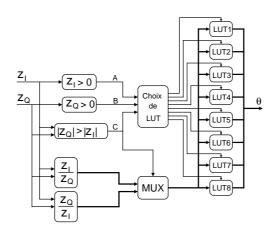

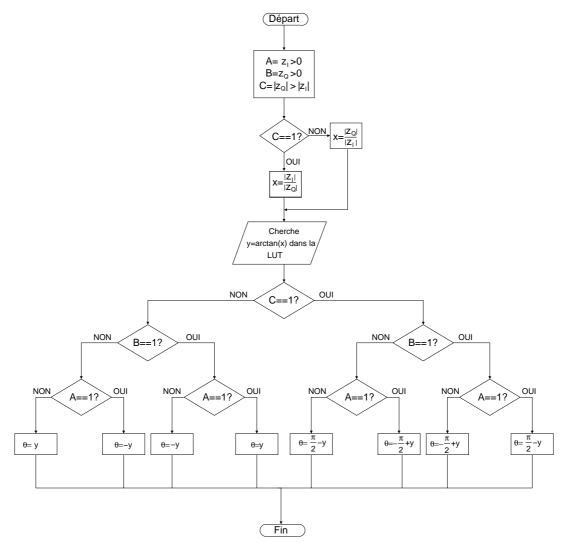

| 5.44 | Diagramme de flux de l'algorithme de détermination de l'arctan(x)                            | 119 |

| 5.45 | Diagramme de bloc de l'algorithme de détermination de l'arctan(x) implanté                   |     |

|      | dans le DSP TMS320C6711                                                                      | 120 |

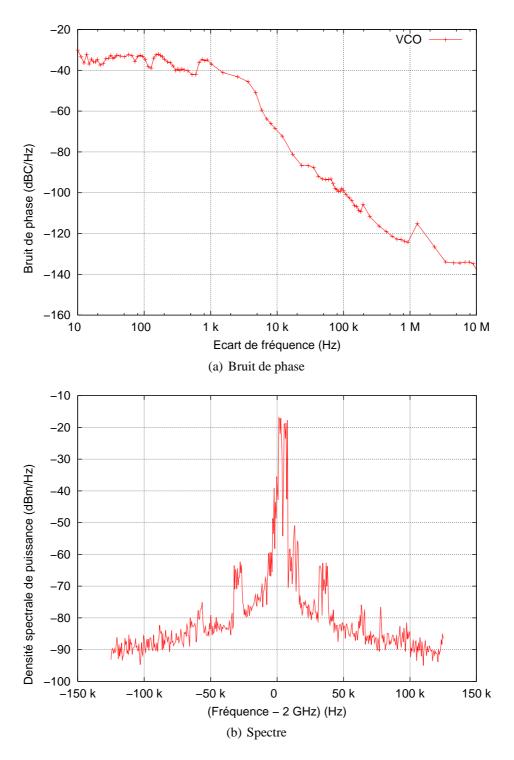

| 5.46 | Bruit de phase et spectre du VCO en fonctionnement libre                                     | 121 |

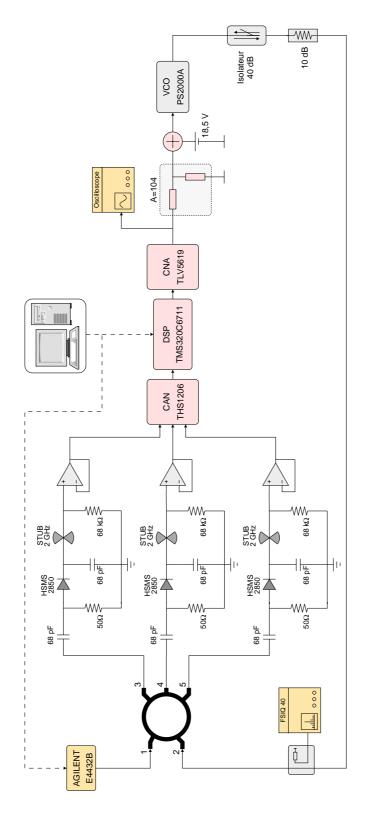

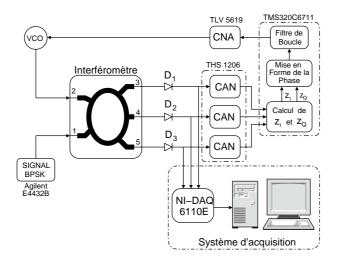

| 5.47 | Schéma synoptique du montage expérimental                                                    | 124 |

| 5.48 | Photo du montage expérimental                                                                | 125 |

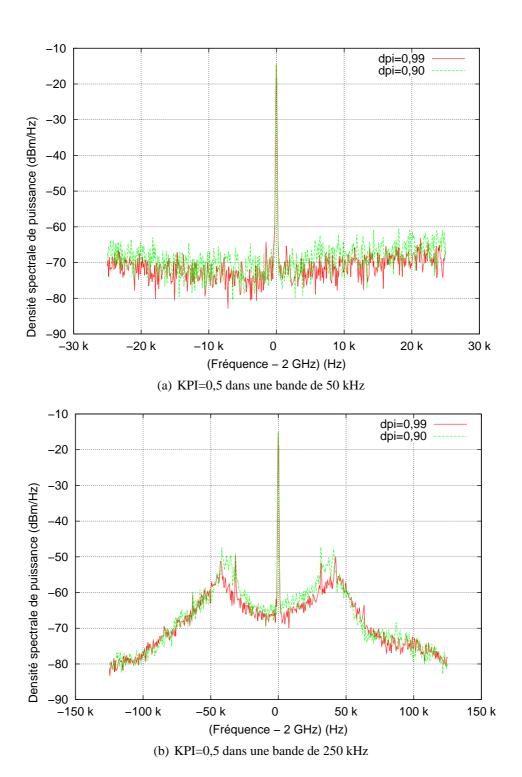

| 5.49 | Spectre du signal de sortie du VCO pour la PLL d'ordre 1 avec deux valeurs                   |     |

|      | de bande passante : $f_{bw}$ =15,92 kHz et $f_{bw}$ =39,79 kHz                               | 126 |

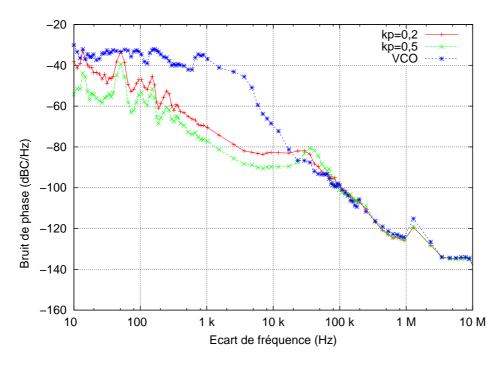

| 5.50 | Courbes du bruit de phase du signal de sortie du VCO pour la PLL de                          |     |

|      | première ordre avec deux valeurs de bande passante : $f_{bw}$ =15,92 kHz et                  |     |

|      | f <sub>bw</sub> =39,79 kHz                                                                   | 127 |

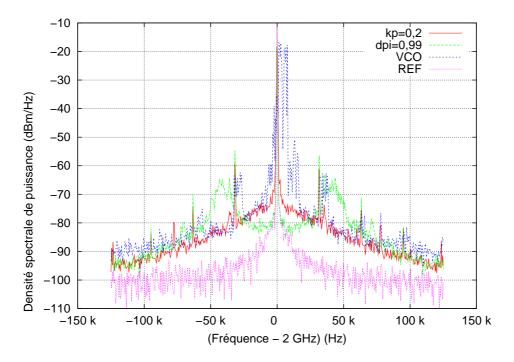

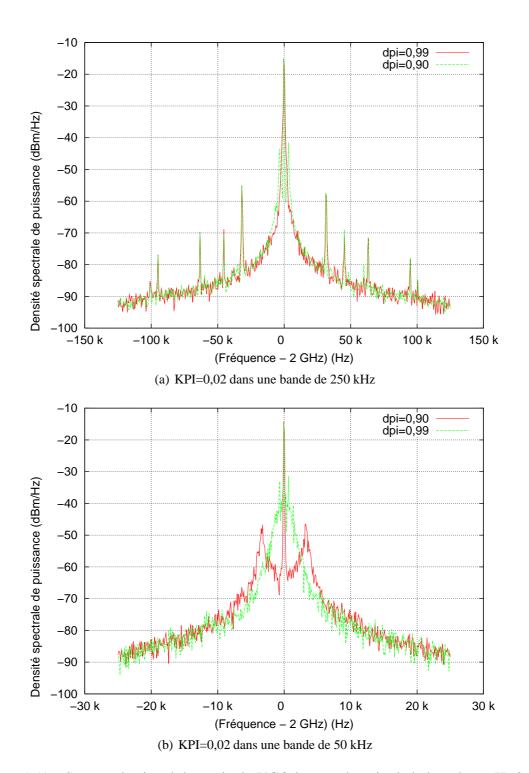

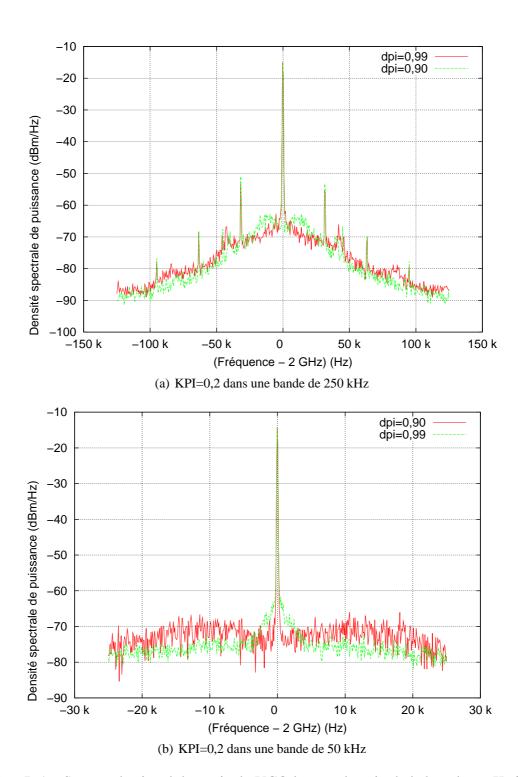

| 5.51 | Spectre du signal de sortie du VCO lorsque le gain de la boucle est K=0,02                   | 129 |

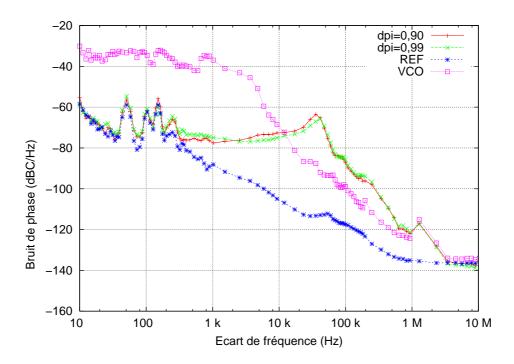

| 5.52 | Bruit de phase du signal de sortie du VCO lorsque le gain de la boucle est                   |     |

|      | K=0,02                                                                                       | 130 |

| 5.53 | Bruit de phase du signal de sortie du VCO lorsque K=0,2 pour les PLLs                        |     |

|      | d'ordre 1 et proportionnel et intégral                                                       | 131 |

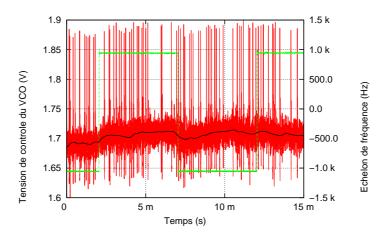

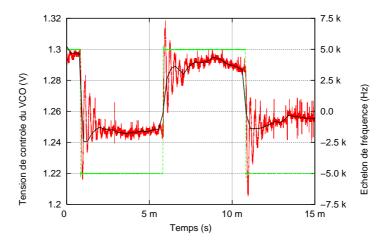

| 5.54 | Réponse de la PLL à un échelon de fréquence de 2 kHz. Le gain de la boucle                   |     |

|      | était K=0,5 et $d_{pi}$ =0,99                                                                | 132 |

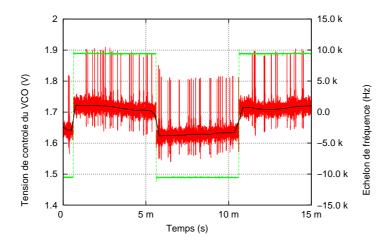

| 5.55 | Réponse de la PLL à un échelon de fréquence de 20 kHz. Le gain de la                         |     |

|      | boucle était K=0,5 et $d_{pi}$ =0,99                                                         | 133 |

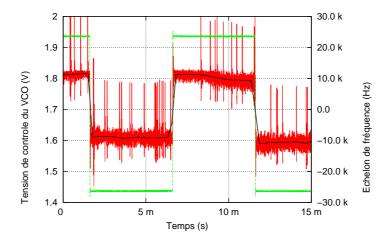

| 5.56 | Réponse de la PLL à un échelon de fréquence de 50 kHz. Le gain de la                         |     |

|      | boucle était K=0,5 et $d_{pi}$ =0,99                                                         | 133 |

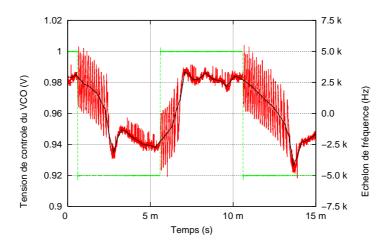

| 5.57 | Réponse de la PLL à un échelon de fréquence de 10 kHz. Le gain de la                         |     |

|      | boucle était K=0,2 et $d_{pi}$ =0,99                                                         | 134 |

| 5.58 | Reponse de la PLL a un echelon de frequence de 10 kHz. Le gain de la       |     |

|------|----------------------------------------------------------------------------|-----|

|      | boucle était K=0,2 et $d_{pi}$ =0,90                                       | 134 |

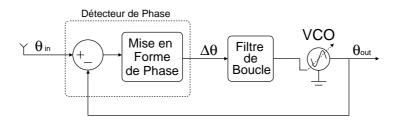

| 6.1  | Schéma élémentaire d'une boucle de Costas                                  | 139 |

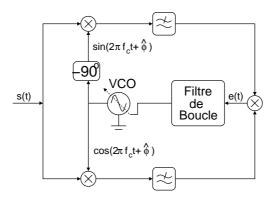

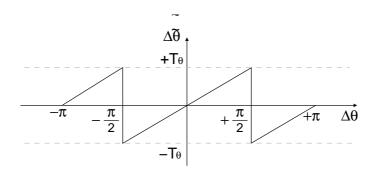

| 6.2  | Schéma synoptique de la boucle de récupération de porteuse proposée        | 140 |

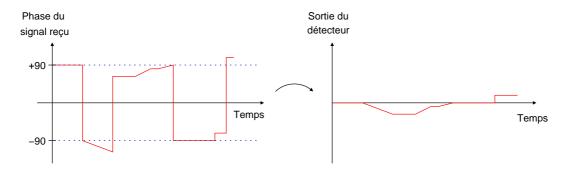

| 6.3  | Réponse souhaitée du détecteur de phase d'une boucle de récupération de    |     |

|      | porteuse pour un signal BPSK                                               | 141 |

| 6.4  | Diagramme de bloc du détecteur de phase de la boucle de récupération de    |     |

|      | porteuse                                                                   | 142 |

| 6.5  | Fonction de transfert du circuit d'annulation de la modulation BPSK        | 142 |

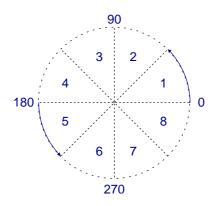

| 6.6  | Cercle trigonométrique divisé en huit octants                              | 143 |

| 6.7  | Diagramme de bloc de l'algorithme de détermination de l'erreur de phase    |     |

|      | dans un système de récupération de porteuse                                | 143 |

| 6.8  | Diagramme de flux de l'algorithme de détermination choisissant les tables  |     |

|      | contenant l'erreur de phase dans un système de récupération de porteuse    | 144 |

| 6.9  | Banc de mesure employé pour évaluer le système de récupération de porteuse | 145 |

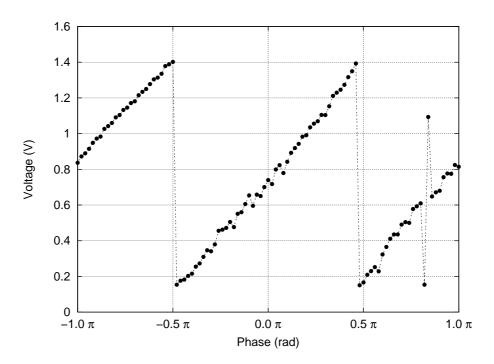

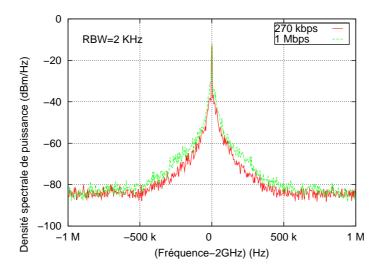

| 6.10 | Fonction de transfert du détecteur de phase                                | 146 |

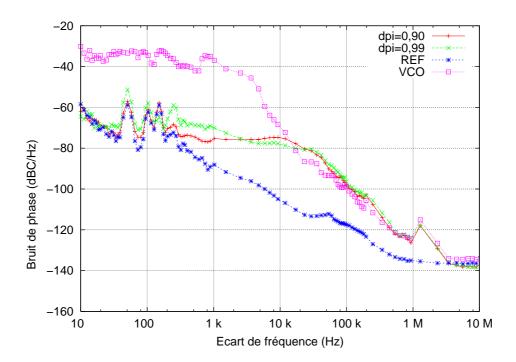

| 6.11 | Bruit de phase du signal du générateur (REF), du VCO en fonctionnement     |     |

|      | libre (VCO), de la porteuse récupérée lorsque le signal transmis est sans  |     |

|      | modulation (MOD OFF) et lorsqu'il est modulé en BPSK avec débits de 270    |     |

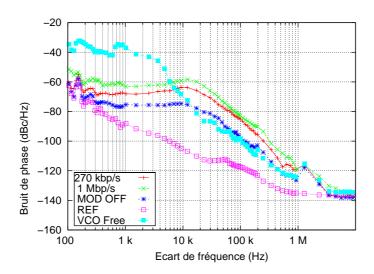

|      | kS/s et de 1 MS/s                                                          | 146 |

| 6.12 | Spectre de la porteuse récupérée lorsque le signal transmis est modulé en  |     |

|      | BPSK avec débits de 270 kS/s et de 1 MS/s                                  | 147 |

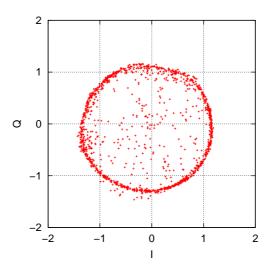

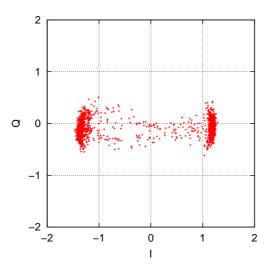

| 6.13 | Diagramme de constellation du signal BPKS à 270 kS/s démodulé avant la     |     |

|      | mise en fonctionnement du système de récupération de porteuse              | 148 |

| 6.14 | Diagramme de constellation du signal BPKS à 270 kS/s démodulé avec la      |     |

|      | porteuse régénérée en utilisant le système « five-port »                   | 149 |

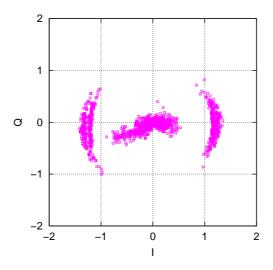

| 6.15 | Diagramme de constellation du signal BPKS à 1 MS/s démodulé avec la                   |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | porteuse régénérée en utilisant le système « five-port »                              | 149 |

| 7.1  | Modèle de la partie hyperfréquence du « five-port »                                   | 153 |

| 7.2  | Schéma synoptique du MODEM « five-port »                                              | 154 |

| 7.3  | Générateur de base vectorielle                                                        | 155 |

| 7.4  | Schéma du démodulateur                                                                | 156 |

| 7.5  | Schéma du modulateur                                                                  | 157 |

| 7.6  | Masque du générateur de base vectorielle                                              | 159 |

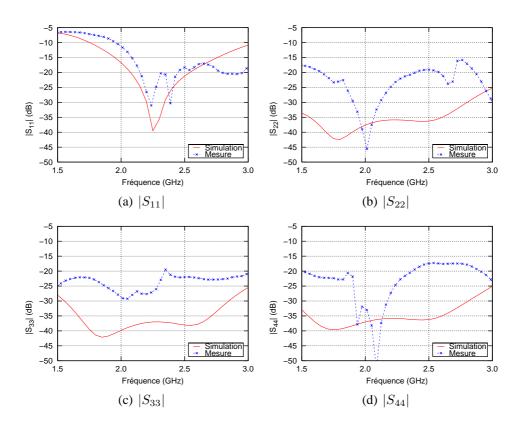

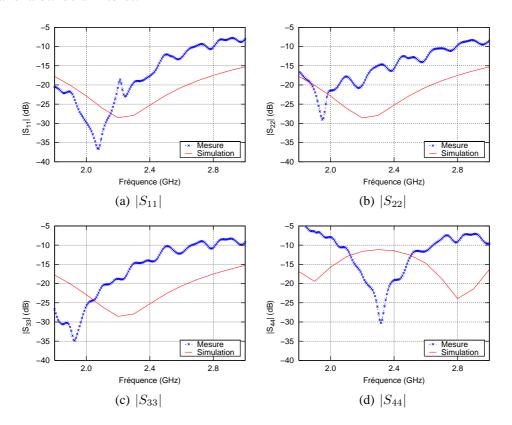

| 7.7  | Coefficients de réflexion du GBV                                                      | 159 |

| 7.8  | Coefficients de transmission du GBV                                                   | 160 |

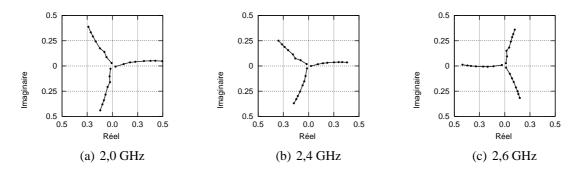

| 7.9  | Déphasages obtenus para simulation (S) et mesure (M) entre les accès 2, 4             |     |

|      | et 6 du GBV.                                                                          | 161 |

| 7.10 | Masque du démodulateur                                                                | 162 |

| 7.11 | Coefficients de réflexion du démodulateur                                             | 163 |

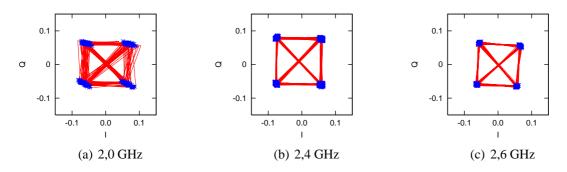

| 7.12 | Signal QPSK -20 dBm/100 kS/s demodulé                                                 | 163 |

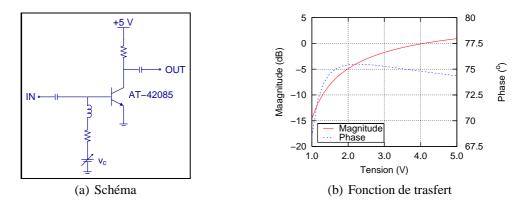

| 7.13 | Schéma simplifié et fonction de transfert de l'atténuateur                            | 164 |

| 7.14 | Masque du modulateur                                                                  | 164 |

| 7.15 | Coefficients de réflexion du modulateur                                               | 165 |

| 7.16 | Bases vectorielles pour des tensions de contrôle variant de 0,7 à 4 V                 | 166 |

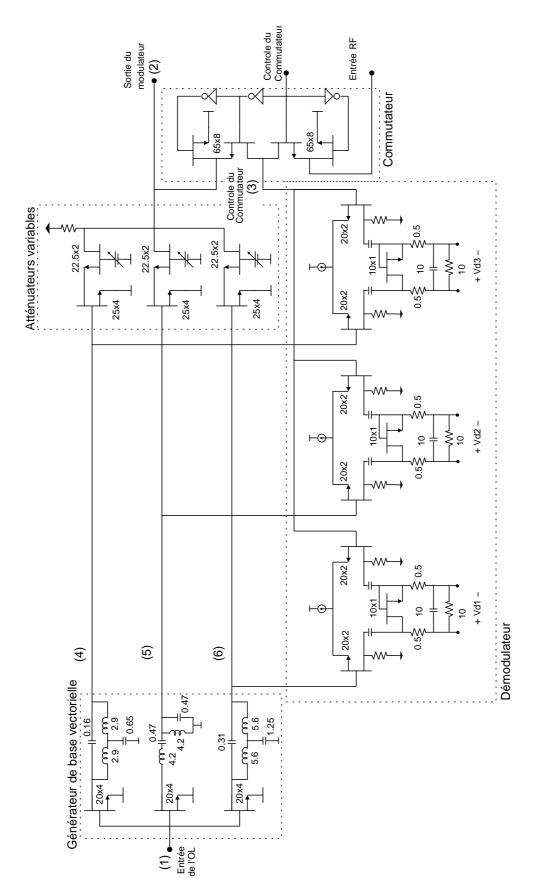

| 7.17 | Schéma électrique de l'émmeteur-récepteur « five-port » en technologie AsGa.          |     |

|      | Les valeurs des résistances sont en $k\Omega$ , des inducteurs en nH et des capacités |     |

|      | en pF                                                                                 | 167 |

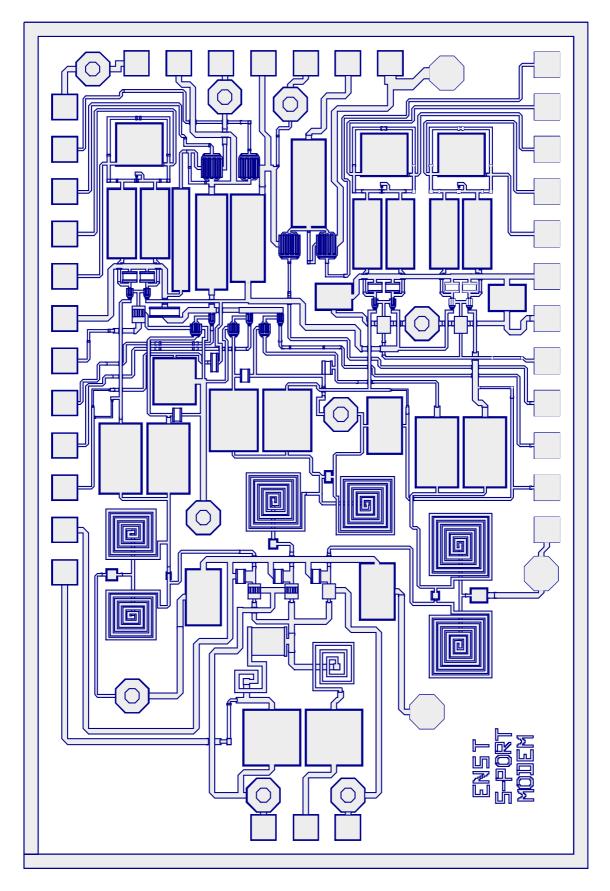

| 7.18 | Masque du MMIC émetteur-récepteur                                                     | 168 |

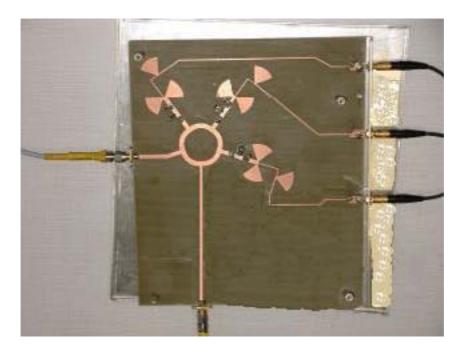

| 7.19 | Photo du banc de mesure                                                               | 170 |

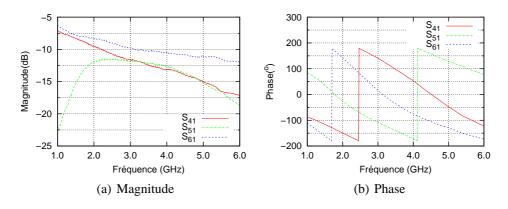

| 7.20 | Coefficients de transmission du GBV mesurés à la sortie du modulateur                 | 170 |

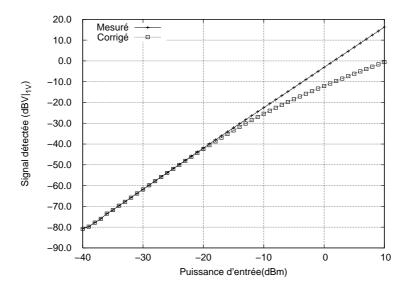

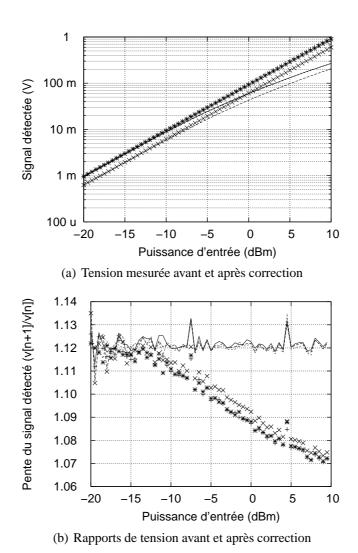

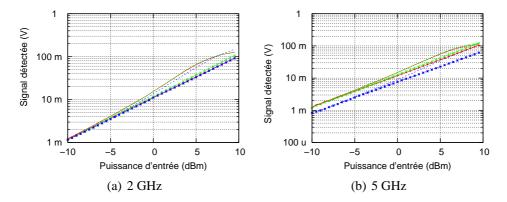

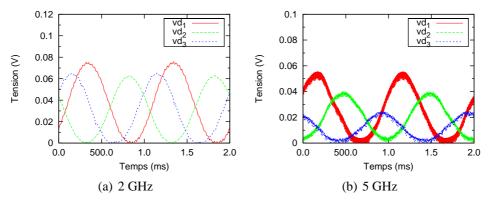

| Tensions détectées aux sorties des détecteurs quadratiques avant (lignes) et |                                              |

|------------------------------------------------------------------------------|----------------------------------------------|

| après (lignes avec des points) linéarisation                                 | 171                                          |

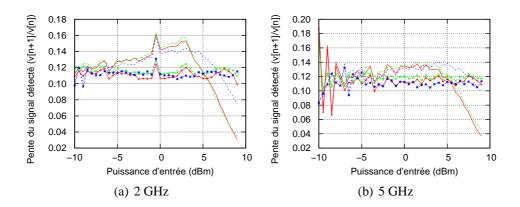

| Pente des tensions détectées aux sorties des détecteurs quadratiques avant   |                                              |

| (lignes) et après (lignes avec des points) linéarisation                     | 172                                          |

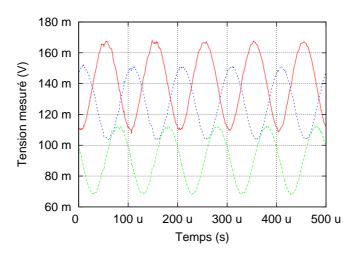

| Tensions mesurées aux sorties des détecteurs                                 | 173                                          |

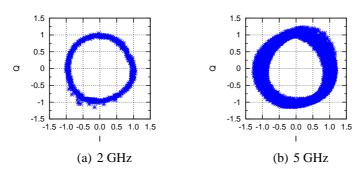

| Représentation sur le plan complexe du décalage de fréquence de 1 kHz entre  |                                              |

| les signaux RF                                                               | 173                                          |

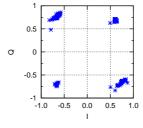

| Diagramme de constellation d'un signal QPSK à -10 dBm et 2,0 GHz, avec       |                                              |

| débit de 1 kS/s démodulé avec l'aide du MMIC « five-port »                   | 173                                          |

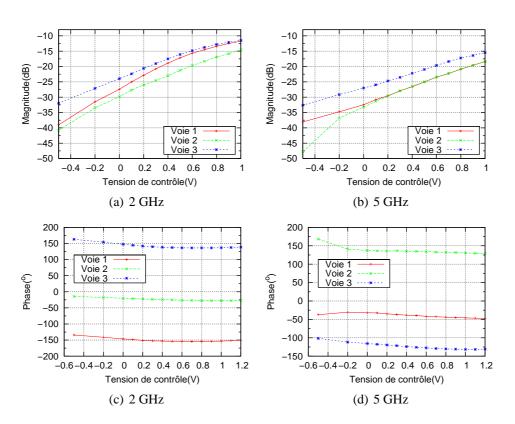

| Coefficient de transmission du circuit modulateur à 2 GHz et à 5 GHz         | 175                                          |

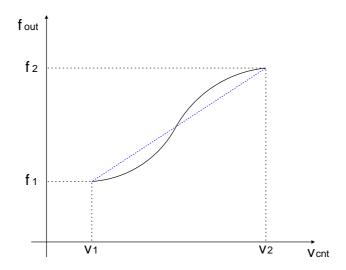

| Fonction de transfert d'un VCO réel                                          | 197                                          |

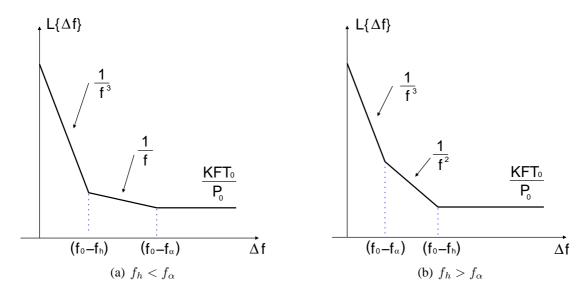

| Bruit de phase d'un oscillateur d'après le modèle de Lesson                  | 199                                          |

| Spectre du signal de sortie du VCO lorsque le gain de la boucle est K=0,2 .  | 202                                          |

| Bruit de phase du signal de sortie du VCO lorsque le gain de la boucle est   |                                              |

| K=0,2                                                                        | 203                                          |

| Spectre du signal de sortie du VCO lorsque le gain de la boucle est K=0,5 .  | 204                                          |

| Bruit de phase du signal de sortie du VCO lorsque le gain de la boucle est   |                                              |

| K=0,5                                                                        | 205                                          |

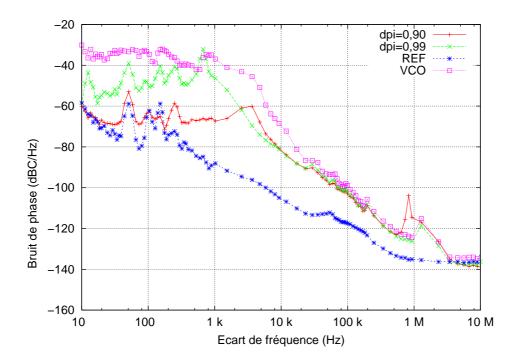

| Bruit de phase du signal de sortie du VCO lorsque $d_{pi}$ =0,90             | 205                                          |

| Bruit de phase du signal de sortie du VCO lorsque $d_{pi}$ =0,99             | 206                                          |

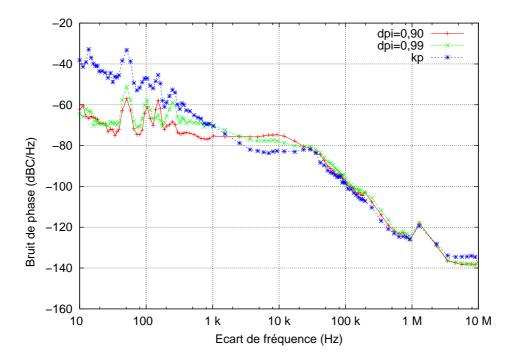

| Bruit de phase du signal de sortie du VCO lorsque K=0,2 pour les PLLs        |                                              |

| d'ordre 1 et proportionnel et intégrateur                                    | 206                                          |

| Bruit de phase du signal de sortie du VCO lorsque K=0,5 d'ordre 1 et pro-    |                                              |

| portionnel et intégrateur                                                    | 207                                          |

| Diagramme d'un modulateur basé sur un réfléctomètre à cinq accès             | 210                                          |

|                                                                              | après (lignes avec des points) linéarisation |

| C.2  | Génération d'une base vectorielle pour la représentation de signaux de deux        |     |

|------|------------------------------------------------------------------------------------|-----|

|      | dimensions                                                                         | 214 |

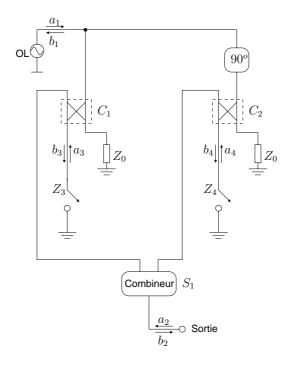

| C.3  | Génération de la base vectorielle de $90^o$                                        | 214 |

| C.4  | Génération de la base vectorielle de $90^o$ avec correction                        | 215 |

| C.5  | Génération de la base vectorielle de $120^o$                                       | 216 |

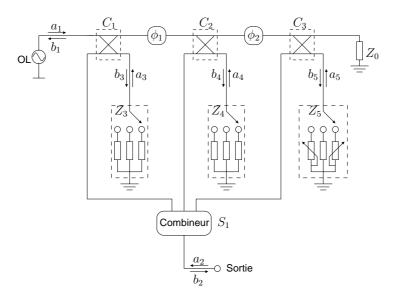

| C.6  | Structure parallèle non-isolée                                                     | 217 |

| C.7  | Structure parallèle semi-isolée                                                    | 218 |

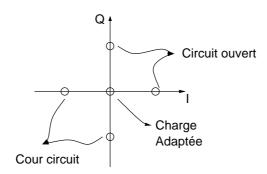

| C.8  | Base vectorielle en fonction des charges                                           | 219 |

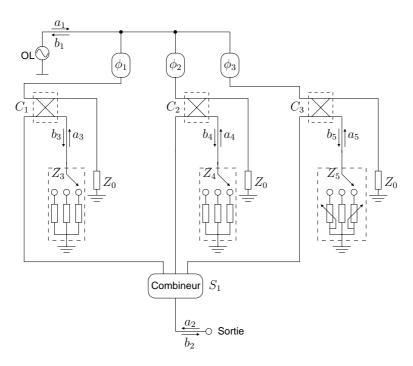

| C.9  | Structure parallèle isolée par des circulateurs capable de générer base de $120^o$ | 220 |

| C.10 | Résultats des simulation du circuit de la Figure C.9                               | 221 |

| C.11 | Structure série semi-isolée                                                        | 222 |

| C.12 | Structure parallèle isolée                                                         | 223 |

| C.13 | Structure parallèle isolée par des circulateurs                                    | 224 |

| C.14 | Structure parallèle isolée par des circulateurs                                    | 225 |

| C.15 | Résultats de simulation du modulateur parallèle isolé par des circulateurs .       | 225 |

| C.16 | Structure parallèle isolée par des circulateurs capable de générer base de $120^o$ | 226 |

| C.17 | Base vectorielle de $120^o$ en fonction des charges                                | 227 |

| C.18 | Structure série isolée                                                             | 228 |

| C.19 | Structure qui réunit les caractéristiques souhaitées pour réaliser la fonction     |     |

|      | modulation et démodulation                                                         | 229 |

# Liste des tableaux

| 1.1 | Paramètres des circuits simulés                                                   | 21  |

|-----|-----------------------------------------------------------------------------------|-----|

| 1.2 | Constantes de calibrage des circuits simulés                                      | 21  |

| 1.3 | Désappariemment de phase                                                          | 22  |

| 1.4 | Désappariemment de gain                                                           | 22  |

| 2.1 | Constantes de la jonction «five-port »                                            | 40  |

| 2.2 | Valeur moyenne et écart type de la valeur absolue de $z(t) \ \ldots \ \ldots$     | 41  |

| 2.3 | Valeur moyenne et écart type de la dérivé de la phase de $z(t) \ \ldots \ \ldots$ | 42  |

| 2.4 | Méthodes de calibrage                                                             | 44  |

| 4.1 | Résolutions effectives des CANs pour les deux expériences                         | 68  |

| 4.2 | Résolutions effectives des tables pour les deux scénarios de mesure sans          |     |

|     | conditionnement                                                                   | 70  |

| 4.3 | Résolutions effectives des tables pour les deux scénarios de mesure lorsque       |     |

|     | les LUT sont mises à jour en fonction de la dynamique du signal                   | 70  |

| 5.1 | Coefficients du polynôme d'extension de la région de détection quadratique        |     |

|     | des détecteurs de puissance                                                       | 108 |

| 5.2 | Coefficients de calibrage de l'anneau à cinq branches                             | 108 |

| 5.3 | Paramètres du filtre de la boucle utilisés pendant l'expérience                   | 128 |

# Introduction générale

Nous vivons actuellement dans une société de consommation où le jeu de séduction des fournisseurs de services ne s'impose pas de limites pour conquérir des nouveaux marchés. Après le déploiement des communications mobiles de première et de deuxième générations où la transmission de la voix et la mobilité étaient les vedettes, nous assistons aujourd'hui à une course effrénée aux innovations technologiques visant offrir la mobilité à toute sorte de service. Les exemples plus récents sont le 3G, le Wi-Fi et le Bluetooth, à quoi s'ajoutent les services audiovisuels DAB, DVB et DRM. Bien que ces marchés soient encore en voie de développement, le WiMax et la 4G sont à l'ordre du jour dans les laboratoires de recherche. Etant donné ce scénario, l'idée d'accorder au consommateur l'accès à ces services en conjuguant dans un appareil de radiocommunication unique cette gamme de standards nous paraît essentielle.

Un système couvrant une gamme large de services doit opérer dans une plage de fréquences ample et décoder plusieurs modes. C'est dans ce contexte que la technique *« five-port »* se présente comme une alternative prometteuse. Cette technique est dérivée du réflectomètre *« six-port »* , un dispositif qui calcule précisément le rapport complexe entre deux signaux hyperfréquences à partir de la mesure des valeurs de puissance aux sorties d'un circuit interférométrique à six accès. Le *« five-port »* s'applique également aux systèmes radars, aux systèmes de détermination de la direction d'arrivée de signaux RF, aux démodulateurs homodynes et, comme nous proposons dans ce travail, aux boucles à verrouillage de phase et de récupération de porteuse.

Les corrélateurs cartésiens classiques projettent le vecteur représentant le signal que l'on veut démoduler sur une base composée de deux vecteurs orthogonaux. En revanche, le corrélateur *« five-port »* effectue cette projection sur une « base » à trois vecteurs décalés en phase idéalement de 120°. Grâce à la redondance introduite par le troisième vecteur, le corrélateur *« five-port »* se présente moins sensible aux désappariements de phase et d'amplitude, fournit une variable permettant d'estimer les produits inter-modulation d'ordre pair et peut fonctionner dans une bande de fréquences large. Ces caractéristiques ne sont exploitables que si l'on applique une procédure de calibrage.

Ce rapport de thèse, comportant sept chapitres, apporte quelques contributions au domaine de la radiocommunication mobile, notamment aux émetteurs-récepteurs multi-bande et multi-mode. Le premier apport original de ce travail est l'application de la technique *« five-port »* aux boucles à verrouillage de phase reconfigurables. Cette reconfigurabilité est exploitée dans une boucle de récupération de porteuse multi-mode, un élément fondamental dans les récepteurs. Également originale est la méthode de caractérisation mise en place pour calibrer les corrélateurs *« five-port »* . Finalement nous proposons et évaluons une nouvelle architecture d'émetteur-récepteur fondée sur une base à trois vecteurs.

Nous consacrons le premier chapitre à la présentation du corrélateur *« five-port »* en partant de ses origines dans les réflectomètres *« six-port »* . Nous proposons par la suite un modèle inspiré d'une interprétation géométrique du principe de fonctionnement du *« five-port »* . Par ailleurs, nous effectuons une analyse de sensibilité visant comparer les systèmes à six et à cinq accès suivi d'une évaluation de l'impact des désappariements de phase et d'amplitude.

La complexité des méthodes de caractérisation des systèmes « six-port » et « five-port » nous a amenée à développer une nouvelle procédure de calibrage de faible complexité de calcul, que nous décrivons dans le deuxième chapitre.

Au cours du troisième chapitre nous faisons un rappel sur les détecteurs quadratiques et présentons la technique de caractérisation des détecteurs que nous adoptons.

Le quatrième chapitre porte sur le traitement numérique nécessaire aux corrélateurs *« five-port »* . Nous proposons une procédure qui s'utilise des tables de correspondance pour accélérer le temps de calcul. Puis, les erreurs qui se produisent lors des procédés de numérisation des valeurs sont évaluées.

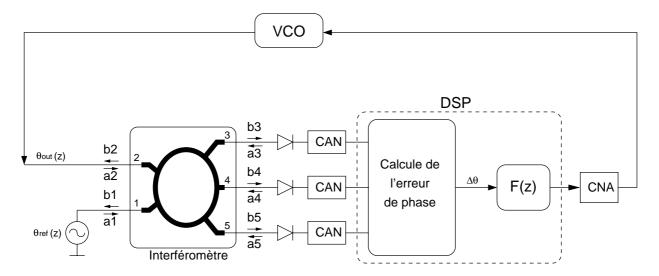

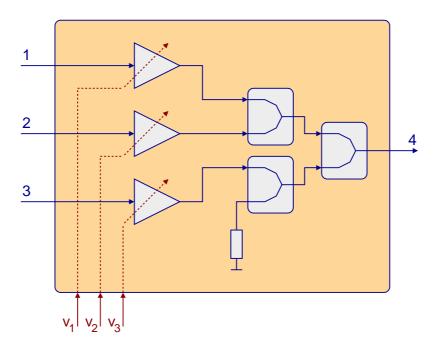

La boucle à verrouillage de phase (PLL) utilisant un corrélateur *«five-port »* comme comparateur de phase est exposée dans le quatrième chapitre. Cette boucle exploite le processeur numérique du corrélateur *«five-port »* pour y intégrer le filtre de boucle, ce qui rend la PLL reconfigurable. Nous démontrons la faisabilité de cette boucle par le biais d'un prototype à la fréquence de 2 GHz composé d'un circuit *«five-port »* construit en technologie micro-ruban, des CANs et CNAs, d'un VCO et d'un circuit de traitement numérique (DSP). Des résultats de mesure de bruit de phase, de spectre et de temps d'acquisition sont présentés validant ainsi le système proposé.

Le sixième chapitre porte sur une boucle de récupération de porteuse reconfigurable multi-mode dont la base est la PLL du chapitre 5. Pour répondre à plusieurs types de modulation, l'implémentation d'une boucle de récupération de porteuse devient complexe, notamment à cause du nombre élevé de composants. Dans notre approche, nous remplaçons ces composants par des tables stockées en mémoire, rendant le système flexible et reconfigurable. Une expérience mise au point pour la modulation BPSK a fourni des résultats de mesures qui vérifient le principe du système proposé.

Avant de conclure nous proposons dans le septième chapitre une architecture originale d'émetteur-récepteur basée sur la technique *«five-port »*. Dans cette architecture nous avons divisé le circuit en trois modules principaux, à savoir le générateur de base vectorielle, le démodulateur et le modulateur. Nous validons l'architecture à partir de deux prototypes fonctionnant respectivement dans les bandes 2,0 - 2,6 GHz et 1,8 - 5,5 GHz. Le premier a été réalisé en technologie micro-ruban et le deuxième, de dimension 2 mm x 3 mm, a été construit en technologie intégrée sur un substrat de Arseniure de Gallium.

## Chapitre 1

# Le corrélateur d'ondes «five-port »

### 1.1 Introduction

Le réflectomètre « six-port » est apparu au cours des années soixante-dix dans le domaine de l'instrumentation et de la mesure [1, 2, 3]. Il était alors employé comme un analyseur de réseaux à faible coût et de haute précision pour mesurer les charges d'étalonnage des analyseurs vectoriels hétérodynes [4]. Son faible coût et la qualité des mesures étaient dûs à la simplicité de ses circuits qui employaient des détecteurs de puissance au lieu des mélangeurs utilisés dans les systèmes hétérodynes. Cette technique de mesure a été améliorée dans les années suivantes par divers chercheurs, soit par le biais du perfectionnement des méthodes de calibrage [5, 6, 7, 8], soit par la proposition de nouvelles architectures [9, 10, 11]

Cependant, la technique *« six-port »* ne sort des laboratoires de métrologie pour gagner les applications destinées au grand public que durant les années quatre-vingt-dix. A son utilisation comme réflectomètre s'ajoute celle de corrélateur d'ondes dans les radars d'aide à la conduite [12, 13, 14], ainsi que de démodulateur homodyne [15, 16, 17, 18, 19]. Il est également employé dans des systèmes de détermination de direction d'arrivée de signaux RF [20, 21] et comme nous proposons dans ce travail, dans les boucles à verrouillage de phase et de récupération de porteuse.

Contrairement à l'analyse de réseaux, dans les applications de télécommunications, la puissance du signal local utilisé comme référence est toujours constante. Cette particularité a été prise en compte pour simplifier le circuit du corrélateur d'ondes, ce qui signifie qu'un accès de sortie communément utilisé pour fournir l'information sur la puissance du signal de référence a été supprimé, donnant naissance au corrélateur à cinq accès, ou corrélateur *« five-port »* . En vérité, la puissance du signal de référence est mesurée une seule fois pendant la procédure de calibrage. Cette simplification engendre une réduction considérable du temps de calcul des composantes cartésiennes de l'enveloppe complexe du signal modulé reçu.

Dans les sections qui suivent, après avoir fait un rappel sur le fonctionnement du réflectomètre « six-port » , nous mettons au point un modèle du corrélateur « five-port » qui sert à analyser son comportement. Ensuite, nous introduisons les équations qui décrivent le comportement du corrélateur suivies d'une étude de la sensibilité du système à cinq accès vis-à-vis de la variation de la puissance du signal de référence. Avant de conclure le chapitre, nous analysons l'influence du cinquième accès sur les erreurs de mesure.

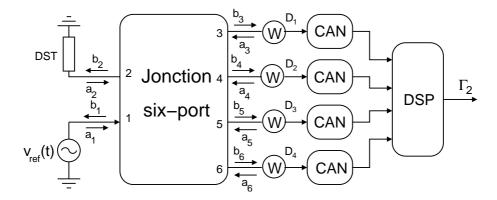

### 1.2 Le réflectomètre « six-port »

Le réflectomètre « six-port » est un dispositif de mesure qui permet de déterminer les valeurs des impédances complexes en utilisant seulement des mesures de puissances suivies d'un traitement numérique des données obtenues. Son schéma de principe est montré sur la Fig. 1.1 d'où nous pouvons constater que ses composants de base sont : un circuit linéaire à six accès, quatre détecteurs de puissance, quatre convertisseurs de signaux analogiques en numériques (CAN) et un circuit de traitement numérique (DSP de l'anglais Digital Signal Processing). Un signal de référence est relié à l'accès 1 et le dispositif sous test (DST), dont nous voulons connaître l'impédance, est relié à la porte 2. Les quatre capteurs de puissance reliés aux portes 3, 4, 5 et 6 mesurent chacun la puissance d'une combinaison linéaire entre les ondes incidente et réfléchie à l'accès 2 déphasées et atténuées différemment selon la

porte de mesure. La valeur du coefficient de réflexion du dispositif sous test est déterminée à partir des équations qui relient les valeurs de puissances et les constantes de calibrage du réflectomètre.

FIG. 1.1 – Schéma de principe du réflectomètre « six-port »

### 1.2.1 Les équations régissant le comportement du réflectomètre « sixport »

Considérons une jonction arbitraire linéaire de six portes avec des détecteurs de puissance connectés aux portes 3, 4, 5 et 6, comme celle illustrée sur la Fig. 1.1. Nous pouvons écrire :

$$b_i = \sum_{j=1}^{6} S_{ij} a_j , \qquad i = 1 \cdots 6$$

(1.1)

où  $a_i$  et  $b_i$  sont les pseudo-ondes de puissance incidentes et émergeantes de la jonction, et  $S_{ij}$  sont les paramètres de dispersion.

Le coefficient de réflexion du détecteur connecté à la porte j est défini comme :

$$a_j = b_j \Gamma_j , \qquad j = 3 \cdots 6$$

(1.2)

Avec 10 équations (1.1, 1.2) et douze variables  $(a_i, b_i)$ , il est possible d'écrire donc,

$$b_i = A_i a_2 + B_i b_2 , \qquad i = 3 \cdots 6$$

(1.3)

où  $A_i$  et  $B_i$  sont les constantes qui déterminent principalement les caractéristiques du réflectomètre « six-port » .

De plus, les valeurs de puissance détectées aux sorties de la jonction peuvent s'écrire comme suit :

$$P_i = |b_i|^2 (1 - |\Gamma_i|^2) = |A_i a_2 + B_i b_2|^2 (1 - |\Gamma_i|^2) , \qquad i = 3 \cdots 6$$

(1.4)

Il est fort courant de concevoir des réfléctomètres « six-port » de sorte que la puissance mesurée par un des quatre détecteurs dépende exclusivement de la pseudo-onde  $b_2$ . Ici, nous choisissons le détecteur relié à l'accès 6 et par conséquent  $A_6=0$ , ce qui nous permet d'écrire :

$$P_6 = |B_6 b_2|^2 (1 - |\Gamma_6|^2) \tag{1.5}$$

En prenant le rapport entre (1.4) et (1.5) et en effectuant quelques opérations, nous parvenons à l'équation suivante :

$$|\Gamma_2 - q_i|^2 = \left| \frac{B_6}{A_i} \right|^2 \left( \frac{1 - |\Gamma_6|^2}{1 - |\Gamma_i|^2} \right) \frac{P_i}{P_6}$$

(1.6)

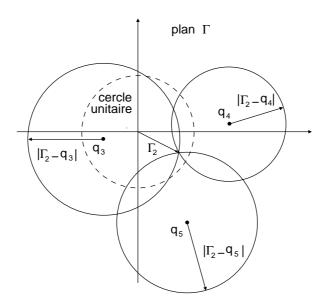

où  $q_i = -\frac{B_i}{A_i}$  et  $\Gamma_2 = \frac{a_2}{b_2}$ . L'équation (1.6) décrit trois cercles centrés en  $q_i$  dont les rayons sont donnés par  $\left|\frac{B_6}{A_i}\right| \sqrt{\frac{1-|\Gamma_6|^2}{1-|\Gamma_i|^2}} \sqrt{\frac{P_i}{P_6}}$ . Nous constatons à partir de la Fig. 1.2 et de (1.6) que l'intersection des trois cercles donne le vecteur qui représente le coefficient de réflexion  $\Gamma_2$  du dispositif sous test relié à l'accès 2.

L'emplacement correct des points  $q_i$  dans le plan complexe est un critère important. Pour la mesure du coefficient de réflexion de charges passives, le module des vecteurs représentant les points  $q_i$  doit être de l'ordre de 1,5 et leur déphasage relatif doit s'approcher de  $\pm 120^\circ$

FIG. 1.2 – Détermination de  $\Gamma_2$  à partir de l'intersection de trois cercles

[3, 4].

# 1.3 Le corrélateur «five-port »

Comme nous l'avons dit précédemment, dans les applications de radiocommunication, les variations de la valeur de la puissance du signal local utilisé comme référence (oscillateur local - OL) restent négligeables. C'est pourquoi le fait d'utiliser une jonction à six accès au lieu de cinq n'ajoute pas d'avantages, vu que  $P_3$  est constante dans (1.6) et peut être mesurée pendant le calibrage.

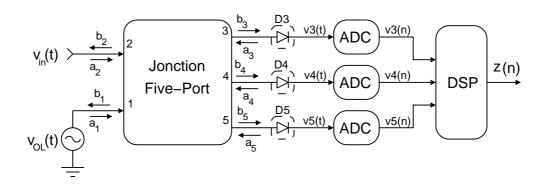

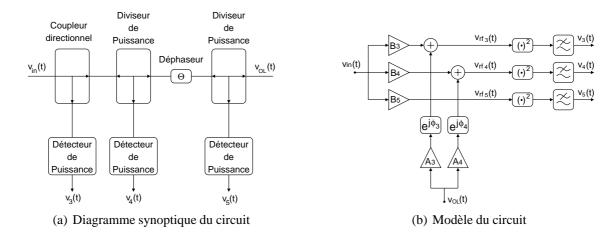

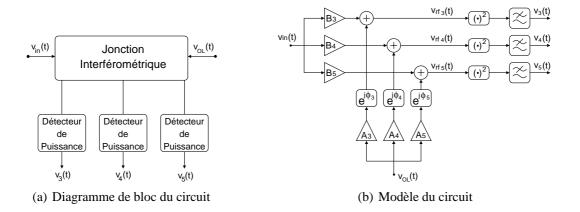

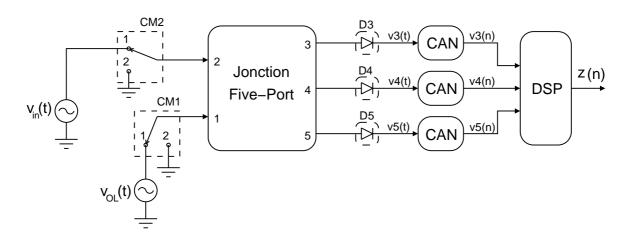

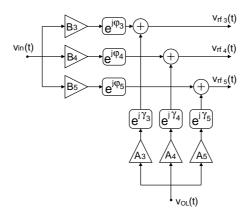

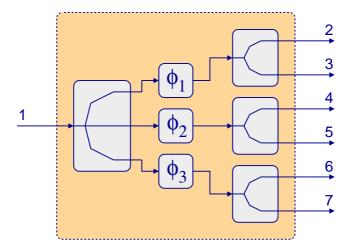

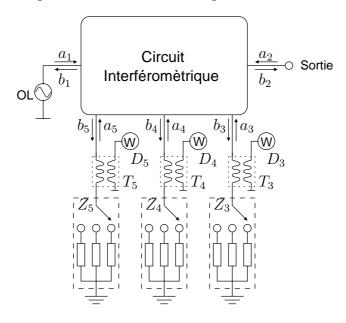

La Fig. 1.3 illustre le schéma de principe d'un corrélateur « five-port » . Ses composants principaux sont une jonction à cinq accès, trois détecteurs de puissance (D3, D4 et D5), trois convertisseurs de signaux analogiques en numériques et un module de traitement de signaux (DSP). Une source de référence  $v_{OL}(t)$  est reliée à l'accès 1, et comme nous pouvons remarquer, le dispositif sous test présent dans le schéma de la Fig. 1.1 a été remplacé par un signal  $v_{in}(t)$  arrivant à l'accès 2 . Nous supposons ici que les accès 1 et 2 sont adaptés.

Faisons l'hypothèse que les spectres des signaux  $v_{OL}(t)$  et  $v_{in}(t)$  sont centrés autour de

FIG. 1.3 – Schéma synoptique du corrélateur «five-port »

la fréquence  $f_c$ . Leurs représentations passe-bande sont alors données par :

$$v_{OL}(t) = \Re\left[V_{OL}e^{j2\pi f_c t}\right] \tag{1.7}$$

$$v_{in}(t) = \Re\left[z(t)e^{j2\pi f_c t}\right]$$

(1.8)

où  $V_{OL}$  est l'amplitude de  $v_{OL}(t)$  et  $z(t)=a(t)e^{j\theta(t)}$  est le signal passe-bas équivalent de  $v_{in}(t)$  (enveloppe complexe).

La jonction - souvent un circuit interférométrique linéaire - réalise une addition vectorielle des signaux  $v_{OL}(t)$  et  $v_{in}(t)$ . Autrement dit, on retrouve les deux signaux entrants superposés avec différents déphasages aux sorties de la jonction. Ces signaux peuvent être exprimés comme :

$$v_{rf_i}(t) = \Re \left[ \alpha_i V_{OL} e^{j2\pi f_c t} + \beta_i z(t) e^{j2\pi f_c t} \right]$$

$$\tag{1.9}$$

où  $\alpha_i$  et  $\beta_i$  sont des constantes complexes dépendantes des caractéristiques de la jonction.

Afin de simplifier l'étude du corrélateur *« five-port »* , nous développons un modèle linéaire de sa partie hyperfréquences. Ceci peut être appliqué pour étudier n'importe quelle architecture de jonction à cinq accès.

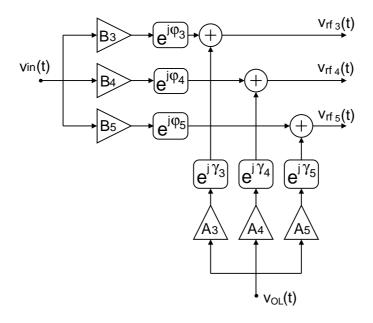

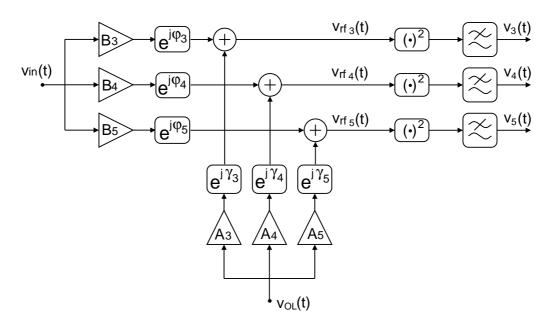

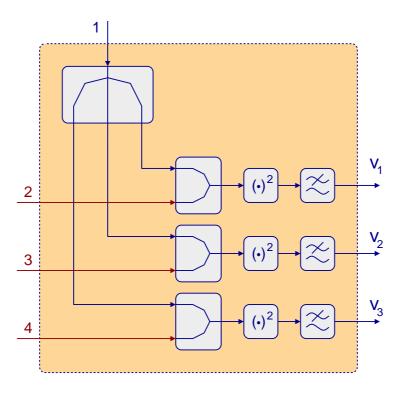

### 1.3.1 Le modèle du corrélateur «five-port »

A partir de (1.9), nous pouvons déduire que la jonction à cinq accès utilisée dans un corrélateur «five-port » se comporte comme le modèle illustré sur la Fig. 1.4. Les signaux  $v_{OL}(t)$  et  $v_{in}(t)$  sont chacun divisés en trois voies. Chacune des voies introduit un gain et un déphasage symbolisés par  $A_i$ ,  $B_i$  et  $\gamma_i$ ,  $\varphi_i$ , respectivement les modules et les arguments des constantes complexes de (1.9)  $\alpha_i$  et  $\beta_i$ . Ensuite, chacune des voies provenant de l'OL est sommée à une voie dérivée de  $v_{in}(t)$ . Finalement nous retrouvons les trois signaux de sortie de la jonction  $v_{rfi}(t)$ .

FIG. 1.4 – Modèle de la jonction hyperfréquences du corrélateur « five-port »

La conception de la jonction consistera donc à dimensionner les valeurs de  $\alpha_i$  et  $\beta_i$  de sorte que la base vectorielle<sup>1</sup> résultante (les points  $q_i$  du refléctomètre « six-port » ) soit bien équilibrée.

Ajoutons au schéma de la Fig. 1.4, les détecteurs quadratiques et les filtres passe-bas (équivalents aux capteurs de puissance du refléctomètre « six-port » comme il est montré

<sup>&</sup>lt;sup>1</sup>Rigoureusement, la base vectorielle d'un espace vectoriel d'ordre deux est composée par deux vecteurs linéairement indépendants. Cependant, nous allons continuer à utiliser le terme base vectorielle pour faire référence aux sous-espaces de trois vecteurs linéairement dépendants formés par les corrélateurs « five-port » .

FIG. 1.5 – Modèle complet du corrélateur « five-port »

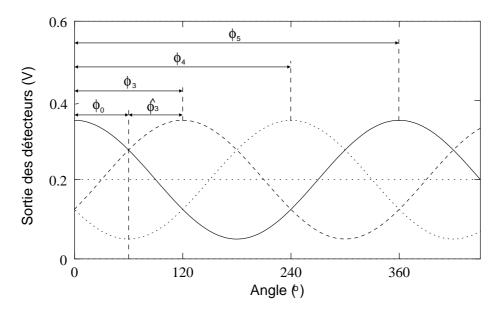

dans le chapitre 3) pour parvenir au modèle illustré sur la Fig. 1.5. Ceci va nous permettre d'exprimer les équations des tensions  $v_3(t)$ ,  $v_4(t)$  et  $v_5(t)$  par :

$$v_i(t) = [v_{rf_i}(t)]^2 * h_{pb}(t)$$

(1.10)

où  $h_{pb}(t)$  est la réponse impulsionelle des filtres passe-bas et \* est l'opérateur intégral de convolution. Remplaçons (1.9) dans (1.10) pour obtenir :

$$v_i(t) = \{A_i V_{OL} \cos(2\pi f_c t + \gamma_i) + B_i a(t) \cos[2\pi f_c t + \theta(t) + \varphi_i]\}^2 * h_{pb}(t)$$

(1.11)

$$v_{i}(t) = \begin{cases} \frac{A_{i}^{2}V_{OL}^{2}}{2} + \frac{B_{i}^{2}a^{2}(t)}{2} + A_{i}B_{i}V_{OL}a(t)\cos[\theta(t) + \varphi_{i} - \gamma_{i}] + \\ \frac{A_{i}^{2}V_{OL}^{2}}{2}\cos(4\pi f_{c}t + 2\gamma_{i}) + \frac{B_{i}^{2}a^{2}(t)}{2}\cos[4\pi f_{c}t + 2\theta(t) + 2\varphi_{i}] + \\ A_{i}B_{i}V_{OL}a(t)\cos[4\pi f_{c}t + \theta(t) + \varphi_{i} + \gamma_{i}] \} * h_{pb}(t) \end{cases}$$

(1.12)

Nous constatons à partir de (1.12) que les signaux  $v_{rf_i}(t)$ , après avoir été soumis aux détecteurs de loi quadratique, présentent des composantes en bande de base (termes 1, 2 et 3) ainsi que des composantes harmoniques de  $f_c$  (termes 4, 5 et 6).

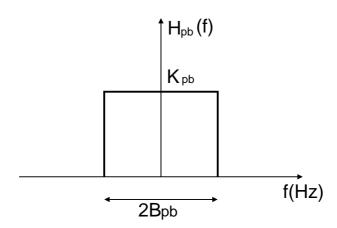

Supposons maintenant que la réponse fréquentielle du filtre passe-bas (Fig. 1.6) est telle que :

$$H_{pb}(f) = \begin{cases} K_{pb} & (-B_{pb} < f < B_{pb}); B_{pb} << f_c \\ 0 & (ailleurs) \end{cases}$$

(1.13)

où  $2B_{pb}$  est la bande passante de z(t) en Hz. Les tensions  $v_i(t)$  n'auront que des composantes en bande de base comme le montrent les expressions suivantes :

FIG. 1.6 – Réponse fréquentielle du filtre passe-bas

$$v_{3}(t) = K_{pb_{3}} \frac{A_{3}^{2} V_{OL}^{2}}{2} + K_{pb_{3}} \frac{B_{3}^{2} a^{2}(t)}{2} + K_{pb_{3}} A_{3} B_{3} V_{OL} a(t) \cos[\theta(t) - \phi_{3}]$$

$$v_{4}(t) = K_{pb_{4}} \frac{A_{4}^{2} V_{OL}^{2}}{2} + K_{pb_{4}} \frac{B_{4}^{2} a^{2}(t)}{2} + K_{pb_{4}} A_{4} B_{4} V_{OL} a(t) \cos[\theta(t) - \phi_{4}]$$

$$v_{5}(t) = K_{pb_{5}} \frac{A_{5}^{2} V_{OL}^{2}}{2} + K_{pb_{5}} \frac{B_{5}^{2} a^{2}(t)}{2} + K_{pb_{5}} A_{5} B_{5} V_{OL} a(t) \cos[\theta(t) - \phi_{5}]$$

$$(1.14)$$

avec  $\phi_i = -(\varphi_i - \gamma_i)$ .

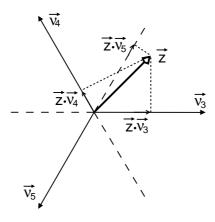

Une analyse plus rigoureuse des équations nous permet de donner une interprétation

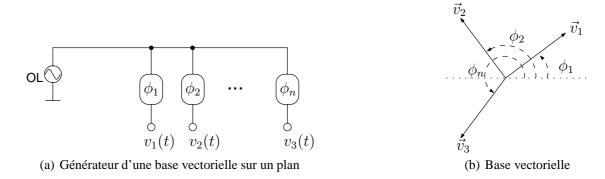

géométrique de (1.14): les termes  $a(t)\cos[\theta(t)-\phi_i]$  sont, en vérité, des projections du vecteur  $\vec{z}=a(t)e^{j\theta(t)}$  sur les vecteurs  $\vec{\nu_i}=e^{j\phi_i}$ . L'opération du corrélateur «five-port » est donc interprétée comme étant la projection orthogonale du signal RF reçu sur une base non-cartésienne de trois vecteurs comme illustré sur la Fig. 1.7.

FIG. 1.7 – Projection de  $\vec{z}$  sur la base  $[\vec{\nu_3} \ \vec{\nu_4} \ \vec{\nu_5}]^T$

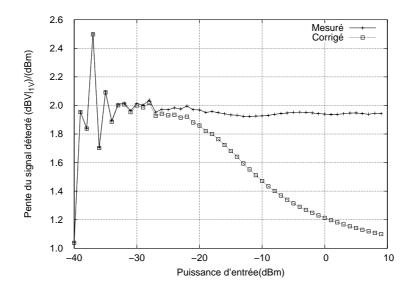

Les trois équations en (1.14) forment un système linéaire de trois variables ( $a^2(t)$ , a(t) et  $\theta(t)$ ) du type  $v_M = As_M + B$ , avec :

$$v_{M} = \begin{bmatrix} v_{3}(t) \\ v_{4}(t) \\ v_{5}(t) \end{bmatrix}, A = \begin{bmatrix} R_{3} & S_{3}\cos\phi_{3} & S_{3}\sin\phi_{3} \\ R_{4} & S_{4}\cos\phi_{4} & S_{4}\sin\phi_{4} \\ R_{5} & S_{5}\cos\phi_{5} & S_{5}\sin\phi_{5} \end{bmatrix}, s_{M} = \begin{bmatrix} n(t) \\ z_{I}(t) \\ z_{Q}(t) \end{bmatrix}, B = \begin{bmatrix} K_{3} \\ K_{4} \\ K_{5} \end{bmatrix}$$

(1.15)

avec  $R_i = \frac{1}{2}K_{pb_i}B_i^2$ ,  $S_i = K_{pb_i}A_iB_iV_{OL}$ ,  $K_i = \frac{1}{2}K_{pb_i}A_i^2V_{OL}^2$ ,  $z_I(t) = a(t)\cos\theta(t)$ ,  $z_Q(t) = a(t)\sin\theta(t)$  et  $n(t) = a^2(t)$ .

L'intérêt du corrélateur «five-port » est de permettre la détermination de z(t), ce qui est possible en faisant  $A^{-1}(v_M - B) = A^{-1}As_M = s_M$  pour obtenir  $z_I(t)$  et  $z_Q(t)$ , les composantes de la représentation rectangulaire de z(t). Les éléments de la matrice  $A^{-1}$  sont trouvés par une des diverses procédures de calibrage rencontrées dans la littérature [5, 6, 7].

Jusqu'ici, nous avons considéré que l'amplitude du signal de l'oscillateur local res-

tait constante. Néanmoins, dans un cas pratique cela n'est pas toujours vrai puisque des phénomènes tels que la variation des valeurs des composantes due aux changements de température entraînent des variations sur l'amplitude des signaux. La section suivante porte sur l'effet de ces variations sur les valeurs estimées de z(t).

#### 1.3.2 L'influence des variations de $V_{OL}$ sur les mesures

Dans la section précédente nous avons vu que le vecteur  $s_M$  peut être estimé à partir des valeurs de mesure du vecteur  $v_M$  en faisant  $s_M = Cv_M + D$  avec

$$C = A^{-1} = \begin{bmatrix} r_N & s_N & t_N \\ r_I & s_I & t_I \\ r_Q & s_Q & t_Q \end{bmatrix} \qquad D = -A^{-1}B = \begin{bmatrix} k_N \\ k_I \\ k_Q \end{bmatrix}$$

(1.16)

Comme nous le montrons dans la section 2.2.2 qui décrit la méthode de calibrage proposée, la matrice C peut s'écrire comme  $V_{OL}C'$ , ainsi que  $D=V_{OL}^3D'$ . Il est donc possible de calculer la sensibilité de  $s_M$  vis-à-vis des variations de  $V_{OL}$  à partir de :

$$S_{s_M:V_{OL}} = \frac{\partial s_M}{\partial V_{OL}} \frac{V_{OL}}{s_M} = 1 + \frac{2D}{s_M}$$

$$\tag{1.17}$$

A partir de (1.17) et sachant que  $\Delta y \approx y \frac{\Delta x}{x} S_{y:x}$  [22], il est possible d'estimer les variations sur  $s_M$  en fonction des variations de  $V_{OL}$  avec l'expression :

$$\Delta s_M \approx \frac{\Delta V_{OL} S_{V_{OL}}^{s_M}}{V_{OL}} s_M = (s_M + 2D) \frac{\Delta V_{OL}}{V_{OL}}$$

(1.18)

avec  $\Delta V_{OL} \approx \partial V_{OL}$ .

Lorsque  $D \ll s_M$ , ce qui est souvent le cas, (1.18) est réduite à :

$$\Delta s_M \approx s_M \frac{\Delta V_{OL}}{V_{OL}} \tag{1.19}$$

qui se traduit par un gain sur le module de  $s_M$  sans variation sur la phase.

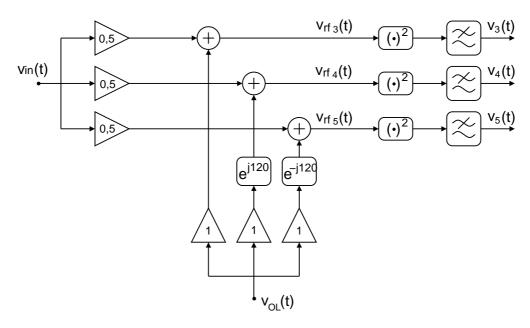

Pour illustrer la relation que nous venons d'établir, prenons le cas d'un corrélateur «five-port » dont le modèle est montré sur la Fig. 1.8. Ses paramètres sont :  $A_i=1,\,B_i=0,5,$   $K_{bp_i}=1,\,\phi_3=0,\,\phi_4=120^o$  et  $\phi_5=-120^o$ .

FIG. 1.8 – Modèle du corrélateur simulé « five-port »

Ce circuit a été simulé avec ADS® à la fréquence de 2 GHz dans les conditions suivantes :

#### 1. Calibrage:

$$- v_{OL}(t) = \Re \left\{ 0, 1e^{j(2\pi \times 2 \times 10^9)t} \right\}$$

$$- v_{in}(t) = \Re \left\{ 0, 1e^{j2\pi(2 \times 10^9 + 10^3)t} \right\}$$

Le choix de l'amplitude de l'OL de 0,1 V se justifie par le fait que cette valeur correspond à des niveaux de puissance typiques ( $\approx$  -13 dBm sur 50  $\Omega$ ) rencontrés dans les systèmes de télécommunication.

2. Mesure des valeurs de  $v_i(t)$  lorsque une variation de  $\pm 20\%$  est imposée à  $V_{ol}(t)$ :  $-v_{OL}(t)=\Re\left\{f(V_{OL})e^{j(2\pi\times2\times10^9)t}\right\}, \text{ avec une dérive monotone croissante de 20 \% definit par } f(V_{OL})=0,08+0,04\times10^3t\,; \quad 0< t< 1~ms. (1~ms~est~l'intervalle)$

de temps nécessaire pour varier l'amplitude de l'OL de  $\pm 20$  %).

$$- v_{in}(t) = \Re \left\{ 0,0001 e^{j\left[(2\pi \times 2 \times 10^9)t + \frac{\pi}{4}\right]} \right\}.$$

Le choix de l'amplitude de  $v_{in}(t)$  a été de 60 dB au dessous de celle de l'oscillateur local, ce qui est une condition fréquemment constatée dans la pratique.

Les constantes de calibrage trouvées sont :  $s_3 = -66, 67, s_4 = 66, 67, s_5 = 133, 33,$   $t_3 = 115, 19, t_4 = 115, 19, t_5 = -3, 77 \times 10^{-11}, k_I = -4, 01 \times 10^{-10}, k_Q = 1, 12 \times 10^{-12}.$  Nous remarquons que  $|k_I + jk_Q|$  est très inférieur à  $|s_3 + jt_3|, |s_4 + jt_4|$  et  $|s_5 + jt_5|$ , ce qui valide l'approximation faite en (1.19).

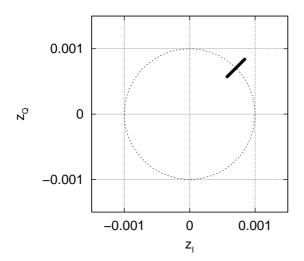

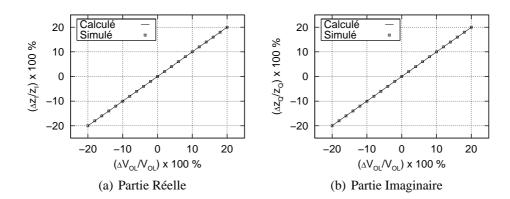

La valeur exacte de  $\vec{z}$  devait être  $0,001e^{j\frac{\pi}{4}}$ , cependant en faisant varier  $V_{OL}$  de  $\pm 20\%$ , une variation de la même proportion apparaît sur  $\vec{z}$ . Nous pouvons constater ce fait sur les Figs. 1.9 et 1.10, où la valeur de  $\vec{z}$  et de ses composantes réelle et imaginaire sont tracées. Les courbes affichent les données obtenues par simulation, mais aussi les valeurs calculées à partir de (1.18). Il n'y a pas d'écart entre prévision et simulation.

FIG. 1.9 – Valeurs de z(t) autour de sa valeur nominale  $0,001e^{j\frac{\pi}{4}}$  lorsque l'amplitude de l'oscillateur local varie de  $\pm 20\%$

A partir de l'analyse théorique et des résultats de simulation nous concluons que les instabilités de l'amplitude de l'oscillateur local ont un impact direct sur les valeurs de mesures. Pour les circuits bien dimensionnés où l'importance de D est moindre, un effet de gain ap-

FIG. 1.10 – Variations sur les valeurs des composantes réelle et imaginaire de z(t) autour de sa valeur nominale  $0,001e^{j\frac{\pi}{4}}$  lorsque l'amplitude de l'oscillateur local varie de  $\pm 20\%$ .

paraîtra sur la constellation. Le gain sera proportionnel à la variation de l'amplitude de l'OL. Néanmoins si une bonne symétrie ne se produit entre les vecteurs de la base, D ne peut pas être négligé et la constellation sera donc distordue et déplacée par rapport à l'origine. Un bon facteur de mérite pour établir la variation maximale de l'amplitude de l'OL peut être le EVM (*Error Vector Magnitude* en anglais ) donné par [23, 24] :

$$EVM = \frac{\frac{1}{N} \sum_{k=1}^{N} |\vec{z_m} - \vec{z_r}|}{|\vec{z_{pk}}|}$$

(1.20)

où  $\vec{z_m}$  est le vecteur mesuré,  $\vec{z_r}$  le vecteur de référence et  $\vec{z_{pk}}$  le vecteur à l'extrémité de la constellation. Nous savons à partir de (1.19) et de (1.15) que  $\Delta \vec{z_m} = \vec{z_m} - \vec{z_r} = \vec{z_r} \frac{\Delta V_{OL}}{V_{OL}}$  (si l'on néglige l'influence de D, bien évidemment). De ce fait, nous pouvons exprimer l'amplitude de la variation de l'OL en fonction de l'EVM à partir de :

$$EVM = \alpha_{evm} \frac{\Delta V_{OL}}{V_{OL}} \tag{1.21}$$

où  $\alpha_{evm}=\frac{\frac{1}{N}\sum\limits_{l}^{N}|\vec{z_{r}}|}{|z_{vk}^{-}|}$  est une constante dépendant du type de modulation.

Au lieu de calculer l'EVM, il serait utile d'estimer la variation admissible sur l'amplitude de l'OL étant donnée l'EVM acceptable. Cela permettra de choisir la qualité des composants aussi bien que de dimensionner correctement les circuits. Pour aboutir à une expression qui

établi le rapport entre l'EVM et  $\Delta V_{OL}$ , il suffit d'inverser (1.21) :

$$\Delta V_{OL} = \alpha_{evm} V_{OL} EVM \tag{1.22}$$

Avec les expressions développées dans cette section, nous pouvons prévoir l'effet causé par les variations de l'amplitude de l'oscillateur local sur les signaux en bande de base. Ces interférences sont directement proportionnelles aux fluctuations sur  $V_{OL}$ .

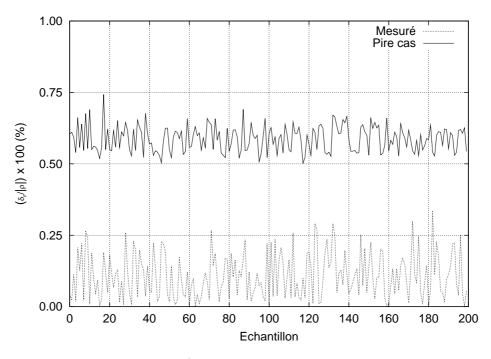

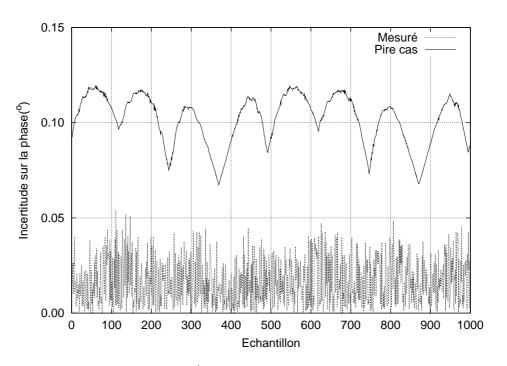

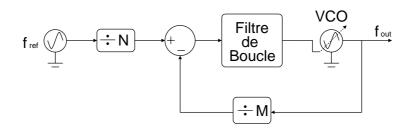

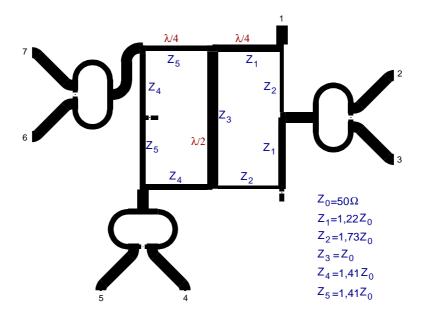

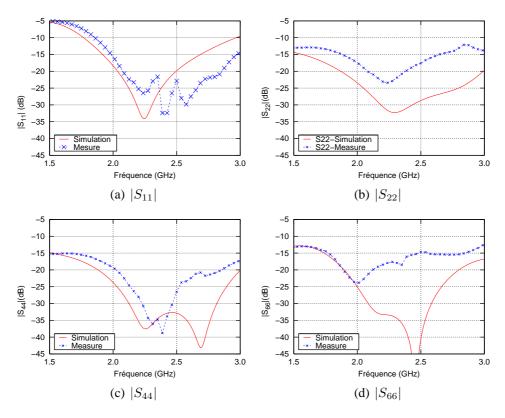

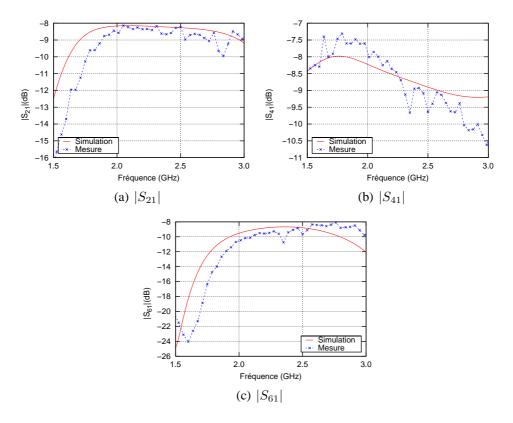

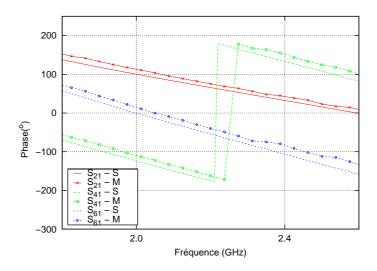

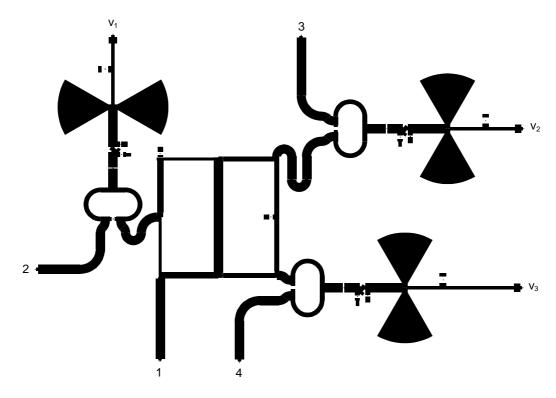

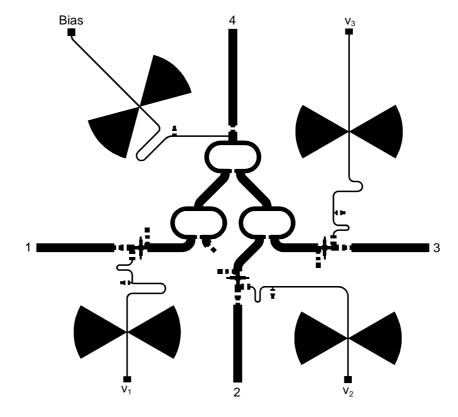

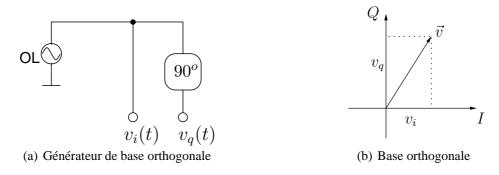

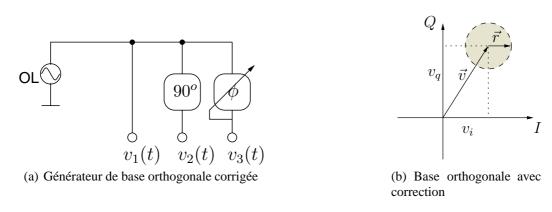

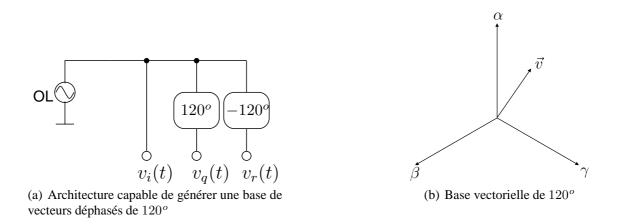

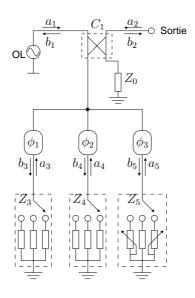

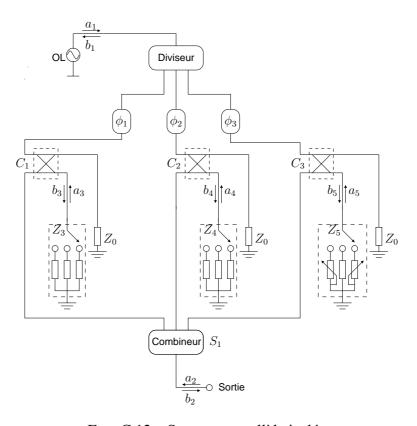

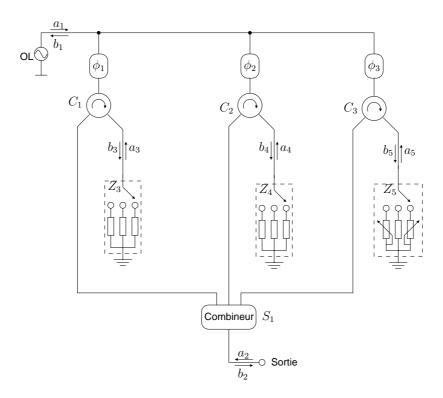

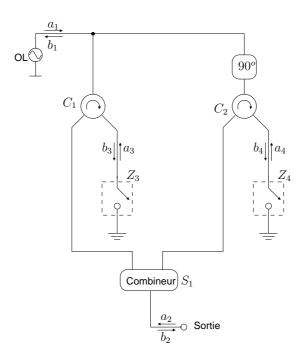

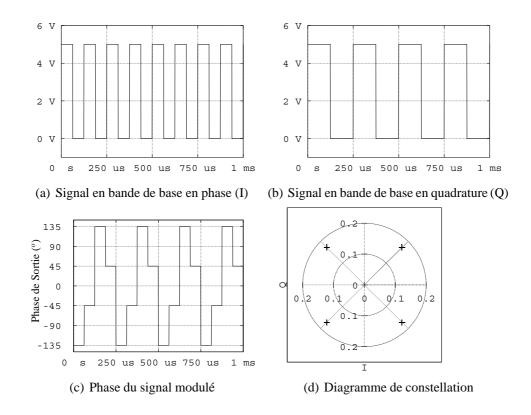

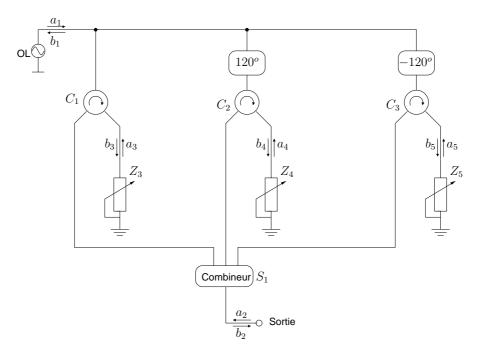

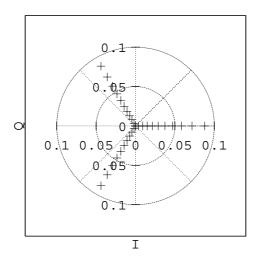

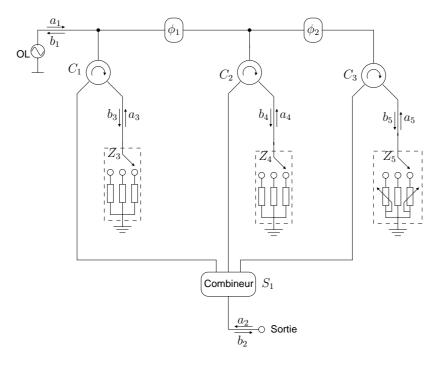

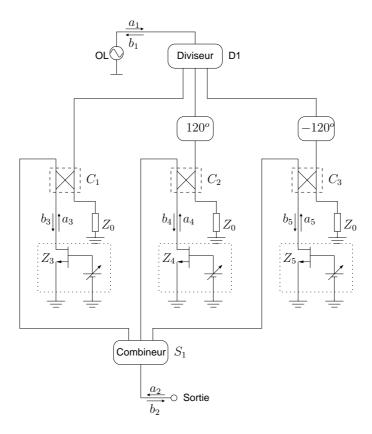

#### 1.3.3 L'influence de l'accès redondant sur les mesures