# Approche multicouches pour la reconfigurabilité de systèmes de communications de 3ème génération

Ioannis Krikidis

## ▶ To cite this version:

Ioannis Krikidis. Approche multicouches pour la reconfigurabilité de systèmes de communications de 3ème génération. domain\_other. Télécom ParisTech, 2005. English. NNT: . pastel-00001552

# HAL Id: pastel-00001552 https://pastel.hal.science/pastel-00001552

Submitted on 26 Jan 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Quand tu partiras pour Ithaque, souhaite que le chemin soit long, riche en péripéties et en expériences. Ne crains ni les Lestrygons, ni les Cyclopes, ni la colère de Neptune. Tu ne verras rien de pareil sur ta route si tes pensées restent hautes, si ton corps et ton âme ne se laissent effleurer que par des émotions sans bassesse. Tu ne rencontreras ni les Lestrygons, ni les Cyclopes, ni le farouche Neptune, si tu ne les portes pas en toi-même, si ton coeur ne les dresse pas devant toi.

Souhaite que le chemin soit long, que nombreux soient les matins d'été, où (avec quelles délices!) tu pénètreras dans des ports vus pour la première fois. Fais escale à des comptoirs phéniciens, et acquiers de belles marchandises: nacre et corail, ambre et ébène, et mille sortes d'entêtants parfums. Acquiers le plus possible de ces entêtants parfums. Visite de nombreuses cités égyptiennes, et instruis-toi avidemment auprès de leurs sages.

Garde sans cesse Ithaque présente à ton esprit. Ton but final est d'y parvenir, mais n'écourte pas ton voyage : mieux vaut qu'il dure de longues années, et que tu abordes enfin dans ton île aux jours de ta vieillesse, riche de tout ce que tu as gagné en chemin, sans attendre qu'Ithaque t'enrichisse.

Ithaque t'a donné le beau voyage : sans elle, tu ne te serais pas mis en route. Elle n'a plus rien d'autre à te donner. Même si tu la trouves pauvre, Ithaque ne t'a pas trompé. Sage comme tu l'es devenu à la suite de tant d'expériences, tu as enfin compris ce que signifient les Ithaques.

A mes parents...

# Remerciements

Une thèse de doctorat ne saurait se résumer qu'à cet écrit où ne figurent que les traces d'un cheminement qui s'est étendu sur trois ans. Ma reconnaissance s'adresse à tous ceux qui, de près ou de loin, ont permis que ce travail se réalise dans les meilleures conditions. Je désire alors exprimer ma profonde gratitude:

A Jean Luc Danger et Lirida Naviner qui m'ont donné l'occasion de faire ma thèse dans d'excellentes conditions au sein de leur équipe.

A tous les partenaires de projet RNRT ASTURIES pour les discussions créatives et pour leur aide.

Au professeur Andreas Polydoros de l'Université d'Athénes, qui m'a fait découvrir le monde de recherche.

Aux professeurs Charalambous et Jaques Palicot pour avoir accepté d'être Rapporteurs de ma thèse.

A madame Marylin Arndt et a monsieur Jean-Didier Legat qui ont accepté d'être examinateurs dans ce jury.

A monsieur Dominique Noguet qui a accepté de participer à ma soutenance comme membre invité.

A mes collègues du Departement Comelec pour leur contribution à la bonne ambiance de travail qui a baigné le cours de ma thèse. Un grand merci à Daniel Cardoso: son soutien et son aide m'ont été indispensables.

Je remercie aussi ma famille, et en particulier mes parents, pour leur patience et la compréhension dont ils ont fait preuve tout au long de mes études.

# Contents

| Li               | st of  | Figures                                                                    | 9         |

|------------------|--------|----------------------------------------------------------------------------|-----------|

| Li               | st of  | Tables                                                                     | 15        |

| N                | otatio | ons                                                                        | 17        |

| $\mathbf{A}$     | bbrev  | viations                                                                   | 19        |

| $\mathbf{T}^{1}$ | he As  | sturies project                                                            | 21        |

| In               | trodi  | uction                                                                     | 23        |

| 1                | 3G     | communication systems                                                      | <b>25</b> |

|                  | 1.1    | Introduction                                                               | 25        |

|                  | 1.2    | Spread spectrum communications                                             | 25        |

|                  |        | 1.2.1 DS-CDMA for personal communications                                  | 27        |

|                  |        | 1.2.2 The wireless propagation channel                                     | 27        |

|                  | 1.3    | CDMA detection                                                             | 28        |

|                  |        | 1.3.1 The conventional RAKE receiver                                       | 28        |

|                  |        | 1.3.2 The advanced receiver schemes                                        | 31        |

|                  | 1.4    | 3G communication systems                                                   | 35        |

|                  |        | 1.4.1 Differences between 3G and 2G air interfaces                         | 36        |

|                  |        | 1.4.2 UMTS                                                                 | 37        |

|                  |        | 1.4.3 CDMA2000                                                             | 42        |

|                  |        | 1.4.4 3G and satellites                                                    | 43        |

|                  | 1.5    | Conclusion                                                                 | 44        |

| <b>2</b>         | Alg    | gorithmic Reconfigurability: Applications                                  | 45        |

|                  | 2.1    | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                      | 45        |

|                  | 2.2    | An adaptive RAKE receiver with variable number of fingers and window-based |           |

|                  |        | channel estimation                                                         | 46        |

|                  |        | 2.2.1 Algorithm motivation                                                 | 46        |

|                  |        | 2.2.2 Problem formulation                                                  | 47        |

|                  |        | 2.2.3 The proposed receiver                                                | 49        |

|                  |        | 2.2.4 Simulation environment                                               | 51        |

6 CONTENTS

|   |     | 2.2.5  | Simulation results                                                                                                        |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------|

|   | 2.3 | High o | data rates and WCDMA systems                                                                                              |

|   | 2.4 | Single | -stage interference cancelation for high data rates                                                                       |

|   |     | 2.4.1  | Algorithm motivation                                                                                                      |

|   |     | 2.4.2  | Problem formulation                                                                                                       |

|   |     | 2.4.3  | The proposed receiver                                                                                                     |

|   |     | 2.4.4  | The Finger Configuration Algorithm                                                                                        |

|   |     | 2.4.5  | Numerical results                                                                                                         |

|   | 2.5 | Multi- | stage interference cancelation                                                                                            |

|   |     | 2.5.1  | Algorithm motivation                                                                                                      |

|   |     | 2.5.2  | Problem formulation                                                                                                       |

|   |     | 2.5.3  | The proposed receiver                                                                                                     |

|   |     | 2.5.4  | The proposed scheme versus conventional receivers                                                                         |

|   |     | 2.5.5  | Numerical results                                                                                                         |

|   | 2.6 | Multi- | stage interference cancelation with realistic channel estimation 81                                                       |

|   |     | 2.6.1  | Algorithm motivation                                                                                                      |

|   |     | 2.6.2  | Problem formulation                                                                                                       |

|   |     | 2.6.3  | The proposed receiver                                                                                                     |

|   |     | 2.6.4  | Numerical results                                                                                                         |

|   | 2.7 | Multi- | stage interference cancelation for multi-user detection                                                                   |

|   |     | 2.7.1  | Algorithm motivation                                                                                                      |

|   |     | 2.7.2  | Problem formulation                                                                                                       |

|   |     | 2.7.3  | The proposed receiver                                                                                                     |

|   |     | 2.7.4  | Numerical results                                                                                                         |

|   | 2.8 | CDM    | A2000 for a satellite environment                                                                                         |

|   |     | 2.8.1  | Algorithm motivation                                                                                                      |

|   |     | 2.8.2  | Problem formulation and simulation environment                                                                            |

|   |     | 2.8.3  | The proposed system                                                                                                       |

|   |     | 2.8.4  | Numerical results                                                                                                         |

|   | 2.9 | Concl  | $usion \dots \dots$ |

|   |     |        |                                                                                                                           |

| 3 |     |        | e Reconfigurability: Applications 107                                                                                     |

|   | 3.1 |        | luction                                                                                                                   |

|   | 3.2 |        | mplementation                                                                                                             |

|   |     | 3.2.1  | TigerSHARC                                                                                                                |

|   |     | 3.2.2  | Time constraints                                                                                                          |

|   |     | 3.2.3  | Optimized code                                                                                                            |

|   |     | 3.2.4  | DSP performance                                                                                                           |

|   | 3.3 |        | vare implementation                                                                                                       |

|   |     | 3.3.1  | The iterative architecture                                                                                                |

|   |     | 3.3.2  | Implementation issues                                                                                                     |

|   |     | 3.3.3  | Simulation results                                                                                                        |

|   |     | 3.3.4  | FPGA implementation                                                                                                       |

|   |     | 3.3.5  | FPGA performance                                                                                                          |

CONTENTS 7

|              | 3.4           | Conclusion                                                     | 133 |

|--------------|---------------|----------------------------------------------------------------|-----|

| 4            | $\mathbf{Th}$ | e iterative reconfigurability concept                          | 135 |

|              | 4.1           | Introduction                                                   | 135 |

|              | 4.2           | The need of a flexible radio                                   | 135 |

|              | 4.3           | Definitions of radio flexibility                               | 137 |

|              | 4.4           | The two-layer reconfigurability concept                        | 140 |

|              |               | 4.4.1 Layer 2: The algorithmic reconfigurability               | 140 |

|              |               | 4.4.2 Layer 1: The hardware reconfigurability                  | 143 |

|              |               | 4.4.3 Layer 1+: The architectural reconfigurability            | 148 |

|              | 4.5           | Conclusion                                                     | 155 |

| Co           | onclu         | sions and Perspectives                                         | 157 |

| $\mathbf{A}$ | De            | finitions and Comments                                         | 161 |

| В            | Lin           | near Profile for the DSP implementation                        | 165 |

| $\mathbf{C}$ | Rés           | sumé                                                           | 169 |

|              | C.1           | Introduction                                                   | 169 |

|              | C.2           | Notion de Reconfigurabilité matèrielle                         | 171 |

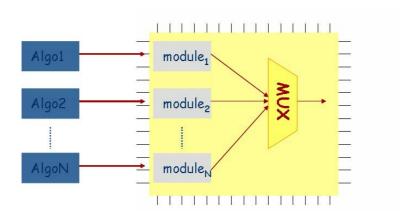

|              |               | C.2.1 Approche multiplexage                                    | 171 |

|              |               | C.2.2 Approche pagination                                      |     |

|              |               | C.2.3 Approche factorisation                                   |     |

|              |               | C.2.4 Approche itération                                       |     |

|              | C.3           | Récepteur RAKE reconfigurable avec annulateur                  |     |

|              |               | d'interférences                                                | 173 |

|              |               | C.3.1 Formulation du problème                                  | 174 |

|              |               | C.3.2 Algorithme proposé                                       | 175 |

|              |               | C.3.3 Evaluation de la performance                             | 176 |

|              |               | C.3.4 Architecture reconfigurable                              | 177 |

|              |               | C.3.5 Implémentation                                           | 180 |

|              | C.4           | Un annulateur d'interférences basé sur une estimation de canal | 183 |

|              |               | C.4.1 Formulation du problème                                  | 183 |

|              |               | C.4.2 Algorithme proposé                                       | 184 |

|              |               | C.4.3 Evaluation de la performance                             | 186 |

|              |               | C.4.4 Architecture reconfigurable                              | 186 |

|              | C.5           | Conclusion                                                     | 188 |

| Bi           | bliog         | graphy                                                         | 189 |

| Li           | st of         | publications                                                   | 199 |

8 CONTENTS

# List of Figures

| 1.1  | Basic spread spectrum technique                                                           | 26 |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | RAKE receiver correlator                                                                  | 29 |

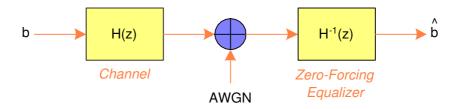

| 1.3  | Block diagram of a simple transmission scheme using a zero-forcing equalizer              | 32 |

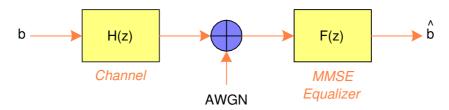

| 1.4  | Block diagram of a simple transmission scheme employing an MMSE equalizer                 | 32 |

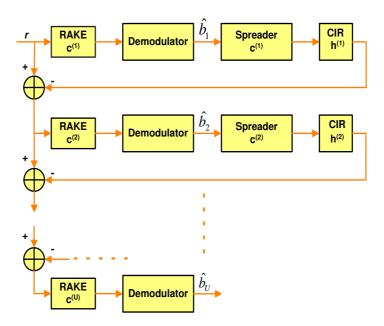

| 1.5  | Schematic of the SIC receiver for $U$ users. The users' signals have been ranked,         |    |

|      | where user 1's signal was received at the highest power, while user $U$ 's signal at      |    |

|      | the lowest power. In the order of ranking, the data estimates of each user are            |    |

|      | obtained and the received signal of each user is reconstructed and canceled from          |    |

|      | the received composite signal, $r$                                                        | 34 |

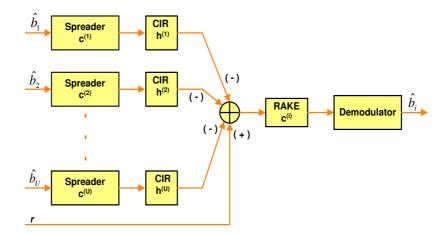

| 1.6  | Schematic of a single cancelation stage for user $i$ in the PIC receiver for $U$ users.   |    |

|      | The data estimates, $b_1,, b_U$ of the other $(U-1)$ users were obtained from the         |    |

|      | previous cancelation stage, and the received signal of each user other than the $i$ -th   |    |

|      | one is reconstructed and canceled from the received signal, $r$                           | 35 |

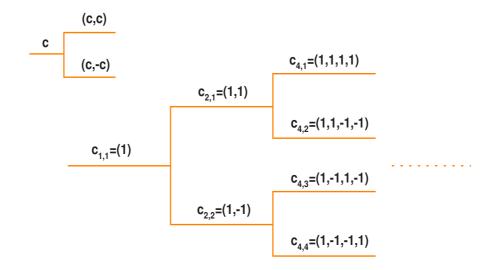

| 1.7  | The channelization tree                                                                   | 38 |

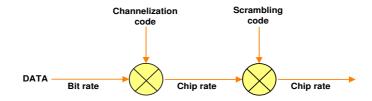

| 1.8  | Relation between spreading and scrambling                                                 | 39 |

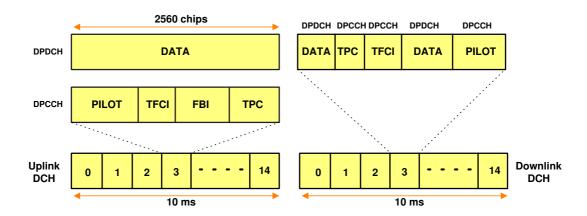

| 1.9  | Uplink/Downlink dedicated physical channel structure                                      | 40 |

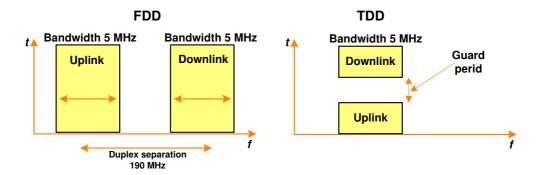

| 1.10 | Principles of FDD and TDD operation                                                       | 41 |

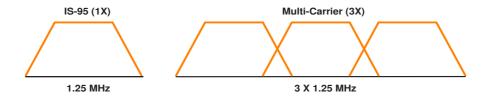

| 1.11 | Relationship between the MC mode $(3X)$ and IS-95 $(1X)$ in spectrum usage                | 43 |

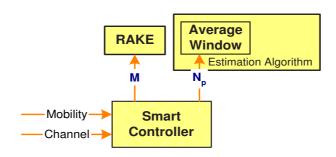

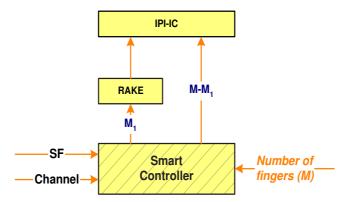

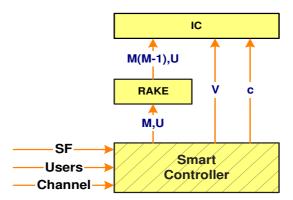

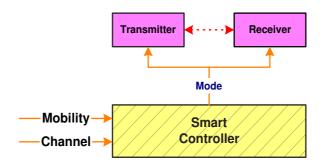

| 2.1  | The Proposed Receiver- Smart Controller                                                   | 50 |

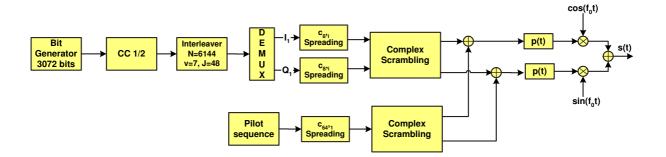

| 2.2  | The transmitter chain                                                                     | 52 |

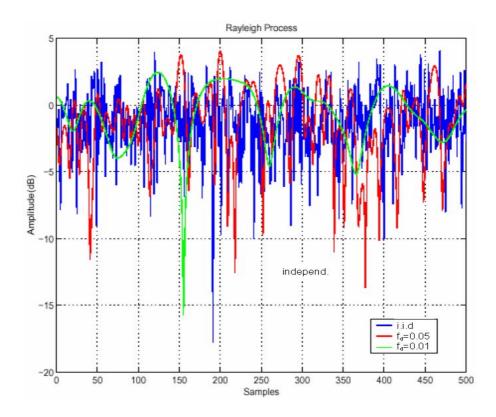

| 2.3  | The power envelope for different correlations                                             | 53 |

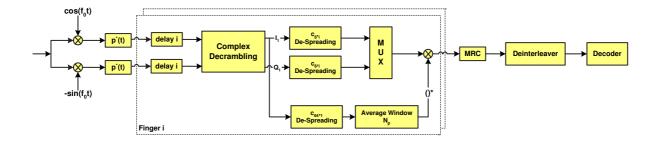

| 2.4  | The receiver chain                                                                        | 54 |

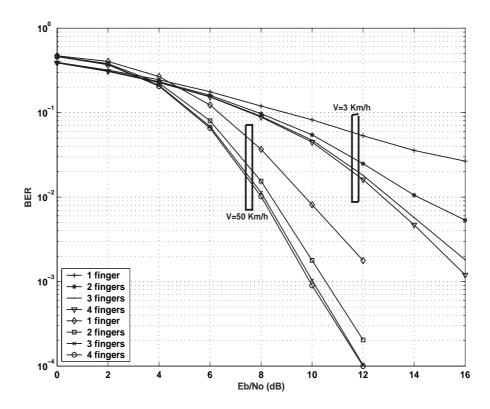

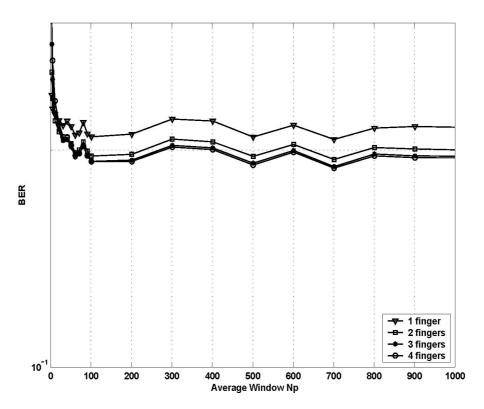

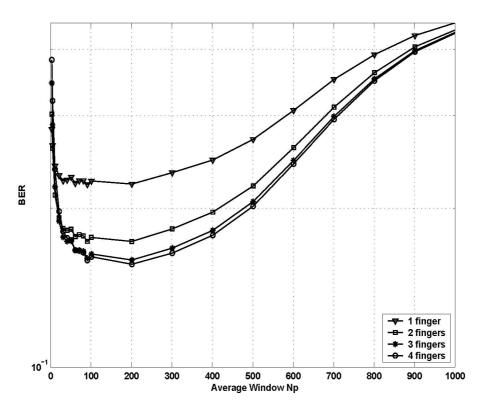

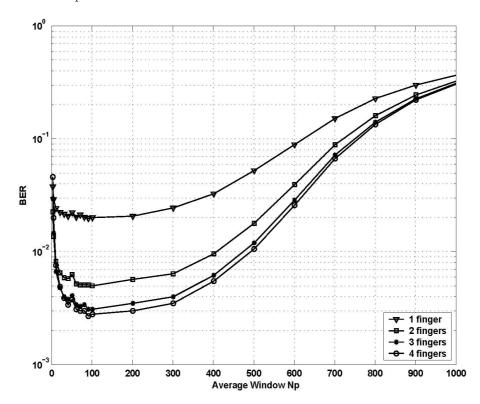

| 2.5  | RAKE receiver with different numbers of fingers for speeds equal to $3~\mathrm{Km/h}$ and |    |

|      | 50 Km/h, and perfect channel estimation                                                   | 55 |

| 2.6  | RAKE receiver with different numbers of fingers for a speed equal to 3 Km/h,              |    |

|      | $E_b/N_0 = 5dB$ and imperfect estimation                                                  | 56 |

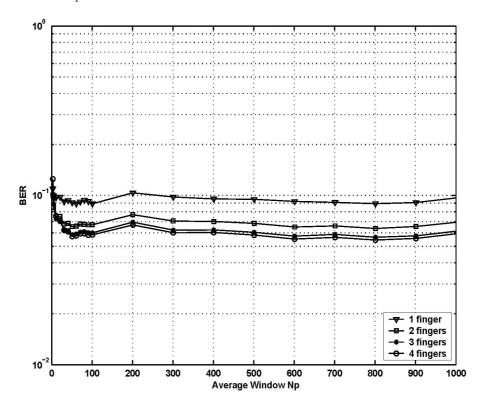

| 2.7  | RAKE receiver with different numbers of fingers for a speed equal to 3 Km/h,              |    |

|      | $E_b/N_0 = 10dB$ and imperfect estimation                                                 | 56 |

| 2.8  | RAKE receiver with different numbers of fingers for a speed equal to 50 Km/h,             |    |

|      | $E_b/N_0 = 5dB$ and imperfect estimation                                                  | 57 |

| 2.9  | RAKE receiver with different numbers of fingers for a speed equal to 50 Km/h,             |    |

|      | $E_b/N_0 = 10dB$ and imperfect estimation                                                 | 57 |

| 2.10 | The proposed algorithm                                                                    | 62 |

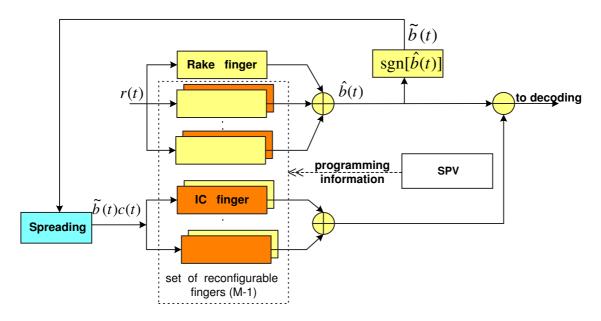

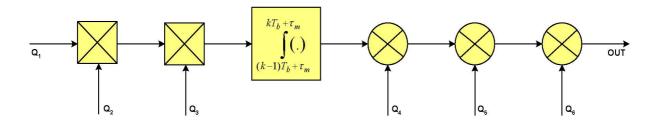

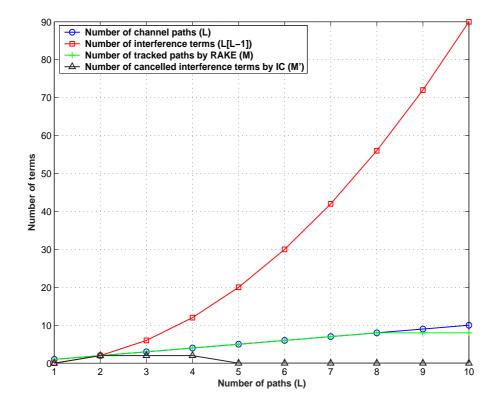

| 2.11 | The computational part of the proposed reconfigurable detector 6                              |

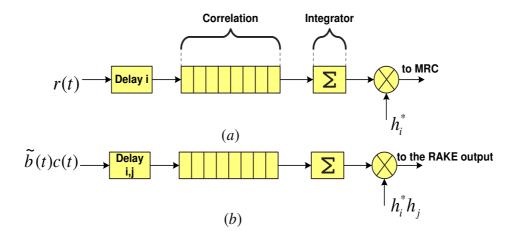

|------|-----------------------------------------------------------------------------------------------|

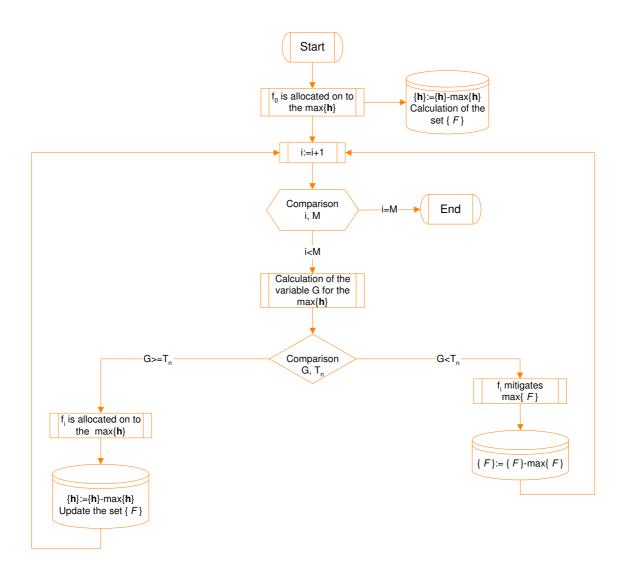

| 2.12 | a) RAKE finger for the <i>i</i> -th channel path b) Interference "finger" for the cancelation |

|      | of the term which arose from the <i>i</i> -th and <i>j</i> -th paths 6                        |

| 2.13 | The block diagram of the finger configuration algorithm                                       |

| 2.14 | Performance comparison for a reconfigurable RAKE receiver with different com-                 |

|      | putational power constraints (number of the available fingers) 6                              |

| 2.15 | BER performance for a spreading factor equal to 4 and $E_b/N_0=16 \mathrm{dB.}$ 6             |

| 2.16 | BER performance for a spreading factor equal to 8 and $E_b/N_0=16 \mathrm{dB.}$ 6             |

| 2.17 | BER performance for a spreading factor equal to 32 and $E_b/N_0=16 \mathrm{dB}$ 6             |

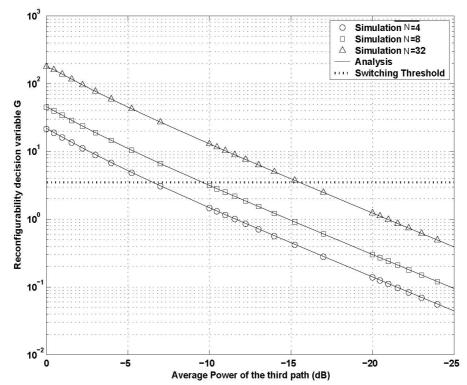

| 2.18 | Reconfigurability decision variable G                                                         |

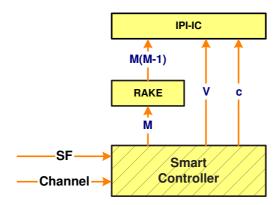

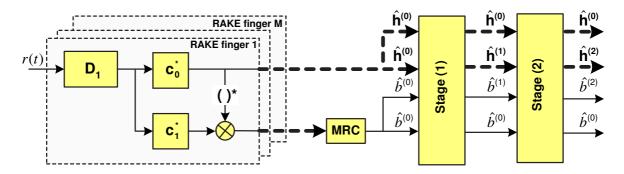

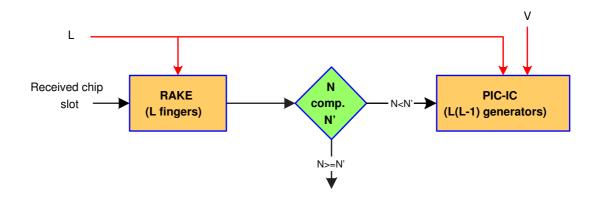

| 2.19 | The proposed algorithm; A RAKE receiver with a multi-stage IC                                 |

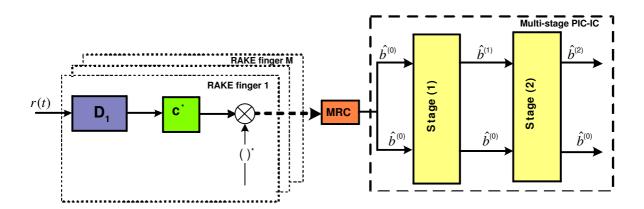

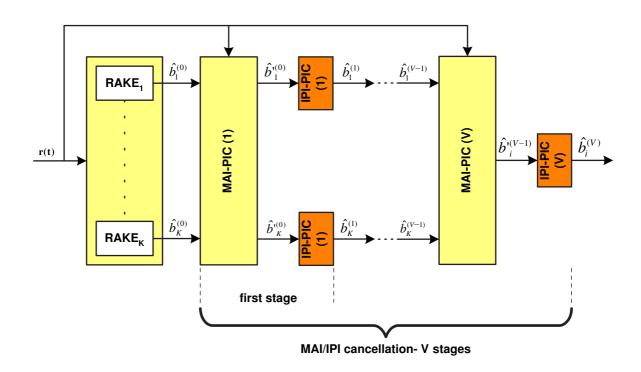

| 2.20 | The general block diagram of the detection algorithm under consideration (com-                |

|      | bination of RAKE with the multistage IPI-IC)                                                  |

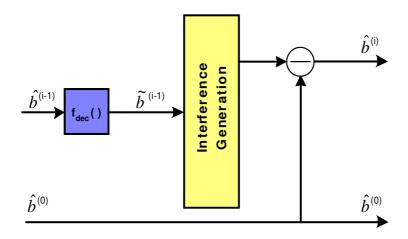

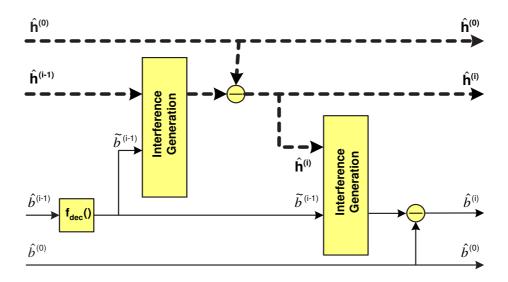

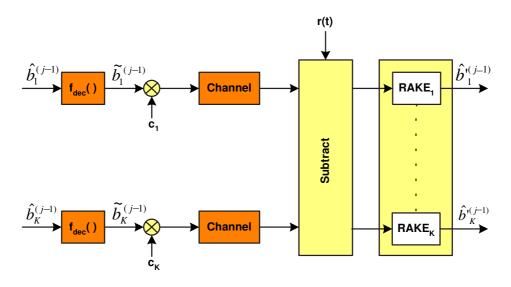

| 2.21 | The <i>i</i> -th stage of the detection algorithm                                             |

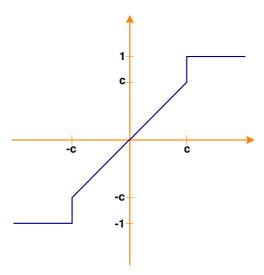

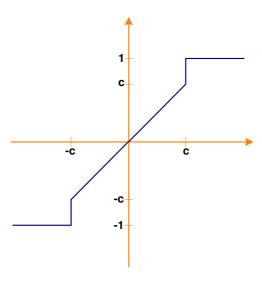

| 2.22 | The decision function $f_{dec}()$ with a threshold $c$                                        |

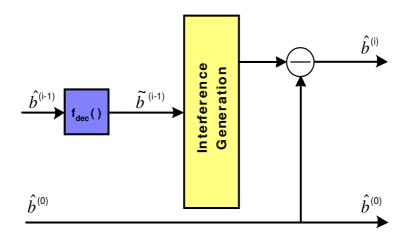

| 2.23 | The interference generation process                                                           |

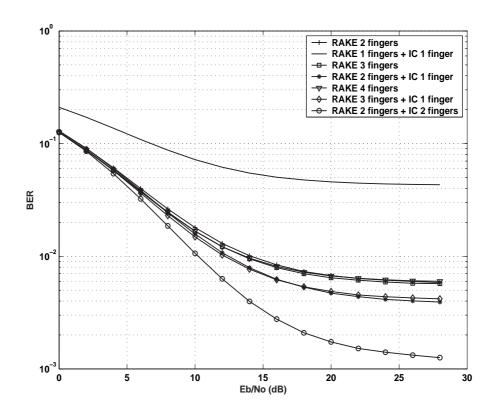

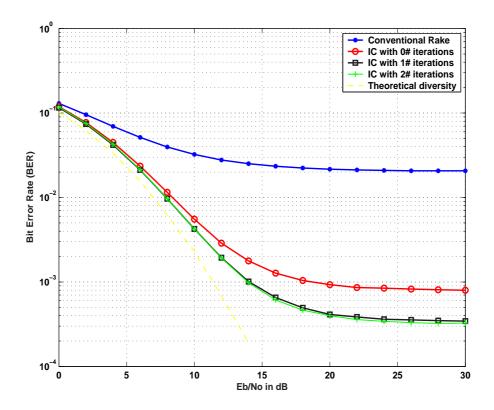

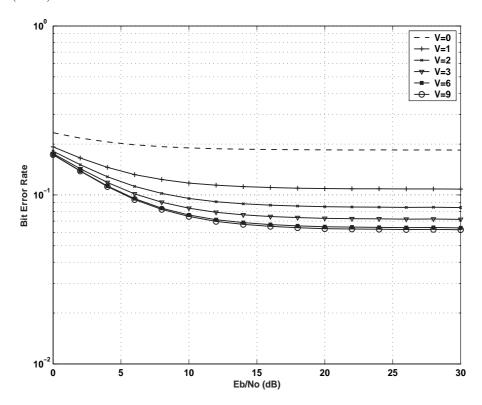

| 2.24 | BER performance of the reconfigurable detector for different configurations versus            |

|      | $E_b/N_o$ , for N=4 and $\mathbf{h} = [0\ 0\ 0]dB$ , $\tau = [0\ 6\ 8]T_c$                    |

| 2.25 | BER performance of the reconfigurable detector for different configurations versus            |

|      | $E_b/N_0$ , for $N=4$ and $\mathbf{h}=[0\ 0\ 0]dB$ , $\tau=[0\ 1\ 2]T_c$                      |

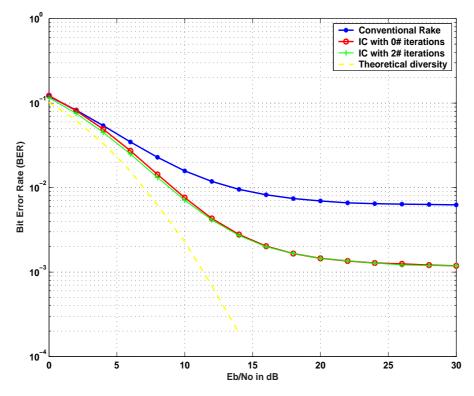

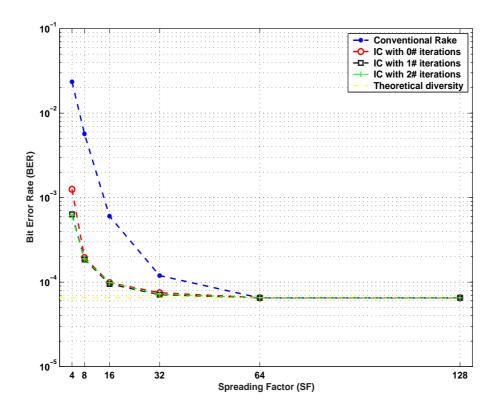

| 2.26 | BER performance of the reconfigurable detector for different configurations versus            |

|      | the spreading factor, for SNR=16dB and $\mathbf{h} = [0\ 0\ 0]dB$ , $\tau = [0\ 6\ 8]T_c$ 7   |

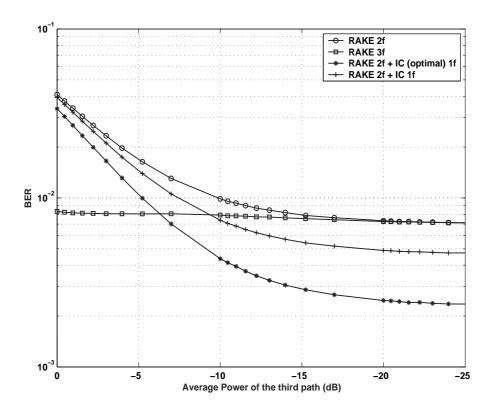

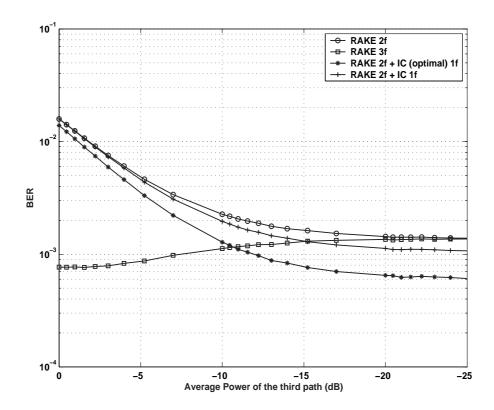

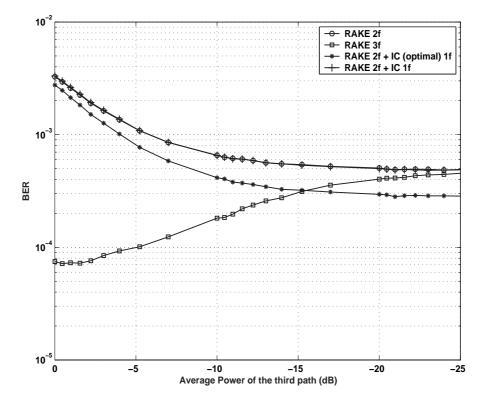

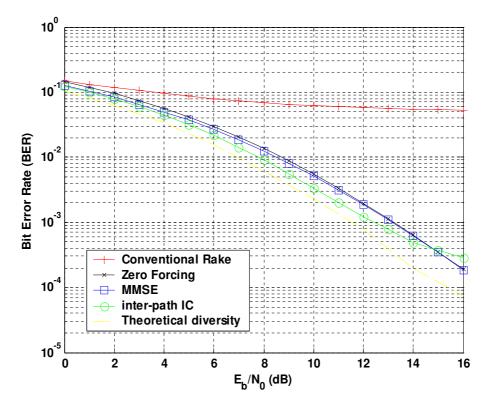

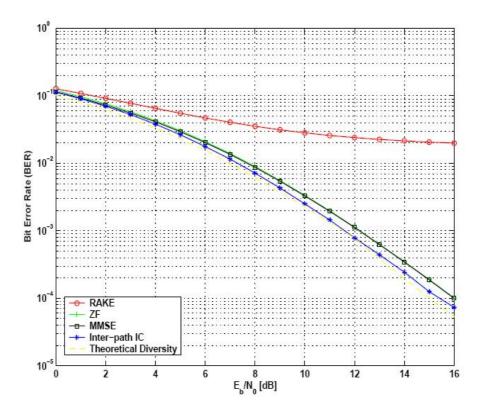

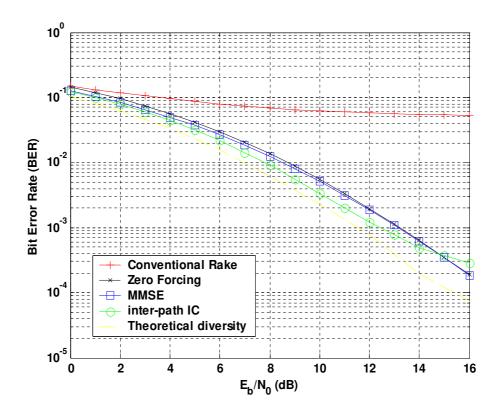

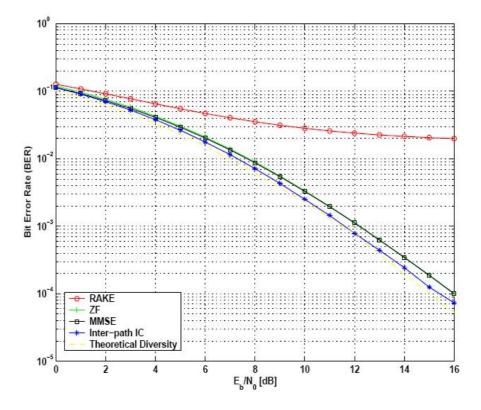

| 2.27 | BER comparison over equal 3-path channel and $N = 2$                                          |

| 2.28 | BER comparison over equal 3-path channel and $N=4$                                            |

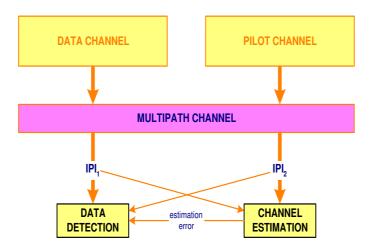

| 2.29 | The intra $(IPI_1)$ - and inter $(IPI_2)$ - interference (from the data channel point of      |

|      | view)                                                                                         |

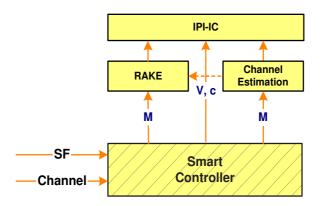

| 2.30 | The general structure of the proposed algorithm; A RAKE receiver with a pilot                 |

|      | channel estimation and IC                                                                     |

| 2.31 | General structure of the multi-stage inter-path interference canceler with a realistic        |

|      | channel estimation                                                                            |

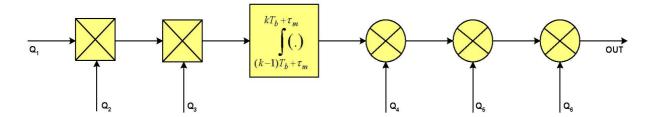

|      | Structure of the <i>i</i> -th cancelation stage                                               |

| 2.33 | The computational similarities of the essential operations of the proposed recon-             |

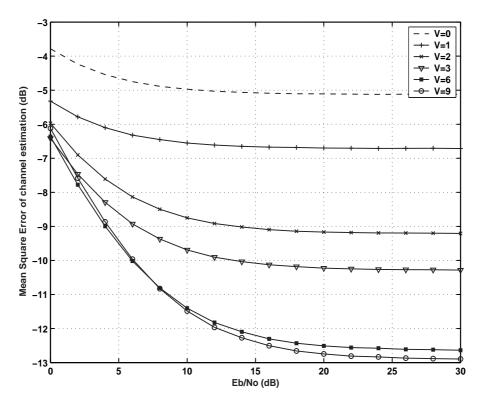

|      | figurable detector                                                                            |

| 2.34 | MSE performance of the proposed channel estimation scheme versus the classic                  |

|      | estimation (V=0)                                                                              |

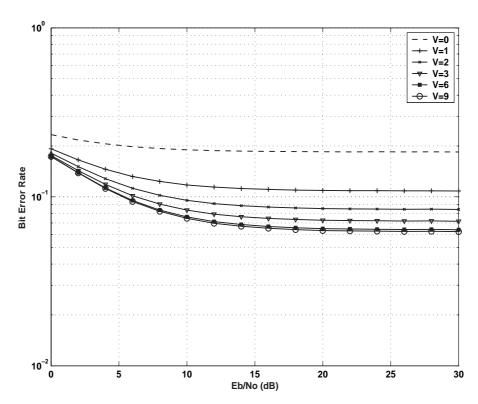

| 2.35 | BER performance of the proposed reception scheme versus the conventional re-                  |

|      | ceiver (V=0)                                                                                  |

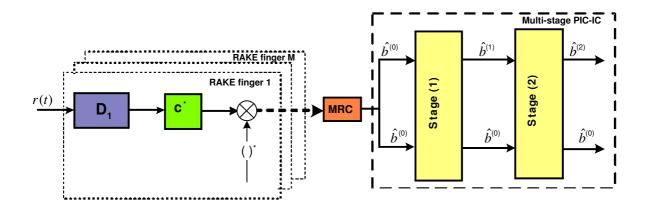

|      | The proposed reconfigurable PIC scheme for DS/CDMA downlink connections. $$ 9                 |

|      | Structure of the proposed multi-stage PIC scheme for the <i>i</i> -th user 9                  |

|      | Structure of the $j$ -th MAI-PIC stage                                                        |

|      | Structure of the $j$ -th IPI-PIC stage                                                        |

| 2.40 | The impact of SF on the performance of a conventional RAKE receiver. $E_b/N_0 =$              |

|      | 16dB, $V = 5$ stages and $U = 1$ users                                                        |

| 2.41 | The impact of the decision function threshold on the PIC performance. $E_b/N_0 = 16$ dB, $V = 5$ stages, $N = 8$ and $U = 5$ users. The thresholds are $c = 0.0, 0.3, 0.7$ |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | and $\infty$ , respectively                                                                                                                                                | 95  |

| 2 42 | BER performance versus $E_b/N_0$ . $V=5$ stages, $N=8$ , $U=5$ users and the                                                                                               | 50  |

| 2.12 | thresholds are $c = 0.0$ and $0.3$                                                                                                                                         | 96  |

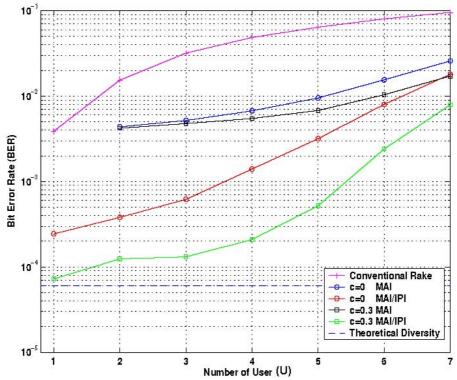

| 2 43 | BER performance versus number of users. $E_b/N_0 = 16 \text{dB}, V = 5 \text{ stages}, N = 8$                                                                              | 50  |

| 4.40 | and the thresholds are $c = 0.0$ and $0.3$                                                                                                                                 | 96  |

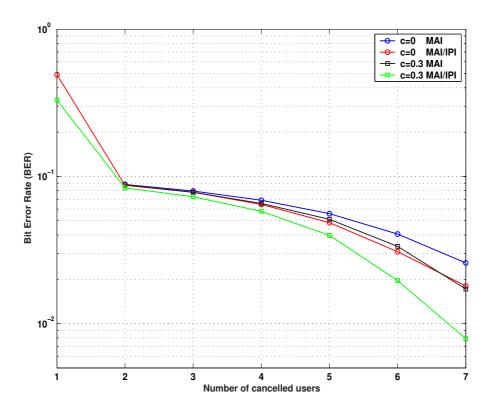

| 2 44 | BER performance versus number of canceled users. $E_b/N_0 = 16  \mathrm{dB},  V = 5  \mathrm{stages},$                                                                     | 30  |

| 2.44 | N=8, U=7 users and the thresholds are $c=0.0$ and 0.3, respectively                                                                                                        | 97  |

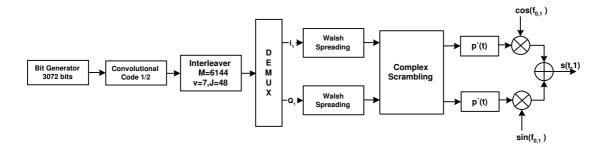

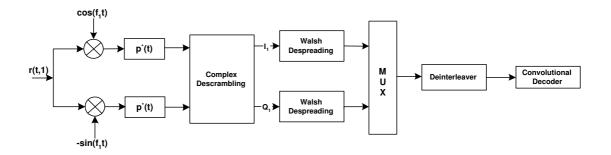

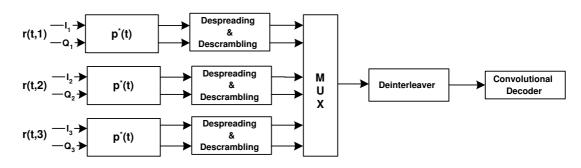

| 2.45 | Transmission chain for mode 1X                                                                                                                                             | 99  |

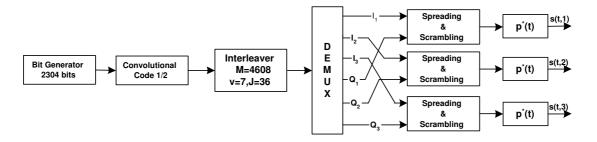

|      | Transmission chain for mode 3X                                                                                                                                             | 99  |

|      | Reception chain for mode 1X                                                                                                                                                | 101 |

|      | Reception chain for mode 3X                                                                                                                                                | 101 |

|      | The proposed reconfigurable CDMA2000 transceiver                                                                                                                           | 102 |

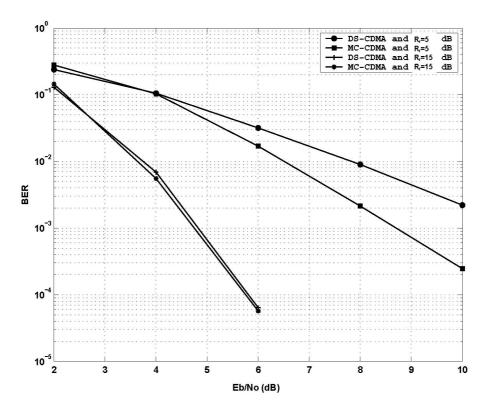

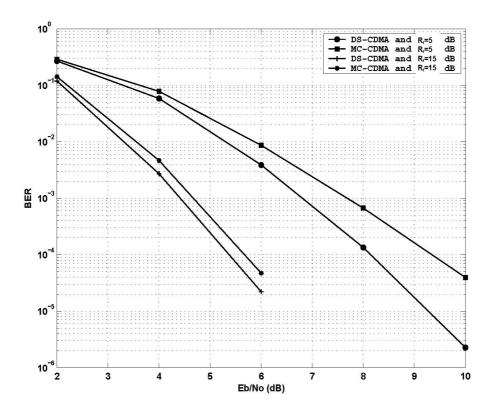

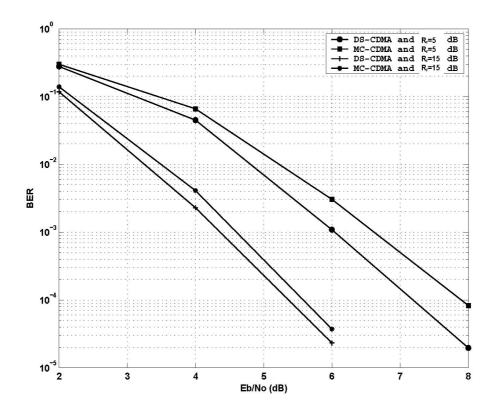

|      | Comparison of DS-CDMA and MC-CDMA for a receiver speed equal to 3km/h.                                                                                                     | 104 |

|      | Comparison of DS-CDMA and MC-CDMA for a receiver speed equal to 50km/h.                                                                                                    | 104 |

|      | Comparison of DS-CDMA and MC-CDMA for a receiver speed equal to 130km/h.                                                                                                   | 105 |

|      |                                                                                                                                                                            |     |

| 3.1  | The block diagram of the DSP implementation; RAKE and IC correspond to                                                                                                     |     |

|      | software functions                                                                                                                                                         | 108 |

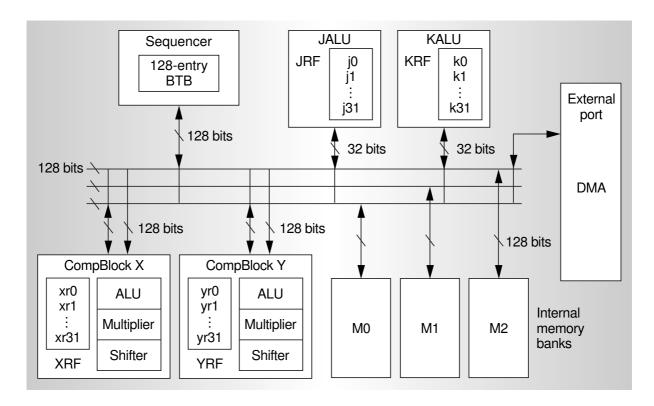

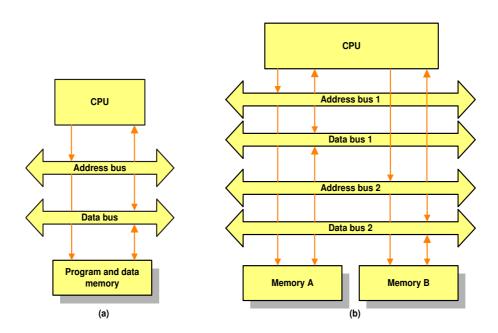

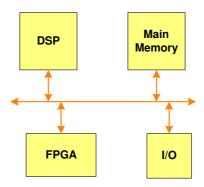

| 3.2  | Top-level block diagram showing the major DSP subsystems and the data buses.                                                                                               | 109 |

| 3.3  | SIMD execution and subword parallel operations                                                                                                                             | 110 |

| 3.4  | The processing time of the RAKE combination versus the number of the channel                                                                                               | 110 |

| 2 5  | paths.                                                                                                                                                                     | 112 |

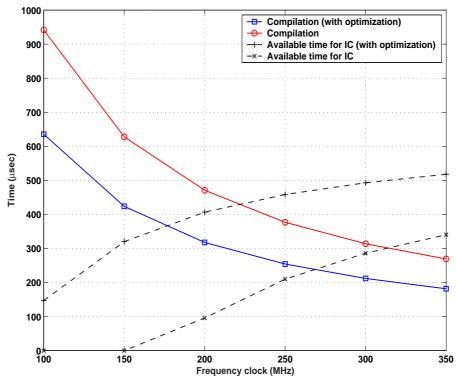

| 3.5  | The processing time of the RAKE combination versus the DSP's frequency clock; $L=4, M=4$                                                                                   | 119 |

| 3.6  | The processing time of the IC versus the number of canceled interference terms;                                                                                            | 112 |

| 5.0  | The processing time of the PC versus the number of canceled interference terms, $L=3$ and $M=3$                                                                            | 119 |

| 3.7  | The processing time of the IC versus the DSP clock frequency for an environment                                                                                            | 110 |

| 3.1  | with $L=2$ and $M=2$ .                                                                                                                                                     | 112 |

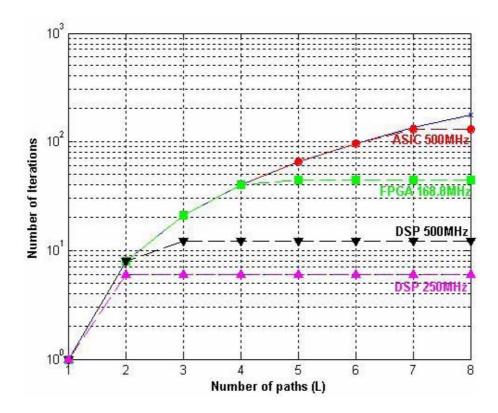

| 3.8  | The efficiency of a DSP with a frequency 250 MHz in terms of the operated                                                                                                  | 110 |

| 3.0  |                                                                                                                                                                            | 115 |

| 3.9  | The FSM model of the iterative mapping approach for the detection scheme under                                                                                             | 115 |

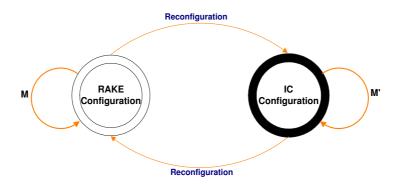

| 5.5  | consideration                                                                                                                                                              | 117 |

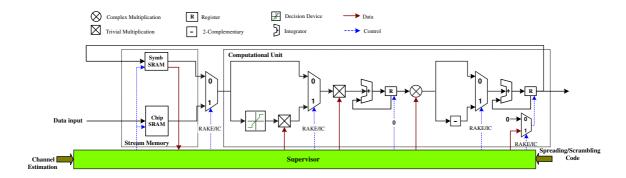

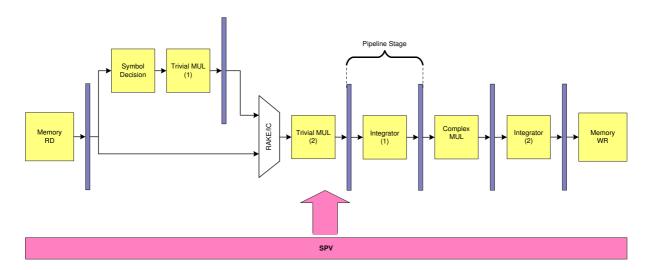

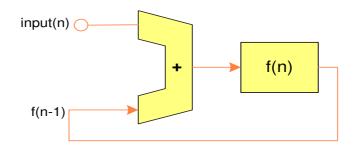

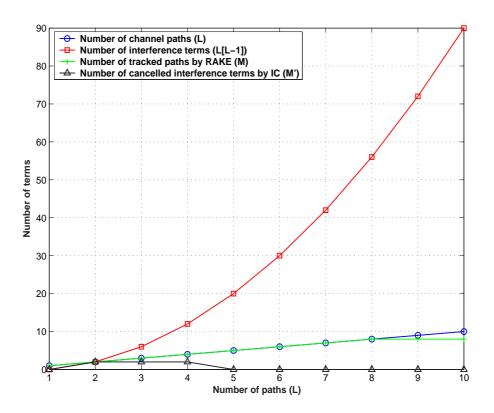

| 3 10 | The corresponding computational core of the iterative approach.                                                                                                            |     |

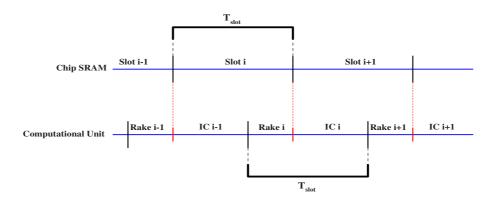

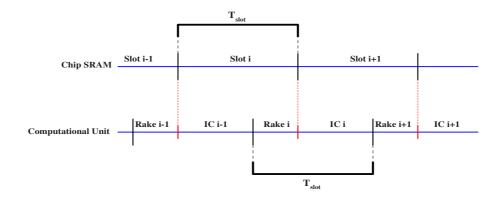

|      | Timing relationship of SRAM chip and SRAM symbol WR/RD operations                                                                                                          |     |

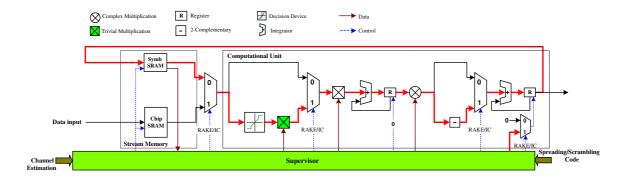

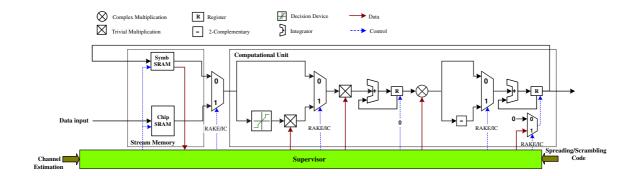

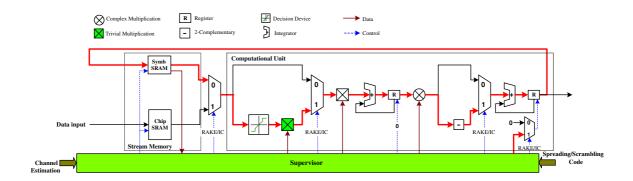

|      | The flow of data during the RAKE configuration mode                                                                                                                        |     |

|      | The flow of data during the IC configuration mode                                                                                                                          |     |

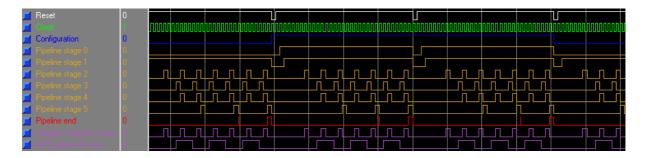

|      | The pipeline implementation of the reconfigurable RAKE/IC detector                                                                                                         |     |

|      |                                                                                                                                                                            | 123 |

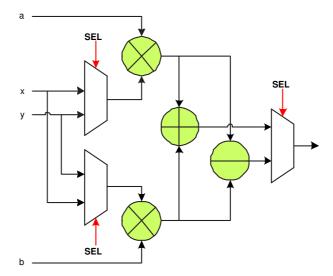

|      | The complex multiplication between $a + bj$ and $x + yj$ in two processing cycles.                                                                                         |     |

|      |                                                                                                                                                                            | 126 |

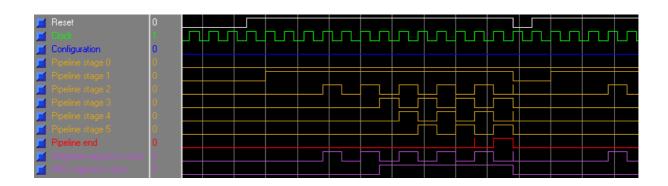

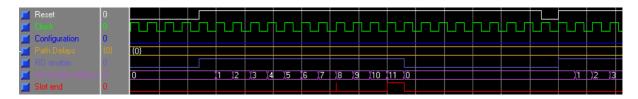

|      | Modelsim time simulation for a channel environment with $L=1$ and $N=2$<br>Modelsim time simulation for a channel environment with $L=3$ and $N=8$                         |     |

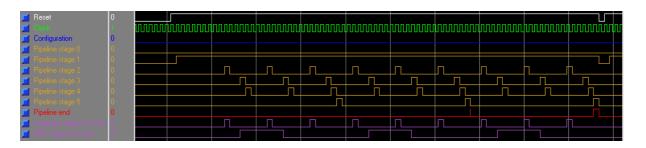

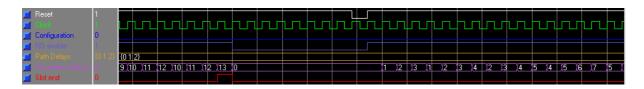

|      | Modelsim time simulation for a channel environment with $L=2,N=4,V=1$ .                                                                                                    |     |

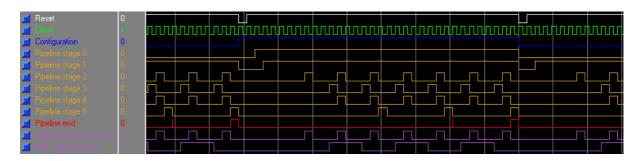

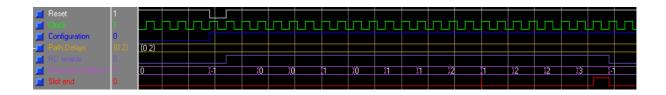

| 0.10 | 1.15 actually time differential for a chamber of the first point $D = D$ , $T_1 = T_2$ , $T_2 = T_3$ .                                                                     |     |

| 3.21       | Modelsim time simulation for a channel environment with $L=2, N=4, V=2$ . Memory structure for a slot with 3 symbols, $L=1$ and $N=4$ Generation of the chip memory addresses for the case of $L=1, N=4$ and | 126<br>127 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| J.44       | $N_{Block}=3$                                                                                                                                                                                                | 127        |

|            | Memory structure for a slot with 3 symbols, $L=3$ , $\tau=[0\ 1\ 2]T_c$ and $N=4$ Generation of the chip memory addresses for the case of $L=3$ , $N=4$ and                                                  | 128        |

| 0.21       |                                                                                                                                                                                                              | 128        |

|            |                                                                                                                                                                                                              | 129        |

| 3.23       |                                                                                                                                                                                                              | 129        |

| 3.27       |                                                                                                                                                                                                              | 130        |

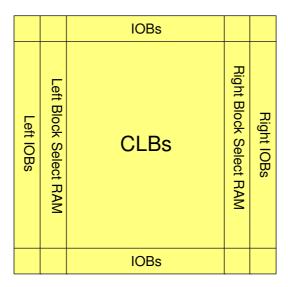

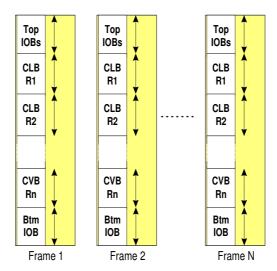

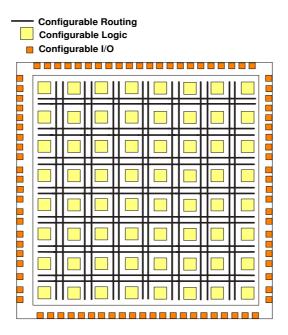

|            | CLB frame organization                                                                                                                                                                                       |            |

|            |                                                                                                                                                                                                              | 132        |

|            |                                                                                                                                                                                                              |            |

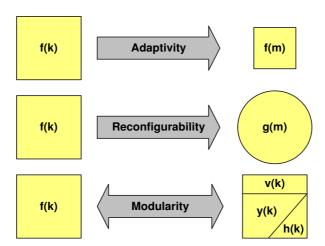

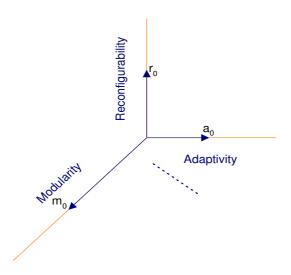

| 4.1        |                                                                                                                                                                                                              | 138        |

| 4.2        | The imagined Euclidean space of flexibility. The vector $[a_0, r_0, m_0,]$ presents the                                                                                                                      |            |

|            | degree/type of flexibility                                                                                                                                                                                   | 139        |

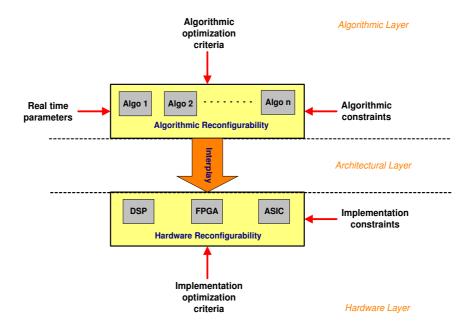

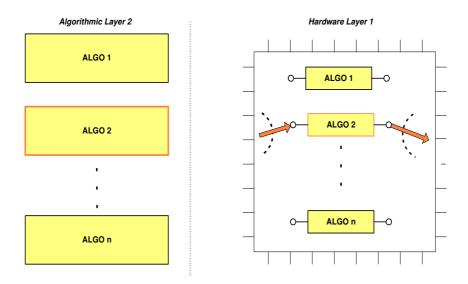

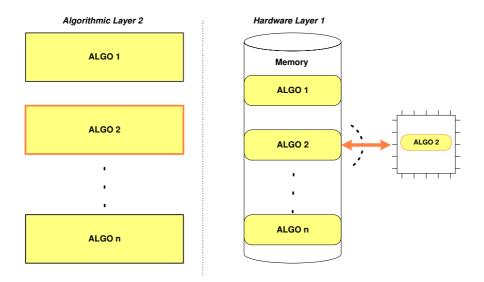

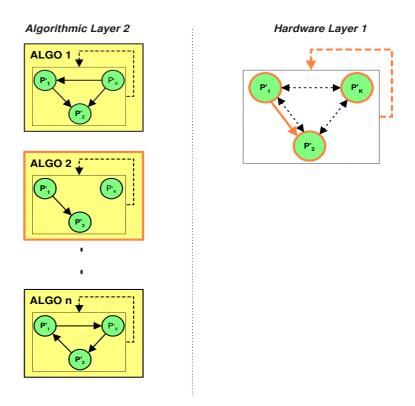

| 4.3        |                                                                                                                                                                                                              | 141        |

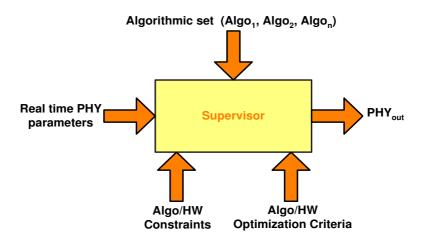

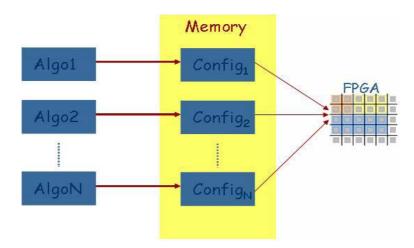

| 4.4        | 1 1                                                                                                                                                                                                          | 142        |

| 4.5        | · / /                                                                                                                                                                                                        | 144        |

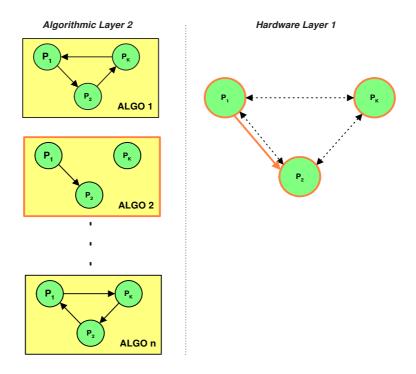

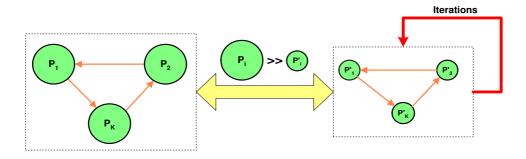

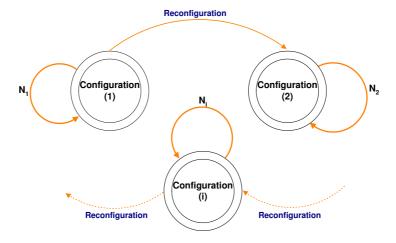

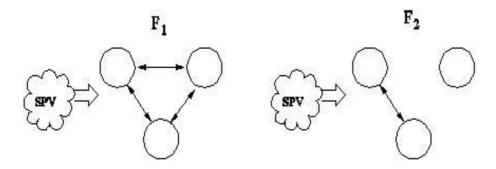

| 4.6        | 0 1                                                                                                                                                                                                          | 146        |

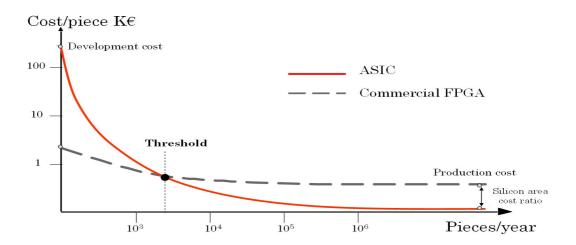

| 4.7        | The behavior of the implementation cost as a function of production volume                                                                                                                                   |            |

| 4.8        | 0 1 1                                                                                                                                                                                                        | 148        |

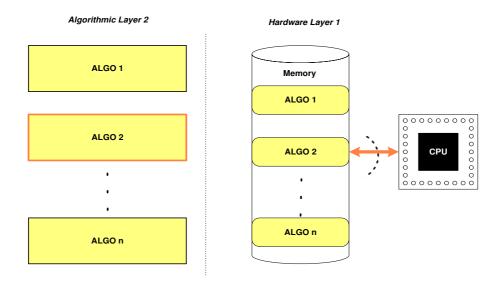

| 4.9        | DSP mapping approach.                                                                                                                                                                                        |            |

| 4.10       | 0 11 0 11                                                                                                                                                                                                    |            |

|            | The hardware paging mapping approach                                                                                                                                                                         |            |

|            | The factorization mapping approach.                                                                                                                                                                          |            |

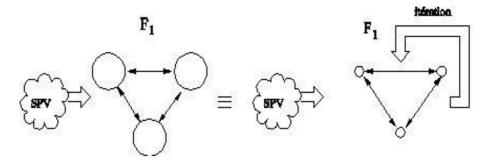

|            | The relation between factorization and iterative approaches                                                                                                                                                  |            |

|            | The iterative mapping approach.                                                                                                                                                                              |            |

| 4.15       | The FSM represents the iterative approach schematically                                                                                                                                                      | 154        |

| B.1<br>B.2 | Linear profiling for the RAKE function; Simulation parameters: $L=2$ , $N=4$ , $K=640$ .<br>Linear profiling for the IC function (Part A); Simulation parameters: $L=2$ , $N=4$ ,                            | 165        |

|            |                                                                                                                                                                                                              | 166        |

| B.3        | Linear profiling for the IC function (Part B); Simulation parameters: $L=2, N=4$ ,                                                                                                                           |            |

|            |                                                                                                                                                                                                              | 167        |

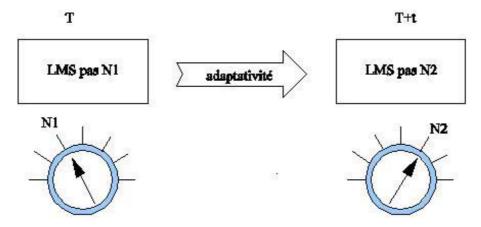

| C.1        | Exemple d'Adaptativité: Changement de pas de l'algorithme LMS                                                                                                                                                | 170        |

| C.2        | Exemple de reconfigurabilité: Changement de code                                                                                                                                                             | 170        |

| C.3        | L'approche multiplexage                                                                                                                                                                                      | 172        |

| C.4        | L'approche pagination                                                                                                                                                                                        | 172        |

| C.5        | Plate-forme configurée pour 2 fonctions différentes                                                                                                                                                          | 173        |

| C.6        | Plate-forme avec opérateurs à grains fins pour la sérialisation                                                                                                                                              | 173        |

| C.7        | Fonctions RAKE et annulateur d'interférences multi-étages                                                                                                                                                    | 176        |

| C.8        | Structure de l'étage i                                                                                                                                                                                       | 176        |

| C.9  | Fonction de décision $f_{dec}()$ avec pallier $c$                              | 177 |

|------|--------------------------------------------------------------------------------|-----|

| C.10 | Evaluation de la performance évaluation de l'annulateur d'interférences; SF=2  | 178 |

| C.11 | Evaluation de la performance évaluation de l'annulateur d'interférences; SF=4  | 178 |

| C.12 | Architecture reconfigurable                                                    | 179 |

| C.13 | Chronogramme des flux de donnée en réception et en traitement                  | 179 |

| C.14 | Configuration en mode Rake                                                     | 180 |

| C.15 | Configuration en mode IC                                                       | 180 |

| C.16 | L'efficacité de DSP en utilisant comme mesure le nombre de calcules effectuées |     |

|      | pour différent nombre de trajets                                               | 182 |

| C.17 | La comparaison de trois implémentations                                        | 182 |

| C.18 | IC inter chemin avec estimation de canal                                       | 185 |

| C.19 | Structure du i-ème étage d'annulation                                          | 185 |

| C.20 | Performance au sens MSE du schéma d'estimation propose versus le schéma clas-  |     |

|      | sique (V=0)                                                                    | 187 |

| C.21 | Performance au sens BER du schéma d'estimation propose versus le schéma clas-  |     |

|      | sique (V=0)                                                                    | 187 |

| C.22 | de traitement de base pour le IC avec estimation de canal                      | 188 |

# List of Tables

| 1.1  | Main physical layer characteristics of UMTS                                    | 38  |

|------|--------------------------------------------------------------------------------|-----|

| 1.2  | FDD and TDD differences.                                                       | 42  |

| 1.3  | Major technical differences between CDMA2000 and UMTS                          | 43  |

| 2.1  | The developed algorithms of this Chapter                                       | 46  |

| 2.2  | Number of operations per bit                                                   | 50  |

| 2.3  | The ETSI channel model                                                         | 52  |

| 2.4  | Our equivalent channel model                                                   | 52  |

| 2.5  | Simulation Parameters                                                          | 54  |

| 2.6  | The structure of an heuristic SPV, which is used by the adaptive detector with |     |

|      | variable number of finger and window-based channel estimation                  | 58  |

| 2.7  | Simulation parameters                                                          | 66  |

| 2.8  | Channel Model 1                                                                | 66  |

| 2.9  | The complexity of matrix inversion                                             | 76  |

| 2.10 | The possible configurations of the parameterized computational term            | 86  |

| 2.11 | Interleaver parameters                                                         | 99  |

| 2.12 | Simulation parameters                                                          | 103 |

| 3.1  | Linear Profile for the RAKE combination (37.87 %)                              | 14  |

| 3.2  | Linear Profile for the IC scheme $(47.74 \%)$                                  | 14  |

| 3.3  | The required time (in $\mu sec$ ) for the processing of one UMTS slot          | 15  |

| 3.4  | The device utilization for the computational unit                              | 131 |

| 4.1  | Comparison of the HW implementation alternatives                               | 148 |

| 4.2  | Comparison of the HW mapping approaches                                        | 155 |

| C.1  | Le temps nécessaire (en $\mu sec$ ) pour le traitement d'un "slot" UMTS        | 181 |

| C.2  | L'utilization du FPGA Virtex 4 pour l'unité de calcul                          | 181 |

| C.3  | Les différentes Configurations                                                 | 188 |

16 LIST OF TABLES

# **Notations**

$\dot{V}$

denotes the speed

$x^*$ denotes the conjugate value of the variable x|x|denotes the absolute value of the variable xNis the spreading factor Lis number of channel paths s(t)denotes the transmitted signal r(t)denotes the received signal is the delay of the *l*-th channel path  $au_l$  $h_l(t)$ is the channel coefficient of the l-th path Uis the number of active users denotes the pulse shaping p(t)is the spreading code for the u-th user  $c_u(t)$ Mis the number of RAKE fingers  $T_b$ is the symbol duration  $T_c$ is the chip duration is the data signal of the u-th user  $b_u(t)$ n(t)is the white gaussian noise  $\sigma_l^2$ is the variance of the l-th channel path denotes the decision function  $f_{dec}$ Kis the number of symbols  $\widehat{b}$ is the output of a RAKE combination  $\tilde{b}$ denotes the output of the decision function  $f_{dec}$ Vis the number of IC stages is the threshold for the decision function cis the Ricen factor  $R_f$  $A_i$ is the average received power of the i-th user is the moving average window of the channel estimation  $N_p$ is the coherence time of the channel  $\Delta t_c$ is the maximum Doppler frequency  $f_D$ denotes the l-th estimated channel path  $h_l$ denotes the decision reconfigurability variable G

18 NOTATIONS

# Abbreviations

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BoD Bandwidth on Demand BPSK Binary Phase-Shift Keying

BS Base station

CC Convolutional Code

CCTrCH Coded Composite Transport Channel

CPICH Common Pilot Channel

DCA Dynamic Channel Allocation

DD Decorrelation Detector

DPCH Dedicated Physical Channel

DS-CDMA Direct Sequence Code Division Multiple Access

DSP Digital Signal Processor

DTX Discontinuous Transmission

EDGE Enhanced Data Rates for GSM Evolution

FDD Frequency Division Duplex FEC Forward Error Correction FH Frequency Hopping

FPGA Field Programmable Gate Array

GPS Global Positioning System

HW Hardware

IC Interference Cancelation

IF Intermediate Frequency

ILP Instruction-Level Parallelism

IMT International Mobile Telephony

IPI Inter-Path Interference

ITU International Telecommunication Union

MAC Multiply Accumulate

MAI Multiple Access Interference

MC Multi-Carrier

MF Matched Filter

MLSD Maximum Likelihood Sequence Detection

MMSE Minimum Mean Square Error

20 ABBREVIATIONS

MRC Maximum Ration Combiner

MS Mobile Station MUD Multiuser Detection

OFDM Orthogonal Frequency-Division Multiplexing

OVSF Orthogonal Variable Spreading Factor

PHY Physical

PIC Parallel Interference Cancelation

PN Pseudo-Noise QoS Quality of Service

QPSK Quaternary Phase-Shift Keying

RC Radio Configuration

RNC Radio Network Controller

SF Spreading Factor

SDR Software Defined Radio

SIC Successive Interference Cancelation

SIMD Single-Instruction Stream Multiple-Data Stream

SNR Signal-to-Noise Ratio

SPV Supervisor

SS Spread Spectrum

SSMA Spread Spectrum Multiple Access

SW Software

TDD Time Division Duplex

TDL Time Delay line

TDMA Time Division Multiple Access

TFCI Transport Format Combination Indicator

TPC Transmit Power Control

UMTS Universal Mobile Telecommunications System

WARC World Administrative Radio Conference WCDMA Wideband Code Division Multiple Access

ZF Zero Forcing

3GPP 3<sup>rd</sup> Generation Partnership Project

3G Third Generation2G Second Generation

# The Asturies project

This thesis has been done under the framework of the French RNRT project **ASTURIES** (Approche Système pour Terminaux mUltimodes multistandards ReconfigurableS). The target of this project was the study and implementation of a reconfigurable terminal (Radio Frequency (RF) and Base Band (BB)) which can support different standards and technologies. The partners which have been involved in this project were: PHILIPS FRANCE, France Télécom R&D, STMicroelectronics, CEA-LETI, U. Bordeaux1, STEPMIND, ENST and LIS Grenoble.

Our research group SEN (Systèmes Electroniques Numériques ) of ENST was responsible for the BB and more specifically for the reception block. We had to propose and implement a novel reconfigurable reception scheme for the downlink DS/CDMA communication links. However, the consideration from the project of operational environments with only one user, directed our research activities to high data rate communication links where conventional RAKE schemes are suboptimal and new equalization/reception schemes are necessary. This was the principal motivation of our developed algorithms. The proposed reconfigurable algorithms are based on two main observations. The first one is that the Interference Cancelation (IC) can be applied to the downlink high data rate connections and with the appropriate parameters, can suppress efficiently the interference in the output of the RAKE receiver. The second observation is that IC and RAKE have computational similarities and can be calculated iteratively. These two observations-computational properties can be considered for a reconfigurable design. The combination of RAKE and IC functions for different environments, computational constraints and optimization targets gave many reconfigurable algorithms which are presented analytically in the Chapter 2 of this thesis. Moreover, the focus of the project demonstrator on single user environments, has limited our implementation activities to an inter-path reconfigurable interference cancelation, which is the third proposed algorithm of Chapter 2. The dealing implementations correspond to TigerSHARC-DSP and Virtex (Xilinx)-FPGA devices, as the used demonstrator is a heterogeneous platform consisting of these two devices.

It is important to note that in this thesis, reconfigurability is limited to an intra-standard concept which is used in order to jointly optimize communication link and computational resources. This work differs slightly from classical literature works which consider reconfigurability as a means to support different standards, technologies and modes.

# Introduction

Reconfigurability is a new research topic. In general it is the ability of a system to dynamically change its functionality. However, the type of change, its scope and its implementation, are subject to different approaches in the literature. The varying definitions of the reconfigurability concept tend to produce confusion.

For the algorithmic specialists, reconfigurability is a real-time change of algorithms in order to optimize some well defined quality of service (QoS) metrics, such as the bit error rate (BER) for the physical layer. On the other hand, for the hardware people, reconfigurability is the ability of a piece of hardware to dynamically change its implemented function. There is no right or wrong in these two points of view. The confusion is generated by the multi-layered nature of reconfigurability. Reconfigurability is a multiple concept, it combines algorithms and implementations, and thus a correct definition must include both of them.

In this thesis, we deal with the reconfigurability concept in the domain of DS-CDMA downlink reception. Motivated by the ASTURIES project, we propose many novel detection schemes which use reconfigurability, in order to jointly optimize performance and computational power. The developed algorithms are a combination of three main functions: RAKE demodulation, pilot channel estimation and interference cancelation (IC). The important characteristics of these functions are that they have computational similarities and that they can be calculated iteratively. An important contribution here was the development of algorithms which use the interference cancelation technique for the downlink. In general, the IC technique is a popular, non linear, multiuser detection scheme to suppress the multi-access interference (MAI) and it requires the codes of all the active users. Due to this required input, IC is used only for the uplink, as this information is known to the base station (BS). However, for the case of a high bit rate where a low spreading factor is used, MAI is negligible and inter-path interference is the most important factor of performance degradation. For this case, an IC can be used to mitigate IPI phenomena using as input information only the code of the user under consideration.

In order to implement the developed algorithms, a novel iterative reconfigurable architecture is proposed. The reconfigurability in this architecture is based on the computational similarities and the iterative nature of the three main functions, and it is accomplished without complicated architectural changes. The achieved optimizations of the hardware resources make this architecture suitable for implementations with strict computational constraints, as the terminal units.

Finally, the formalization of the developed reconfigurable algorithms and architectures, has lead to a new reconfigurability concept, which is called "iterative approach". This concept is a new interplay of the general two-layer reconfigurability structure and requires algorithms with a high

24 INTRODUCTION

degree of similarities and iterative computations. This approach is appropriate for the domain of communications and signal processing, which commonly deal with this type of algorithms. This new interplay has been compared to the other approaches of the literature and their advantages have been brought out.

These original contributions will be proposed throughout this thesis which is organized as following.

The first Chapter gives an overview to the DS-CDMA systems and their basic algorithmic schemes which are important for the following Chapter of this thesis. The most important DS-CDMA commercial standards with their major characteristics are also derived.

The second Chapter presents the development algorithms which show the algorithmic dimension of reconfigurability. Our contribution is the development of six different DS-CDMA detection schemes for the downlink case. More specifically, in contrast with the conventional solutions of the literature, the presented algorithms use the reconfigurability concept in order to jointly perform performance and computational power optimization.

The third Chapter is dedicated to the hardware dimension of reconfigurability. Different implementation issues are presented in order to support the algorithmic reconfigurability of the second Chapter. The hardware implementation which is based on the computational similarities and the iterative nature of the supporting algorithms, is the most efficient. In addition to benefits from the support of the algorithms under consideration, it minimizes the required hardware resources. The proposed architecture and implementation is an important contribution of this Chapter.

The fourth Chapter generalizes the conclusions of the previous two Chapters and proposes the iterative reconfigurability concept. Reconfigurability is a two-layer concept which consists of functional and implementation changes. The intermediate layer which is a function of the algorithmic structure and of the nature of the hardware elements, categorizes the different approaches of the literature. The proposed iterative reconfigurability approach is based on the computational similarities and the iterative nature of the supporting algorithms. This approach is an attractive solution for digital communications.

A conclusion and some perspectives are given at the end of this thesis.

# Chapter 1

# 3G communication systems

### 1.1 Introduction

In this Chapter we give a brief introduction to third-generation (3G) communication systems and the technology on which they are based. We present the basic algorithms that we deal with in the following Chapters of this thesis. More specifically, we introduce the Spread Spectrum and CDMA communication systems in Section 1.2. Section 1.3 presents the basic detection schemes from the literature. Finally, a description of the most important commercial 3G communication systems is given in Section 1.4, followed by concluding remarks in Section 1.5.

# 1.2 Spread spectrum communications

The motivation for Spread Spectrum (SS) systems as a means of multiple-access communications is found in Claude E. Shannon's pioneering work in information theory [SHA48]. In particular, in 1948, Shannon derived the maximum channel capacity of a bandlimited communications system as

$$C = W \log_2 \left( 1 + \frac{S}{N} \right) \tag{1.1}$$

In Eq. 1.1, C is the channel capacity (bits/second), W is the transmission bandwidth (in Hz), S is the received signal power (in watts), and N is the total noise power at the receiver. This contribution is important in that it provides a justification for increasing the transmission bandwidth in a communication system, as the capacity is directly related to the transmission bandwidth for a given Signal-to-Noise Ratio (SNR). This idea gave impetus to the use of SS as a means of increasing the available capacity for wireless systems [COO83], [PIC82].

SS may be defined as "a technique in which an auxiliary modulation waveform, independent of the information data, is employed to spread the signal energy over a bandwidth much greater than the signal information bandwidth". The signal is "despread" at the receiver using a synchronized replica of the auxiliary waveform. Fig. 1.1 is an a general diagram to describe SS modulation. Multiplication of two unrelated signals produces a signal whose spectrum is the convolution of the spectra of the two component signals. Thus, if the digital data (binary) signal is relatively narrow-band compared to the spreading signal, the product signal will have nearly the spectrum

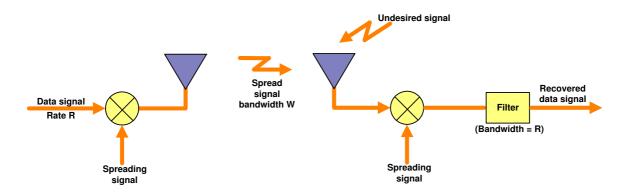

Figure 1.1: Basic spread spectrum technique.

of the wider (spreading) signal. At the demodulator, the received signal is multiplied by exactly the same spreading signal. If this spreading signal, locally generated at the receiver, is lined up (synchronized) with the received spread signal, the result is the original signal plus, possibly, some spurious higher-frequency components outside the band of the original signal, and hence easily filtered to reproduce the original data essentially undistorted. If there is any undesired signal at the receiver, on the other hand, the spreading signal will affect it just as it did the original signal at the transmitter. Thus, even if it is a narrow-band signal in the middle of the band of interest, it will be spread to the bandwidth of the spreading signal. The result is that the undesired (jamming) signal will have a bandwidth of at least W. More specifically, its average density, which is essentially uniform and can be treated as wideband noise, will be

$$N_0 = N/W \quad Watts \cdot second$$

(1.2)

If the data rate is R bits/second, the received energy per bit is

$$E_b = S/R \quad Watts \cdot second \tag{1.3}$$

Now it is generally recognized that, in digital communication systems, Bit Error Rate (BER) performance is a direct function of the dimensionless ratio  $E_b/N_0$ , which for SS signals may thus be expressed as

$$\frac{E_b}{N_0} = \frac{S}{N} \frac{W}{R},\tag{1.4}$$

and hence, the jamming power-to-signal power ratio is

$$\frac{N}{S} = \frac{W/R}{E_b/N_0} \tag{1.5}$$

This establishes that if  $E_b/N_0$  is the minimum bit energy-to-noise density ratio needed to support a given BER, and if W/R is the ratio of spread bandwidth to the original data bandwidth, also called the processing gain, then N/S is the maximum tolerable jamming power-to-signal power ratio, also known as the jamming margin. It is obvious that for a fixed  $E_b/N_0$  and jamming margin, the selection of the appropriate processing gain can guarantee the communication link.

There are two principal types of SS systems, Direct Sequence (DS) and Frequency Hopping (FH) [VIT95]. Direct-sequence signaling is accomplished by phase-modulating the data signal with a pseudo-noise (PN), i.e., pseudo-random, sequence of zeros and ones, which are called chips. The chip modulation is most commonly binary phase-shift keying (BPSK) for simplicity and is achieved by mod-2 adding the PN chip sequence. The number of PN chips per bit is a measure of the processing gain. Quaternary PSK (QPSK) chip modulation, while more complex, is sometimes used to prevent signal capture when a strong interferer drives the receiver into saturation. The second class of SS systems utilizes a frequency-hopping carrier. Here the spreading signal remains at a given frequency for each bit or even for several bits. Thus, locally it is no wider than the data signal, but when it hops to a new frequency, it may be anywhere within the 'spreading' bandwidth W. One fundamental difference between the two techniques is that direct-sequence PN spread signals can be coherently demodulated. With frequency-hopped signals, on the other hand, phase coherence is difficult to maintain when the signal frequency is hopped over a wide range; hence, this modulation is usually demodulated noncoherently.

### 1.2.1 DS-CDMA for personal communications

The enhancement in performance obtained from a DS spread spectrum signal through the processing gain can be used to enable many DS spread spectrum signals to occupy the same channel bandwidth provided that each signal has its own distinct PN sequence. Thus, it is possible to have several users transmit messages simultaneously over the same channel bandwidth. This type of digital communications in which each user (transmitter-receiver pair) has a distinct PN code for transmitting over a common channel bandwidth is called either Code division multiple access (CDMA) or Spread Spectrum Multiple Access (SSMA) [MAR98].

In the demodulation of each PN signal, the signal from the other simultaneous users of the channel appears as an additive interference. The level of interference varies, depending on the number of users at any given time. A major advantage of CDMA is that a large number of users can be accommodated if each transmits messages for a short period of time. In such a multiple access system, it is relatively easy either to add new users or to decrease the number of users without disrupting the system.

# 1.2.2 The wireless propagation channel

The signal transmitted or received by the mobile is subject to multiple reflections, diffractions, and attenuations of its energy which are caused by obstacles like buildings, hills or trees. The effect of these phenomena is to spread the signal in time, so that at the receiver we collect the superposition of several copies of the same transmitted signal arriving at different moments and having random phases and amplitudes. Thus, the multipath fading channel can be presented as a linear time-varying system having an impulse response  $h(t,\tau)$  which is a wide-sense stationary random process in the t-variable.

Furthermore, the channel impulse response can be written at time t as a function of the parameter  $\tau$  using the usual Tapped Delay Line (TDL) representation as:

$$h(t,\tau) = \sum_{l}^{L} \alpha_{l}(t) \cdot e^{j\phi_{l}(t)} \cdot \delta(t - \tau_{l}(t)), \qquad (1.6)$$

where L is the number of resolvable paths,  $\alpha_l(t)$ ,  $\phi_l(t)$  are the amplitude and the phase of the l-th path, respectively, and  $\tau_l$  is the path delay of the l-th path.

Using this equation, there are three quantities that have to be described by statistical methods: path amplitudes  $\alpha_l(t)$ , path phases  $\phi_l(t)$  and delay times  $\tau_l(t)$ . The used statistical model depends on the propagation environment as well as the state of knowledge that we have for it [BRA99], [CHA99], [PRO95]. A successful channel model is the one which represents in the best way the propagation environment under consideration by incorporating only the available information and nothing more [DEB00]. For the statistical model used all along this thesis, we suppose that path phases are uniform distributed, path amplitudes are Raylegh or Rice distributed, and path delays have a constant value. In the follow, we present the two path amplitudes' distributions [PAP02].

## Rayleigh fading

The Rayleigh distribution

$$P_{\alpha}(\alpha) = \frac{\alpha}{\sigma^2} \cdot e^{-\frac{\alpha^2}{2\sigma^2}}, \quad \alpha \ge 0, \tag{1.7}$$

describes the amplitude fading for the case of a superposition of scattered components with approximately identical power. It is appropriate for the modeling of paths amplitudes in outdoor environment. In Eq. 1.7,  $2\sigma^2$  is the variance of the Rayleigh random variable  $\alpha$ .

### Rice fading

The Rice distribution

$$P_{\alpha}(\alpha) = \frac{\alpha}{\sigma^2} \cdot I_0\left(\frac{\alpha \cdot \mu}{\sigma^2}\right) e^{-\frac{\alpha^2 + \mu^2}{2\sigma^2}}, \quad \alpha \ge 0, \tag{1.8}$$

represents a Rayleigh scattering process with a superimposed dominant component. It is appropriate for the modeling of the propagation channel in a satellite environment where a Line-of-Sight (LOS) signal exists. In Eq. 1.8,  $\alpha$  is the Ricean random variable,  $I_0()$  is a modified Bessel function of the first kind, and  $\sigma^2$  and  $\mu$  are the parameters of the distribution.

## 1.3 CDMA detection

# 1.3.1 The conventional RAKE receiver

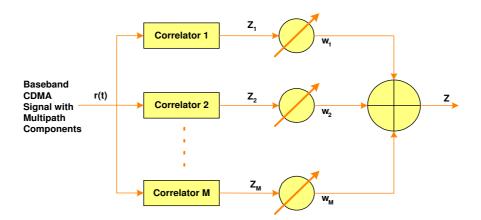

In 1958, Price and Green proposed a method of resolving multipath problems using wideband pseudorandom sequences modulated onto a transmitter using other modulation methods (AM or FM) [PRI58]. The pseudorandom sequence has the property that time-shifted versions of itself are almost uncorrelated. Thus, a signal that propagates from transmitter to receiver over multiple paths (hence multiple different time delays) can be resolved into separately fading signals by cross-correlating the received signal with multiple time-shifted versions of the pseudorandom sequence. The receiver is called RAKE receiver since the block diagram looks like a garden rake. Fig. 1.2 shows a block diagram of a typical RAKE receiver.

The RAKE receiver is a simple implementation of the matched filter which accounts for the most important components of the multipath propagation channel. It consists of a bank of demodulators, called RAKE fingers, each tracking a path of the channel, and a multipath

Figure 1.2: RAKE receiver correlator.

combiner which combines the outputs of these fingers (the multipath components) in proportion to their strengths. This combining is a form of diversity and can help reduce fading. Multipath components with relative delays of less than Dt = 1/W cannot be resolved and, if present, contribute to fading; in such cases, Forward Error Correction (FEC) and power control schemes play a dominant role in mitigating the effects of fading.

The outputs of the M correlators are denoted as  $Z_1, Z_2, ..., Z_M$ . The weights of the outputs are  $w_1, w_2, ..., w_M$  respectively. The weighing coefficients are based on the power or the SNR from each correlator output [MAN04], [SIN02]. If the power or SNR is small from a particular correlator, it is assigned a small weighing factor. The composite signal is given by

$$Z = \sum_{m=1}^{M} w_m \cdot Z_m \tag{1.9}$$

As for the weighing coefficients, different approaches exist in the literature. Among them, the most important are the selection combiner, the equal-gain combiner and the Maximum-Ratio Combiner (MRC) [HAN00]. The selection combiner is the simplest of all the schemes. In its ideal application, it chooses the signal with the highest instantaneous SNR, so the output SNR is equal to that of the best incoming diversity component. The last two combiners require the estimation of some channel parameters and thus this type of detection can be considered as coherence detection. The equal-gain combiner requires that the receiver can estimate the phase offsets on each of the M received components. These estimated phases are the weighing coefficients of the equal-gain combination approach. According to equation 1.9, the equal-gain combination corresponds to  $w_m = e^{-j\phi_m}$ , where  $\phi_m$  is the estimated phase offset of the m-th diversity component. If, in addition, the received signal power is estimated for each of the diversity components and it takes part in the previous combination, the resulting combination technique is called MRC. Based on the general equation 1.9, the MRC corresponds to  $w_m = \hat{\alpha}_m e^{-j\phi_m}$ , where  $\widehat{\alpha}_m$  is the estimated signal power of the m-th diversity component. The MRC is the most efficient one when a reliable power estimation exists, and thus it is considered as the combination approach of the conventional RAKE receiver in the following Chapters of this thesis [ALO97].

In CDMA cellular/PCS systems (commercial IS-95 system), the forward link (base station

(BS) to terminal (MS)) uses a three-finger RAKE receiver, and the reverse link (MS to BS) uses a four-finger RAKE receiver.

### Channel estimation

The coherence detection introduced by the combination scheme of the conventional RAKE receiver requires the parameter estimation of the propagation channel. These parameters consist of the phase offset and the power amplitude for each diversity component, as well as the path delay.

Channel estimation is a huge research topic, and many approaches are proposed in the literature. In general, we can find all the classical algorithms of signal processing for parameter estimation, applied for channel estimation [HAY02], [MAM02]. The best trade-off between quality of estimation and implementation complexity is always the practical selection criterion of a channel estimation algorithm.

In this thesis, we suppose a simple data-aided channel estimation based on a pilot physical channel, which is transmitted in parallel with the data channel. In this case, the channel estimation is performed by a correlation of the received signal with different phases of the pilot code. Multipath arrivals at the receiver unit manifest themselves as correlation peaks that occur at different times. The time of each peak, relative to the first arrival, provides a measurement of the path delay. Moreover, the peak amplitude and phase provide an estimation of the path amplitude and phase, respectively. The complex amplitude estimation (phase and power envelope) needs to be averaged over a reasonably long period, while coherence time sets the upper limit for the averaging time (i.e., the channel should not change during the estimation). This process is necessary in order to average out the Gaussian noise and improves the estimation quality.

The required estimation speed for impulse response measurements depends on the mobile speed and the radio environment. The faster the mobile station is moving, the faster the measurements need to be performed in order to catch the best multipath components for the RAKE fingers. Furthermore, in a long delay spread environment, the scanning window needs to be wider.

#### The limitations of the RAKE receiver

DS-CDMA systems support a multitude of users within the same bandwidth by assigning different - typically unique - codes to different users for their communications, in order to be able to distinguish their signals from each other. When the transmitted signal is subjected to hostile wireless propagation environments, the signals of different users interfere with each other and hence CDMA systems are interference- limited due to this multiple access interference (MAI), generated by the users transmitting within the same bandwidth simultaneously. Moreover, the interference between the different paths of the channel, which is called Inter-Path interference (IPI), can further degrade the achieved performance for the cases where a low spreading factor is used.

The conventional RAKE receiver is optimized for detecting the signal of a user for a single-user environment. However, even its simple structure and implementation, it is inefficient for the environments with MAI and IPI interference, since the interference is treated as unstructured gaussian noise and the knowledge of the channel impulse response (CIR), or the spreading

sequences of the interferers, is not exploited. In order to mitigate MAI and IPI phenomena, a range of advanced detectors have been proposed in the literature, which will be reviewed in the forthcoming subsections.

#### 1.3.2 The advanced receiver schemes

These schemes try to suppress MAI and IPI interference in order to improve performance and capacity. They are popular under the term Multi-User Detection (MUD), as for the detection of a user, they require information regarding the other (interfering) users [DUE95], [KOU00], [MOS96]. Because of the huge complexity of the optimal MUD based on a Maximum Likelihood Sequence Estimation (MLSE) criterion, many suboptimal MUD techniques have been developed in recent years. These suboptimal MUDs can be divided in two categories: linear MUDs (e.g. the Decorrelation Detector (DD), Minimum Mean Square Error (MMSE) detector) and nonlinear interference cancelers, such as the Successive Interference Canceler (SIC) and the Parallel Interference Canceler (PIC). Interference cancelation has a lower complexity than decorrelation and MMSE detection and can easily be implemented in hardware. In addition to this, in a synchronized CDMA system over a AWGN channel, nonlinear interference cancelation is superior to any type of linear MUD.

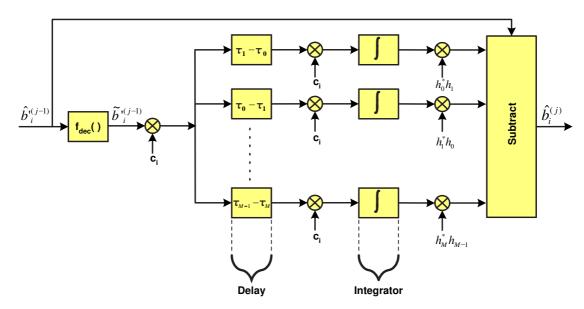

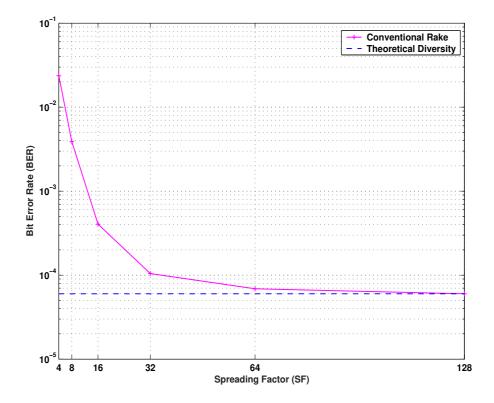

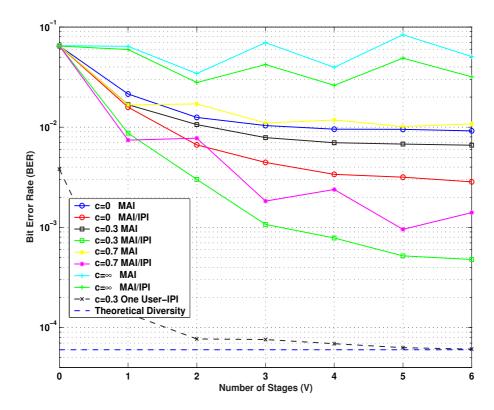

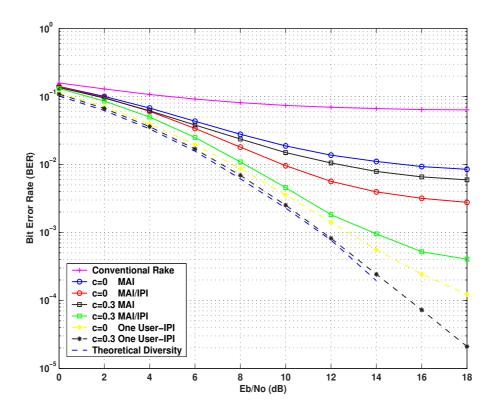

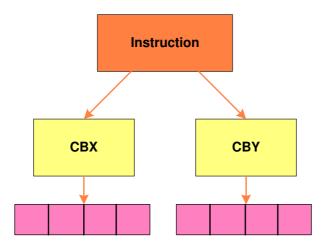

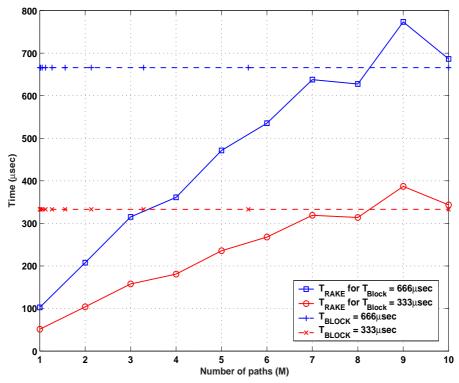

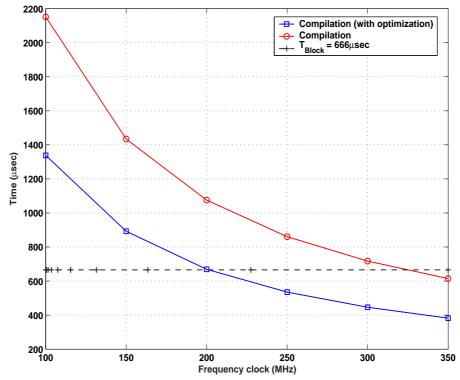

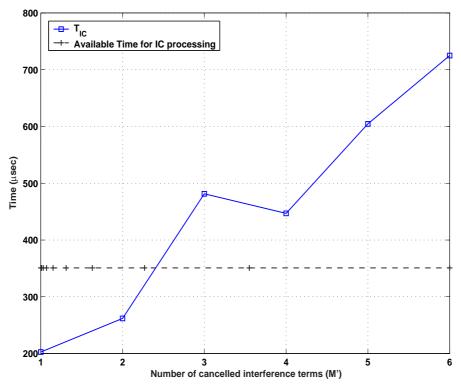

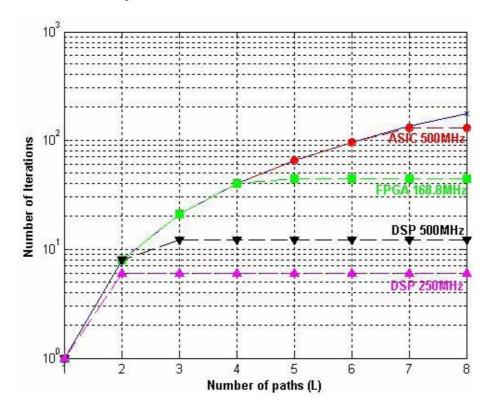

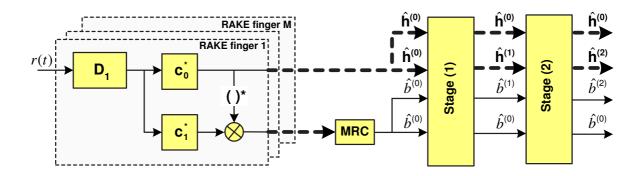

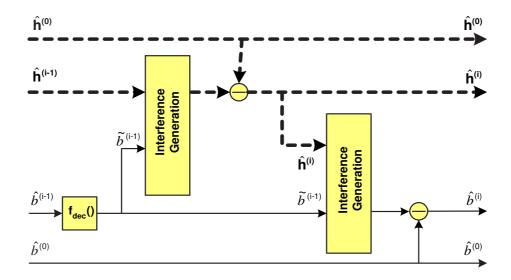

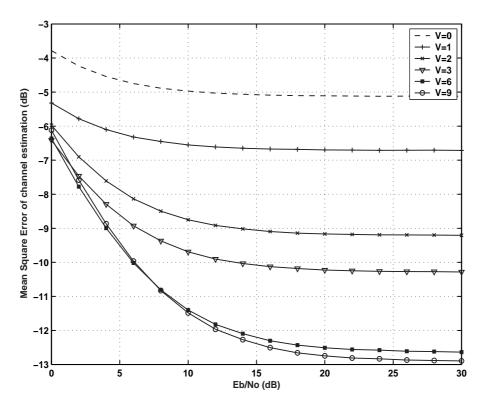

### Maximum Likelihood Sequence Estimation (MLSE) Detector