# Contre-mesures géométriques aux attaques exploitant les canaux cachés

Sylvain Guilley

### ▶ To cite this version:

Sylvain Guilley. Contre-mesures géométriques aux attaques exploitant les canaux cachés. domain\_other. Télécom ParisTech, 2007. English. NNT: . pastel-00002562

### HAL Id: pastel-00002562 https://pastel.hal.science/pastel-00002562

Submitted on 25 Jun 2007

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# GET / Télécom Paris CNRS – LTCI (UMR 5141)

#### Thèse de doctorat:

Contre-mesures géométriques aux attaques exploitant les canaux cachés

#### Jury:

- David NACCACHE, professeur à Paris II et membre du groupe crypto de l'ENS (rapporteur)

- Jean-Jacques QUISQUATER, professeur à l'Université Catholique de Louvain-la-Neuve (rapporteur)

- Marc RENAUDIN, professeur à l'INPG (examinateur)

- Pierre-Yvan LIARDET, docteur, cryptologue chez STMicroelectronics (examinateur)

- $\bullet\,$ Francis JUTAND, professeur, directeur scientifique du GET (président du jury)

- Yves MATHIEU, directeur d'études à l'ENST Paris (examinateur)

- Renaud PACALET, ingénieur d'études à l'ENST Sophia Antipolis, responsable du laboratoire LabSoC (directeur de thèse)

Sylvain GUILLEY

January 10th, 2007

# Résumé de la thèse en français

Ce travail de thèse concerne la sécurisation des circuits électroniques contre les attaques (dites « par la bande ») qui visent leur implémentation. Les algorithmes cryptographiques ont été traditionnellement étudiés pour résister aux attaques théoriques. Néanmoins, dès lors que ces algorithmes sont mis en œuvre sur des dispositifs concrets, de nouvelles attaques deviennent possibles. Effectivement, de l'information peut être extraite passivement (par observation) ou activement (par injection de fautes) des circuits [43]. Cette information complémentaire, communément appelée « canal caché », apporte un pouvoir supplémentaire aux attaquants. Les canaux cachés les plus populaires sont le temps de calcul, la consommation électrique, le rayonnement, la température et le bruit. Les dispositifs les plus vulnérables sont ceux qui sont alimentés de l'extérieur, comme les cartes à puce avec ou sans contacts, ou les appareils portables en général. Les radiations électromagnétiques constituent également une fuite d'information, qui permet notamment à un attaquant de réaliser des attaques à distance. Ainsi, d'une manière générale, tous les systèmes électroniques, nomades ou non, dont par ailleurs l'utilisation par le grand public ne cesse de croître, sont de potentielles cibles d'attaques malveillantes. La sécurisation du matériel est donc un enjeu sociétal. L'appropriation des systèmes électroniques embarqués (typiquement à base de TPM) ne pourra en effet perdurer que si leur niveau de sécurité apporte des garanties prouvées, inspirant par là-même aux utilisateurs finals une confiance suffisante dans la technologie.

Nous montrons tout d'abord que les attaques sur les canaux cachés (ou Side-Channel Attacks, SCA) sont des attaques structurelles, c'est-à-dire inhérentes au traitement de l'information. Il se trouve par ailleurs que les algorithmes cryptographiques sont spécialement sensibles aux attaques SCA, à cause des propriétés constitutives de certaines fonctions booléennes utilisées. Dans le cas du chiffre symétrique, nous montrons que les SCA sont inéluctables, car la fuite d'information minimale se trouve justement être égale à la clé secrète. De plus, les contraintes technologiques de mise en œuvre accentuent la force des attaques. L'étude de l'attaque montrera que le talon d'Achille principal est l'architecture RTL (Register Transfer Level) de l'opérateur cryptographique. Effectivement, les transferts de registres rendent possible une attaque dite en « distance de Hamming », particulièrement efficace.

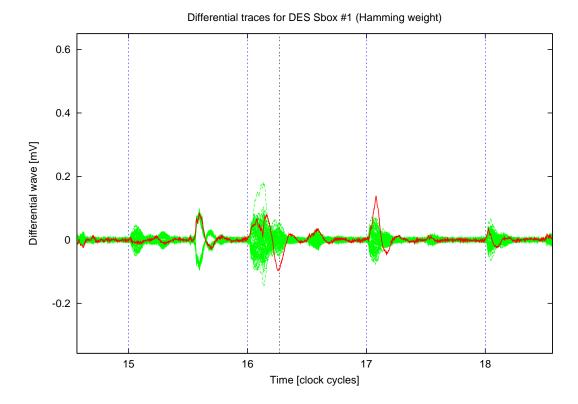

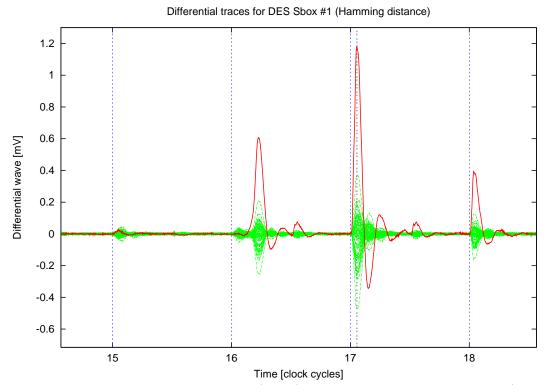

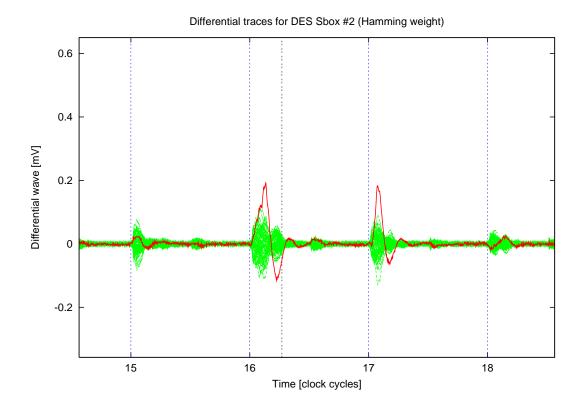

Nous continuons en recherchant des moyens permettant de ne fuir pratique-

ment aucune information exploitable par un attaquant. Sur l'exemple d'un coprocesseur DES itératif, nous montrons comment exploiter concrètement les fuites d'information. Nous décrivons l'attaque par analyse différentielle de consommation (DPA) de DES en poids et en distance de Hamming sur le premier et le dernier tour de l'architecture du crypto-processeur non protégé. Des considérations subtiles, comme l'influence de la diaphonie, de la mémorisation capacitive et du moyennage temporel des traces de consommation, sont présentées. Ces effets, du second ordre, sont en effet à même d'induire de nouvelles failles de sécurité. Il s'avère donc que les portes logiques elles-mêmes possèdent des caractéristiques critiques à protéger.

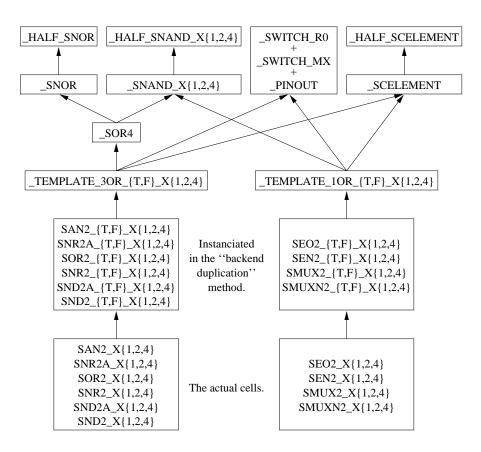

Les failles de sécurité mises en évidence sur l'exemple de DES nous conduisent à émettre des recommandations pour la conception d'un opérateur robuste, basées sur l'usage d'une bibliothèque de portes et d'une stratégie de routage géométriquement équilibrées. Les portes logiques sont conçues de sorte à minimiser les violations de symétrie. Une contrainte supplémentaire a été de rendre ces portes logiques interopérables avec les portes d'une bibliothèque standard de STMicroelectronics (à savoir HCMOS9GP, du procédé 130 nanomètres). La stratégie de routage équilibré obéi aux mêmes critères. La conservation de la symétrie est traitée avec un soin tout particulier, aboutissant à la méthode générique de « backend duplication ». Pour autant, la compatibilité avec les outils de conception assistée par ordinateur (CAO) n'est pas négligée. La backend duplication s'implémente par de simples ajouts de contraintes lors du placement-routage, ce qui rend la méthode adaptable à tout flot de conception propriétaire.

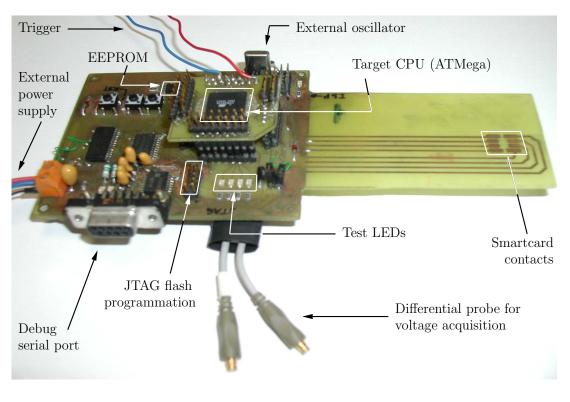

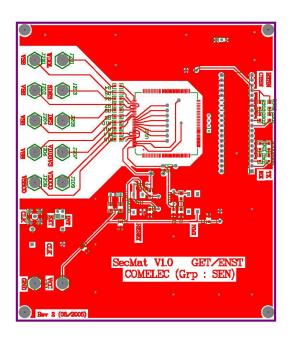

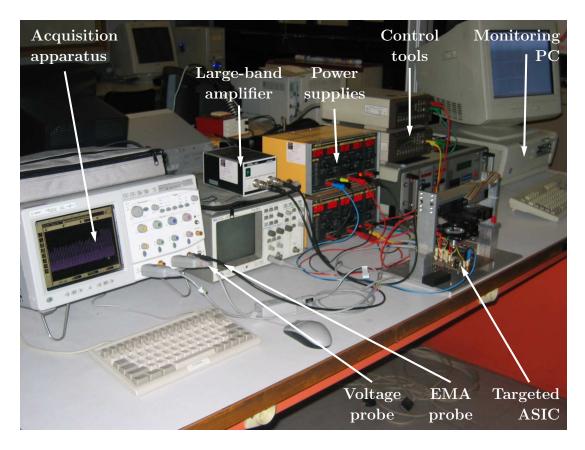

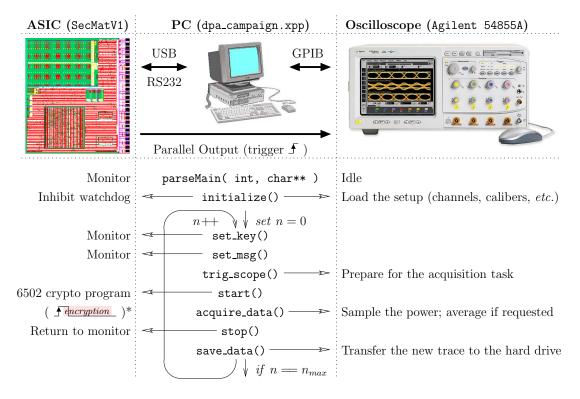

La plateforme d'analyse et les logiciels d'attaques sont décrits dans les annexes du manuscrit. Les mesures de canaux cachés ont été réalisés sur des circuits cousus-main (Application Specific Integrated Circuits, ou ASICs) conçus dans le cadre des travaux de cette thèse. La chaîne d'acquisition s'est progressivement enrichie de fonctionnalités, à tel point qu'elle est actuellement devenue un laboratoire d'évaluation sécuritaire des systèmes embarqués. Les logiciels d'analyse de traces ont également été améliorés au cours des travaux. Les algorithmes mis en œuvre dans les attaques présentées dans ce manuscrit sont désormais plus puissants de plusieurs ordres de grandeurs.

Le reste de cette section présente les idées directrices et les enchaînements de la thèse, les résultats et les conclusions, en s'appuyant sur l'articulation logique entre les cinq chapitres.

### Chapitre 1 : Cryptographie physique

Ce chapitre présente la nature des vulnérabilités des circuits électroniques, dans la situation où un attaquant est en mesure d'acquérir des mesures physiques pendant son fonctionnement. Par rapport au scénario d'une cryptanalyse conventionnelle, le contexte est donc plus riche : les attaques « logiques » sont toujours possibles, mais en plus les attaques « physiques » deviennent réalisables.

Les systèmes électroniques peuvent être modélisés par des couches d'abstraction (dites « OSI »). Les attaques, logiques comme physiques, peuvent cibler chacune de ces couches. Ceci signifie que la sécurité d'un système est égale à celle du maillon le plus vulnérable. Or il s'avère que dans le domaine des systèmes embarqués, c'est actuellement la couche la plus basse, à savoir la couche physique, qui est la plus exposée et la plus facilement attaquable en pratique. Ceci motive donc l'étude de telles attaques et la définition de conditions nécessaires pour accroître le niveau de sécurité de la couche physique.

Dans le contexte d'attaques sur la couche physique, l'attaquant dispose d'un potentiel de frappe impressionnant. Moyennant certaines hypothèses, toute variable logique peut être soit lue soit écrite [43].

Nous appelons attaques sur les canaux cachés les attaques passives, où les données internes ne peuvent qu'être consultées. Lorsque l'attaquant a le pouvoir supplémentaire de les altérer, nous parlerons d'attaques par injection de fautes. Cette catégorie d'attaque, non abordée dans le cadre de cette thèse, est également dite « active ».

Maintenant, il n'est souvent pas concevable à un prix raisonnable d'accéder arbitrairement aux variables internes des circuits cryptographiques. Les attaques physiques ne sont donc pas totalement en « boîte blanche ». La bon niveau de modélisation est celui de la « boîte grise » :

- les canaux cachés apportent une information globale (sur plusieurs variables simultanément) et intégrée (sur plusieurs valeurs consécutives), et

- les injections de fautes touchent également plusieurs nœuds, et ce de façon non localisée dans le temps.

En résumé, les attaques physiques ne sont pas chirurgicales. Si elles l'étaient, il n'est pas difficile de comprendre qu'aucune implémentation ne leur résisterait. La barrière à franchir serait celle de la rétro-conception : il s'agit de pouvoir interpréter la masse d'information que l'on est en mesure d'accéder, pour extraire uniquement celle qui est pertinente. Néanmoins, des techniques de fouille de données (data mining) éprouvées permettent aisément de répondre à ce problème de gestion de la complexité.

Par ailleurs, les données seront souvent bruitées. La mesure physique, surtout de quantités nanoscopiques, n'est pas parfaite. De même, l'injection de fautes ne peut pas être contrôlée avec une précision arbitraire. Ce caractère aléatoire conduit à la définition d'attaques statistiques. Nous investiguerons surtout l'analyse différentielle de consommation, qui consiste en une corrélation statistique

d'un jeu de données avec un modèle de fuite. D'autres attaques statistiques ne nécessitent aucune connaissance préalable du circuit attaqué. Il s'agit par exemple de l'IPA (*Inferential Power Analysis* [32]) ou des attaques par patron (aussi appelées template attacks [25]). Néanmoins, celles-ci nécessitent une phase d'entraînement sur un circuit clone pour acquérir de la connaissance sur le fonctionnement de la victime. Nous n'aborderons pas ces attaques – néanmoins prometteuses – dans ce manuscrit.

À l'inverse, nous supposerons dans ce travail que non seulement l'algorithme utilisé, mais également le dessin des masques de son implémentation, sont connues de l'attaquant. Il s'agit donc du scénario d'attaque le plus flexible. Dans le même ordre d'idée, nous autoriserons un attaquant à faire un nombre d'appels non borné aux opérations cryptographiques. Cela signifie que l'on suppose que toutes les contre-mesures « haut-niveau » ont été désactivées ou contournées. Bref, le niveau de sécurité envisagé est celui d'une implémentation nue, qui doit se défendre simplement au niveau où on l'attaque, à savoir sur la couche physique.

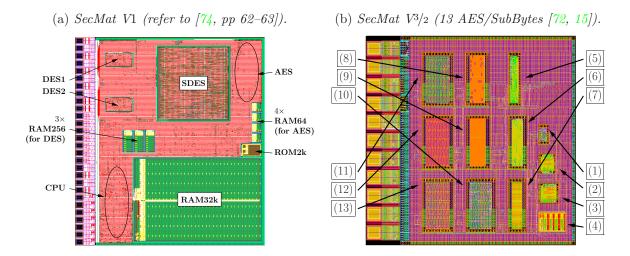

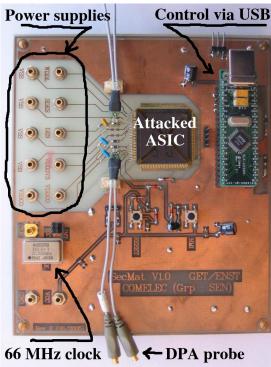

Pour évaluer des contre-mesures, nous avons réalisé des prototypes de circuits cousus main (ASIC – Application Specific Integrated Circuits). Dans la même optique d'évaluation sécuritaire que celle mentionnée plus haut, ces circuits donnent à l'attaquant un signal de synchronisation avec les opérations cryptographiques et permettent un accès aisé aux canaux cachés (par exemple la consommation électrique instantanée ou le rayonnement électromagnétique).

Dans la conception des contre-mesures, la priorité a été résolument mise sur la sécurité, en évitant tout compromis sur les performances. La motivation de cette approche radicale est simple : notre démarche est de prouver qu'il existe une façon de rendre impossible les attaques sur les canaux cachés. Si, même en investissant le prix maximum, en terme de temps de calcul, de surface d'implémentation et d'énergie consommée, notre solution reste faillible face aux attaques passives, alors aucun compromis ne sera résistant. À l'inverse, si cette solution est fructueuse, il pourra être envisagé d'optimiser les performances, en réduisant de façon concomitante le niveau de sécurité, que l'on suppose donc surévalué. Une telle étude ouvrira la porte à de nombreuses solutions technologiques, intéressantes à deux points de vue :

- 1. Il s'agira de la première fois qu'un nouveau critère, à savoir la « sécurité », pourra être intégré au triangle canonique vitesse, surface, consommation de l'adéquation algorithme-architecture; En d'autres termes, des options de sécurité vont pouvoir émerger dans les outils logiciels CAO de conception automatique de circuits.

- 2. La sécurité pourra être mesurée en unité monétaire, et également pour la première fois, il sera concevable de dégrader le niveau de sécurité au profit des performances, alors que jusqu'à présent, dans la conception des cryptographes, la sécurité est considérée comme un attribut non négociable.

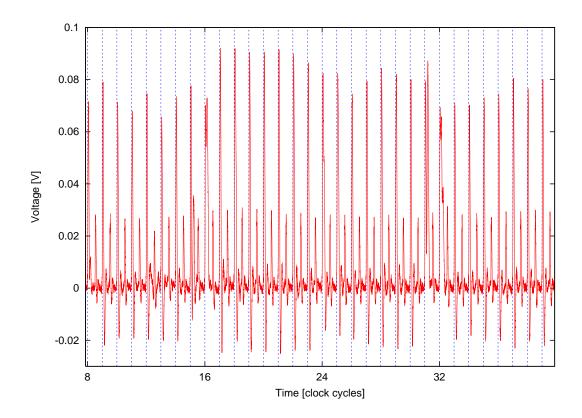

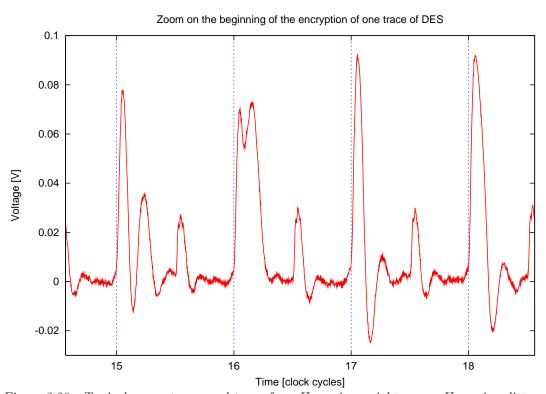

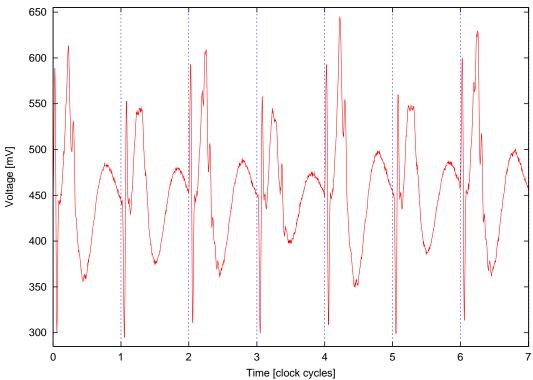

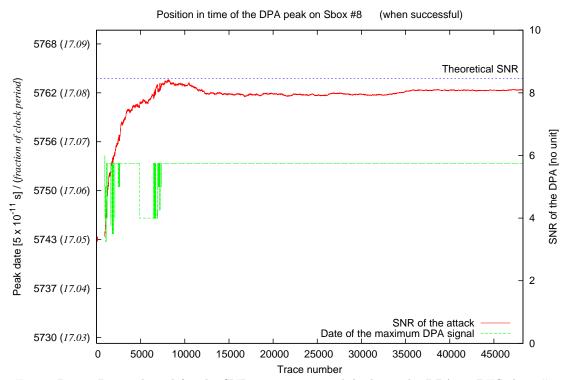

Les analyses de canaux cachés fournies dans cette thèse sont rassemblés en annexe, afin ne pas surcharger le corps du document. Contrairement à la grande ma-

jorité des publications scientifiques du domaine, nous avons pris soin de préciser les unités de grandeurs physiques et de resynchroniser les traces avec le déroulement de l'algorithme cryptanalysé. Il s'agit de la première étude en consommation précise au cycle près de matériel électronique. La résolution temporelle est de loin supérieure à ce qui est *stricto sensu* nécessaire pour réussir une attaque : les acquisitions sont réalisées au rythme de 20 milliards de point par seconde sur des circuits tournant à 32 ou 66 MHz. Ainsi, plusieurs centaines d'échantillons sont disponibles par période d'horloge.

Enfin, il convient de comparer la force des attaques physiques et logiques. Si l'on ne considère que le temps de traitement des données, voilà deux chiffres permettant de comparer la puissance relative des deux types d'attaques sur l'algorithme de chiffrement symétrique DES [71]:

- un ordinateur de bureau typique est capable d'exécuter  $5\,369\,726 \sim 2^{22}$  chiffrements DES par seconde (performance obtenue avec la commande "openss1 speed des"),

- un oscilloscope met une seconde pour l'acquisition d'une trace de consommation (cas très défavorable avec du matériel bas de gamme).

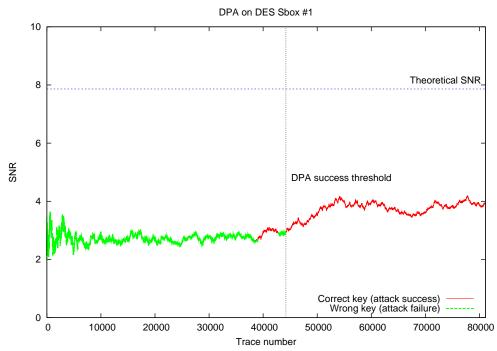

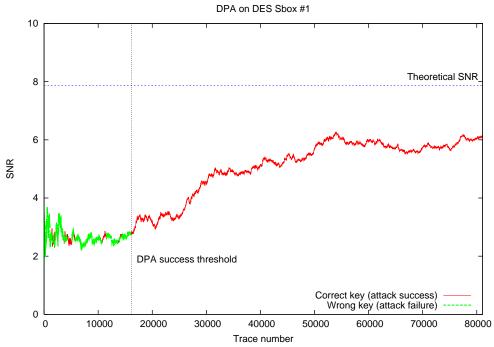

Cela signifie qu'une attaque logique (la recherche exhaustive des 56 bits de la clé) est aussi puissante qu'une attaque physique (une analyse différentielle de consommation) si l'on réussit celle-ci en  $2^{56-22}=2^{34}$  traces, soit environ 17 milliards de traces. Or, sur les implémentations non protégées, les attaques physiques réussissent souvent après analyse de moins de mille (disons  $2^{10}$ ) traces. Les résultats du chapitre 3 démontrent cette assertion. La conclusion est donc que les attaques physiques sont, dans l'état de l'art actuel, de plusieurs ordres de grandeurs plus puissantes que les cryptanalyses logiques. Le danger qu'elles représentent est donc bel et bien réel, ce qui motivera au chapitre 4 la recherche de contre-mesures efficaces.

### Chapitre 2 : Immanence des canaux cachés

Ce chapitre montre que, quelque soit l'algorithme de chiffrement utilisé, une analyse par les canaux cachés permet d'extraire l'intégralité de la clé. Tout d'abord, un modèle de dissipation logique est présenté. Lorsque des contre-mesures appropriées ne sont pas prises, le modèle démontre que l'information minimale qui est fuie se trouve être la clé. Ensuite, un modèle de l'attaque est présenté. Il montre qu'une attaque sur les canaux cachés est d'autant plus puissante que l'algorithme attaqué est robuste du point de vue cryptanalytique. La validité du modèle s'étend aussi bien aux algorithmes à clé secrète de type Feistel (comme DES [71]) qu'aux réseaux de permutation-substitution (comme AES [72]). Enfin, ce chapitre se termine sur des remarques importantes au sujet de l'implémentation pratique de l'analyse différentielle de consommation.

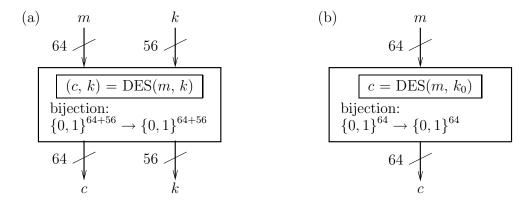

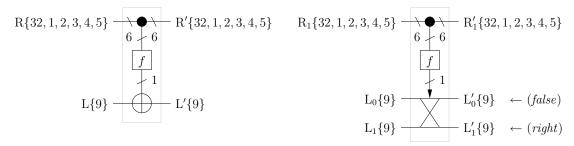

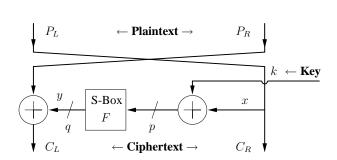

Nous qualifions une attaque de « structurelle » quand elle s'applique à une classe générique d'algorithmes. Les attaques sur les canaux cachés sont structurelles, car elles concernent tous les algorithmes qui dissipent une quantité physique corrélée à un secret. Nous montrons comment un algorithme de chiffrement symétrique tel que DES est obligé de fuir de l'information. Dans la figure 1, il apparaît que :

- (a) soit l'algorithme dissipe logiquement la clé secrète k,

- (b) soit il est spécialisé pour une clé  $k_0$ , et s'expose par là même à une rétroconception ou à une divulgation publique de son implémentation.

Ainsi, le cas (b) est naturellement exclus par le principe de Kerkhoff. Le cas (a) montre qu'il est nécessaire de détruire la clé k avant de diffuser la sortie (c,k) de la boîte chiffrante. Cette destruction d'une entropie de 56 bits s'accompagne physiquement d'une dissipation corrélée à la clé, car celle-ci est nécessairement stockée dans une ressource matérielle (registre, mémoire, etc.) qui devra être mise à zéro ou masquée par toute autre grandeur indépendante de la clé.

FIG. 1 – Conception abstraite d'un chiffrement symétrique (ici, le crypto-système DES [71]), (a) générique dans la clé k ou (b) personnalisée pour une clé donnée de 56 bits  $k_0$ .

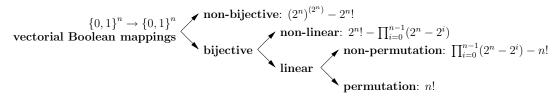

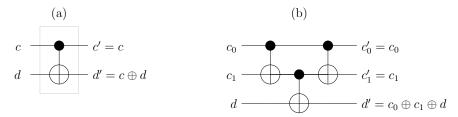

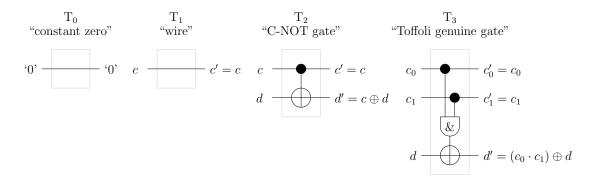

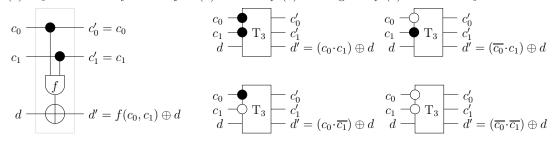

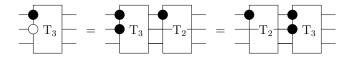

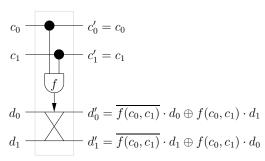

Il existe certes des méthodes théoriques permettant de réaliser une opération sans dissiper d'énergie sur la durée totale du calcul. Deux façons de procéder s'appuient sur des styles de logiques proposés par Toffoli et Fredkin:

- 1. La logique réversible [107] consiste à décomposer les bijections booléennes vectorielles sur des primitives *a priori* non dissipatives.

- 2. La logique conservative [35] consiste à calculer à poids de Hamming constant. Un modèle de calcul, dit « à boules de billard », permet effectivement d'imaginer un mode de calcul sans dissipation.

Néanmoins, aucune implémentation pratique de ces logiques n'a encore vu le jour, ce qui motive une recherche de solutions avec les procédés technologiques actuels, comme la logique CMOS [65] par exemple.

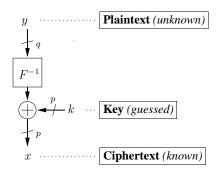

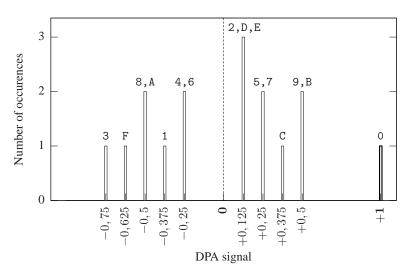

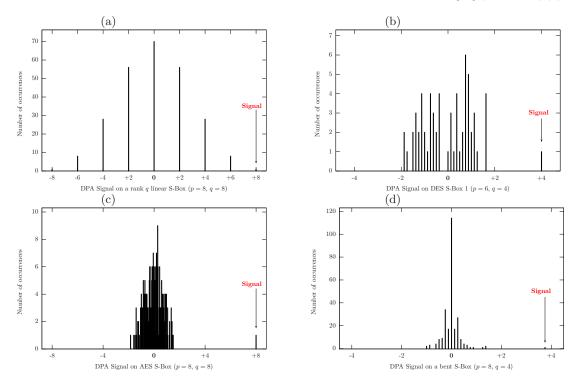

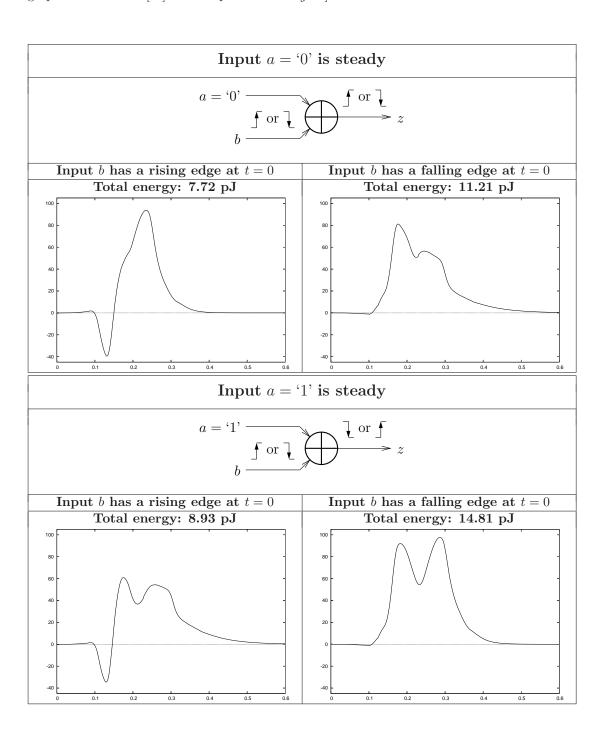

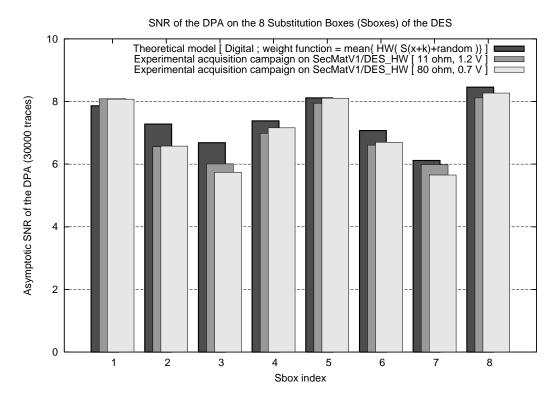

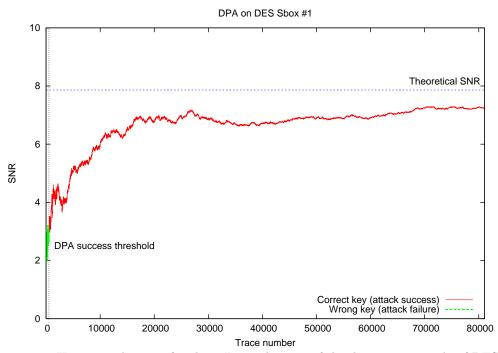

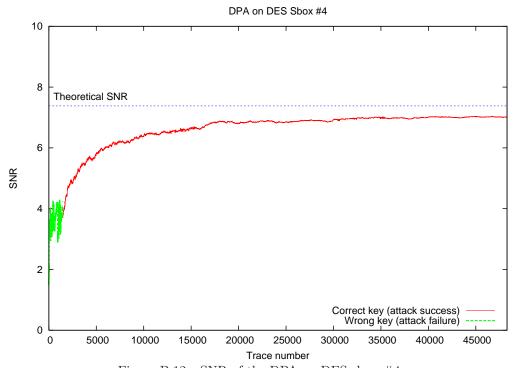

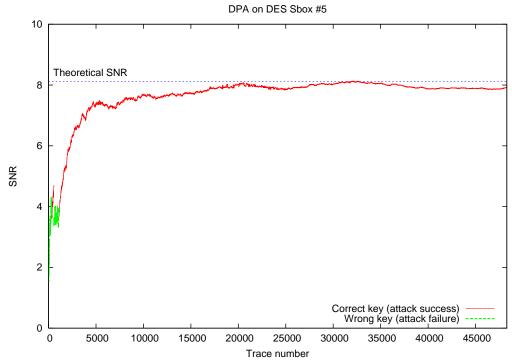

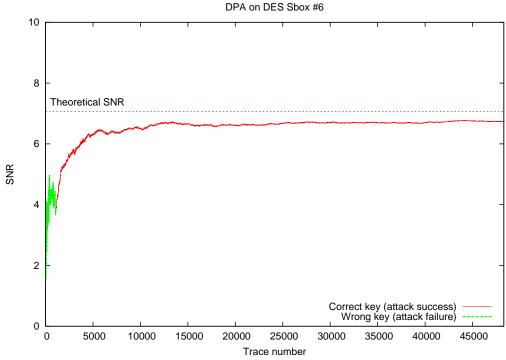

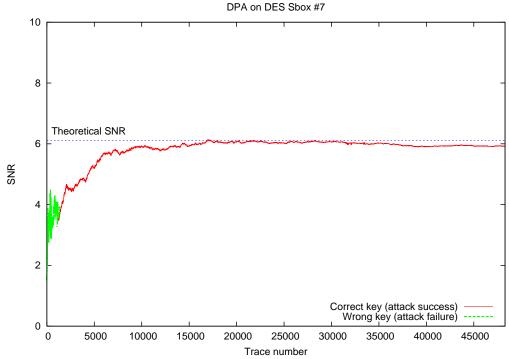

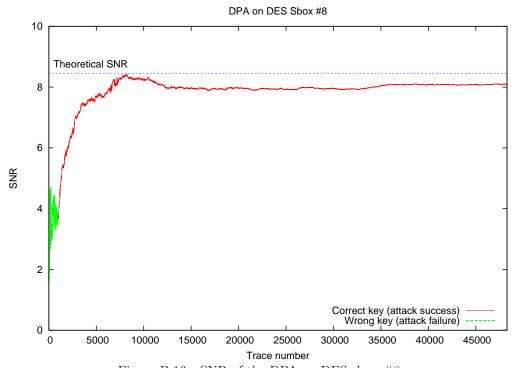

Un modèle de l'attaque DPA est présenté. Il s'appuie sur la modélisation simple de la consommation : toutes les portes consomment le même quantum d'énergie quand elles commutent. Il s'agit donc d'un modèle basé sur l'étude de l'activité logique. Lorsque ce modèle est appliqué à l'attaque DPA, qui cible soit le premier, soit le dernier tour, il se trouve que les opérations linéaires n'interviennent pas. Seule les opérations non-linéaires, qui se réduisent dans la plupart des cas à l'utilisation d'une table de substitution (dite « sbox », et notée F ou S, opérant de  $\{0,1\}^p$  dans  $\{0,1\}^q$ ) impacte le modèle d'attaque. Les résultats [89] sont que :

- la corrélation maximale est obtenue pour l'hypothèse de clé correcte. Cette observation provient de l'application du théorème de Cauchy-Schwarz sur la fonction pseudo-booléenne d'auto-corrélation.

- Les corrélations sont, en moyenne, nulles,

- ce qui prouve qu'il existe des corrélation pour les hypothèses de clé erronées (appelée « pics fantômes » – ou aussi « ghost peaks » dans la littérature scientifique anglaise).

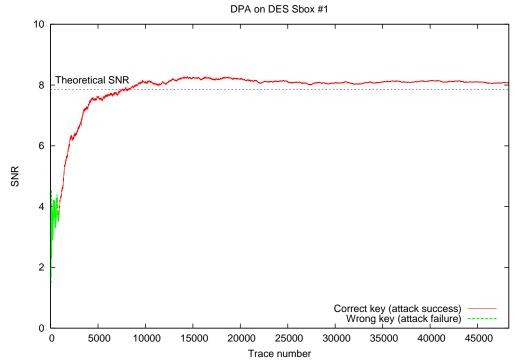

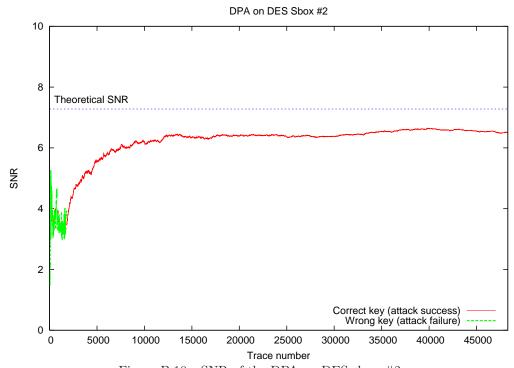

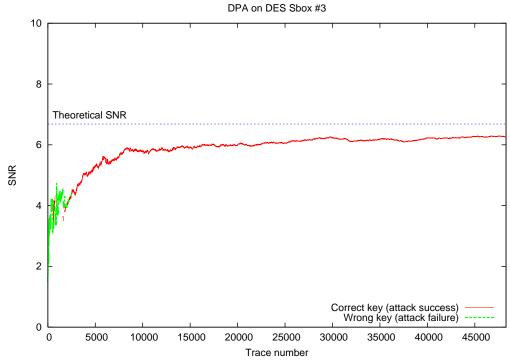

- La qualité de l'attaque peut donc se mesurer par un rapport signal-à-bruit (SNR), qui ne dépend que de la structure de l'algorithme, à savoir aux propriétés des boîtes de substitution utilisées.

- De plus, le rapport signal-à-bruit ne dépend pas de la clé, ce qui démontre qu'il n'y a pas de clé faible en attaque DPA.

Le rapport entre le SNR de l'attaque DPA et les sbox est caractérisé par les deux relations suivantes, qui définissent des bornes inférieures :

$$\begin{split} \mathbf{SNR}(\mathbf{DPA})(F) & \geq & \frac{2^{\frac{3p}{2}-2}}{q\,\Lambda_S^2} = \mathcal{O}\left(\frac{1}{\Lambda_S^2}\right)\,,\\ \mathbf{SNR}(\mathbf{DPA})(F) & \geq & \frac{2^p}{\Delta_S} = \mathcal{O}\left(\frac{1}{\Delta_S}\right)\,. \end{split}$$

Les deux quantités  $\Lambda_S$  et  $\Delta_S$ , définies dans [34], sont respectivement les caractéristiques linéaires et différentielles des sboxes. Elles sont d'autant plus petites que la sbox est solide face aux cryptanalyses linéaires ou différentielles. Ainsi, mieux un système de chiffrement est protégé contre les attaques logique, plus facilement il est attaquable via les canaux cachés.

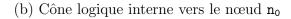

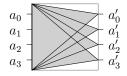

(a) Inter-pénétration de cônes logiques

FIG. 2 – Illustration de la factorisation des cônes de logique sur une fonction combinatoire de 4 bits vers 4 bits  $(a[0..3] \rightarrow a'[0..3])$ .

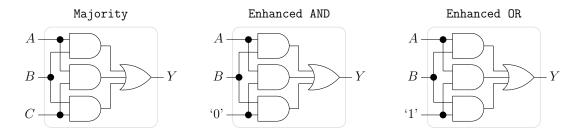

Une contre-mesure possible contre la DPA serait d'agrandir la taille des boîtes de substitution ou de faire en sorte que de nombreux (idéalement tous) bits de clé interviennent dans le calcul de confusion (rôle dévolu aux sbox) dès le premier tour. Ces contre-mesures souffrent néanmoins d'un problème d'intégrabilité. Toutes deux accroissent la taille de l'implémentation de façon exponentielle, ce qui est rédhibitoire. Ainsi, c'est la nécessité de pouvoir scinder un algorithme en sous-parties de taille raisonnable (par exemple 8 bits) qui rend possible des attaques exhaustives partielles, qui une fois réunies, compromettent l'intégralité du système. Les attaques sur les canaux cachés fonctionnement effectivement sur la base d'une stratégie dite « diviser pour régner » ou en terminologie anglo-saxonne « divide-and-conquer ».

Enfin, il n'a pas encore été prouvé qu'une attaque à l'intérieur d'un cône de logique ne soit pas réalisable. Dans ce cas de figure, un attaquant peut sonder par les techniques statistiques de la DPA l'activité d'un nœud arbitraire, comme  $n_0$  au cœur même de la mer de portes constituant la sbox (voir la figure 2). Dans ce cas, l'attaque se ramène à un test exhaustif d'hypothèses, mais sur un nombre réduit de bits de clé de tour.

En conclusion, si la constitution d'algorithmes intrinsèquement résistants aux attaques sur les canaux cachés est une problématique porteuse, les solutions les plus naïves ne sont certainement pas pérennes. Ceci laisse à penser que les contremesures « bas niveau » ont un potentiel moins incertain.

Dans le chapitre 3, l'attaque DPA est étudiée dans le cas de DES (sbox  $p=6 \rightarrow q=4$ ). Les vulnérabilités constatés permettent de définir un cahier des charges sécuritaire, qui sera appliqué dans le chapitre 4 pour concevoir et implémenter un style de logique résistant de façon optimale aux fuites d'information via la consommation électrique.

### Chapitre 3: Attaque DPA sur l'algorithme DES

L'objectif de ce chapitre est de montrer quels sont les facteurs qui rendent possibles une attaque de type DPA. Contrairement au chapitre précédent, de nature théorique, ce chapitre se veut expérimental. Les vulnérabilités ne sont pas toutes capturées par un modèle, aussi sophistiqué soit-il. La confrontation de la théorie avec la pratique conduit à des enseignements sur la nature des failles exploitables par un attaquant.

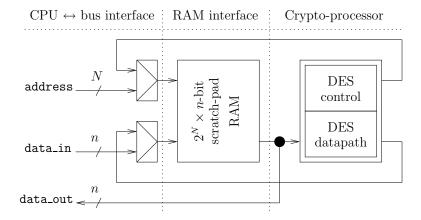

Parmi les circuits qui sont potentiellement les cibles d'attaques physiques, on peut citer les ASIC, les FPGA, les micro-processeurs, ou encore les générateurs d'aléa vrai. Nous concentrons notre étude sur les accélérateurs matériels réalisés sur-mesure (ASIC). Notons que dans tous les cas de figure, il est souvent inutile de sécuriser toute l'application, sans discernement. À l'inverse, il s'agit d'identifier l'élément qui pourra être le germe de la sécurité, qui se propagera grâce à des protocoles idoines à l'ensemble du système. Ainsi, à titre d'exemple, nous envisageons l'étude de cas d'un crypto-processeur DES.

DES est actuellement l'algorithme de chiffrement symétrique le plus étudié par la communauté scientifique et le plus répandu dans les systèmes embarqués (il est notamment utilisé dans les masques B0' des cartes bancaires, etc). L'algorithme utilise huit boîtes de substitution S1–S8 différentes, ce qui permet de tester la force des attaques en fonction des caractéristiques de chacune d'entre elles. Néanmoins, le choix de DES pour l'étude de vulnérabilité aux attaques sur les canaux cachés n'est pas « verrouillant ». Effectivement, les conclusions de ce chapitre peuvent se transposer à tout système cryptographique utilisant des boîtes de substitution. Seul le cas de RC5 est a priori non adressé par nos résultats.

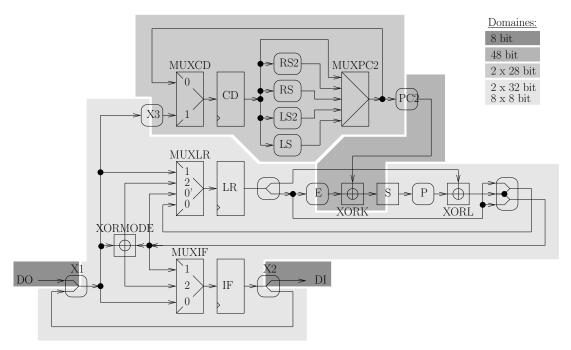

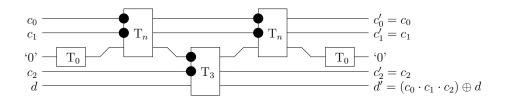

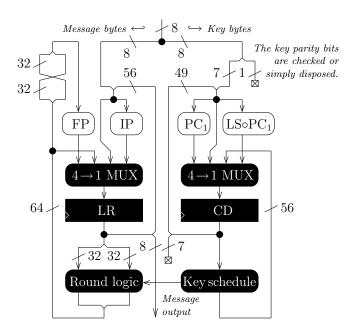

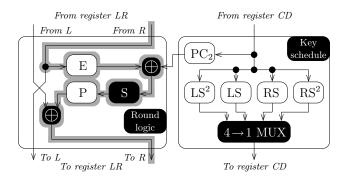

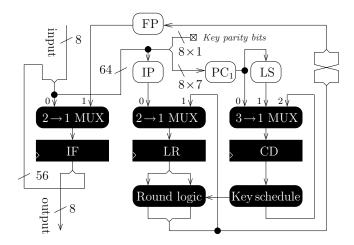

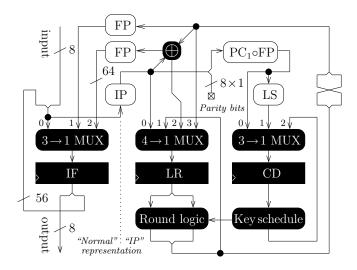

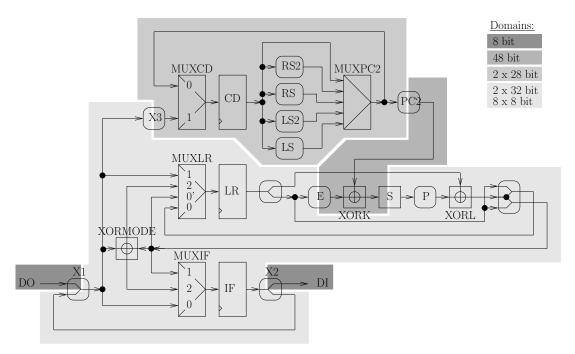

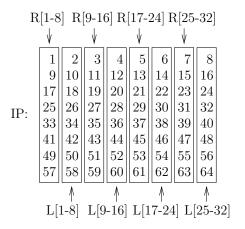

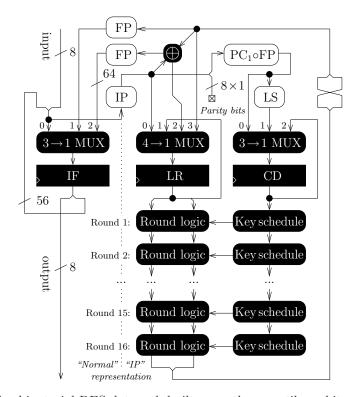

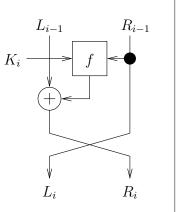

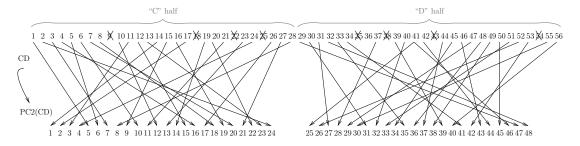

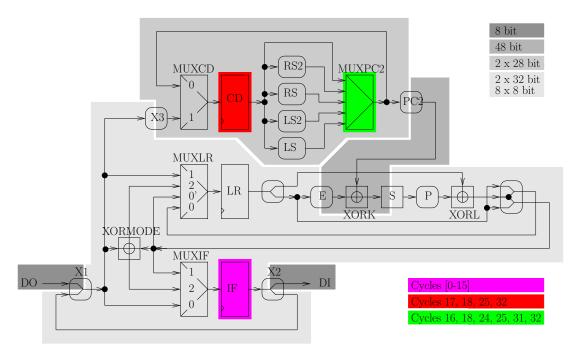

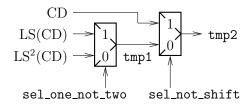

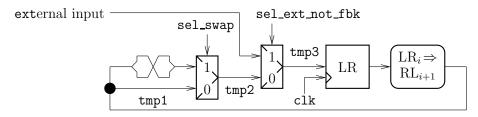

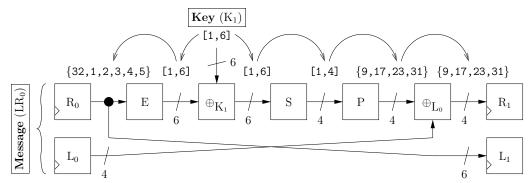

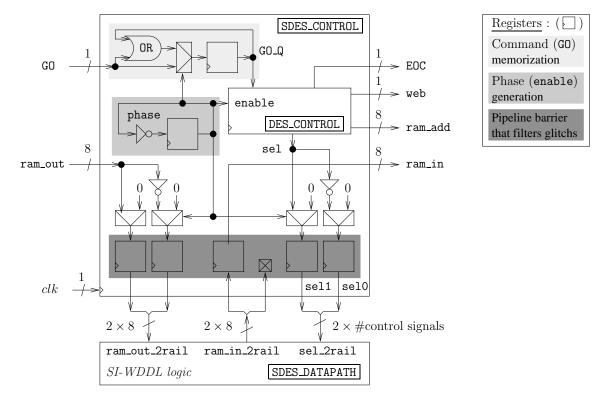

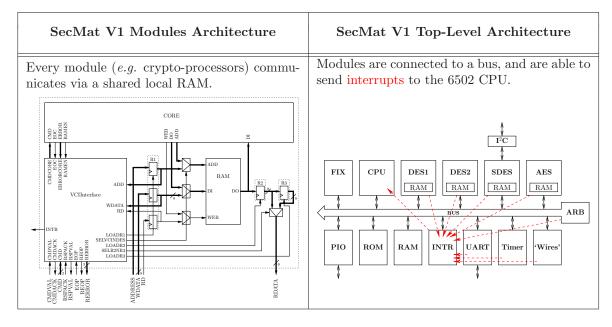

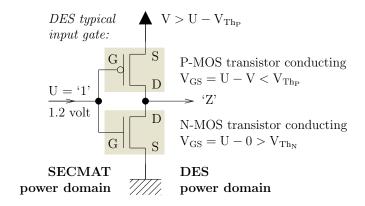

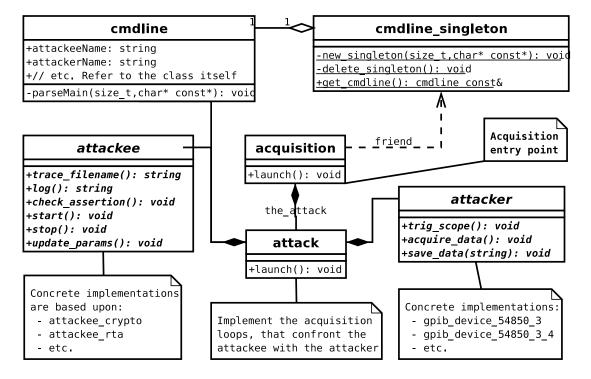

L'architecture du module de chiffrement DES est décrite de façon détaillée dans l'article de revue [101]. Il est nécessaire de bien connaître à la fois les ressources matérielles (niveau RTL) et l'ordonnancement des opérations, car celui-ci conditionne les transferts de registres. Le schéma du co-processeur étudié est résumé dans la figure 3.

Il est notoirement connu que DES a deux problèmes de sécurité [63] (hormis la trop faible longueur des clés) :

- 1. Il existe des clés faibles, pour lesquelles le chiffrement est involutif. Avec de telles clés, il existe 2<sup>32</sup> points fixes.

- 2. De plus, il existe des couples de clés semi-faibles, telles que le chiffrement avec l'une corresponde au déchiffrement avec l'autre. En utilisant des telles clés, il existe  $2^{32}$  anti-points fixes.

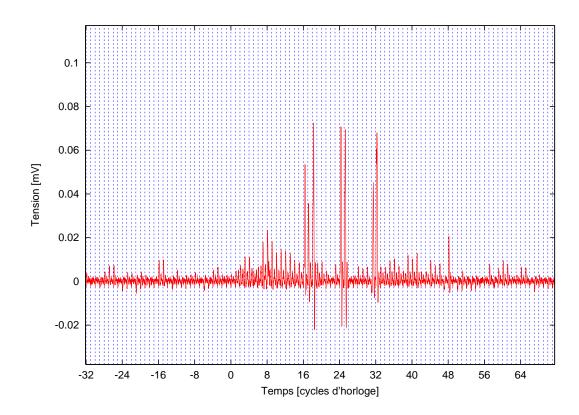

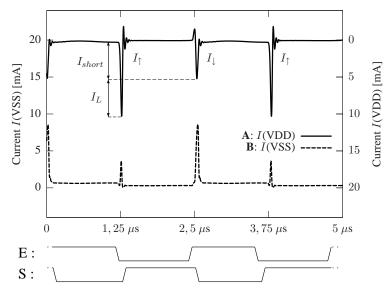

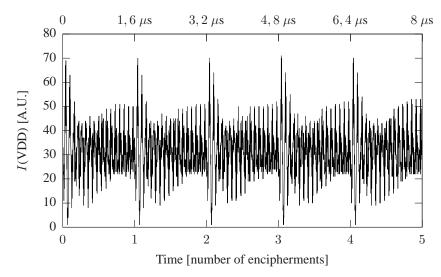

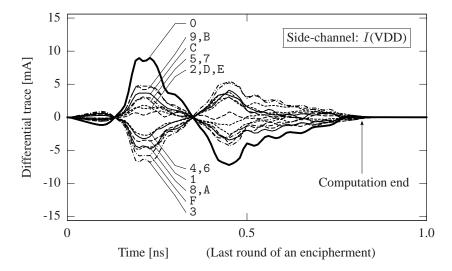

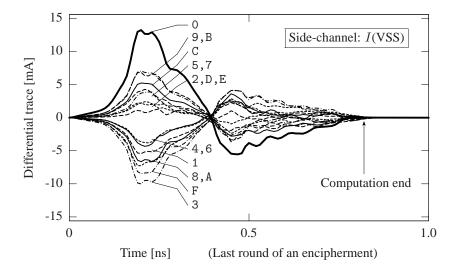

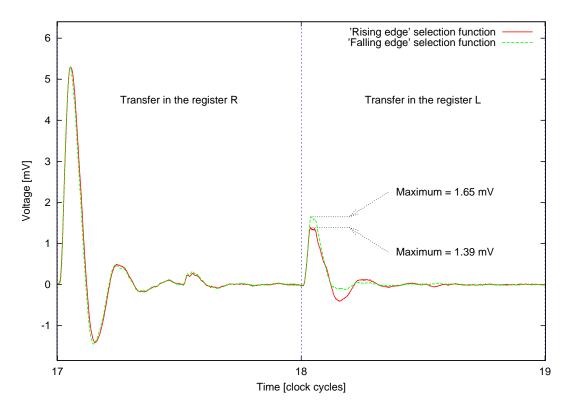

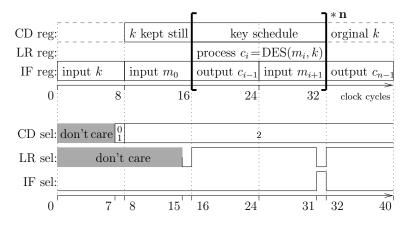

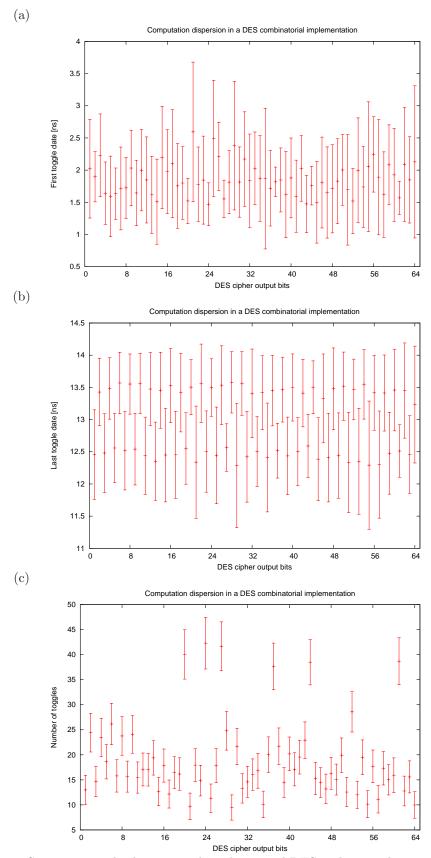

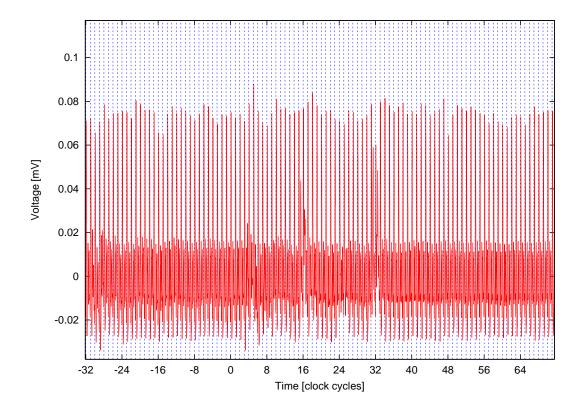

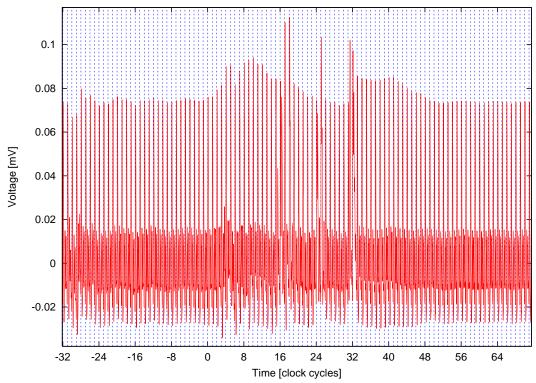

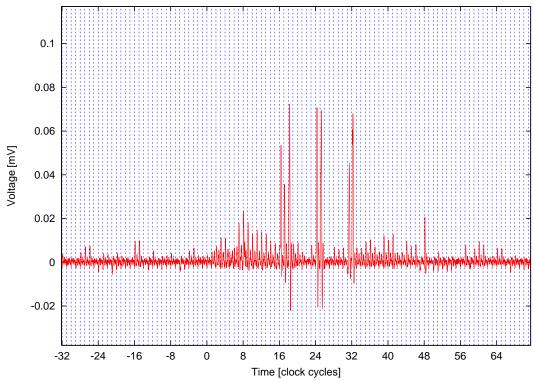

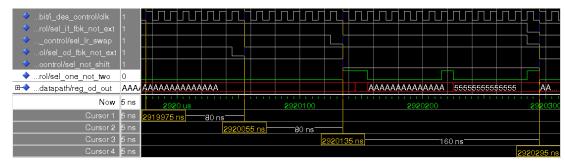

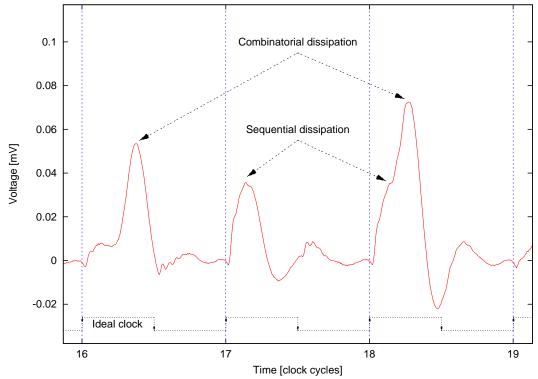

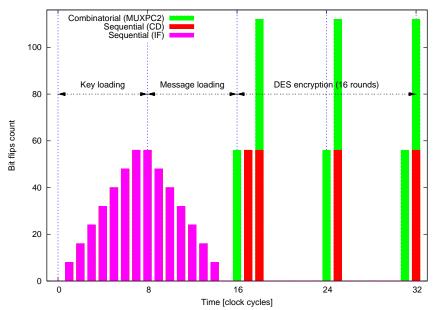

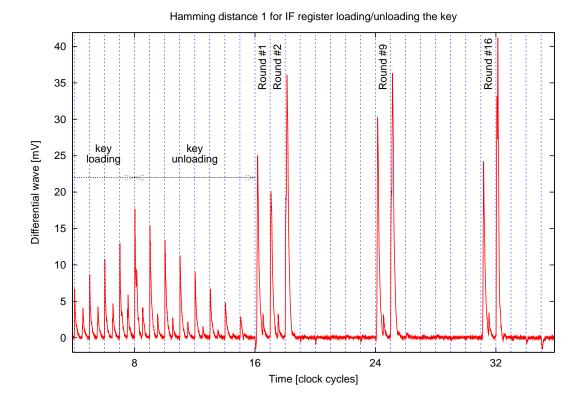

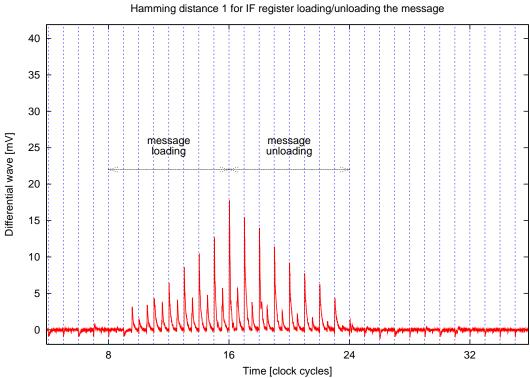

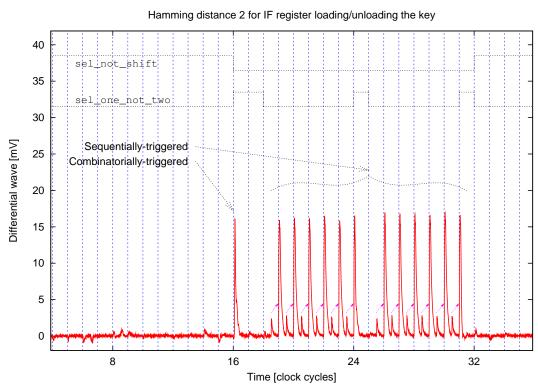

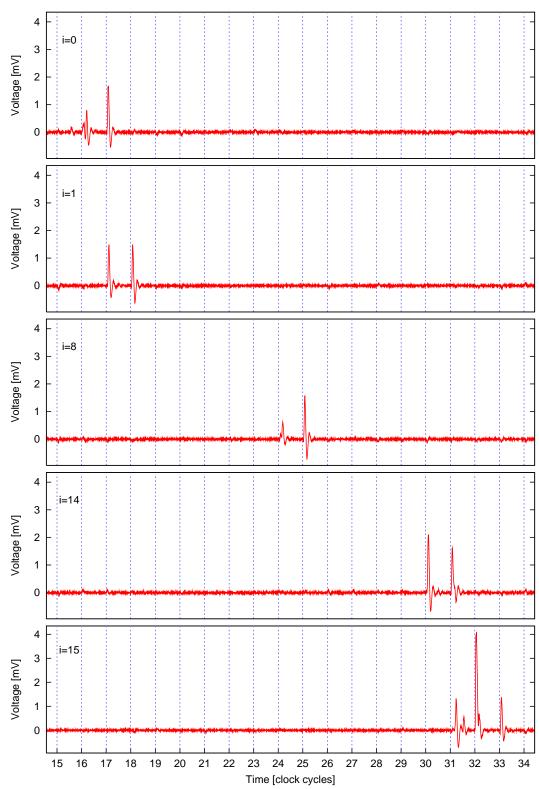

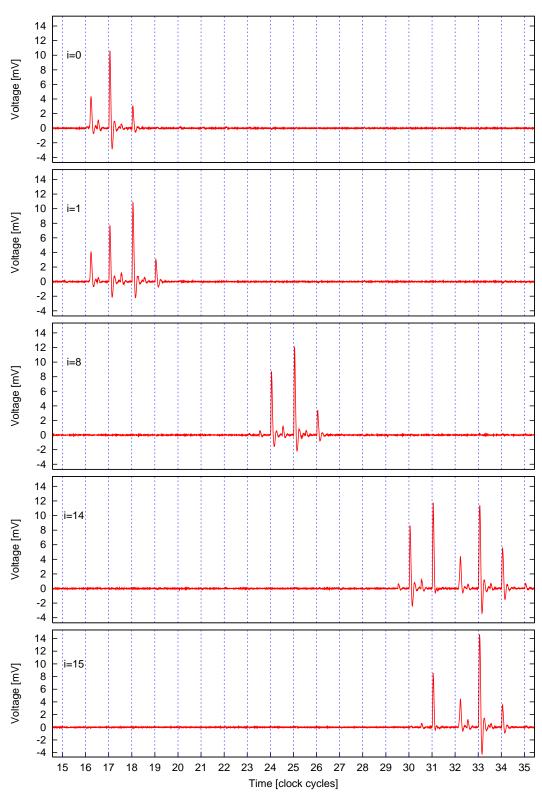

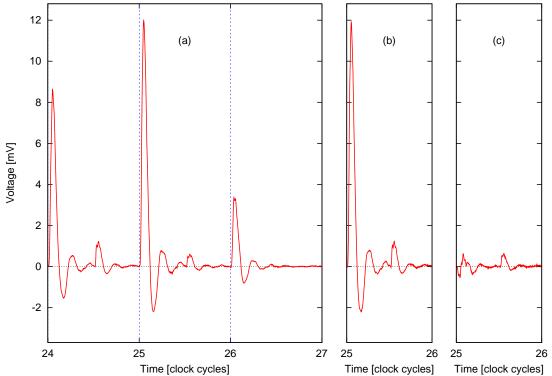

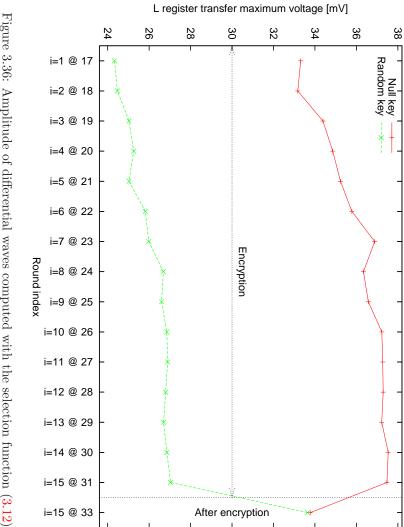

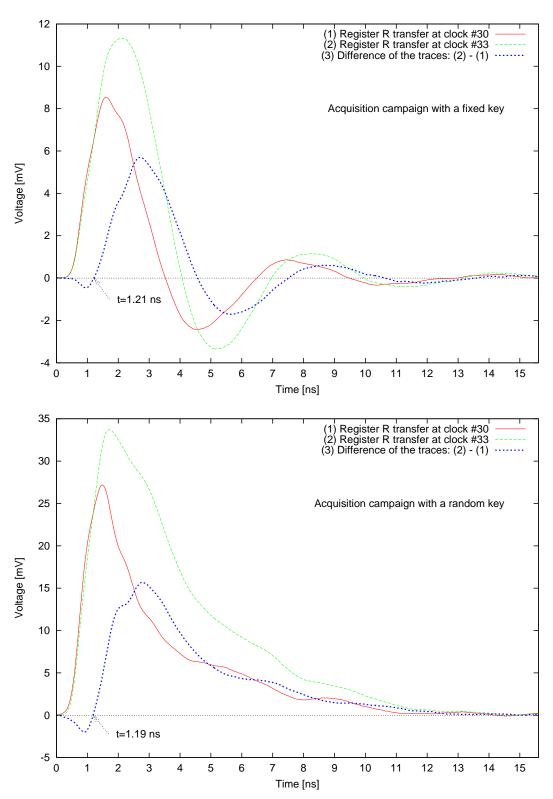

Ces propriétés permettent à un attaquant de localiser dans le temps le début et la fin d'un chiffrement. Par exemple, la figure 4 permet de mettre en évidence :

- le chargement de la clé (cycles notés 0-8),

- le chiffrement lui-même (cycles notés 16-32).

FIG. 3 – Version « SecMat V1 » du chemin de données de l'accélérateur de chiffrement DES, avec indication de la largeur des bus (*en teintes de gris.*)

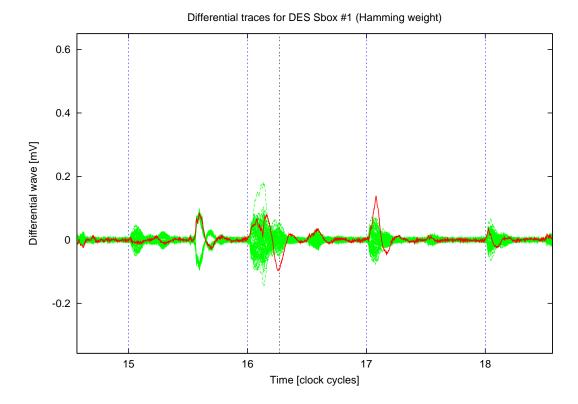

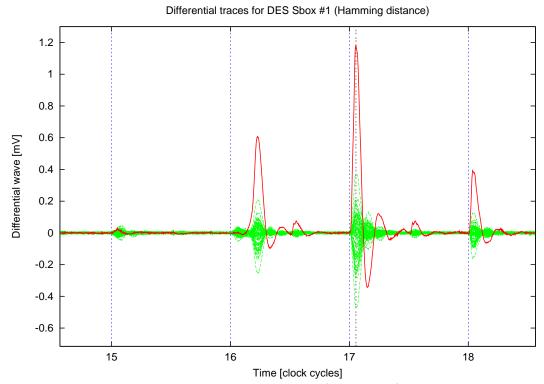

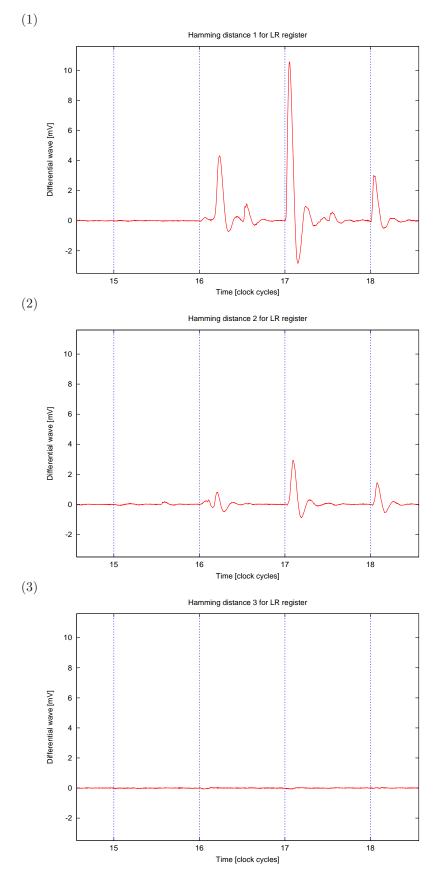

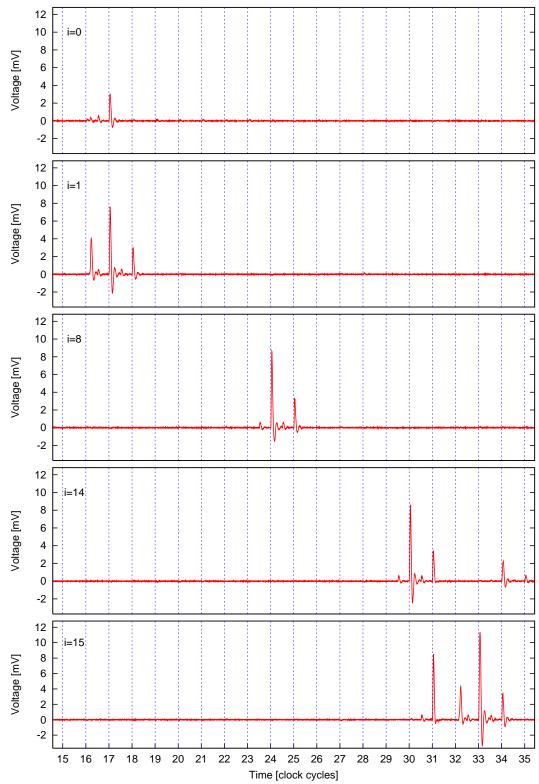

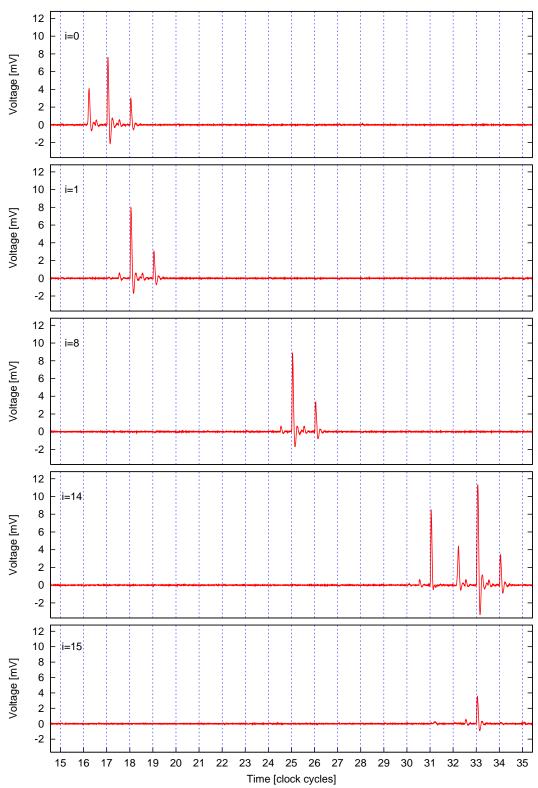

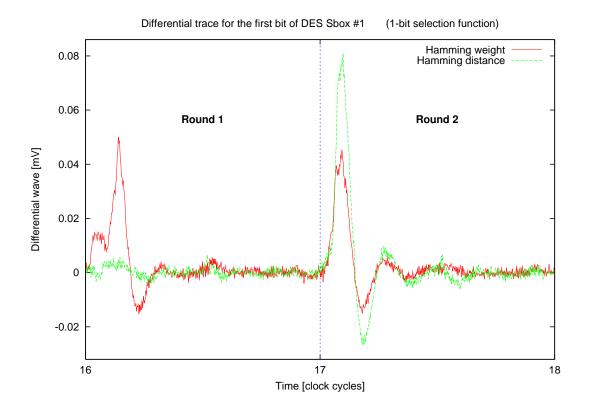

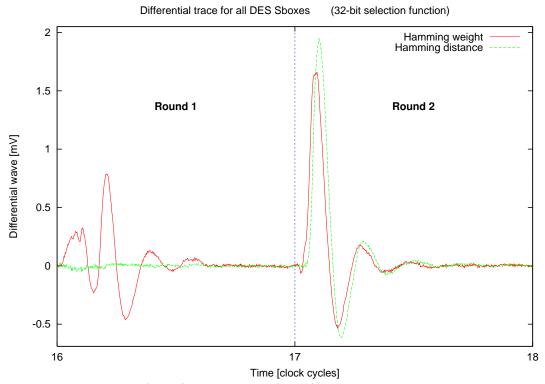

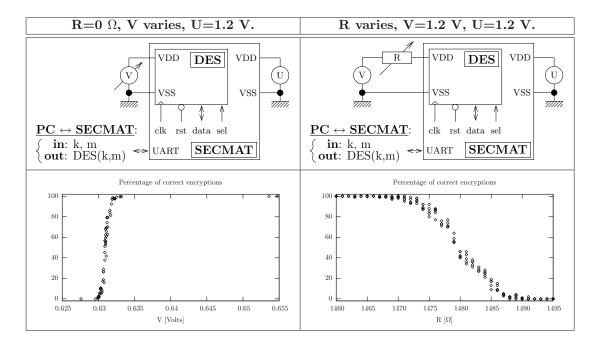

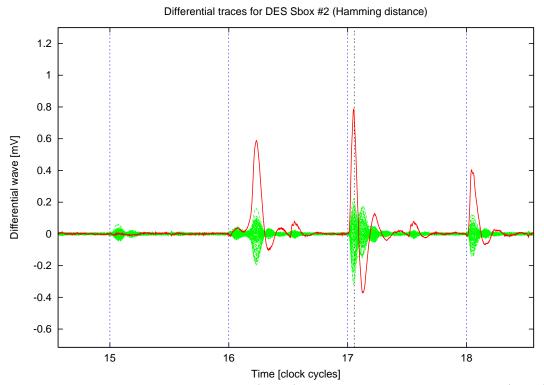

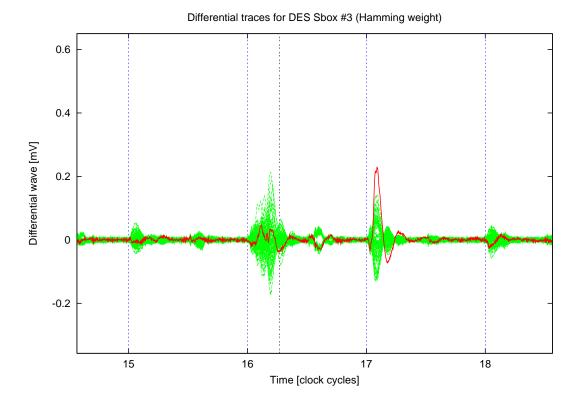

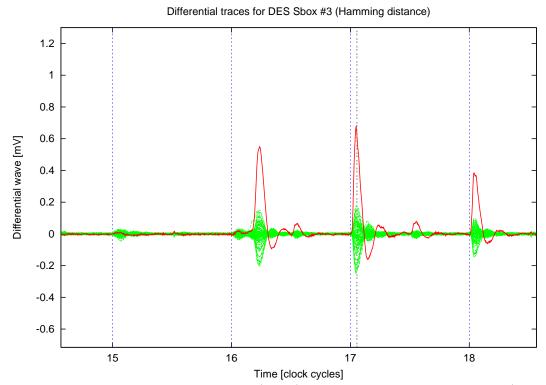

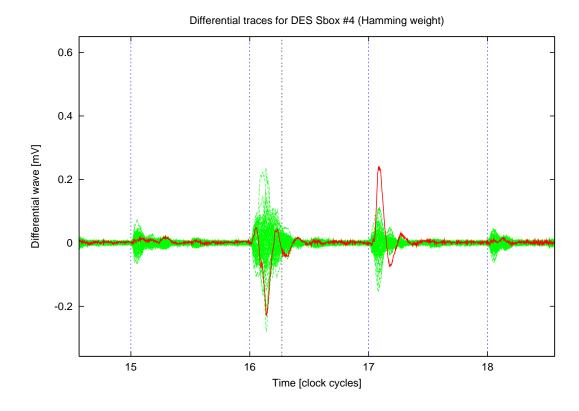

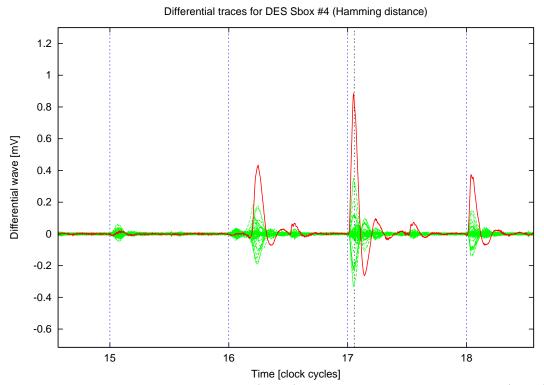

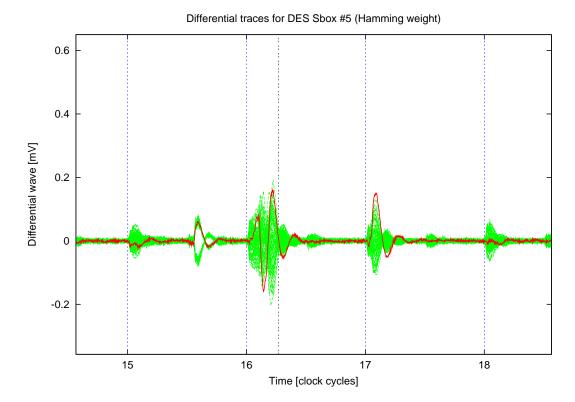

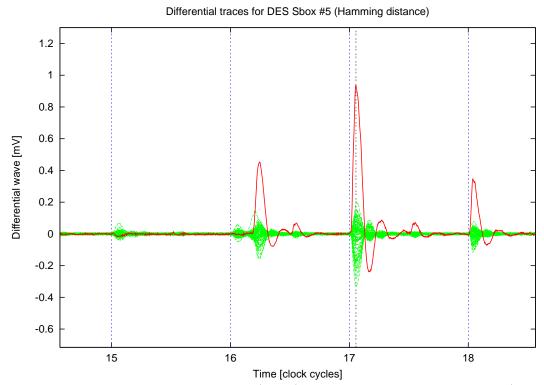

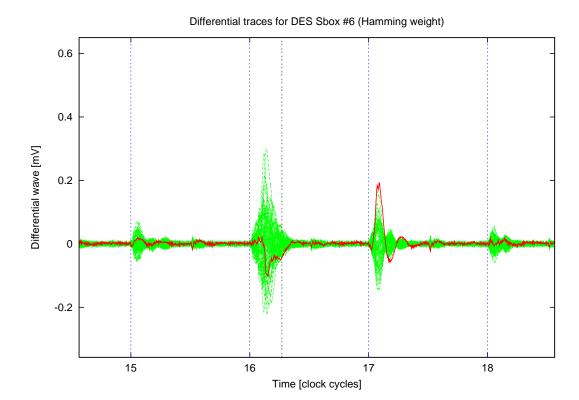

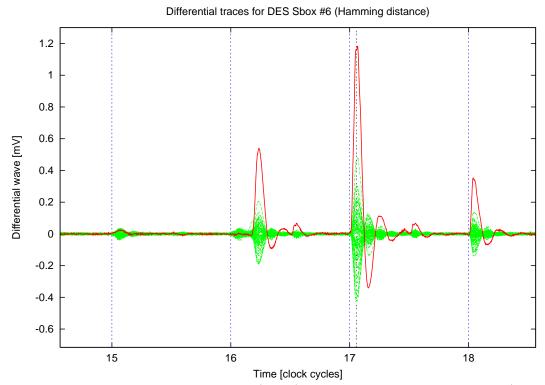

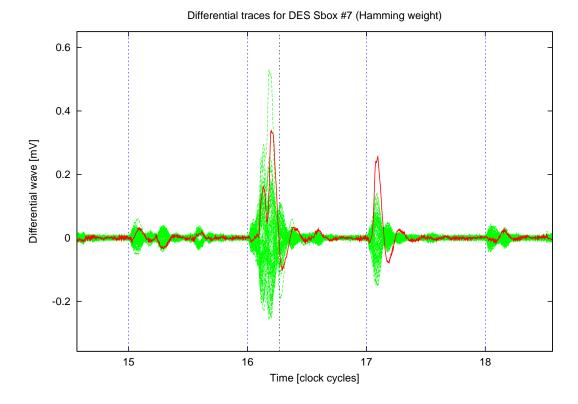

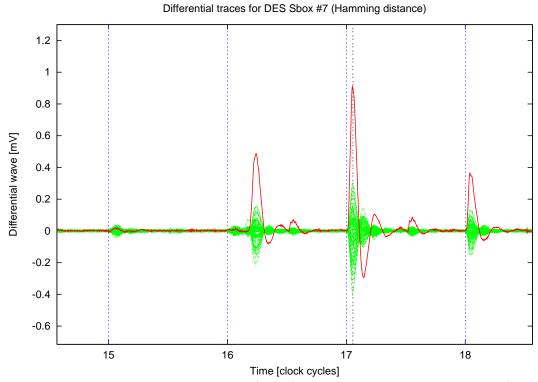

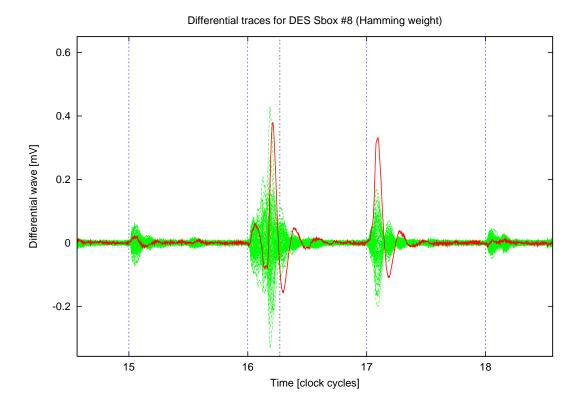

Quand les clés ne peuvent pas être choisies par l'attaquant, l'existence de clés particulières n'est pas un problème. Nous réalisons alors avec des clés « banalisées » les attaques DPA en poids et en distance de Hamming. Les deux attaques réussissent. Néanmoins, il s'agit de noter les observations suivantes :

- 1. L'attaque en poids de Hamming réussit car il existe une signature dépendant de la clé au tour suivant celui que l'on pense initialement attaquer. Nous montrons que c'est l'existence d'un glitch qui cause la signature sans équivoque du poids de Hamming de la sortie des huit sboxes. Cette constatation va inciter la mise en place de contre-mesures où les portes élémentaires re-synchronisent entre elles leurs entrées, afin d'interdire la propagation de transitions non fonctionnelles.

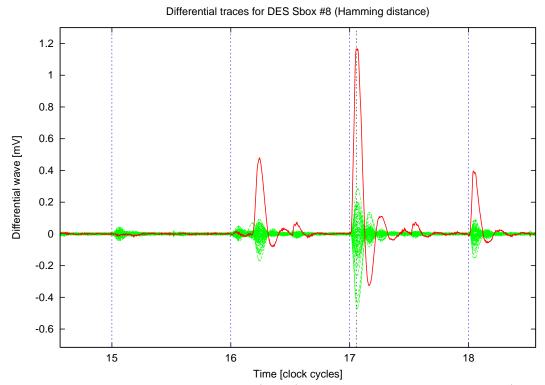

- 2. L'attaque en distance de Hamming entre parfaitement dans le cadre du modèle présenté dans le chapitre 2, et réussit donc sans surprise particulière. Nonobstant, alors qu'un unique pic de corrélation est attendu, on en observe en réalité trois. L'explication de la complexité a priori inattendue de ce phénomène provient de la structure dite de Feistel de l'algorithme DES. À chaque itération, la moitié droite du message sert à la fois à calculer un masque pour la partie gauche, et à être conservée telle quelle pour, afin que le système reste déchiffrable. Le « schéma de Feistel » est représenté dans la figure 3.19 à la page 72. Ainsi, l'existence de cette fourche sur la moitié droite du message provoque, en plus du pic principal, une duplication de la

Fig. 4 – Analyse SPA obtenue par différence de seulement deux courbes de consommation de DES, utilisant une clé faible et une autre semi-faible.

fuite, ayant lieu pour moitié dans le tour précédent et pour moitié dans le tour suivant. Ceci explique complètement que <u>trois</u> pics soient observés.

D'autres types d'analyses, notamment à clé connue, sont réalisées. Elles permettent de tirer les conclusions suivantes quant aux caractéristiques sensibles d'une implémentation matérielle :

- Les attaques en poids de Hamming peuvent réussir (même sans état initial fixé) par la simple propagation d'un glitch. Il s'agit donc de supprimer les glitches et également d'équilibrer les portes logiques dans leurs entrées.

- Certaines corrélations peuvent se manifester alors qu'elles ne sont pas attendues. Il est ainsi nécessaire de bien étudier les transferts de données à l'intérieure d'une zone de confiance et également aux interfaces avec les zones non sécurisées.

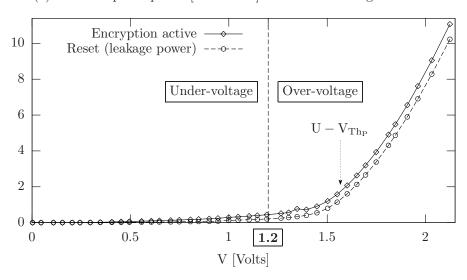

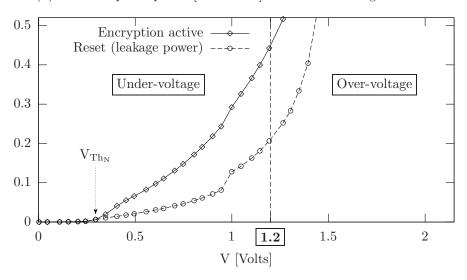

- Il existe des corrélations au-delà de deux périodes d'horloge. Cela va inciter à supprimer les états « haute impédance » (aussi dits « Z ») et à utiliser des protocoles de calcul reposant sur une alternance pré-charge / évaluation.

- La diaphonie peut être mis en évidence. En conséquence, les équipotentielles sensibles doivent être protégées par du blindage avec un nœud global.

- Les attaques continuent à réussir même sur des traces moyennées dans les temps. Les contre-mesures consistant à introduire une gigue temporelle sont donc inopérantes. Il faudra donc concentrer les efforts vers une logique déterministe (par opposition à aléatoire).

# Chapitre 4 : Contre-mesures au niveau de la conception physique

Les vulnérabilités identifiées dans le chapitre précédent sont autant de recommandations sécuritaires pour la définition et la mise en place de contre-mesures pertinentes. Nous spécifions et implémentons dans ce chapitre une réalisation possible de calcul qui pallie à tous les écueils identifiés.

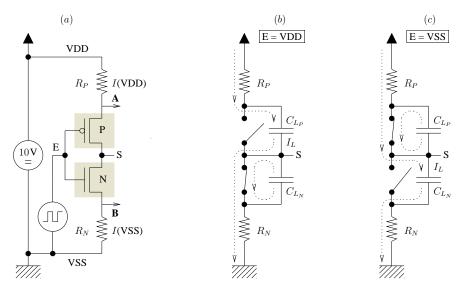

En technologie VLSI, le calcul numérique se décompose en deux étapes :

- 1. Le grain élémentaire de calcul, réalisant des opérations booléennes partielles.

- 2. L'interconnexion des résultats booléens indépendants pour réaliser la fonctionnalité globale.

Ces deux étapes sont étudiées successivement. La première porte sur le dessin des masques d'une famille de portes logiques. Quant à la seconde, elle concerne l'utilisation éclairée des outils de placement-routage. L'objectif de la deuxième étape est d'éviter de ruiner les efforts réalisés localement lors de leur assemblage final sur silicium.

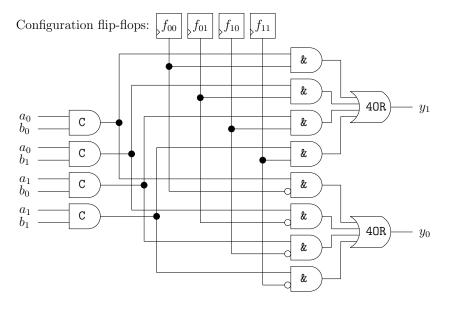

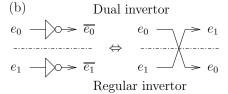

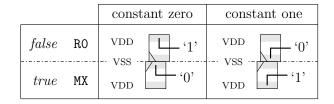

La partie logique s'appuie sur une représentation redondante des données, dite « dual-rail ». Chaque nœud logique A est représenté par une paire de fils  $(a_0, a_1)$ , dont l'évolution dans le temps est décrite comme ci-après :

|              |       |                   |        |                   |       |                   | VALID(0,1) |                   |  |

|--------------|-------|-------------------|--------|-------------------|-------|-------------------|------------|-------------------|--|

| $(a_0, a_1)$ | (0,0) | $\longrightarrow$ | (0, 1) | $\longrightarrow$ | (0,0) | $\longrightarrow$ | (1,0)      | $\longrightarrow$ |  |

Dans ces chronogrammes, la valeur de pré-charge a été fixée arbitrairement à (0,0). Les deux valeurs valides sont  $A=0 \Leftrightarrow (a_0,a_1)=(1,0)$  et  $A=1 \Leftrightarrow (a_0,a_1)=(0,1)$ . Cependant, d'autres représentations peuvent être utilisées avantageusement. Par exemple, la logique dite « à espaceurs entrelacés » [96] utilise de façon interchangeable (0,0) ou (1,1).

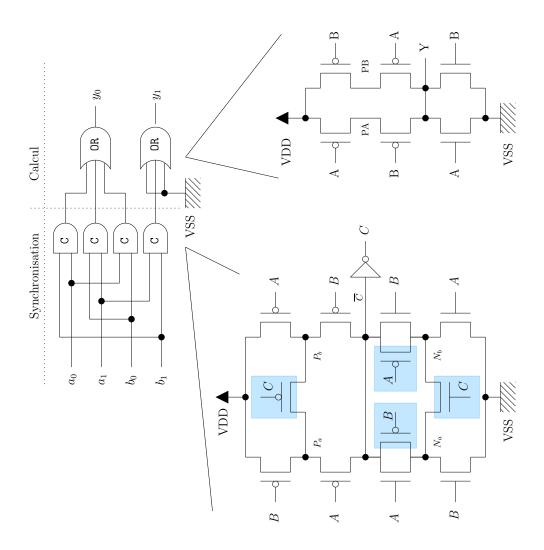

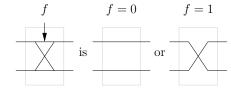

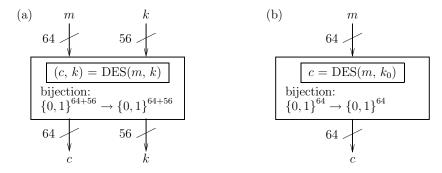

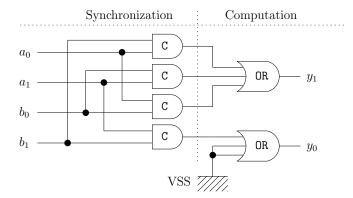

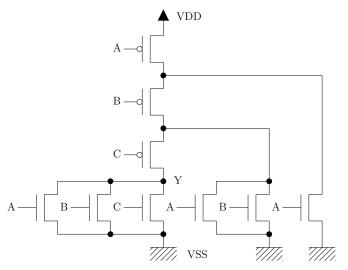

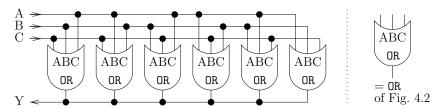

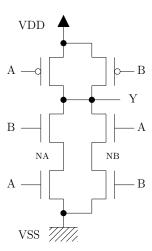

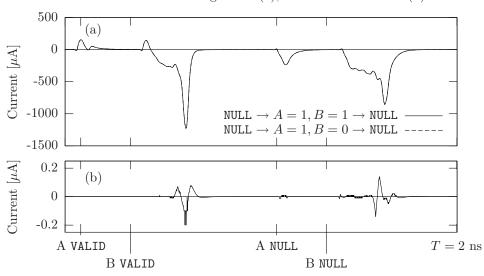

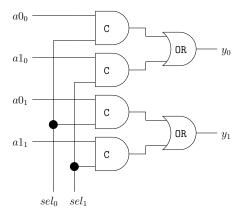

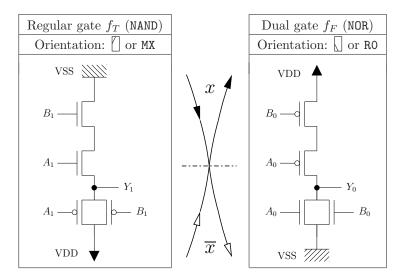

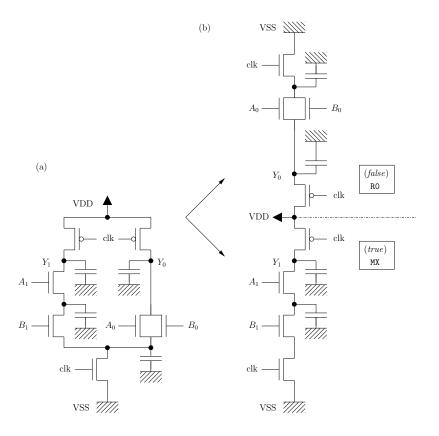

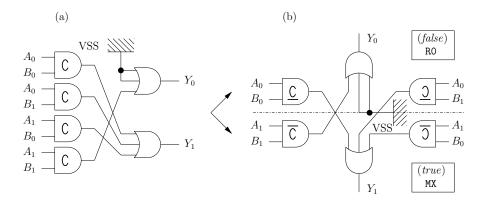

Les portes utilisées, respectant le protocole dual-rail avec retour à l'état NULL, défini par NULL  $\doteq (0,0)$ , doivent de plus être équilibrées vis-à-vis des chemins d'exécution. Nous proposons la structure illustrée dans la figure 5 pour le cas particulier de la porte universelle NON-ET. La porte réalise successivement les étapes suivantes :

- 1. Synchronisation des entrées, par couples, grâce à des portes de « rendezvous », aussi connues sous le nom de portes de Muller ou C-éléments [93].

- 2. Calcul à proprement parler : aiguillage vers la sortie *vraie* ou *fausse* en fonction du min-terme qui a été décodé.

Afin d'accroître le niveau de robustesse de cette porte, trois niveaux de sécurité supplémentaires sont mis en œuvre :

1. Les portes de rendez-vous sont toutes identiques, et sans état haute-impédance suspicieux. Il est à noter que seules les équipotentielles internes  $N_a$  et  $N_b$  doivent être protégées, car  $P_a$  et  $P_b$  ne fuient pas d'information (*confer* figure 5).

Fig. 5 – Schéma en transistor de la porte  ${\tt NON-ET}$  sécurisée [42] de la bibliothèque SecLib.

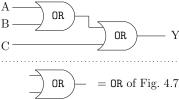

Fig. 6 – Dessin des masques de la porte de rendez-vous symétrisée et équilibrée, sans aucun état haute-impédance.

- 2. Les portes de concentration du calcul sont de type OR. Leur structure est rendue redondante, pour éviter de particulariser l'une des deux entrées.

- 3. Au niveau global, alors que, *stricto sensu*, seules quatre portes OR sont nécessaires pour véhiculer les quatres valeur de la table de vérité vers les deux sorties, six (trois et trois) sont utilisées en pratique. De cette façon, les deux sorties sont chargées par le même nombre de portes, et le temps de calcul devient constant.

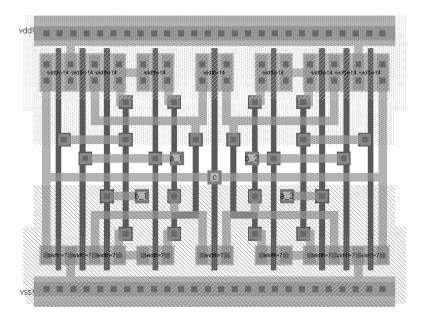

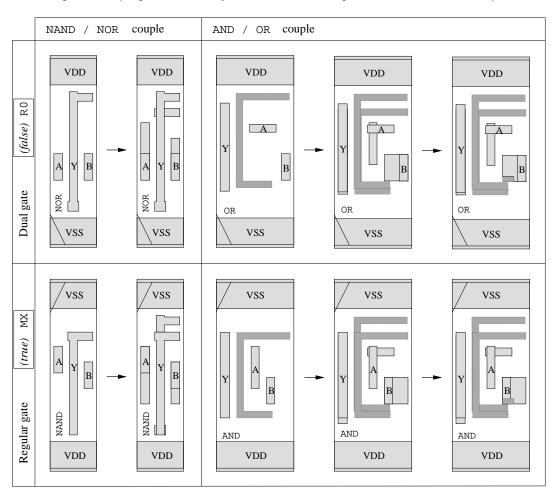

Un enjeu important est de conserver la symétrie en passant du *schéma* au *dessin des masques*. Cette étape est réalisable, moyennant certaines concessions bien identifiées. La structure, dite « symétrique », de la porte de rendez-vous, se prête particulièrement bien à une projection technologique avec respect des invariants topologiques, comme illustré dans la figure. 6.

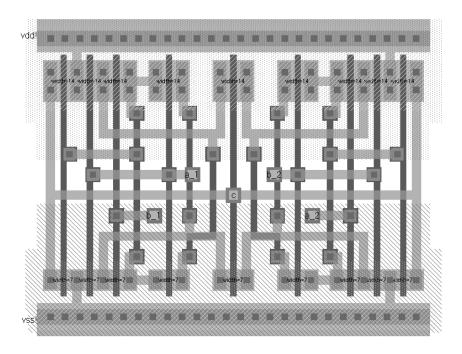

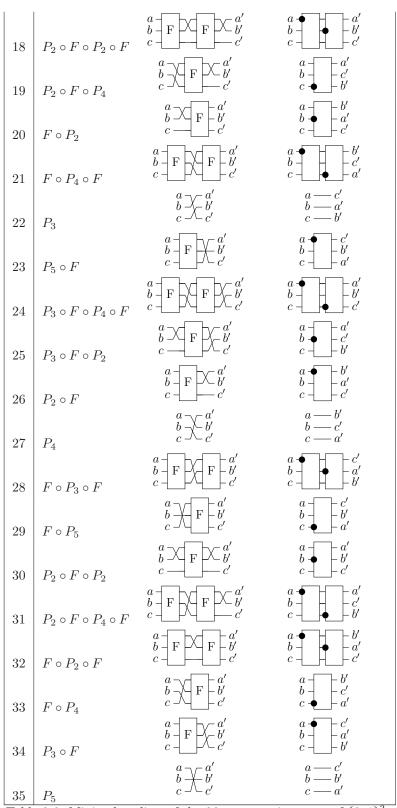

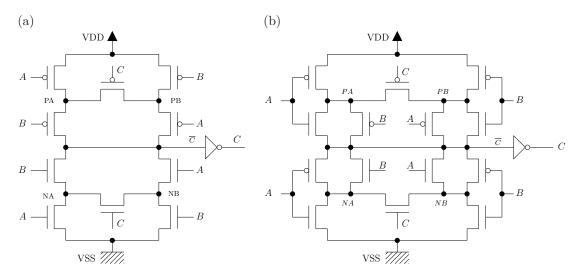

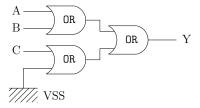

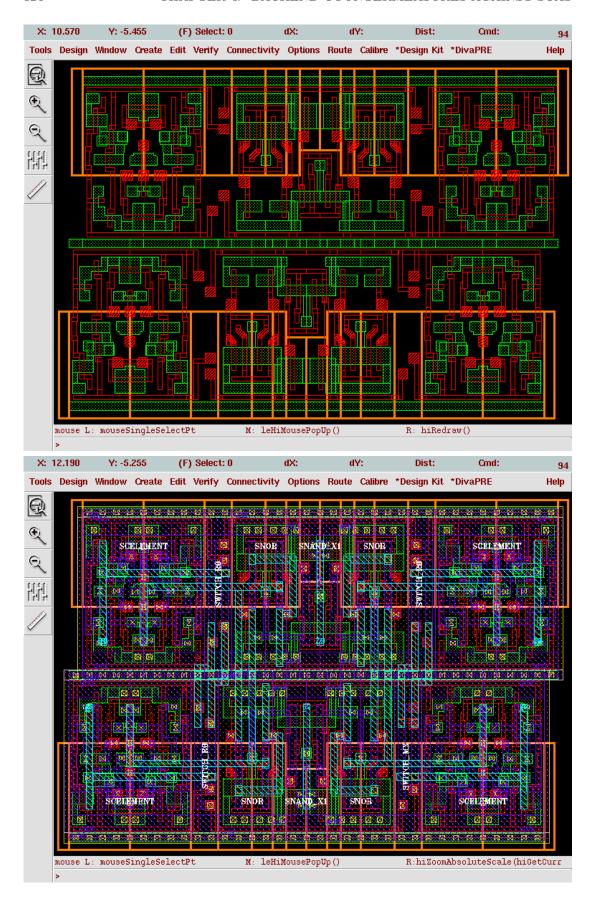

Le résultat final sur la fonction NON-ET est une porte duale, dessinée dans la figure 7.

Le niveau d'indiscernabilité atteint par cette porte est validé par simulation électrique exhaustive de tous les cas de figure (arrivées concomitantes ou différées, dans n'importe quel ordre autorisé par le protocole). La simulation confirme bien que la signature en consommation de la porte est indépendante des données manipulées.

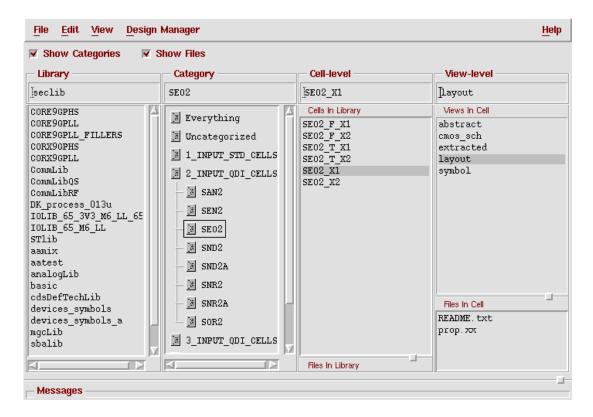

Le dessin des masques de toutes les portes sécurisées à deux entrées est identique, *modulo* la position de certains vias. Ceci permet de concevoir rapidement

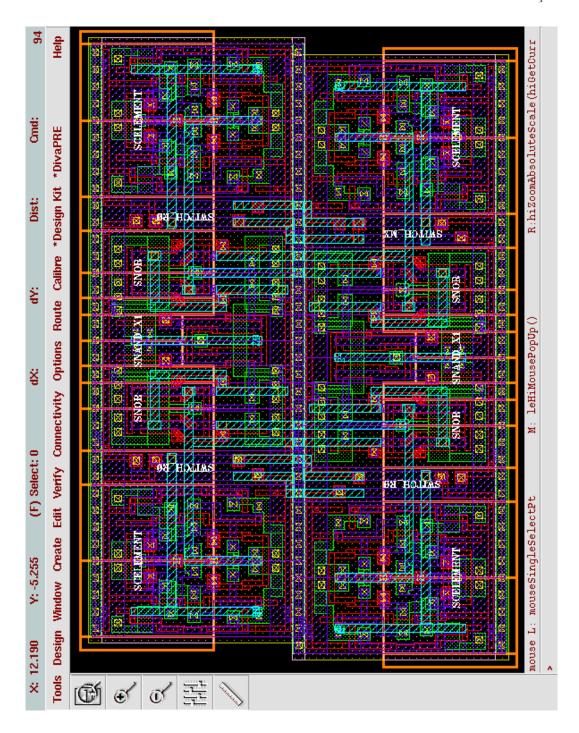

Fig. 7 – Exemple du dessin des masques de la porte  ${\tt NON-ET}$  de la bibliothèque SecLib, vue depuis l'éditeur Virtuoso de Cadence  $^\circledR$  .

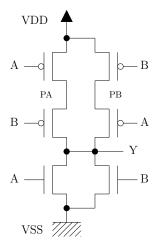

Fig. 8 – Plan de masse en dual-rail pour la porte NON-ET sécurisée [42].

une bibliothèque, surnommée « SecLib », comportant les 10 portes logiques à deux entrées non dégénérées (parmi les  $2^{(2^n)}$  possibles, avec n=2).

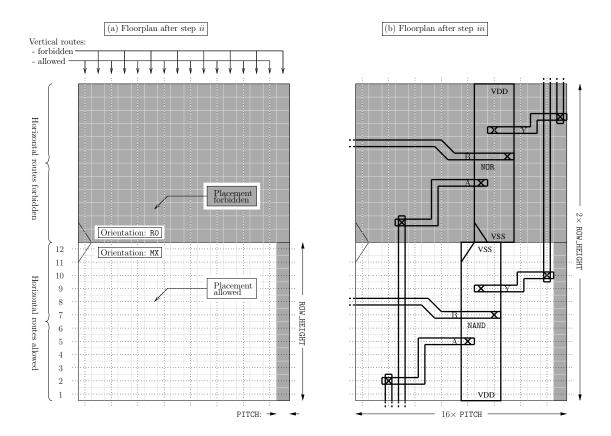

Les deux principales étapes de la conception physique, à savoir le placement et le routage, se doivent de préserver les invariants de sécurité mis en place dans les portes logiques de SecLib. Grâce à un placement différentiel (chaque instance voit son homologue dual dans une symétrie axiale) et à un routage également différentiel (chaque fil est le translaté de son dual), les contraintes géométriques de sécurité sont étendues du niveau porte au niveau netlist (composition de portes).

La figure 8 illustre l'opération sur une *netlist* simplifiée, réalisant comme seul calcul la fonction NON-ET.

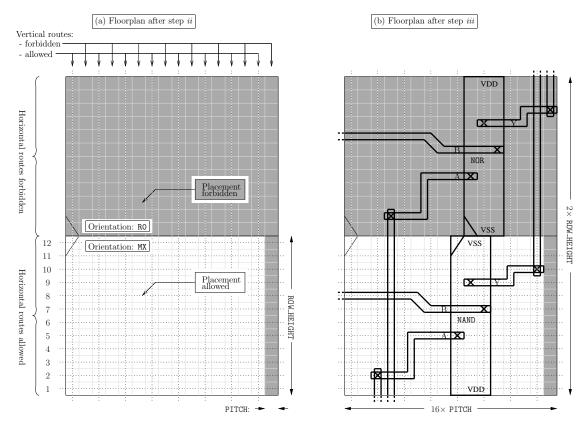

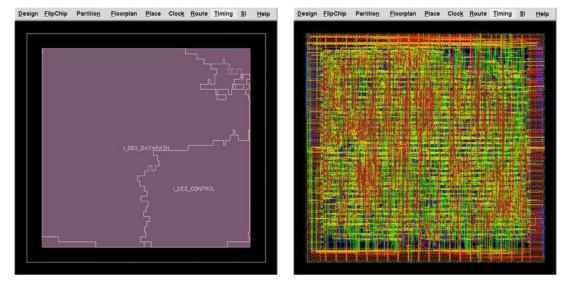

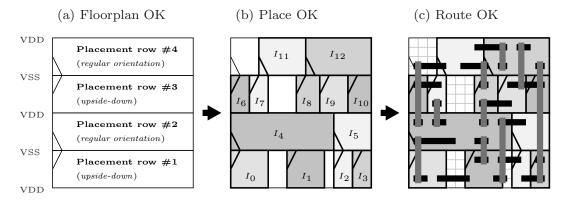

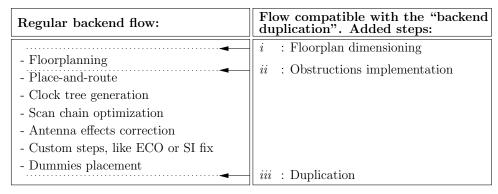

L'opération illustrée dans la figure 8 est en pratique réalisée par l'adjonction de trois étapes à un flot de conception usuel. Ces étapes sont :

- 1. Le dimensionnement préalable du plan de masse à des distance paires en terme d'espacement de routage (ou « pitch ») et de sites de placement.

- 2. Avant le placement et le routage, l'instanciation d'obstructions de placement sur une rangée de placement sur deux, et la mise en place de contraintes de routage :

- les canaux horizontaux sont interdits au-dessus des zones de placement interdites et

- seul un canal vertical sur deux est accessible.

- 3. À la fin du flot de placement-routage contraint, l'ensemble des éléments (placement, routage, signaux globaux, métal non-fonctionnel de remplissage ou dummies, etc.) sont dupliqués par un script ad hoc, traitant par exemple la description DEF [56] du circuit.

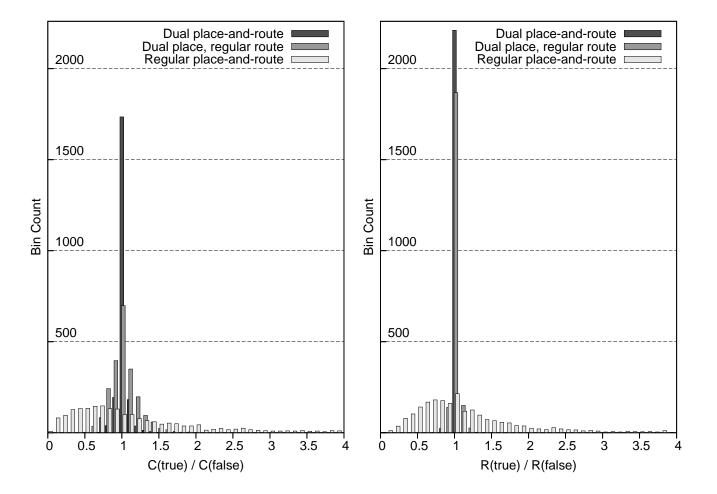

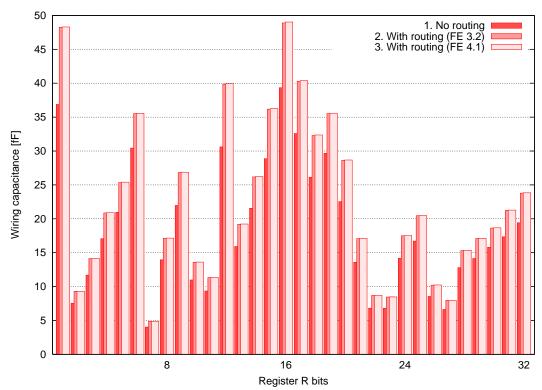

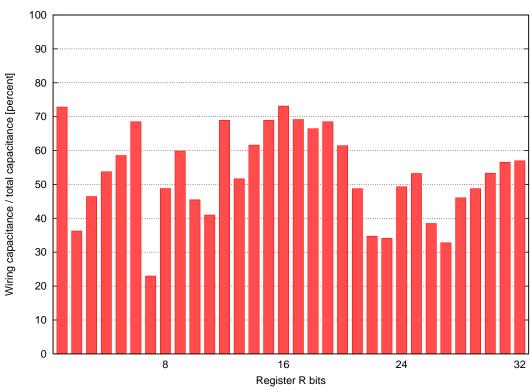

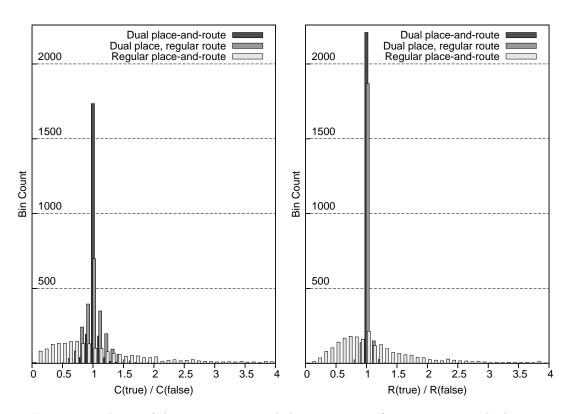

La méthode proposée dans ce chapitre a été mise en œuvre sur le chemin de donnée de l'opérateur DES décrit dans le chapitre 3. Les résultats sont résumés dans la figure 9.

Le premier histogramme (à gauche de la figure 9) représente la répartition des rapports C(true) / C(false) des équipotentielles de chaque paire différentielle. La répartition est toujours centrée autour de 1. Mais la dispersion diminue notamment lorsque le placement-routage est contraint :

- Sans contrainte, la dispersion peut monter jusqu'à des rapports 1:4.

- En contraignant simplement le placement (les instances duales sont côte à côte), les écarts sont fortement réduits. Cette stratégie est porteuse en technologie FPGA, où il est difficile (voire impossible avec certains IDE) de contraindre le routage.

- Avec la méthode de duplication du plan de masse [102], l'équilibrage gagne encore un ordre de grandeur.

Le test C(true) / C(false) est particulièrement significatif, car nous avons évalué que dans la technologie utilisée et avec le crypto-système DES, la contribution majoritaire des capacités d'interconnexion provient du routage, et non plus des capacités d'entrée des portes.

Le second histogramme (à droite de la figure 9) présente la dispersion des résistances des fils. Dans le cas de la duplication du plan de masse [102], la répartition est un pic de Dirac parfait, car par construction, les fils de chaque paire ont exactement la même longueur. Et comme il n'existe pas de couplage entre résistances (à l'inverse des capacités, pour lesquelles la diaphonie est un phénomène non négligeable), la distribution n'a pas de variance.

### Chapitre 5 : Conclusions

Depuis notre entrée de plein pied dans la « société de l'information », la grande majorité des échanges de données est devenue numérique. En conséquence, les appareils électroniques qui manipulent de l'information sont devenus omniprésents. Ils ont envahi aussi bien la sphère professionnelle que privée. Dans ce contexte, dit de « calcul pervasif », les problèmes de sécurité s'avèrent être cruciaux. Jusqu'à très récemment, les attaques usuelles ciblaient les bugs logiciels ou les faiblesses des protocoles des réseaux. Maintenant que les terminaux (mobiles, assistants personnels, ordinateurs de bureau, etc.) se rapprochent de l'utilisateur final, l'implémentation elle-même est devenue la cible d'attaques. Ceci s'oppose à la conception traditionnelle de la sécurité, où les organes sensibles (serveurs, routeurs, etc.) pouvaient être considérés comme des forteresses. De plus, la sécurité devient de moins en moins cloisonnée au domaine militaire car de plus en plus une affaire civile.

L'objectif de cette dissertation est double :

- 1. tout d'abord, nous analysons la force des attaques sur les implémentations physiques de systèmes de chiffrement symétrique, puis

- 2. nous proposons, en réponse, des contre-mesures raisonnées.

Cette mission est délicate, car il s'avère que les algorithmes utilisés en cryptographie, par exemple le chiffre symétrique, représente justement la classe d'algorithmes la plus facilement attaquable sur les canaux cachés. Par ailleurs, nous montrons que la sécurisation des implémentations est une tâche délicate, car même des attaques a priori non significatives, comme celle en « poids de Hamming », se trouve réussir, à cause d'effets de bords dévastateurs, car non anticipés. Il s'agit en l'occurrence de transitions « non-fonctionnelles », dites glitches. Nous détaillons l'origine de cette vulnérabilité, due à la fois à une dissymétrie de la porte OU-EXCLUSIF dans ses deux entrées et à une course temporelle de signaux. Il est intéressant de remarquer que cette même faille a permis de casser en 2006 une contre-mesure populaire aux attaques sur les canaux cachés, à savoir la logique WDDL [100].

Ayant pris conscience de la force des attaques sur les circuits, il s'agit de proposer des contre-mesures à la hauteur de l'enjeu sécuritaire. Étant donné que dans l'état de l'art des technologie industrielles permettant le calcul intensif (la filière CMOS n'a à jour pas de rival), il est impossible d'éliminer la consommation d'énergie, il va falloir composer avec les canaux cachés. Notre objectif est donc de faire en sorte que le canal caché (par exemple la consommation instantanée) mesurée par un attaquant ne fuit aucune information sur les données internes manipulées par le circuit. Nous étude consiste à symétriser les structures élémentaires de calcul, de telle sorte que tout calcul produise les mêmes symptômes physiques, du moins dans les limites imposées par les imperfections technologiques. Les portes logiques elles-mêmes sont donc garantes de la confidentialité des données qu'elles traitent. Grâce à une micro-architecture équilibrée

du point de vue géométrique, cette contrainte peut être implémentée, moyennant certains compromis d'ordre topologique. Effectivement, certaines symétries ne peuvent pas être respectées sans créer de court-circuits : c'est par exemple le cas de la symétrie axiale quand il s'agit de relier deux couples de points symétriques (A,B) & (B',A') de façon croisée, i.e. A=A' & B=B' électriquement parlant. Une étude sur la porte réalisant la fonction NON-ET se généralise à l'ensemble des primitives logiques utiles pour la réalisation de fonctions booléennes vectorielles arbitraires. Une bibliothèque complète de portes, appelée SecLib, est ainsi spécifiée et dessinée en technologie CMOS 130 nanomètres. Un effort particulier porte sur l'utilisabilité pratique de SecLib avec les outils d'assistance à la conception disponibles commercialement. De plus, la compatibilité de SecLib avec les bibliothèques dites « standards », fournies par les fondeurs de silicium, est une contrainte supplémentaire. Elle permet de mélanger les deux types de portes, sécurisés et normaux, dans un souci d'économie d'efforts de conception et de réutilisation d'éléments déjà validés par ailleurs. Un accélérateur cryptographique dédié au chiffrement multi-mode DES et triple-DES est conçu avec SecLib d'une part et une technique de placement-routage originale, appelée "duplication du dessin des masques" ("backend duplication" [102]) d'autre part. Cette réalisation démontre qu'une méthodologie de conception sécurisée est effectivement transférable vers le tissu industriel du semi-conducteur.

# Contents

| R  | Résumé de la thèse en français iii |                                                               |  |  |  | iii |     |

|----|------------------------------------|---------------------------------------------------------------|--|--|--|-----|-----|

| A  | Acknowledgments xxix               |                                                               |  |  |  |     |     |

| In | itrod                              | uction                                                        |  |  |  | X   | xxi |

| 1  | Phy                                | vsical cryptography                                           |  |  |  |     | 1   |

|    | 1.1                                | Overview of the cryptography                                  |  |  |  |     | 1   |

|    |                                    | 1.1.1 Security needs                                          |  |  |  |     | 1   |

|    |                                    | 1.1.2 Security objects                                        |  |  |  |     | 1   |

|    | 1.2                                | The gray box model                                            |  |  |  |     | 2   |

|    |                                    | 1.2.1 Framework for the attacks considered in this PhD thesis |  |  |  |     | 3   |

|    |                                    | 1.2.2 Side-channel analyzes provided with in this PhD thesis  |  |  |  |     | 3   |

|    | 1.3                                | Attack of flawed implementations                              |  |  |  |     | 4   |

|    | 1.4                                | Common misconceptions                                         |  |  |  |     | 4   |

|    | 1.5                                | Audience                                                      |  |  |  |     | 5   |

|    | 1.6                                | Personal contributions                                        |  |  |  |     | 5   |

| 2  | SC                                 | A immanence                                                   |  |  |  |     | 7   |

|    | 2.1                                | Structural attacks                                            |  |  |  |     | 7   |

|    | 2.2                                | Logical dissipation                                           |  |  |  |     | 7   |

|    |                                    | 2.2.1 Reversible logic                                        |  |  |  |     | 8   |

|    |                                    | 2.2.2 Conservative logic                                      |  |  |  |     | 12  |

|    |                                    | 2.2.3 Application to DES                                      |  |  |  |     | 20  |

|    |                                    | 2.2.4 Conclusion about reversible and conservative logics     |  |  |  |     | 22  |

|    | 2.3                                | Power attack model                                            |  |  |  |     | 22  |

|    |                                    | 2.3.1 Introduction to power attacks                           |  |  |  |     | 22  |

|    |                                    | 2.3.2 Differential power analysis                             |  |  |  |     | 23  |

|    |                                    | 2.3.3 DPA model                                               |  |  |  |     | 26  |

|    |                                    | 2.3.4 Electrical simulation of the DPA                        |  |  |  |     | 29  |

|    |                                    | 2.3.5 Connections between DPA and conventional cryptanalysis  |  |  |  |     | 32  |

|    |                                    | 2.3.6 Conclusion of the power attack model                    |  |  |  |     | 37  |

|    |                                    | 2.3.7 Illustration of DPA signal-to-noise ratio on histograms |  |  |  |     | 38  |

|    | 2.4                                | Practical computing as security weaknesses                    |  |  |  |     | 39  |

|    |                                    | 2.4.1 Integrability constraints                               |  |  |  |     | 39  |

|    |                                    | 2.4.2 Hamming weight <i>versus</i> Hamming distance           |  |  |  |     | 41  |

xxvi CONTENTS

| 3 | $\mathbf{DP}$ | A on DES 49                                                                        |

|---|---------------|------------------------------------------------------------------------------------|

|   | 3.1           | Secured crypto-processors design                                                   |

|   |               | 3.1.1 Security target                                                              |

|   |               | 3.1.2 Motivation for DES                                                           |

|   | 3.2           | A DES architecture operating in IP representation                                  |

|   |               | 3.2.1 Introduction on DES                                                          |

|   |               | 3.2.2 DES datapath improvement thanks to a generalized pipelining 52               |

|   |               | 3.2.3 Optimal software / hardware partition to realize all DES variants 58         |

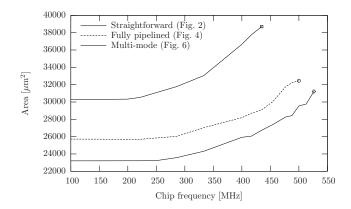

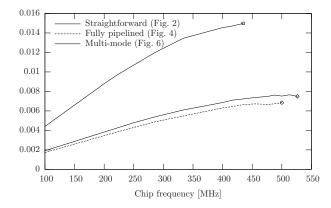

|   |               | 3.2.4 Performance evaluation of the proposed architecture 61                       |

|   |               | 3.2.5 Comparison with other fast and versatile implementations of DES 63           |

|   |               | 3.2.6 Proposed architectures modifications for bit-slice P&R 65                    |

|   |               | 3.2.7 Conclusion on the DES architecture                                           |

|   | 3.3           | Fully combinatorial DES implementation                                             |

|   |               | 3.3.1 Combinatorial DES datapath                                                   |

|   |               | 3.3.2 Security properties of the combinatorial DES 69                              |

|   | 3.4           | DES remarkable cryptological properties                                            |

|   |               | 3.4.1 DES weak keys and fixed points                                               |

|   |               | 3.4.2 DES semi-weak keys and anti-fixed points                                     |

|   | 3.5           | DES remarkable SCA properties                                                      |

|   |               | 3.5.1 Semi-weak keys                                                               |

|   |               | 3.5.2 Weak keys                                                                    |

|   |               | 3.5.3 SCA properties generalization for arbitrary keys                             |

|   | 3.6           | Explanation for the differential traces using HW vs HD                             |

|   | 0.0           | 3.6.1 Interpretation of the differential trace using HW                            |

|   |               | 3.6.2 Interpretation of the differential trace using HD                            |

|   |               | 3.6.3 Single <i>versus</i> multi-bit HW or HD selection functions                  |

|   |               | 3.6.4 Conclusion: improvement of side-channels analyzes                            |

|   | 3.7           | Realization of the DPA on DES                                                      |

|   | 0.,           | 3.7.1 Selection function for the DPA on the DES architecture of SecMat V1 107      |

|   |               | 3.7.2 DPA on traces integrals                                                      |

|   |               | · · · · · · · · · · · · · · · · · · ·                                              |

| 4 |               | kend countermeasures against SCAs 113                                              |

|   | 4.1           | Leaking no information                                                             |

|   |               | 4.1.1 Information = distinguishability                                             |

|   |               | 4.1.2 Randomization                                                                |

|   | 4.2           | The secured library "SecLib"                                                       |

|   |               | 4.2.1 Secured standard cells                                                       |

|   |               | 4.2.2 CMOS structures for the secured cells                                        |

|   |               | 4.2.3 Use in a regular design flow                                                 |

|   |               | 4.2.4 Performances                                                                 |

|   |               | 4.2.5 The "SecLib" library                                                         |

|   |               | 4.2.6 Interconnect involvement in a circuit security                               |

|   | 4.3           | A place-and-route strategy for secured ASICs                                       |

|   |               | 4.3.1 Using differential logic to thwart SCA                                       |

|   |               | 4.3.2 The "backend duplication" method                                             |

|   |               | 4.3.3 The constraints required by the "backend duplication" method 132             |

|   |               | 4.3.4 "Backend duplication" method insertion into an existing design flow $133$    |

|   |               | 4.3.5 Comparison of the "backend duplication" method with related works $134$      |

|   |               | 4.3.6 Suitability of the "backend duplication" method with some logic styles $134$ |

|   |               | 4.3.7 Backend triplication                                                         |

|   |               | 4.3.8 Implementing a duplicated netlist                                            |

|   |               | 4.3.9 Conclusion on the "backend duplication"                                      |

| CONTERNITO | ••    |

|------------|-------|

| CONTENTS   | XXVII |

| CONTENTS   | AAVII |

|              | 4.3.10 Graphical illustrations of the "backend duplication" method | 41 |

|--------------|--------------------------------------------------------------------|----|

| 5            | Conclusions                                                        | 45 |

|              | 5.1 Summary of the dissertation                                    | 45 |

|              | 5.2 Perspectives                                                   |    |

|              | 5.2.1 Open issues                                                  |    |

|              | 5.2.2 Going further                                                |    |

| $\mathbf{A}$ | Attackees/attackers technical details                              | 47 |

|              | A.1 The SecMat circuits family                                     | 47 |

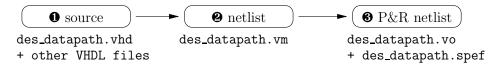

|              | A.1.1 SecMat frontend                                              |    |

|              | A.1.2 SecMat backend                                               |    |

|              | A.2 The attack boards                                              |    |

|              | A.3 The acquisition setup                                          |    |

|              | A.3.1 Optimal power traces acquisition experimental conditions     |    |

|              | A.3.2 The acquisition software                                     |    |

| В            | Power Traces on the DES Co-Processor of SecMat V1                  | 61 |

|              | B.1 Hamming weight vs Hamming distance differential traces         | 62 |

|              | B.2 DPA signal-to-noise ratios on DES                              |    |

| $\mathbf{C}$ | Glossary 1                                                         | 77 |

xxviii CONTENTS

# Acknowledgments

The work presented in this manuscript compiles the results of four years of research towards the definition of a backend-level solution to thwart power attacks on electronic integrated cryptosystems.

First of all, I am grateful to the members of the jury, to have accepted to review my work and to organize my public defense. Professor Francis JUTAND made me the invaluable honor of being the chairman of the jury. His broad knowledge of the information theory sector helped situating this work in a more global and quickly evolving context. Professors David NAC-CACHE and Jean-Jacques QUISQUATER thoroughly analyzed my manuscript and suggested relevant perspectives. Professor Marc Renaudin, through the work conducted under his supervision at TIMA, gave me insights related to power attacks realized on QDI (and other exotic logic styles) circuits. Doctor Pierre-Yvan LIARDET represented the industrial point of view on side-channel resistance: he motivated sound albeit integrable solutions against the side-channel leakage problem.

I could not have produced this document without the help of many folks.

To begin with, I wish to express all my sincere gratitude to Renaud PACALET, my supervisor. He has been able to make me take crucial decisions, while in the meantime leaving me a large space for innovation. This accounts for the large variety of skills that I learnt throughout this PhD. For instance, I had the rare opportunity to design two dedicated circuits in embedding full custom structures. It is from Renaud that got the conviction that there was both a scientific and industrial need for trusted computing platforms. Renaud's philosophy to find the best possible solutions before looking for acceptable trade-offs encouraged me: this idea gave birth to fundamental results, resisting the evolution of the state-of-the-art, which was reassuring me regarding the continuity of the work. As the leader of the LabSoC at Sophia Antipolis, Renaud also plunged the problematic of ASICs security into that of complex systems-on-chip. Many local contractual projects (especially with STMicroelectronics) added to the stimulation towards achieving a reliable DPA-proof design flow for trusted platforms.

Philippe MATHERAT taught me that the physics of the computation is a theory still at its infancy: the principal results remain to be discovered. He interested me on the links between logical and physical dissipation; this open question motivated my researches. Is the dissipation correlated to the difficulty of the computations? This problem is certainly is major theoretical challenge deserving of being tackled with in the next century!

Philippe HOOGVORST gave me inestimable insights about some advanced cryptographical issues. He has always been available to discuss some very accurate technical questions. Moreover, I owe him a lot of gratitude for his lessons in object-oriented coding and in software development technics.

All the other members of the Digital Electronic Group at the ENST (groupe "VLSI", later renamed "Systèmes Électroniques Numériques") also contributed to this work, everyone in its own manner. Yves MATHIEU, with its inexhaustible energy, encouraged me on an everyday basis. He also provided the adequate support when necessary: it is with its help that libraries were layout, that simulations were achieved, that complex designs were verified, and finally that circuits were timely taped-out. Jean-Luc DANGER got personally involved in the security

project, also trying to apply the results to other fields, such as reconfigurable computing and asynchronous logic. Jean PROVOST transferred me most of his valuable expertise in submicronic technology processes and in electrical simulation. Alexis POLTI and Lirida NAVINER DE BARROS's interest in embedded devices also influenced this work. I am also in debt from them for their pieces of advice when I was stuck on technical problems.

I also thank Karim BEN KALAIA for designing and debugging the attack boards. Without his help, no accurate side-channel measurements would have been possible. Karim provided and still provides useful guidance for the choice of the appropriate technical solution to the daily electric challenges.

The IT team, and especially the system administrators of the COMELEC laboratory, Arnaud LAURIOU and Frédéric PAUGET (staff of the CNRS LTCI – UMR 5141), installed the peripherals needed to control devices and to automate the traces acquisition campaigns. They guided the choice for the most adequate hardware and software resources to carry out the difficult task of building up a security evaluation platform. I especially thank Frédéric PAUGET for his proactivity in the choice for two critical computing resources: the 2-Terabytes SVN repository & SQL database server (geant.enst.fr) and the supercomputer (genie.enst.fr), taylored for the side-channel traces storage and analysis.

Laurent SAUVAGE actively contributed to the side-channel evaluation platform and solved many difficult issues related to side-channel measurements. I now wish that Laurent obtains brilliant results from the time he invested in the traces acquisition platform. Many thanks to Florent FLAMENT, for its exceptional involvement in the "SecMat" adventure, and for his highly valuable technical mastering and also for his precious sense of organization. Florent's work helped to structure the various developments around hardware attacks and counter-measures, and to capitalize on them. I am very proud to say that some brilliant results, especially those reported in chapter 3, were first suggested by Florent.

Many other people participated on aspects that are not accounted for in this manuscript. To cite a few: Mohamed EL HARHAR and Freddy ZANIN, for the design of the ancestor of SecMat, Hervé FINE and Nicolas PACHER for attacks on FPGA boards, Sumanta CHAUDHURI for the securization of asynchronous FPGAs, Viriginia MARTíN HERíZ for her preliminary results on the DPA on AES, Johannes SCHMIDT for the implementation of novel attacks, Korinna LENZ for the attack against software implementation of DES running into an home-made fake smartcard based on an ATMEL ATMega processor.

The integration of this work on the circuits' security into a larger "Trusted Computing" GET<sup>1</sup>-wide structuring project enlarged the scope for the hardware to the software. The contributions of Sophie COUDERT, Ronan KERYELL and Guillaume DUC, and of course of Renaud PACALET, were fundamental for the project creation.

Collaborations outside of the GET, mainly motivated by national projects, were also very fruitful. Many ideas originate from discussions with STMicroelectronics at Rousset, TIMA CIS and QLF groups at Grenoble, the multi-wafer project broker CMP at Grenoble, LIRMM at Montpellier, UCL at Louvain-la-Neuve and Oberthur at Nanterre. I also thank colleagues from the LIP6 of Université Pierre et Marie Curie for informal information exchange during the backend stages of the ASICs design.

Finally, I thank all my close friends and my family, that were sometimes wondering why I spent so much time working instead of caring of them. Thank you for your comprehension, and also for making me work smarter, not harder!

For the list to be really complete, I must thank the open source and/or free software developers and maintainers community. Many of them, through their advice and their software packages, helped me a lot, for a variety of tasks: computation, design automation, source code management, edition, typesetting and presentation. I especially thank the numerous volunteers of bugs.gcc.org and of comp.lang.c++.

<sup>&</sup>lt;sup>1</sup>The GET is the "Groupe des Écoles des Télécommunications": http://www.get-telecom.fr/.

## Introduction

This thesis is concerned with the security of electronic circuits against attacks on their implementation

Cryptographic algorithms have traditionally been studied to withstand theoretical attacks, that are tacitly tantamount to black-box attacks. However, when these algorithms are implemented in a real devices, many other specific attacks become possible. With the advent of attacks on the physical implementations, some information can be diverted (i.e. extracted) from the circuits, or even altered (i.e. modified) by external means, which makes the security requirements more stringent. The new types of attacks are referred to as **observation** (or "SCA", short for Side-Channel Attack) and **injection** (or "FA", short for Fault Attack) attacks. These attacks, targeting the physical level, move the context from black-box to gray-box, because some internal variables can be partially read or written to [43]. The type of hardware that is vulnerable to SCA and FA is that where the power is supplied externally or easily accessible by an outsider: this includes contact and contactless smartcards, but also any mobile devices (handheld or not.) The exploitation of the electromagnetic field makes it possible to mount remote attacks on otherwise physically unattainable circuits. In this security context, the attacker model must be refined. In the introduction or the dissertation, the difference between the logical and the physical cryptanalysis is discussed.

Then an analysis of the SCAs [66] is carried out. They happen to be "structural attacks", in the sense that are inherent to information processing. In particular, cryptographic algorithms, because of some Boolean properties of their architecture, are especially sensitive to SCAs. When applied on symmetrical ciphers, we show that SCAs are inescapable on ideal hardware without counter-measures, because the minimum information that leaks happens to be the full key itself. Then we show that SCAs are enhanced by the technological limitations, such as the limited datapath bitwidth, and that cryptographic algorithms increase the power of SCAs.

After that, we show how to avoid SCAs by leaking almost no information. And, given that information leakage is inescapable, how to build secured circuits? The DES case-study helps us to show how to evaluate the implementation dissipation via the power emanations. The architecture of a representative crypto-processor and the implementation issues are discussed. The co-processor security is evaluated w.r.t. logical and physical attacks.

The security flaws brought to the fore are then used to propose an unconditionally secure module. We discuss a method based on a technological balancing. Both gate-level design and CAD techniques are addressed: the SecLib secured library conveys a syndrome-free elementary computation kernel at the bit-level, while the "backend duplication" strategy allows for an efficient use of those gates in arbitrary complex netlists.

Finally, we conclude on the evaluation platform that has been set up, and we mention the open problems that remain to be tackled with.

**Key words**: Trusted computing, secured electronics, layout-level counter-measures, side-channel attacks, SPA/DPA, power analysis, physical cryptanalysis, topological constraints, geometrical symmetries.

# Chapter 1

# Physical cryptography

This chapter presents the vulnerabilities of electronic circuits arising when an attacker is able to acquire some physical emanations in addition to the public information. The attack scenario is thus augmented: "logical" security requirements remain, while "physical" security precautions add up. The objective of this chapter is to lay rational bases for the topics developed in the rest of the PhD dissertation. The two ideas that we promote are:

- 1. The need for rigorous threat assessment and associated proven counter-measures.

- 2. The fact that attacks are reproducible, and that their outcome is deterministic and inherent to both the algorithm and the *ad hoc* architecture used.

It is thus possible to unify logical and physical security requirements in a global security framework where defenses against both abstract and concrete attacks must be devised. This is the field of "physical cryptography".

### 1.1 Overview of the cryptography

#### 1.1.1 Security needs

From a user point of view, the cryptography is a set of solutions that can be assembled to provide solutions to some basic usages, such as:

- privacy,

- integrity,

- authentication.

- non-repudiation, etc.

#### 1.1.2 Security objects

Similarly to every complex system, the cryptography can be divided into layers, that are illustrated in the table below along with an example of a desirable property;

| Layer             | Example of property        |

|-------------------|----------------------------|

| Boolean functions | Non-linearity              |

| Algorithms        | One-way                    |

| Protocols         | Zero-knowledge             |

| Applications      | Authentication implemented |

This structure allows an abstraction between the layers. For instance, the algorithms are most of time independent of the Boolean functions actually used, provided they feature a high degree of non-linearity. The protocols are themselves independent of the underlying algorithms. If for instance the one-wayness property is desired, then many algorithms can be used interchangeably. Finally, at the application level, the protocols are also seen as commodities. Application that rely on SSL/TLS (Secure Sockets Layer / Transport Layer Security) typically initiate a communication with an exchange of ServerHello and ClientHello, where the two parties agree for a common protocol.

In the framework of this thesis, we focus on the Boolean vectorial functions and algorithms. This selection is motivated by the facts that the attacks on the implementation usually target more specifically the lower layers and that the security of protocols and applications are more logical concerns.

The algorithms of concrete use can basically fall into three categories. Their resistance against cryptanalytic and brute-force (or exhaustive) attacks is respectively based on [60]:

- 1. Symmetrical encryption and message authentication codes (MACs):

- Cryptanalysis: number of rounds, taylored substitution boxes,

- Brute force: size of the key;

- 2. Hash:

- Cryptanalysis: number of rounds, taylored substitution boxes,

- Brute force: size of the hash-code;

- 3. Asymmetrical encryption:

- Cryptanalysis: mathematical  $\mathcal{NP}$ -complete problem,

- Brute force: size of the key.

Symmetrical encryption, hash and MAC primitives are closely related. A block cipher, such as DES [71], can achieve the three. Similarly, a hash function, such as SHA [69], can do the same (the encryption algorithm derived from SHA has been baptized SHACAL.) There are no widespread MAC algorithm that is not based upon an encryption or an hash algorithm.

In the sequel, algorithms based on DES will be more specifically studied.

### 1.2 The gray box model

The general context for cryptographic attack is that of a black-box: internal variables are unknown. However, the algorithmic details are fully available to the attacker. This principle is known as Kerckhoff's law. It encourages security-by-clarity design methodologies rather than security-by-obscurity. The security-by-obscurity is somehow similar to obfuscation: it makes the attack setup more difficult, but once this obstacle is overcome, it does not decrease its strength.

The concrete systems that are the targets of attacks are often very complex, which might confuse analysis when trying to identify their critical parts. The first goal of an attacker is indeed to locate the sub-system in charge of using confidential information. This sub-system is almost always a cryptographic block. Under the abovementioned "open system model", the whole system reverse-engineering is supposed to be feasible; it is even assumed that the insulation of the cryptographic sub-system is easy as compared to its attack.

Paradoxally enough, the "architectural" complexity of a system is a burden to its security. Indeed, a complex system is structured in layers (similar to the OSI [110] stack), in which every

level of abstraction brings its own vulnerability. The security of a combination (even with embedded counter-measures) equals that of the weakest link.

In the context of attacks on the implementation, some internal variables, not always chosen nor known, can be read or written to [43]. These attacks are customarily referred to as side-channel attacks (SCAs), that divide into passive (or observation) and active (or fault) attacks.

Cryptanalysis consists in finding an exploitable bias, due to an unknown design flaw, that none of the up-to-now tests detected. In that sense, passive attacks on the implementations and cryptanalysis are much alike.

Active attacks are more powerful than passive ones: the DFA<sup>1</sup> of Piret and Quisquater [40] requires as few as two well-behaved faults to successfully attack AES, whereas DPAs [54] require in the best cases a few hundreds of traces. Active attacks are also more expensive, because their setup is not trivial [11]. Seldom gate-level counter-measures against FAs have been reported (refer for instance to [94] for some suggestions); One reason is that the reporting of a detected error is complex, and that this protection can itself be circumvented with faults. Therefore FA counter-measures are usually a matter of algorithms. Additionally, the FAs are very different in nature from SCAs and so are the counter-measures against them. Because the SCAs are already a very complex matter we decided not to consider FAs. Instead, we focus on observation attacks and associated counter-measures at the implementation-level.

#### 1.2.1 Framework for the attacks considered in this PhD thesis

The security evaluations realized in this work meet the same standards as cryptanalysis: all the implementation information, such as algorithm and its layout, is supposed to be known to the attackers.

Moreover, the attacker can make an unrestricted use of the system. Typically, an unbounded number of calls to cryptographic functions is possible. The attacker can also tamper with the circuit that make up the system, for instance to access its power supply.

Furthermore, we make the hypothesis that the analysis laboratory itself (probes, synchronization signals, etc.) is embedded onto the chip.

In order to evaluate our work, custom ASICs have been designed. They allow for a full control over the algorithm implementation, and an accurate access to the synchronization and the physical parameters (such as the power, the EMI, the temperature, etc.) They also allow for a comparison between the measures and the simulations, which is essential from a scientific point of view when analyzing attacks results.

When dealing with counter-measures, **efficiency** is the first focus, irrespectively of **over-head**. Unless otherwise explicitly stated, this is the securization strategy we adopt in this thesis. Indeed, the goal of this work is to conclude regarding the efficiency of counter-measures when the maximum efforts have been spent. If an efficient (albeit expensive) solution is found, then it is relevant to optimize it without compromising its efficiency until its cost becomes acceptable for a given application. On the contrary, if no satisfying solution can be found whatever the cost, it would be useless to spend efforts in optimization. In this case, the very valuable result would be the conclusion that low level design counter-measures are unpractical.

### 1.2.2 Side-channel analyzes provided with in this PhD thesis

The analysis of side-channel information from power or electromagnetic traces requires a lot of care to properly *gather*, and then *understand* them. Some power traces are included in Appendix B, to avoid over-loading chapters with numerous graph data. We paid attention to annotate the graphs with the time expressed in clock periods and the amplitudes with the appropriate physical units. This enables a rigorous scientific interpretation of the data.

<sup>&</sup>lt;sup>1</sup>The technical acronyms are explained in the Appendix C.

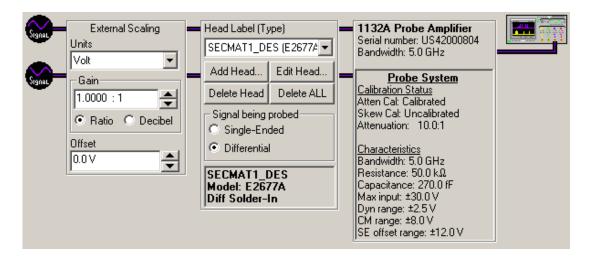

The acquisition platform is described in Appendix A. It can be noticed that all the acquisitions are performed at 20 Gsample/s, which is in most cases much more than necessary to successfully attack an unprotected device (refer for instance to the attacks described in Sec. 3.7.2.) The attacked circuits were typically clocked at 32 or 66 MHz, which means that some hundreds of points are available for every clock period. However, this acquisition speed is not an over-kill from a scientific viewpoint, because it makes it possible to analyze fine events occurring within the clock period. Many results presented in the Chp. 3 would not have been obtained with a lower acquisition rate.

# 1.3 Attack of flawed implementations

A software bug can trivially make some attacks possible. For instance, a software bug may be exploited to read a sensitive memory area. Like in software, hardware flaws can fully compromise the security. For instance, if scan-chains or test-points are left unprotected, secrets could be disclosed But in hardware, the consequences of design flaws can lead to more subtle leaks. In a design that lacks clock-tree buffers, the power consumption will be increased and so will probably be the information leaks. A dual-rail<sup>2</sup> circuit where the gates are balanced, but the routing is not, compromise the intended counter-measure based on symmetry. Ironically enough, those two problems were indeed encountered in our first ASIC (nicknamed SecMat V1) . . .

All the results presented in this work take for granted that the studied implementations are correct, that is to say that they respect their specifications and that the specifications are sane (which is far from being obvious.)

# 1.4 Common misconceptions

When evaluating the strength of attacks targeting a piece of hardware, its security level is generally over-estimated. Let us compare the cost of a logical and a physical cryptanalysis on DES. For the sake of simplicity, the attack is chosen to be of *brute force* type in both cases. The cost function is taken equal to computation time:

- no space-time trade-off is used for the logical attack and

- the traces are accumulated as soon as they are captured in a DPA acquisition setup.

Then with the state-of-the-art hardware,

- $5369726 \approx 2^{22}$  simple-DES encryptions per second (assessed with the built-in self test "openss1 speed des" [30])

- 1 acquisition per second with an oscilloscope, including the pre- and post-processing (trigger setting & saving the averaged results on the disks; for accurate figures, refer to Appendix B at page 161)

Thus, to keep the same level of security as DES (which is low w.r.t. current security standards), a DPA-proof hardware should withstand an attack using  $2^{56-22}=2^{34}\approx 17$  billion traces. This ratio is relevant in the respect that the rare resource is the minimum number of encryptions that an attack must realize to retrieve the full secret. This figure is much higher than what is usually considered in the literature. This cautionary note is to be taken all the more seriously as some attacks on unprotected implementations are practical with as few as a couple or tens of power traces. Such attacks are for instance reported in the article about ITA [32] when some

$<sup>^2</sup>$ Dual-rail circuits is a widely studied counter-measure against power analysis. It will be explained in deep details in the following chapters.

1.5. AUDIENCE 5

key bits are manipulated individually, which might happen in software implementations. On parallel architectures, we successfully retrieved six key bits (the ones at the input of the sbox #6) with as few as 28 averaged power traces, using a selection function not described in this thesis.

# 1.5 Audience

The target audience for this PhD thesis is mainly cryptographers and designers of secured embedded systems. Some results from the PhD has been published in journals or conferences proceedings. Some others are presented genuinely in this manuscript. Finally, some issues were not fully explored. They are presented as "open problems" or as "conjectures", to be addressed in future works.