# Fiabilité du signal des circuits logiques combinatoires sous fautes simultanées multiples

Denis Teixeira Franco

### ▶ To cite this version:

Denis Teixeira Franco. Fiabilité du signal des circuits logiques combinatoires sous fautes simultanées multiples. domain\_other. Télécom ParisTech, 2008. English. NNT: . pastel-00005125

### HAL Id: pastel-00005125 https://pastel.hal.science/pastel-00005125

Submitted on 13 Aug 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Fiabilité du Signal des Circuits Logiques Combinatoires sous Fautes Simultanées Multiples

Denis Teixeira Franco

2

\_

# Acknowledgments

Follows some acknowledgements, that have been written in French.

Et voilà, la thèse est finie. Cette section est consacrée aux remerciements aux personnes que d'une façon ou d'autre ont participé de ce parcours pendant trois années et quelques mois. Cette section représente aussi la possibilité d'une manifestation personnelle dans un document strictement technique et, alors, une précieuse opportunité.

Je remercie tous les membres de mon jury de thèse : M. Patrick Garda (président), MM. Alexandre Schmid et Patrick Girard (rapporteurs), MM. Fabrice Auzanneau et Yves Mathieu (examinateurs). Je remercie également mes directeurs M. Jean-François Naviner et Mme. Lirida Naviner pour l'évaluation publique très positive qu'ils ont faite du travail realisé.

Je voudrais remercier les personnes qui ont participé, directement ou indirectement, à la réussite de cette thèse. Je pense particulièrement aux professeurs du département de langues de l'ENST, qui m'ont appris à aimer la langue et la culture française. Les cours de FLE (Français Langue Étrangère) ont été une excellente opportunité de connaître des collègues du monde entier, avec leurs coutumes et richesses, qui m'ont fait voir le monde autrement.

Je remercie les interlocuteurs d'EGIDE, qui ont fait de leur mieux pour mener toutes les situations à bon terme. Un merci spécial à M. Bonenfant, qui s'est toujours battu avec EGIDE pour nous garantir les meilleures conditions de séjour possibles.

Je remercie les personnes du département COMELEC, dont quelques uns ont dépassé leurs attributions officielles et sont devenus des amis. Chantal et Karim, un grand merci à vous. Je remercie les membres du groupe SIAM : Mme. Desgreys et Messieurs Loumeau, Petit et Nguyen. Mon merci est extensible à Ali, Rachid et Hussein, qui ont rejoint le groupe. Les échanges et l'ambiance bonne humeur m'ont beaucoup aidé dans ce parcours.

Je remercie tout particulièrement mes directeurs de thèse, M. Jean-François Naviner et Mme. Lirida Naviner, pour la confiance qu'ils m'ont faite, pour leur manière de diriger ce travail de recherche. Vos conseils et suggestions m'ont permis de mener à bien ce travail. Je vous remercie aussi pour les opportunités que vous m'avez offertes, elles ont été fondamentales pour l'évaluation et maturation des recherches développées. J'espère pouvoir travailler en coopération avec vous dans l'avenir.

Je remercie les collègues en thèse et stage et les amis à l'école, qu'ils soient arrivés ou qu'ils soient partis pendant mon séjour, nous avons partagé des moments de sport, de pause café, de Butte aux Cailles, de karaokê, pique-nique ou simplement de rigolade au bureau. Sans ces moments de décontraction, je ne pense pas que la thèse se serait déroulée aussi bien que ça.

Je voudrais remercier ma famille, qui même au Brésil a eu un rôle très important dans cette conquête. Leur support logistique et psychologique a été très important et a beaucoup aidé à réduire la distance qui parfois pesait énormément.

Je voudrais finalement remercier ma femme, qui a été la principale responsable pour l'achèvement de ce travail. Merci beaucoup Roberta, d'avoir cru à notre venue en France, d'avoir insisté quand j'avais déjà désisté, d'avoir compris mes moments de absence et de m'avoir supporté et soutenu dans les moments de tristesse et angoisse. Roberta, ce travail est dédié à toi.

# Abstract

Integrated circuits have known a constant evolution in the last decades, with increases in density and speed that followed the rates predicted by *Moore's law*. The tradeoffs in area, speed and power, allowed by the CMOS technology, and its capacity to integrate analog, digital and mixed components, are key features to the dissemination of integrated circuits on the field of telecommunications. In fact, the progress of the CMOS technology is an important driver for telecommunications evolution, with the continuous integration of complex functions needed by demanding applications. The evolution scenario of the consumer electronics industry is a result of the fairly easy gains obtained with CMOS scaling, but this scenario is about to change, as scaling approaches some limits that make further improvements more difficult and even unpredictable.

The continuous reduction in the dimensions of integrated circuits has raised some serious problems to the implementation of nanometric circuits, like power consumption and dissipation, current leakage and parametric variations. Many of these problems lead to a reduction in the yield and the reliability of CMOS devices, what can seriously compromise the gains attained with technology scaling. To cope with these problems, work-around solutions are necessary, and more specifically, the sensibility of the circuits to transient faults must be improved.

Historically, transient faults were a concern in the design of memory and sequential elements only, and the protection of these elements is fairly simple and do not impose critical overheads, due to the static nature of the data involved. On the other way, the susceptibility of combinational blocks to transient faults, e.g., soft errors, thermal bitflips, parametric variations, etc, increases as a side effect of technological scaling, and the protection of these blocks poses some problems to the designers. Known solutions are the use of fault-tolerant approaches, like modular redundancy and concurrent error detection but these solutions lead to important overheads in terms of implementation area, propagation time and power consumption. The referred solutions are traditionally targeted to mission critical applications, where reliability improvement and fault secureness are the main design objectives, and the resulting overheads can be accepted. In the case of mainstream applications, other design objectives are privileged and the implementation of these fault-tolerant approaches must be bounded by a detailed cost-benefit analysis.

Given the overheads associated with the traditional fault-tolerant approaches, alternative solutions based on partial fault tolerance and fault avoidance are also being considered as possible solutions to the reliability problem. These approaches are based on the application of fault tolerance to a restricted part of the circuit or hardening of individual cells, allowing fine-tuned improvements on the reliability and limiting the concerned overheads.

The choice of what reliability improvement method is better suited for a given application is not simple as the problem involves multi-criteria optimization. In this context, a fast and accurate evaluation of circuit's reliability is fundamental, to allow a reliability-aware automated design flow, where the synthesis tool could rapidly cycle through several circuit configurations to assess the best option. Unfortunately, reliability analysis is a complex task, and computing its exact value is intractable for practical circuits.

Different methodologies have been proposed to evaluate the reliability of combinational circuits, where the computation of its exact value is limited by the size of the target circuits. For practical circuits, reliability analysis is generally bounded by simplified assumptions, like single-output, single-fault or single-path, what limits the results of the analysis. Furthermore, most of the proposed methodologies are based on external software packages or simulation, making difficult its integration to an automated design flow.

The current work proposes two new methods for reliability analysis, the first one based on a probabilistic binomial model and the second one based on signal probability propagation. The probabilistic binomial reliability analysis (PBR) method uses fault injection and functional simulation to determine an analytical model for the reliability of the circuit. Exploring the binomial probability distribution of multiple simultaneous faults, the proposed method allows an accurate estimation of the signal reliability of combinational logic circuits. The signal probability reliability analysis (SPR) uses a modified representation of signal probabilities to determine the cumulative effect of multiple simultaneous faults in the reliability of a circuit. Based on a straightforward signal probability computation algorithm, the methodology allows the evaluation of the logical masking capability of combinational logic circuits.

To validate the proposed methods, the reliability analysis of several fault-tolerant and hardened arithmetic circuits are presented and the bounds of applicability of these approaches are determined.

# French Summary

### Introduction

L'entrée de la technologie CMOS dans les dimensions nanométriques résulte de l'évolution prévue pour les circuits intégrés, déterminée par l'industrie des semi-conducteurs d'après les feuilles de route établies selon la loi de Moore [1]. Pourtant, la production des circuits nanométriques présente des défis de plus en plus critiques, qui demandent des efforts considérables de la communauté scientifique. Ces défis sont liés à des limitations d'ordre physique, économique et technologique, et se traduisent en un changement du comportement des structures fortement intégrées et en une difficulté pour les fabriquer avec la précision nécessaire [2].

La majorité des problèmes associés à la réduction des structures CMOS amène à une réduction du rendement de fabrication et de la fiabilité d'opération des circuits. Les technologies émergentes, conçues pour étendre, complémenter, voire substituer la technologie CMOS, seront très sensibles aux variations paramétriques des composants et aux défauts de fabrication. Les solutions proposées passent par les méthodes traditionnelles de tolérance aux fautes, tolérance aux pannes et durcissement des composants, mais passent aussi par un changement de la façon de concevoir et implémenter les fonctions intégrées, dans une méthode de conception ascendante. La méthode de conception ascendante est inspirée des architectures reconfigurables, telles que les FPGA, parfois avec une granularité beaucoup plus fine. Ces structures reconfigurables, appelées "nanotissus", sont des matrices de très haute densité qui peuvent être configurées pour réaliser des fonctions logiques diverses, en prenant en compte seulement les composants opérationnels.

La conception ascendante est une réponse envisagée pour la question du rendement de fabrication mais la fiabilité d'opération des circuits reste un problème critique, pour lequel les solutions proposées font appel aux techniques de tolérance aux pannes. Selon quelques études [2], la probabilité d'occurrence des fautes transitoires dans les systèmes nanométriques montera au fur et à mesure de l'augmentation de densité des composants intégrés, atteignant le même niveau observé dans les mémoires, où les fautes transitoires sont plus facilement traitées. Historiquement, les techniques de tolérance aux pannes étaient destinées aux circuits de mission critique, à cause des surcoûts matériels, de performance et de consommation d'énergie associés à son application. Son utilisation dans les circuits logiques non critiques dépendra directement de son rapport coût/bénéfice, ce qui n'est pas évident à déterminer, d'autant plus que l'occurrence de multiples fautes simultanées deviendra une réalité.

Alors, le problème qui se pose est la détermination de la fiabilité des circuits logiques, en amont dans le flot de conception, de façon à permettre l'application des méthodes de durcissement les plus adaptées à chaque système, et de permettre une exploration rapide de l'espace de projet disponible. La fiabilité en question est la fiabilité du signal et des données, associée aux fautes transitoires et intermittentes. Les méthodes proposées pour ce type d'analyse sont généralement déconnectées du flot de conception des circuits intégrés et sont applicables à des parties spécifiques des circuits. Ce travail explore des méthodes d'estimation rapide de fiabilité, facilement intégrables dans le flot de conception, et qui peuvent permettre une comparaison préalable des différents choix architecturaux.

### Fiabilité et technologie nanométrique

La réduction des dimensions des structures CMOS intégrés a une très forte répercussion sur la fiabilité des circuits. L'augmentation de la densité des circuits associée à la réduction de la tension d'alimentation fait augmenter la probabilité d'occurrence des fautes transitoires et aussi la probabilité d'occurrence de fautes multiples. Les fautes transitoires peuvent être originaires de plusieurs sources :

- Neutrons de haute énergie et particules alpha présentes dans l'atmosphère;

- Bruit de couplage ou crosstalk;

- Bruit thermique;

- Fluctuations des tensions dues aux commutations des courants et IR drop (réduction de la tension d'alimentation dans un composant par la résistance des conducteurs);

- Bruit de substrat.

La prise en compte des ces problèmes est un défi urgent pour la communauté scientifique, ce qui représente la création et la validation de modèles et d'outils d'analyse adaptés aux besoins des concepteurs, intégrés dans le flot de conception de façon presque transparente. Parmi les problèmes mentionnés, les erreurs *soft* originaires des particules alpha et neutrons représentent un ancien défi, bien connu, mais qui prend une nouvelle dimension dans les structures nanométriques.

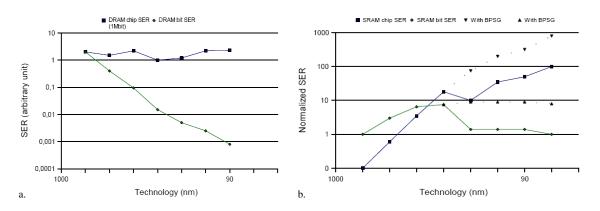

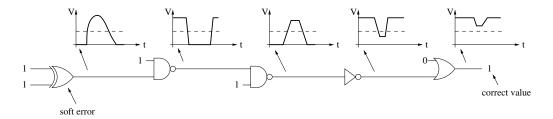

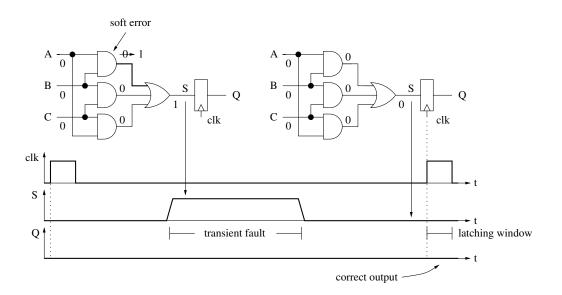

Les erreurs soft sont une menace classique pour les mémoires intégrées et pour les composants séquentiels, comme les bascules et flip-flops. L'interaction des particules alpha ou neutrons de haute énergie avec des composants CMOS peut faire commuter l'état d'un point mémoire ou d'une bascule, et cette erreur restera active jusqu'au moment où une nouvelle valeur est enregistrée. La prise en compte de ce type d'erreur est simple et les mémoires tolérantes aux fautes sont courantes dans les systèmes intégrés. Pourtant, les circuits logiques sont en train de devenir plus susceptibles aux soft erreurs à chaque nouvelle génération et ce niveau s'approche du niveau des mémoires non protégées [3]. L'équation (1) permet l'estimation du taux de soft erreurs (SER) dans les circuits CMOS dues aux neutrons de haute énergie.

$$SER \propto F \times A_{diff} \times exp(-\frac{Q_{crit}}{Q_{coll}})$$

(1)

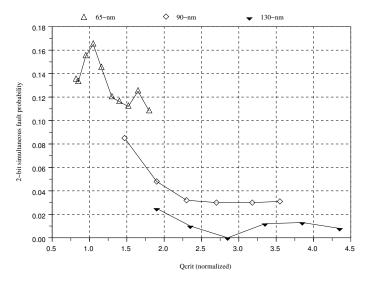

Dans ce modèle, F correspond au flot des particules,  $A_{diff}$  à la surface sensible à ces particules (surface des diffusions de la cellule),  $Q_{crit}$  au seuil de charge pour un changement de la valeur logique, et  $Q_{coll}$  correspond à la charge collectée par la cellule à l'occasion d'un impact de particule. La réduction des dimensions des composants amène à une réduction de la surface des diffusions et aussi de la capacité de collecte des charges. Par contre, la réduction de la tension d'alimentation correspond à une réduction du seuil  $Q_{crit}$ . Quelques études ont prévu une augmentation du taux d'erreurs à cause de la réduction de la tension d'alimentation, mais des études plus récentes ont démontré que ce taux est en baisse pour les cellules individuelles, qu'il reste presque constant pour les matrices de mémoire et qu'il augmente pour les circuits logiques. La situation est plus difficile parce que la réduction des tensions d'alimentation n'a pas suivi le facteur prévu par les règles de scaling. Même si la sensibilité aux erreurs soft due aux neutrons n'est pas si critique que prévue, la sensibilité aux particules alpha est en train de monter. De plus, la probabilité d'erreurs multiples augmente beaucoup avec l'augmentation de la densité des circuits, où un même impact de particule peut générer des erreurs dans les cellules voisines [4].

Le bruit thermique est, peut-être, la plus grande menace à l'évolution des circuits intégrés [5]. L'augmentation de densité et de fréquence d'opération des circuits peut amener à l'occurrence d'erreurs logiques, ce qui est associé à des limites physiques incontournables. En fait, les fréquences d'horloges des circuits intégrés n'augmentent plus comme prévu par la loi de Moore, à cause des problèmes d'instabilité d'opération et aujourd'hui l'évolution technologique représente plutôt un gain en densité des circuits qu'un gain en fréquence d'opération.

Pour faire face aux erreurs transitoires, les concepteurs peuvent utiliser des méthodes de durcissement et les architectures tolérantes aux fautes et aux pannes. Ces méthodes représentent toujours un surcoût en surface, en consommation ou en vitesse et leur utilisation pour le sauvetage des circuits nanométriques n'est pas évidente. Pour cela, l'estimation de la fiabilité des circuits logiques est fondamentale pour déterminer les gains réels obtenus avec les méthodes de tolérance aux fautes et de durcissement des circuits.

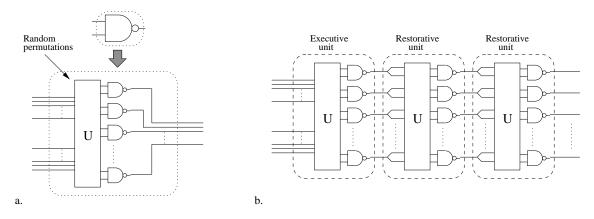

#### Les architectures auto-contrôlables, tolérantes aux fautes et robustes

La prise en compte des erreurs transitoires dans les circuits logiques passe par l'utilisation de redondance, sous une forme spatiale ou temporelle. Alors, un circuit intégré robuste représente toujours un surcoût matériel, temporel et de consommation d'énergie. Pour les applications critiques, dans les domaines médical, militaire et spatial, entre autres, la fiabilité d'opération est la propriété la plus importante et ces surcoûts sont nécessaires. Par contre, pour les applications plus générales, l'évolution est guidée par les gains obtenus avec la réduction d'échelle des structures intégrées, et l'implémentation de circuits plus robustes sera limitée par cette règle.

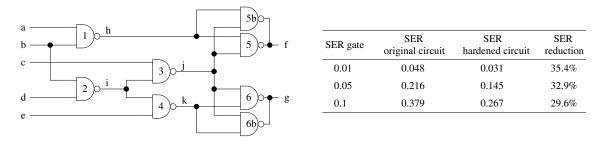

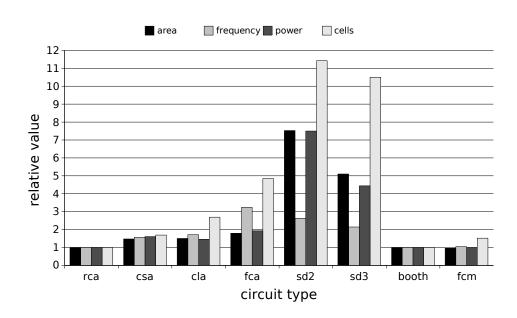

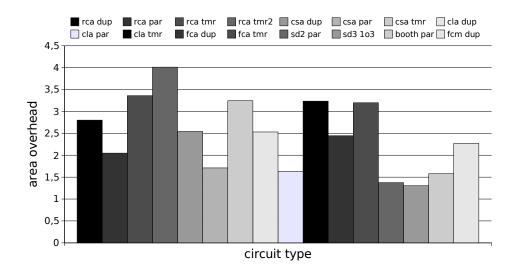

Dans le présent travail, une bibliothèque de circuits arithmétiques robustes a été implémentée, dans le but d'étudier l'impact des différentes techniques dans la fiabilité des circuits. Même si les surcoûts sont bien connus et le gain en fiabilité en présence d'une seule faute est bien compris, l'augmentation de la probabilité d'erreurs multiples et la réduction de la fiabilité de circuits logiques nanométriques demande des nouveaux modèles d'estimation de fiabilité, de façon a mesurer le gains réels apportés par les méthodes de durcissement proposées.

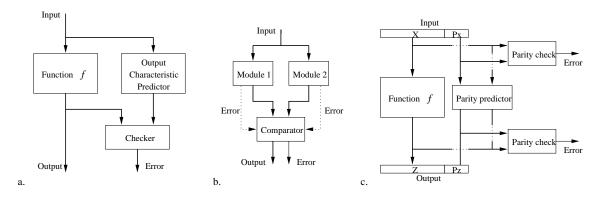

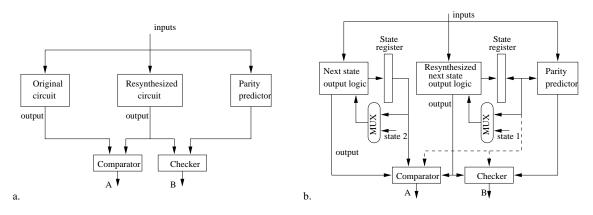

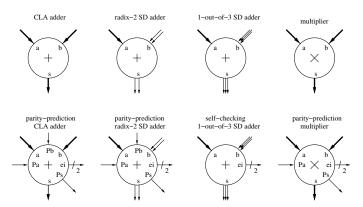

Dans le domaine des circuits auto-contrôlables, deux méthodes ont été étudiées, la prédiction de parité et la duplication. La prédiction de parité permet la détection d'une erreur dans un circuit arithmétique du type additionneur [6] ou multiplicateur [7, 8] en suivant le modèle de parité en (2). Dans l'équation, Pa et Pb correspondent à la parité des données d'entrée, Pc est la parité des données de retenue et Ps est la parité prévue du résultat.

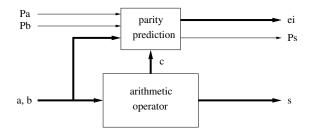

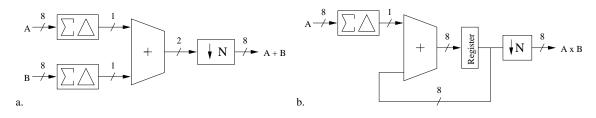

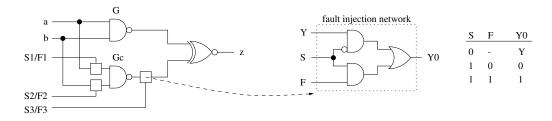

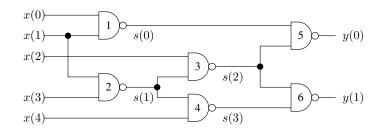

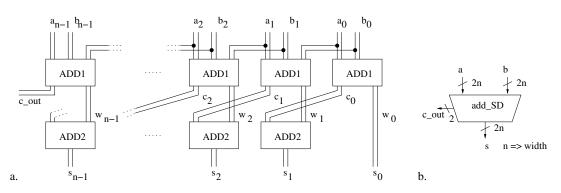

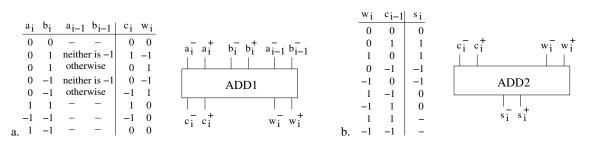

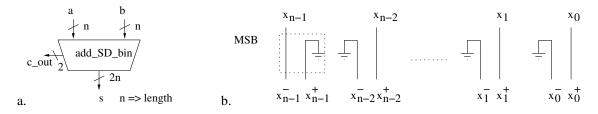

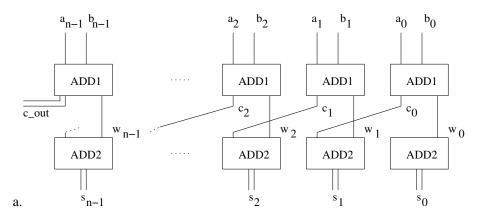

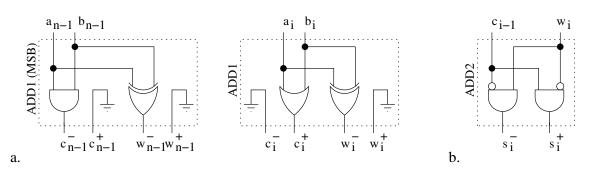

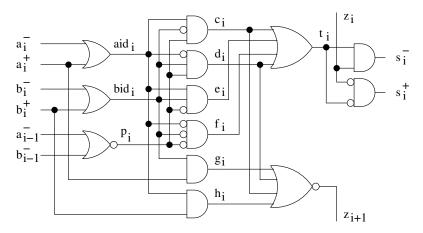

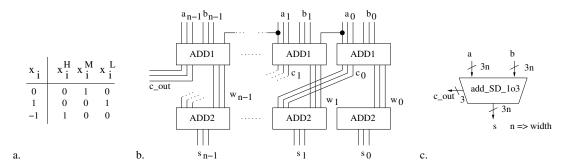

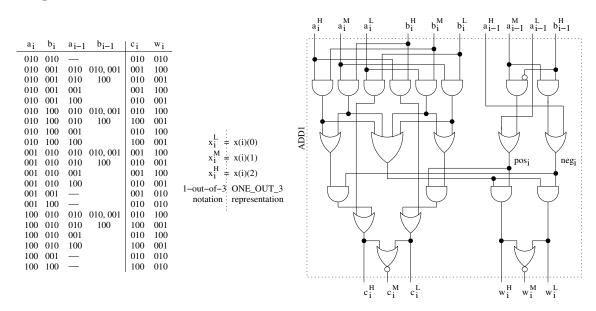

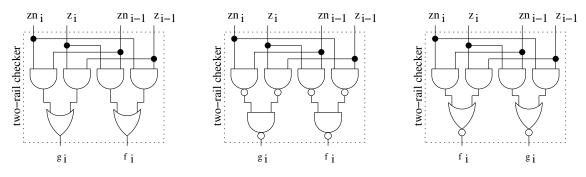

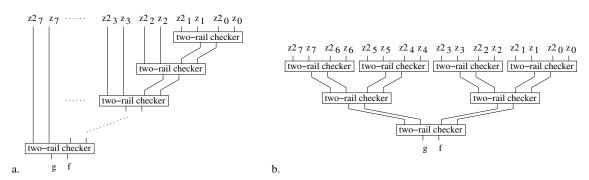

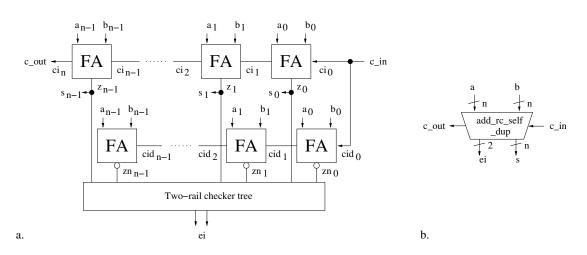

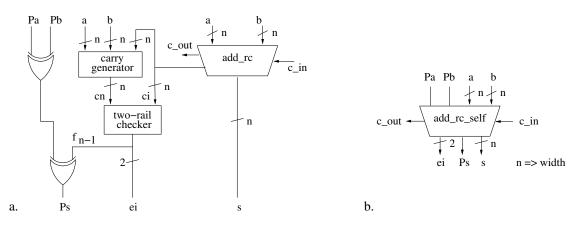

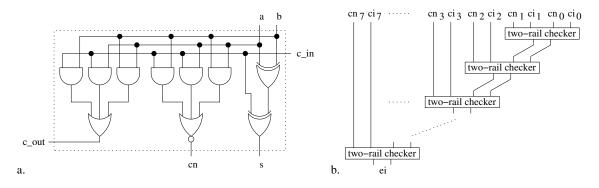

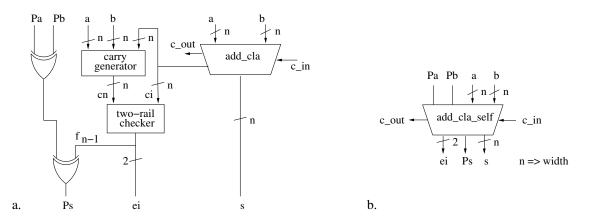

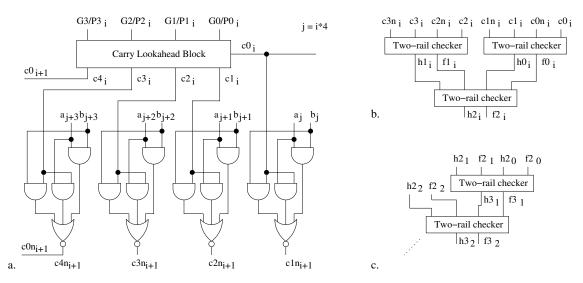

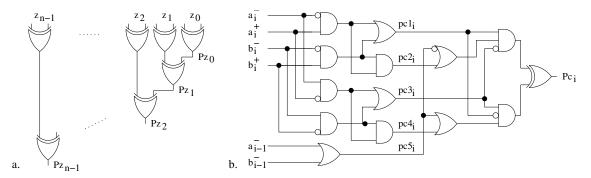

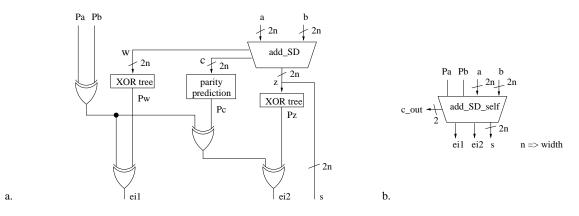

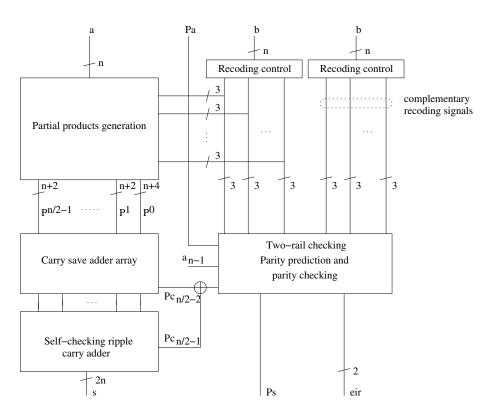

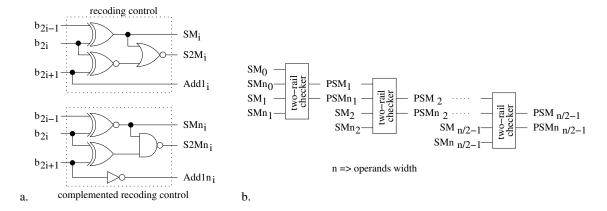

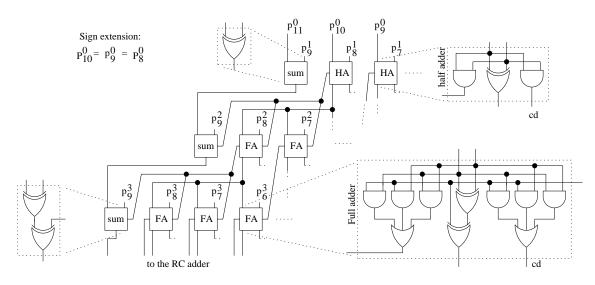

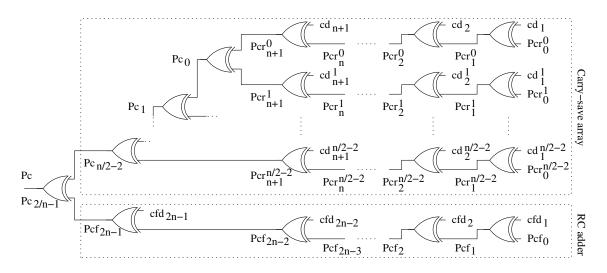

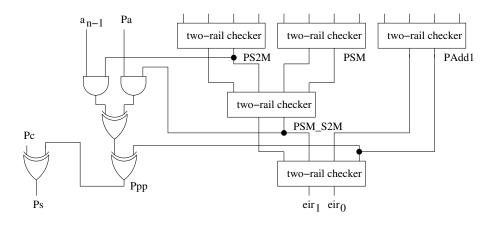

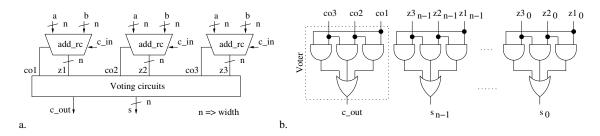

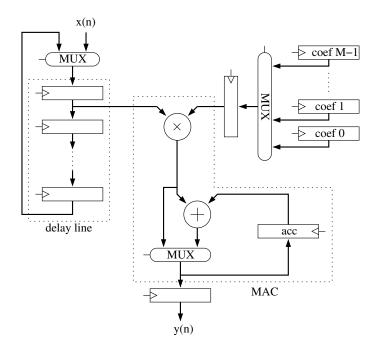

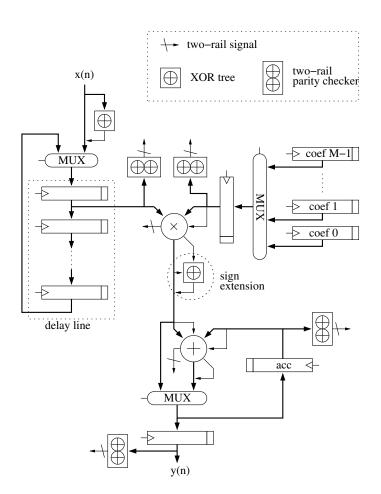

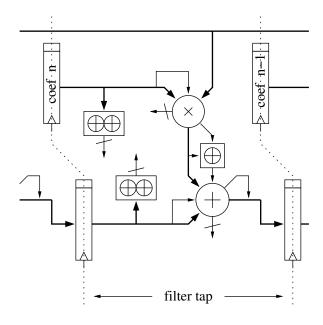

La Fig. 1 montre le schéma général de prédiction de parité dans un circuit arithmétique. La sortie *ei*, codée en représentation double rail, peut indiquer des erreurs dans le circuit qui ne sont pas détectables par le modèle en 2. Le contrôle de la parité est fait par les circuits externes à l'opérateur arithmétique. Le surcoût matériel pour la prédiction de parité est le plus bas parmi ceux des méthodes étudiées.

FIG. 1 – Schéma générale de la prédiction de parité.

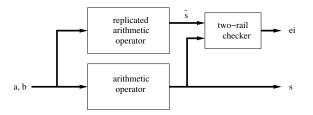

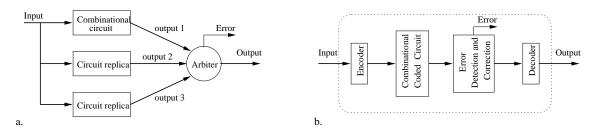

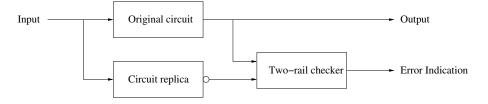

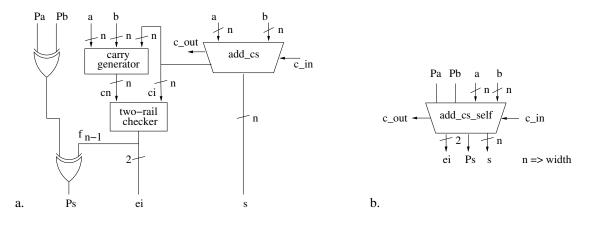

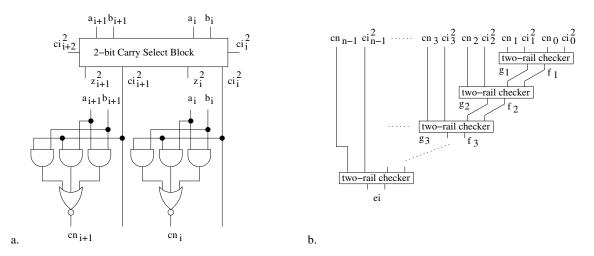

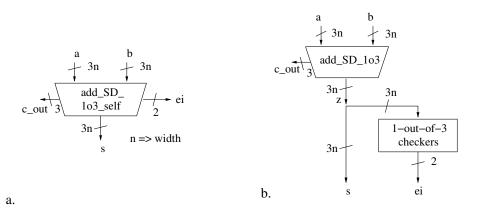

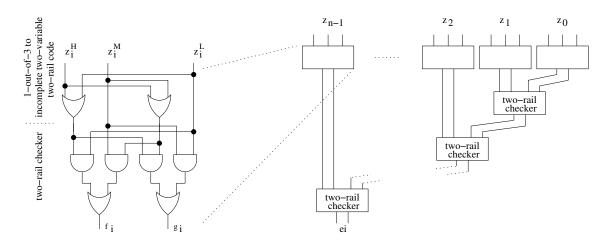

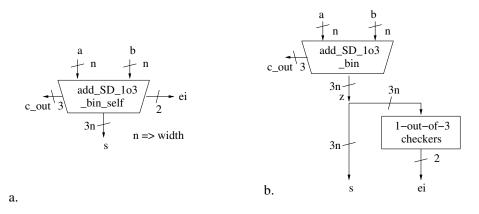

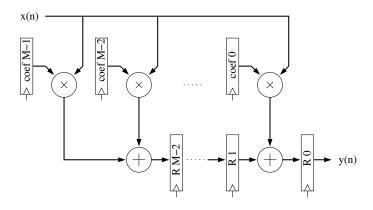

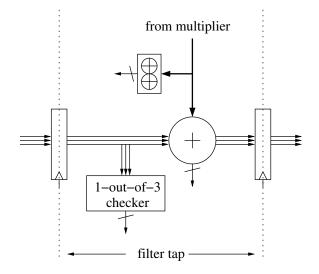

La duplication est basée sur la réplication du circuit pour la détection des différences entre les résultats [9]. La sortie du deuxième circuit est complémentaire à celle du premier pour permettre l'utilisation d'un contrôleur double rail, envisageant aussi la détection des erreurs internes au contrôleur. Le surcoût matériel est plus que 100% mais la simplicité d'implémentation est un avantage de cette méthode. La Fig. 2 montre le schéma général de la duplication dans un circuit arithmétique.

La prédiction de parité et la duplication sont des méthodes auto-contrôlables, lesquelles signaleront l'occurrence d'une faute et déclencheront des actions de prise en compte de l'erreur, ayant un impact supplémentaire sur la performance.

FIG. 2 – Schéma générale de la duplication.

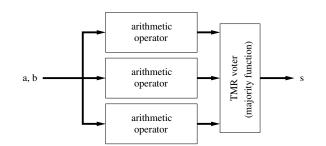

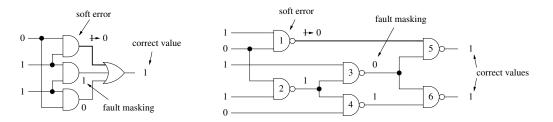

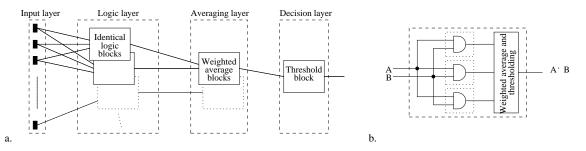

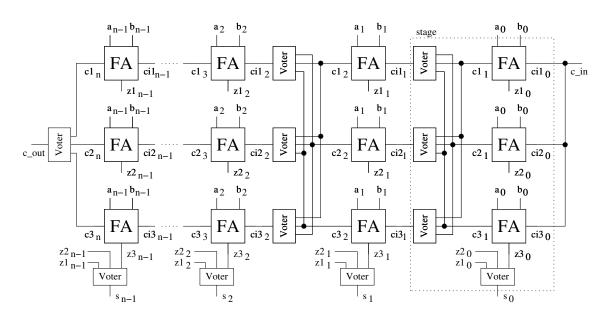

La troisième méthode implémentée est la redondance modulaire triple (TMR), qui consiste en l'utilisation de trois circuits identiques pour l'exécution de l'opération et la détermination du résultat par l'application de la fonction majorité sur les trois résultats [10]. Le schéma général de la TMR est illustré à la Fig. 3. Le problème avec la TMR est le surcoût matériel de plus de 200%, mais en étant une méthode de tolérance aux fautes basée sur le masquage d'erreurs, la TMR permet une opération continue du système en présence d'une faute, sans impact sur la performance (seulement le retard de l'arbitre). La fiabilité de la méthode est fortement dépendente de la fiabilité de l'arbitre.

Les méthodes implémentées de tolérance aux fautes et d'auto-contrôle sont bien adaptées aux circuits d'applications critiques mais les surcoûts dérivés sont très élevés pour les circuits normaux et leur effectivité dans un environnement des fautes multiples n'est pas garanti. En considérant ces limitations, plusieurs études ont proposé l'application partielle de ces méthodes, comme une duplication des cellules plus importantes, ou la TMR d'une partie restreinte du circuit, mais aussi l'application des méthodes de prévention de fautes

FIG. 3 – Schéma général de la redondance modulaire triple.

(durcissement des composants) [11, 12, 13, 14]. Ces méthodes sont basées sur une duplication des cellules critiques ou la redondance locale, avec l'utilisation des transistors plus robustes, moins sensibles aux variations des courants transitoires.

Ces méthodes ont des surcoûts beaucoup plus souples dans les circuits, et ces surcoûts peuvent être adaptés aux contraintes de conception. Le problème principal de ces méthodologies est la complexité de l'analyse nécessaire pour déterminer les composants critiques et sa nature extrinsèque au flot de conception. L'utilisation d'une méthodologie d'analyse de fiabilité intégrée dans le flot de conception permettrait la prise en compte en amont des effets des méthodes de durcissement et le management automatique de la fiabilité par les outils, en utilisant des bibliothèques de composants avec différents niveaux de durcissement.

La bibliothèque de composants robustes est composée d'additionneurs du type *ripple* carry, carry-select, carry lookahead et signed digit, et un multiplieur du type Booth. Tous les circuits ont été implémentés en version auto-contrôlable et quelques circuits en version TMR. Les circuits ont été décrits en langage VHDL et ont été synthétisés en technologie 130-nm pour permettre l'étude de la topologie résultante. Les circuits générés par cette méthode de conception sont la base pour l'étude de fiabilité et d'évaluation des méthodes de prévention de fautes.

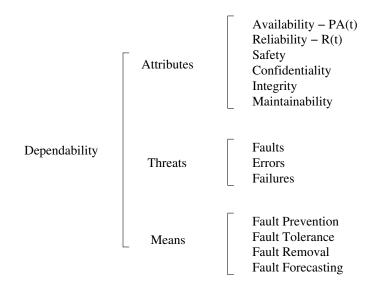

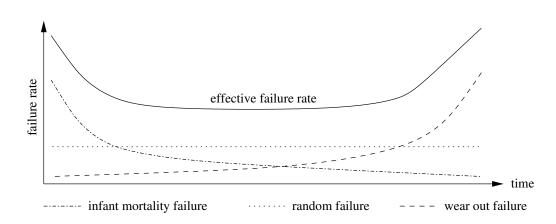

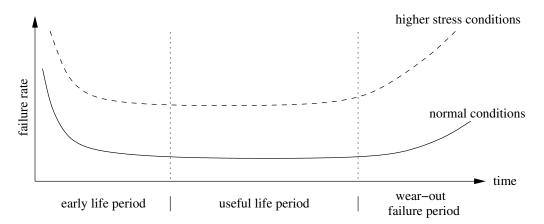

### L'Analyse de la fiabilité

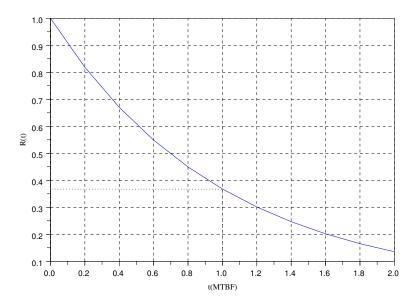

La fiabilité (R) est un attribut de la sûreté de fonctionnement et correspond à la probabilité de fonctionnement d'un composant ou système, pendant une durée déterminée. La fiabilité est associée au taux de défaillance  $(\lambda)$  d'un composant, une mesure obtenue par des essais avec un lot de ces composants, sous différentes conditions d'opérations, pour permettre la définition d'un modèle de fiabilité plus précis [15]. Le taux de défaillance des composants intégrés est caractérisé par la "courbe en baignoire", qui est en fait la composition de trois courbes différentes, représentant les taux de défaillance initial, aléatoire et du au vieillissement. Les composants intégrés ont un taux de défaillance défini en FIT (*failures in time*), qui correspond au nombre de défaillances dans une période de  $10^9$  heures. Une autre métrique du taux de défaillance est le temps moyen entre pannes  $(1/\lambda)$  ou MTBF (*mean-time-between-failures*). L'équation 3 montre la fiabilité comme une fonction du taux de défaillance.

$$R(t) = e^{-\lambda t} \tag{3}$$

La fiabilité étudiée dans le présent travail concerne la fiabilité du signal, qui est associée au taux de défaillance aléatoire. La fiabilité du signal correspond à la probabilité d'occurrence d'une valeur correcte à la sortie du circuit, en considérant une probabilité donnée d'occurrence de fautes. La probabilité d'un résultat correct en présence de faute est une fonction de la capacité de masquage de fautes du circuit, ce qui peut être d'origine logique, électrique ou temporelle. La présente étude concerne plus spécifiquement la modélisation de la fiabilité du signal due au masquage logique, dépendante de la topologie du circuit.

Pour l'étude de la fiabilité du signal associée aux fautes transitoires, un modèle de faute d'inversion est utilisé, où une cellule ou porte logique en panne génère une valeur logique complémentaire à la valeur correcte. Chaque cellule dans un circuit a une probabilité d'erreur, et la fiabilité du circuit doit être calculée comme une fonction de la fiabilité de ses cellules et de la structure logique du circuit. Ce calcul a une complexité exponentielle par rapport au nombre d'entrées et sorties du circuit et des solutions approximatives sont nécessaires.

Trois méthodes d'estimation de la fiabilité ont été implémentées dans le présent travail, la méthode d'analyse de fiabilité par le modèle des matrices de transfert probabilistes (PTM), le modèle probabiliste binomial (PBR) et le modèle de la probabilité du signal (SPR). Ces méthodes sont présentées dans les sections qui suivent.

#### Le modèle des matrices de transfert probabilistes

La première méthode a être implémentée est basée sur le modèle des matrices de transfert probabilistes (PTM). Ce choix est du à la possibilité d'application directe de cette méthode, qui utilise des opérations matricielles courantes et qui permet la modélisation individuelle des portes logiques. Dans la proposition originelle de la méthode il n'y avait pas d'interface avec les outils de synthèse et nous voudrions exploiter cette possibilité dans l'implémentation courante.

La PTM a été introduite dans les travaux de Patel et Krishnaswamy [16, 17, 18]. L'idée principale du modèle est de déterminer une matrice de probabilité d'occurrence d'une sortie par rapport aux probabilités des entrées. Cette matrice de corrélation entre entrées et sorties est appelée PTM. Elle est déterminée par la composition de la fiabilité des portes du circuit et sa topologie. La PTM peut être utilisée pour le calcul de la fiabilité du signal du circuit, en prenant en compte l'occurrence de fautes multiples.

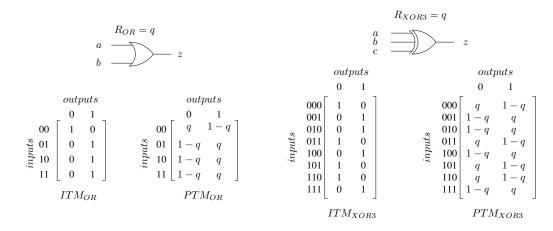

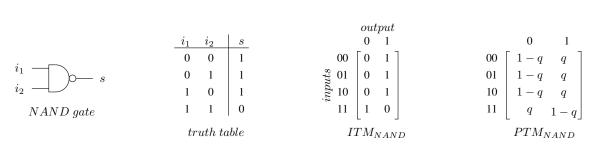

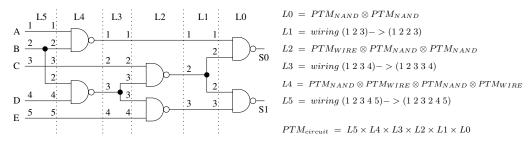

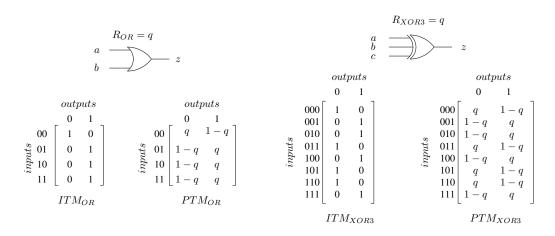

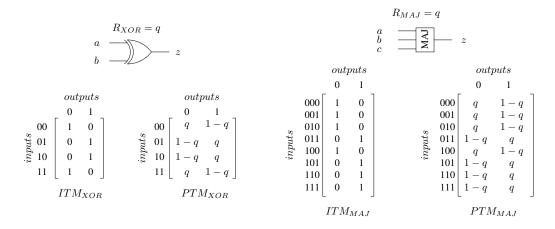

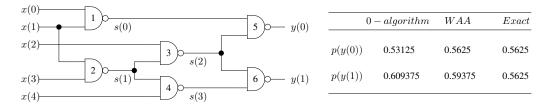

La PTM d'un circuit est une matrice de dimension  $2^n \times 2^m$ , où *n* est le nombre d'entrées et *m* est le nombre de sorties. La PTM d'une porte logique peut être définie à partir de sa table de vérité, aussi comme sa matrice de transfert idéale (ITM), qui correspond au modèle de fonctionnement sans faute de la porte. La figure 4 présente la PTM et l'ITM de deux portes logiques.

Comme montré dans la figure, les matrices représentent la probabilité d'occurrence d'entrées et sorties, et dans le cas de l'ITM, la probabilité est toujours 100% ou 0%. Les variables q et 1 - q représentent respectivement la fiabilité et la probabilité d'erreur de la porte.

La détermination de la PTM d'un circuit est effectuée par la combinaison des PTMs des portes et de l'ITM des connexions. Le circuit doit être organisé par niveaux et la PTM d'un niveau est calculé par le tenseur des PTMs des composants du niveau. En multipliant les PTMs des différents niveaux, la PTM du circuit est déterminé. Les figures 5 et 6 montrent le calcul de la PTM d'un circuit simple, où  $\bar{q} = 1 - q$ .

Après le calcul de la PTM du circuit, sa fiabilité peut être déterminée à l'aide de l'ITM du circuit, en calculant la somme des probabilités de la PTM qui correspondent aux positions de probabilité 1 dans l'ITM, comme exprimé en (4), où I est l'ITM, p(j|i) est la

FIG. 4 – Exemple de modélisation PTM et ITM des portes logiques.

Level 1 (L1) Level 2 (L2)

A

B

C

PTM L1 = PTM AND

$$\otimes$$

PTM NOT =  $\begin{bmatrix} \bar{q} & q \\ q & \bar{q} \end{bmatrix}$  PTM AND =  $\begin{bmatrix} q & \bar{q} \\ q & \bar{q} \\ q & \bar{q} \end{bmatrix}$  PTM NOT =  $\begin{bmatrix} \bar{q} & q \\ q & \bar{q} \\ q & \bar{q} \end{bmatrix}$  PTM NOT =  $\begin{bmatrix} \bar{q} & q \\ q & \bar{q} \\ q & \bar{q} \end{bmatrix}$  PTM NOT =  $\begin{bmatrix} \bar{q} & q \\ q & \bar{q} \\ q & \bar{q} \end{bmatrix}$   $\bar{q} \cdot \begin{bmatrix} \bar{q} & q \\ q & \bar{q} \end{bmatrix}$   $\bar{q} \cdot \begin{bmatrix} \bar{q} & q \\ q & \bar{q} \end{bmatrix}$  =  $\begin{bmatrix} \bar{q} & q & \bar{q} \\ q & \bar{q} \\ q & \bar{q} & \bar{q} \\ \bar{q} & \bar{q} & \bar{q} & \bar{q} \\ \bar{q} & \bar{q} & \bar{q} & \bar{q} \\ \bar{q} & \bar{q} & \bar{q} \end{bmatrix}$  =  $\begin{bmatrix} \bar{q} & q & \bar{q} \\ \bar{q} & \bar{q} \\ q & \bar{q} & \bar{q} & \bar{q} \\ \bar{q} & \bar{q} & \bar{q} \\ \bar$

FIG. 5 – Calcul de la PTM d'un niveau de circuit.

$$PTM_{CIR} = PTM_{L1} \cdot PTM_{NOR} = \begin{bmatrix} 2\bar{q}^2q + \bar{q}q^2 + q^3 & \bar{q}^2q + 2\bar{q}q^2 + \bar{q}^3 \\ \bar{q}^2q + 3\bar{q}q^2 & 2\bar{q}^2q + \bar{q}^3 + q^3 \\ 2\bar{q}^2q + \bar{q}q^2 + q^3 & \bar{q}^2q + 2\bar{q}q^2 + \bar{q}^3 \\ \bar{q}^2q + 3\bar{q}q^2 & 2\bar{q}^2q + \bar{q}^3 + q^3 \\ 2\bar{q}^2q + \bar{q}q^2 + q^3 & \bar{q}^2q + 2\bar{q}q^2 + \bar{q}^3 \\ \bar{q}^2q + 3\bar{q}q^2 & 2\bar{q}^2q + \bar{q}^3 + q^3 \\ 2\bar{q}q^2 + \bar{q}^3 + q^3 & 3\bar{q}^2q + \bar{q}q^2 \\ 2\bar{q}q^2 + \bar{q}q^2 + q^3 & \bar{q}^2q + 2\bar{q}q^2 + \bar{q}^3 \end{bmatrix}$$

FIG. 6 – Détermination de la PTM du circuit.

probabilité d'occurrence d'une sortie j étant donnée l'entrée i. Cette expression est valable pour le cas où toutes les entrées ont la même probabilité d'occurrence

$$R(e) = 1/2^n \sum_{I(i,j)=1} p(j|i)$$

(4)

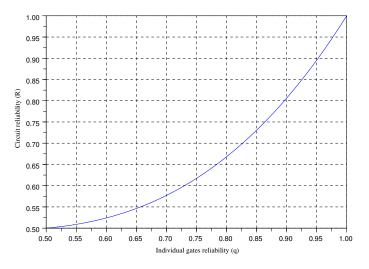

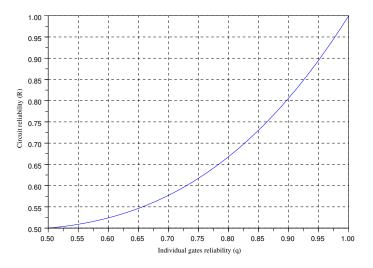

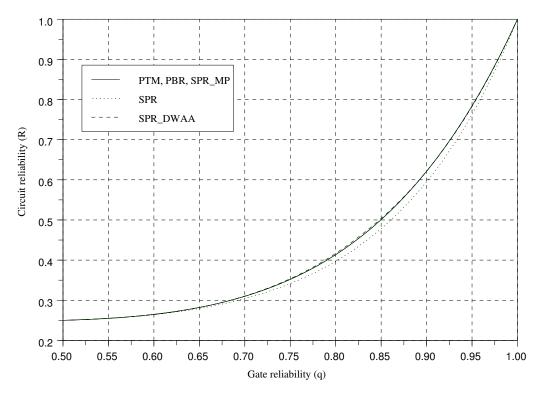

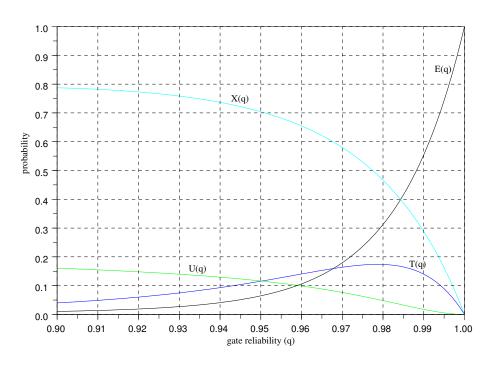

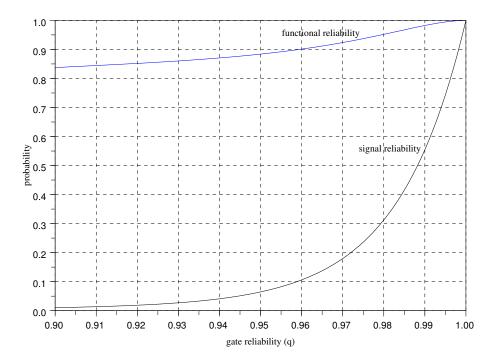

La figure 7 montre une analyse de fiabilité possible avec la méthode PTM, où la fiabilité du circuit est répresentée comme une fonction de la fiabilité de ses composants (q).

FIG. 7 – Courbe de fiabilité du circuit par rapport à la fiabilité de ses portes.

Malgré la simplicité associée a la méthode PTM, son utilisation est restreinte aux circuits de petite taille, à cause de sa complexité exponentielle par rapport au nombre d'entrées et sorties. La méthode fourni un résultat précis. Des outils nécessaires pour l'application de la PTM aux circuits issus de synthèse logique ont été implémentés et les résultats sont fournis dans le présent travail.

#### Le modèle probabiliste binomial

La méthode du modèle probabiliste binomial (PBR) est basée sur une analyse de la probabilité d'occurrence de fautes et leur masquage par rapport au taux de défaillance des cellules du circuit et leur nombre [19].

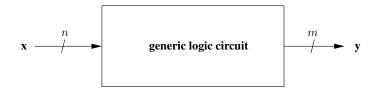

Si nous considérons que les portes d'un circuit ont une certaine probabilité de tomber en panne, la fiabilité R de ce circuit, vue comme une boîte noire, peut être déterminée comme en (5), où  $p(\vec{y} = correct | \vec{x}_i)$  représente la probabilité d'une sortie correcte étant donnée un vecteur d'entrée  $\vec{x}_i$  et sa probabilité d'occurrence  $p(\vec{x}_i)$ .

$$R = \sum_{i=0}^{2^{m}-1} p(\vec{y} = correct | \vec{x}_i) p(\vec{x}_i)$$

(5)

Pour modéliser la contribution de chaque porte dans la fiabilité totale, la probabilité de toutes les combinaisons d'entrées et vecteurs de fautes doit être déterminée. Soit  $\Gamma$ l'ensemble de toutes les portes du circuit (G portes), l'ensemble  $\phi \subseteq \Gamma$  des portes qui tombent en panne et l'ensemble  $\gamma \subseteq \Gamma$  des portes qui fonctionnent normalement. Dans ce cas, l'expression (6) modèle la fiabilité du circuit par rapport aux vecteurs d'entrées  $\vec{x}_i$  et de fautes  $\vec{f_j}$ . Le vecteur de fautes représente les portes en panne par une valeur 1 dans la position correspondante. La figure 8 illustre le vecteur de fautes.

$$R = \sum_{j=0}^{2^G - 1} \sum_{i=0}^{2^m - 1} p(\vec{y} = correct | \vec{x}_i, \vec{f}_j) p(\vec{x}_i) p(\vec{f}_j)$$

(6)

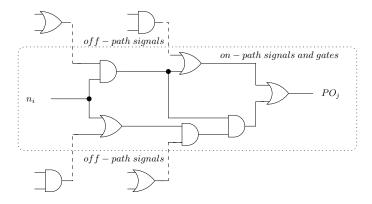

FIG. 8 – Circuit logique combinatoire générique.

L'expression générale de la fiabilité en (7) modèle le masquage de fautes pour les portes avec une fiabilité différente entre elles.

$$R = \sum_{j=0}^{2^{G}-1} \prod_{lc \in \gamma} q_{lc} \prod_{lf \in \phi} (1 - q_{lf}) \sum_{i=0}^{2^{m}-1} p(\vec{x}_i) \left( \overline{\vec{y}(\vec{x}_i, \vec{f_0}) \oplus \vec{y}(\vec{x}_i, \vec{f_j})} \right)$$

(7)

En considérant une probabilité égale des vecteurs d'entrées et les portes avec les mêmes fiabilités, l'expression (7) peut être ré-écrite comme en (8), en suivant un modèle probabiliste binomial, où k correspond au nombre des fautes simultanées.

$$R = \frac{1}{2^n} \sum_{k=0}^{G-1} (1-q)^k q^{G-k} \sum_{j \in \sigma} \sum_{i=0}^{2^i - 1} \left( \overline{\vec{y}(\vec{x}_i, \vec{f_0}) \oplus \vec{y}(\vec{x}_i, \vec{f_j})} \right)$$

(8)

L'expression est dépendante du nombre de masquages en présence de fautes, ce qui est représenté par la fonction XOR. Le nombre de masquage doit être déterminé par simulation ou émulation, ce qui a été implémenté pendant le présent travail. Les outils développés déterminent le taux de masquage (coefficients  $c_k$ ) des circuits cibles.

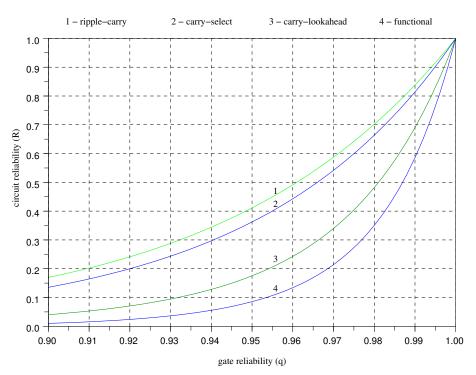

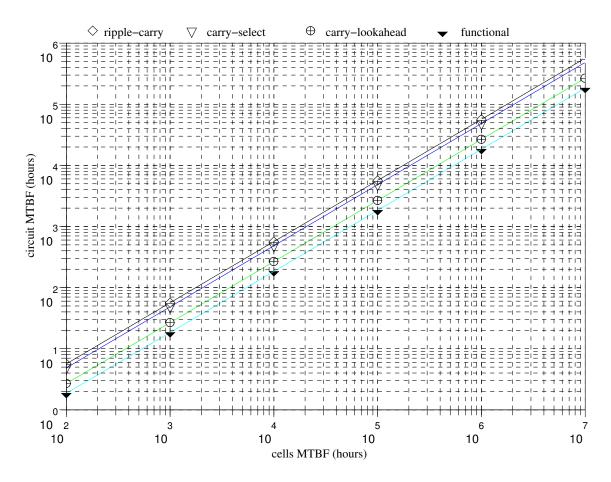

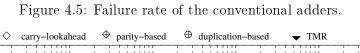

Le tableau 1 montre le taux de défaillance de 4 additionneurs différents de 4-bit, répresenté par rapport au taux de défaillance de ses cellules composantes, obtenu avec la méthode PBR et l'équation (3). Les additionneurs sont des types *ripple-carry*, *carry-select*, *carry-lookahead* et *signed digit*. Les résultats obtenus avec la PRB sont exacts, et prennent en compte l'occurrence de fautes multiples simultanées.

| Adder type | Individual cell $\mathrm{MTBF}_{i}(\mathrm{hours})$ |                     |                     |          |

|------------|-----------------------------------------------------|---------------------|---------------------|----------|

|            | $10^{12}$                                           | $10^{9}$            | $10^{6}$            | $10^{3}$ |

| RCA        | $1.09\cdot 10^{11}$                                 | $1.10 \cdot 10^{8}$ | $1.08 \cdot 10^{5}$ | 109      |

| CSA        | $1.03 \cdot 10^{11}$                                | $1.07 \cdot 10^{8}$ | $1.06 \cdot 10^{5}$ | 106      |

| CLA        | $0.68 \cdot 10^{11}$                                | $0.66 \cdot 10^{8}$ | $0.71 \cdot 10^{5}$ | 70       |

| SD         | $0.20 \cdot 10^{11}$                                | $0.18 \cdot 10^8$   | $0.26 \cdot 10^{5}$ | 21       |

TAB. 1 – MTBF des additionneurs 4-bit.

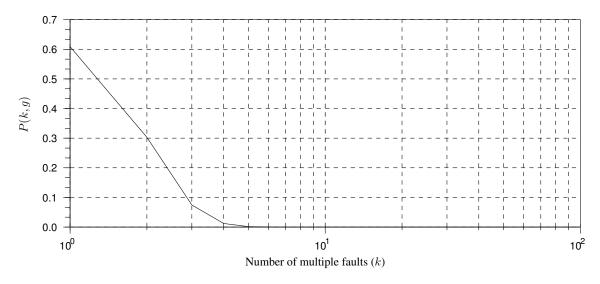

Etant donnée la complexité temporelle de la PBR, quelques approximations peuvent être faites pour permettre l'analyse des circuits plus importants. L'effet cumulatif des fautes dans la fiabilité du circuit permet l'application progressive de la méthode, par rapport au nombre des fautes simultanées considéré. La probabilité d'occurrence de fautes multiples est une fonction de la fiabilité et du nombre des cellules dans le circuit, régi par l'expression en (9).

$$P(k,G) = (C_k^G)q^{G-k}(1-q)^k$$

(9)

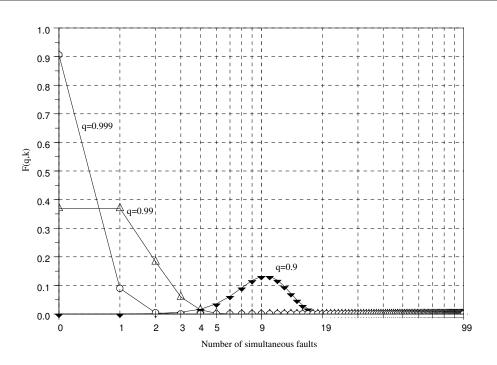

Si nous considérons que la fiabilité q des cellules est connue en avance, les coefficients  $c_k$ nécessaires pour un résultat avec une tolérance donnée peuvent être déterminés à travers cette expression. La Fig. 9 montre P(k, G) pour un circuit composé de 100 cellules logiques, où la fiabilité de chaque cellule est q = 0.995. Dans ce cas, pour déterminer la fiabilité avec un erreur de moins de 1% il suffit d'utiliser les coefficients  $c_1$  à  $c_4$ , i.e., le coefficients de masquage de fautes pour un nombre de fautes simultanées entre 1 et 4.

FIG. 9 – Probabilité d'occurrence de fautes dans un circuit avec 100 cellules (q = 0,995).

Une deuxième approximation peut être appliquée, en remplaçant la simulation exhaustive par une simulation pseudo-aléatoire, avec une durée déterminée. Dans ce cas, l'expression de fiabilité doit être ré-écrite comme en (10), où  $N_x$  est le nombre d'entrées appliquées et  $N_f$  le nombre de vecteurs de fautes du type  $\vec{f_k}$ .

$$R = \sum_{k=0}^{N_k-1} C_k^G (1-q)^k q^{G-k} \frac{\sum_{j=0}^{N_f-1} \sum_{i=0}^{N_x-1} \left( \overline{\vec{y}(\vec{x}_i, \vec{f}_0) \oplus \vec{y}(\vec{x}_i, \vec{f}_j)} \right)}{N_f N_x}$$

(10)

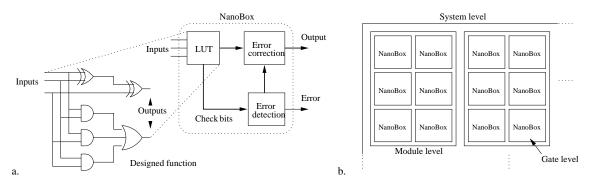

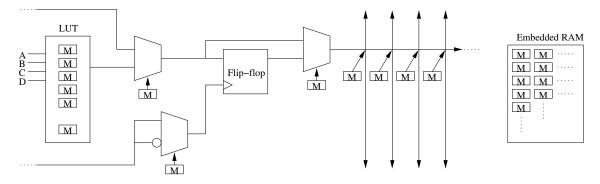

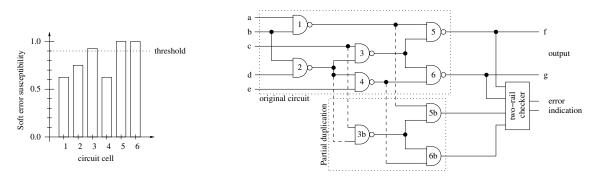

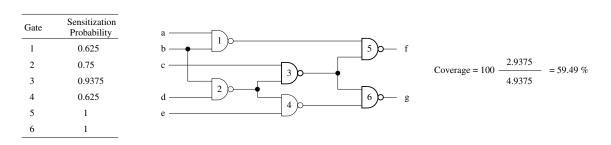

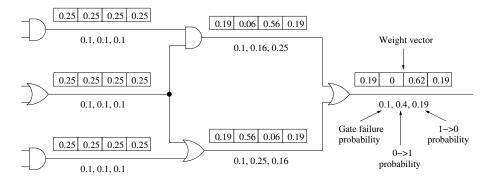

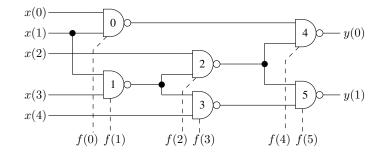

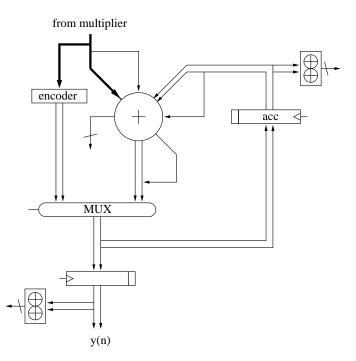

L'analyse de la fiabilité à travers le modèle probabiliste binomial nécessite une simulation fonctionnelle pour la détermination des coefficients de l'équation analytique. Pour permettre une implémentation générique et automatique du *testbench* des circuits logiques, l'outil d'analyse génère une version modifiée du circuit cible, en ajoutant des points d'injection de faute dans les sorties des cellules du circuit. Le testbench consiste à comparer les sorties des circuits sans et avec fautes pour déterminer le masquage des résultats et générer l'équation analytique de fiabilité. En s'appuyant sur la capacité reconfigurable des FPGA, et en considérant la taille des circuits cibles, la simulation fonctionnelle peut être remplacée par une émulation des circuits, avec un gain intéressant en terme de performance. Cette possibilité a été exploitée dans le présent travail. La figure 10 montre le schéma implémenté pour l'émulation des circuits en présence de fautes.

FIG. 10 – Schéma d'émulation pour l'analyse PBR.

La méthode PBR permet l'obtention de résultats très précis dans le calcul de la fiabilité des circuits, étant limitée par le temps disponible pour la simulation/émulation des fautes.

#### Le modèle de la probabilité du signal

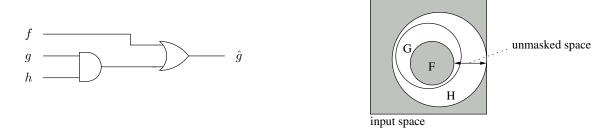

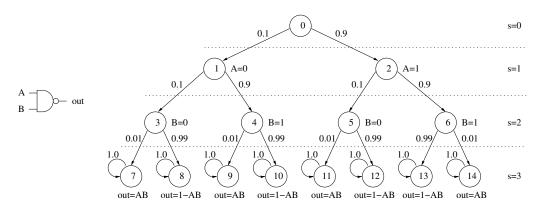

L'analyse de la fiabilité par la probabilité du signal est basée sur l'observabilité des fautes à la sortie du circuit, ce qui correspond à la probabilité de masquage de ces fautes par les entrées ou par l'effet cumulatif des fautes concurrentes [20, 21].

La probabilité de masquage d'une faute à l'entrée d'une porte logique est une fonction de la probabilité d'occurrence de quelques combinaisons des autres entrées. Dans ce cas, la détermination de la probabilité des signaux dans un circuit en présence de fautes permettrait la détermination de sa fiabilité à travers une comparaison avec la probabilité des signaux du circuit sans faute. Au lieu de faire une analyse de la probabilité des signaux pour chaque faute possible, une analyse directe de la fiabilité des signaux permettrait la prise en compte de l'effet cumulatif des fautes multiples. En considérant la fiabilité d'une cellule logique, la fiabilité du signal à la sortie est une fonction de la fiabilité de la cellule et de la fiabilité des signaux d'entrée. Alors, la propagation de la fiabilité de chaque signal à travers le circuit logique permet le calcul de la fiabilité des signaux à la sortie du circuit, en prenant en compte sa topologie. La fiabilité conjointe des signaux à la sortie du circuit correspond à la fiabilité du signal pour ce circuit.

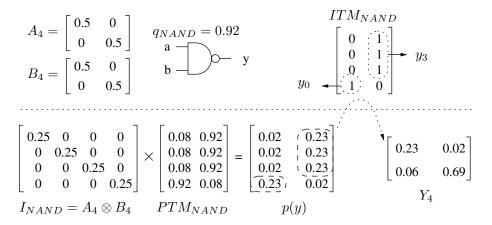

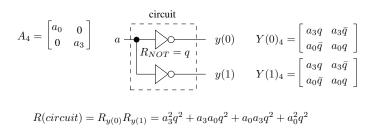

Considérons une porte logique quelconque, dont la fiabilité de fonctionnement peut être représentée par sa matrice de transfert probabiliste (PTM). La fonction logique est représentée par sa matrice de transfert idéale (ITM). L'ITM et la PTM expriment la probabilité d'occurrence des paires entrées/sorties dans une cellule logique [16, 17]. La Fig. 11 montre la PTM et l'ITM d'une porte NAND, avec une fiabilité q, et une probabilité d'erreur (1 - q).

Considérons la probabilité d'un signal binaire comme étant représenté par 4 états possibles, à savoir, 0 correct, 0 incorrect, 1 correct et 1 incorrect. En organisant ces probabilités dans un format matriciel  $2 \times 2$ , la probabilité d'occurrence de chaque état d'un signal peut être écrite comme  $signal_0$  (0 correct),  $signal_1$  (1 incorrect),  $signal_2$  (0 incorrect) et  $signal_3$ (1 correct), et la probabilité du signal dans cette forme matriciel peut être écrite comme  $SIGNAL_4$ . La Fig. 12 montre la représentation matriciel de la probabilité du signal.

La probabilité conjointe des signaux peut être déterminée par le produit tensoriel (ou produit de Kronecker) des signaux. La Fig. 13 montre le calcul de la probabilité conjointe

FIG. 11 – L'ITM et PTM d'une porte NAND.

$SIGNAL_4 = \begin{bmatrix} signal_0 & signal_1 \\ signal_2 & signal_3 \end{bmatrix}$

$P_{2\times 2}(signal) = \begin{bmatrix} P(signal = correct \ 0) & P(signal = incorrect \ 1) \\ P(signal = incorrect \ 0) & P(signal = correct \ 1) \end{bmatrix}$

FIG. 12 – Représentation matricielle de la probabilité du signal.

de deux signaux, a et b. Si a et b sont les signaux à l'entrée d'une porte logique, la matrice I représente toutes les probabilités à l'entrée de cette porte.

| т [     | $a_0$ | $a_1$                         | $b_0$ | $b_1$                                                                                                               | $\left[\begin{array}{c}a_0b_0\\a_0b_2\end{array}\right]$ | $a_0b_1 \\ a_0b_3$   | $a_1b_0 \\ a_1b_2$                             | $\begin{bmatrix} a_1b_1\\a_1b_3 \end{bmatrix}$ |

|---------|-------|-------------------------------|-------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------------------------------------------------|------------------------------------------------|

| $I_g =$ | $a_2$ | $a_3 \end{bmatrix}^{\otimes}$ | $b_2$ | $\begin{bmatrix} b_1 \\ b_3 \end{bmatrix} = \begin{bmatrix} a_0 b_0 \\ a_0 b_2 \\ a_2 b_0 \\ a_2 b_2 \end{bmatrix}$ | $a_2b_1 \\ a_2b_3$                                       | $a_3b_0$<br>$a_3b_2$ | $\begin{bmatrix} a_3b_1\\a_3b_3 \end{bmatrix}$ |                                                |

FIG. 13 – Calcul de la probabilité conjointe de deux signaux.

La fiabilité du signal à la sortie d'une cellule logique est la composition de la fiabilité de la cellule avec la fiabilité des signaux d'entrée, ce qui peut être déterminé par la multiplication de la probabilité conjointe des entrées (I) par la PTM de la cellule. Alors, la probabilité de la sortie y de la porte g est donnée par  $P(y) = I_g \otimes PTM_g$ . La matrice P(y) représente la probabilité d'occurrence des paires entrées/sortie de la porte g et en utilisant l'ITM de la porte, la probabilité  $Y_4$  du signal peut être déterminée, à travers les expressions 11 à 14, où 0, r ou 1, r correspondent à la colonne, ligne de l'ITM de la porte.

$$y_0 = \sum_{r=0}^{2^i - 1} P(y)_{[0,r]} ITM_{[0,r]}$$

(11)

$$y_1 = \sum_{r=0}^{2^i - 1} P(y)_{[1,r]} (1 - ITM_{[1,r]})$$

(12)

$$y_2 = \sum_{r=0}^{2^i - 1} P(y)_{[0,r]} (1 - ITM_{[0,r]})$$

(13)

$$y_3 = \sum_{r=0}^{2^i - 1} P(y)_{[1,r]} ITM_{[1,r]}$$

(14)

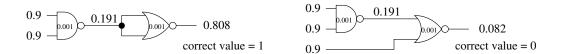

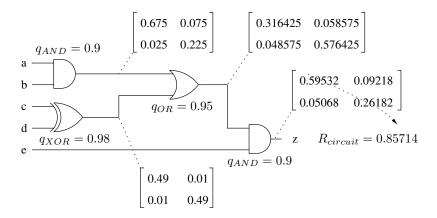

La Fig. 14 montre la détermination de la probabilité du signal à la sortie s d'une porte AND avec une fiabilité  $q_{AND} = 0.9$ . Le procédé de calcul de la probabilité du signal à la sortie est appelé **propagation** de la probabilité.

$$A_{4} = \begin{bmatrix} 0.5 & 0 \\ 0 & 0.5 \end{bmatrix} \qquad \begin{bmatrix} 0.25 & 0 & 0 & 0 \\ 0 & 0.25 & 0 & 0 \\ 0 & 0.25 & 0 \\ 0 & 0 & 0.25 \end{bmatrix} \times \begin{bmatrix} 0.9 & 0.1 \\ 0.9 & 0.1 \\ 0.9 & 0.1 \\ 0.1 & 0.9 \end{bmatrix} = \begin{bmatrix} 0.225 & 0.025 \\ 0.225 & 0.025 \\ 0.225 & 0.025 \\ 0.025 & 0.225 \end{bmatrix} \longrightarrow \begin{bmatrix} 0.675 & 0.075 \\ 0.025 & 0.225 \end{bmatrix}$$

FIG. 14 – Propagation des probabilités des signaux d'entrée.

La fiabilité d'un signal peut être déterminée directement par  $R(signal) = signal_0 + signal_3$  et la fiabilité du signal à la sortie d'un circuit logique correspond à la fiabilité du circuit. Pour un circuit avec plusieurs sorties, la fiabilité du circuit peut être déterminée par la multiplication de la fiabilité des sorties, comme montré à l'expression (15), où  $R_j$  correspond à la fiabilité de la sortie j.

$$R_{circuit} = \prod_{j=0}^{m-1} R_j \tag{15}$$

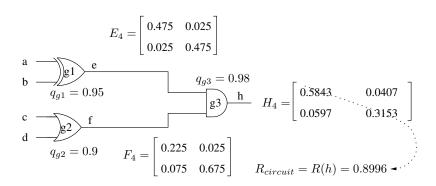

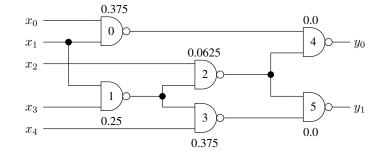

La Fig. 15 montre la détermination de la fiabilité d'un circuit à travers la propagation de la probabilité des signaux.

$$E_{4} = \begin{bmatrix} 0.475 & 0.025 \\ 0.025 & 0.475 \end{bmatrix}$$

$$P_{4}(inputs) = \begin{bmatrix} 0.5 & 0 \\ 0 & 0.5 \end{bmatrix}$$

$$e_{1} = \begin{bmatrix} 0.95 \\ 0 \end{bmatrix}$$

$$e_{2} = 0.98$$

$$G_{3} = \begin{bmatrix} 0.8843 \\ 0.5843 \\ 0.0597 \end{bmatrix}$$

$$H_{4} = \begin{bmatrix} 0.5843 \\ 0.0597 \\ 0.3153 \end{bmatrix}$$

$$R = 0.8996$$

FIG. 15 – Détermination de la fiabilité d'un circuit à travers la propagation des probabilités des signaux.

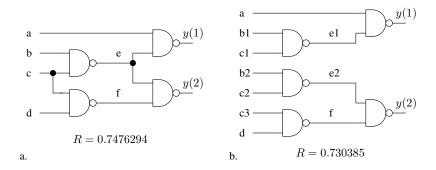

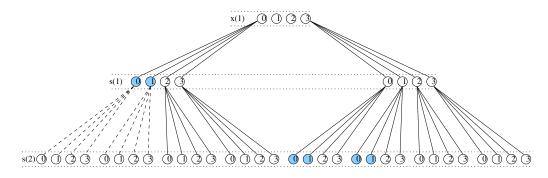

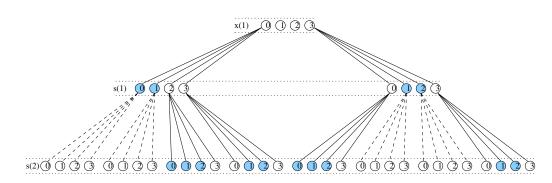

Le calcul de la probabilité des signaux dans un circuit logique est un problème de haute complexité, du type #P-complete [22, 23], dans les circuits avec des signaux reconvergents. Dans ce cas, le calcul de la probabilité des signaux à travers une seule propagation (single-pass) ne conduit pas à un résultat exact. Plusieurs heuristiques peuvent être imaginées pour corriger ou minimiser cet erreur et deux heuristiques ont été implémentées dans le présent travail, la propagation multi-pass et l'algorithme des moyennes pondérées dynamique (DWAA) [23].

L'algorithme multi-pass correspond à l'implémentation successive de la propagation de la probabilité des signaux en prenant en compte à chaque itération un seul état de la probabilité des signaux *reconvergents*. A la fin de chaque propagation, la fiabilité du circuit est calculée et accumulée aux valeurs précédentes, comme montre l'équation (16), où k est le nombre des signaux *reconvergents*, et s l'état de chaque signal.

$$R = \sum_{j=1}^{k} \sum_{s=0}^{3} R(j * s)$$

(16)

La complexité de calcul pour l'algorithme multi-pass est exponentielle par rapport au nombre des signaux *reconvergents* du circuit, mais des échanges entre précision et temps de calcul sont possibles. La possibilité d'un choix explicite des signaux *reconvergents* à prendre en compte dans le calcul de l'algorithme multi-pass permet le choix entre précision et temps de calcul.

L'algorithme des moyennes pondérées dynamique est une heuristique qui exécute une approximation successive des probabilités des signaux. Cette heuristique a une complexité linéaire par rapport au nombre des signaux *reconvergents* et le nombre des portes logiques dans le circuit.

L'algorithme DWAA boucle la propagation des probabilités en remplaçant à chaque itération la probabilité d'un état du signal *reconvergent* par 1 et 0, successivement, et en effectuant la correction de la probabilité des signaux dépendants par rapport aux déviations des probabilités. L'algorithme débute par le calcul des probabilités de tous le signaux selon l'algorithme de propagation simple (algorithme-0). Après, les probabilités des signaux *reconvergents* (f) sont mis successivement à la valeur **1** et **0**, et des nouvelles valeurs de probabilité sont calculées pour les signaux j, dépendants de f, d'après l'expression (17).

$$p(j|f) = p(j|f=0)p(f=0) + p(j|f=1)p(f=1)$$

(17)

La déviation de la probabilité par rapport au signal *reconvergent* est calculée selon l'expression (18), où p(j,0) est la probabilité calculée par l'algorithme-0. Les valeurs des déviations sont accumulées pour permettre la pondération des corrections. L'expression (19) présente ce calcul, où t-1 représente les nombre de signaux *reconvergents* déjà calculés.

$$w_f(j) = |p(j|f) - p(j,0)|$$

(18)

$$w_s(j,t-1) = \sum_{k=1}^{t-1} w_k(j)$$

(19)

Finalement, la correction des probabilités est calculée selon l'expression (20).

$$p(j,t) = \frac{p(j,t-1)w_s(j,t-1) + p(j|f)w_f(j)}{w_s(j,t-1) + w_f(j)}$$

(20)

A chaque itération de l'algorithme, les nouvelles probabilités sont calculées, et aussi la fiabilité, qui est corrigée par des expressions similaires à celles présentées. L'algorithme DWAA demande un ordonnancement des signaux par dépendance.

#### Résultats

Les outils d'analyse de fiabilité selon les modèles proposés dans le présent travail ont été implémentés en langage C. Ces outils permettent l'analyse des circuits décrits en langage VHDL ou Verilog, générés par les outils de synthèse, et calculent leur fiabilité du signal, en générant des fichiers de données au format Scilab, pour permettre la visualisation et le traitement des résultats. Ces mêmes outils peuvent être modifiés pour permettre la communication de la valeur de fiabilité directement à l'outil de synthèse pour une synthèse dirigée vers la fiabilité.

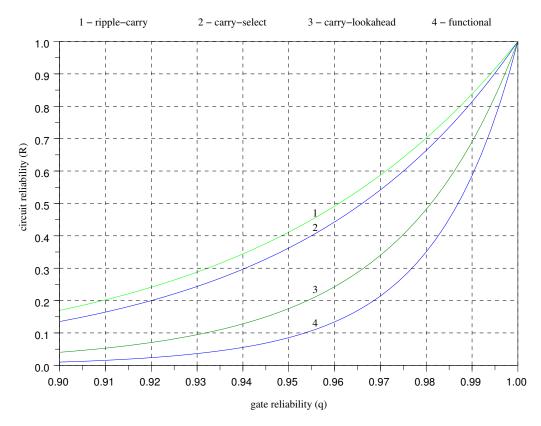

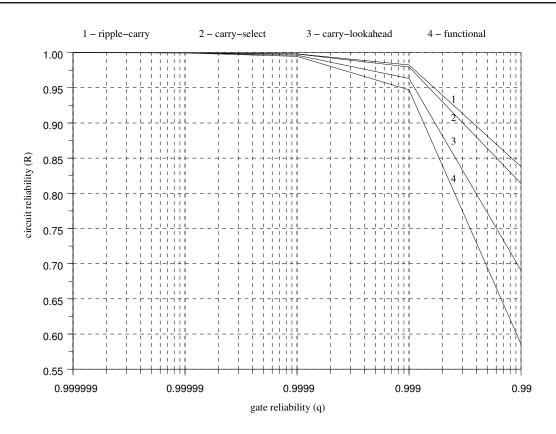

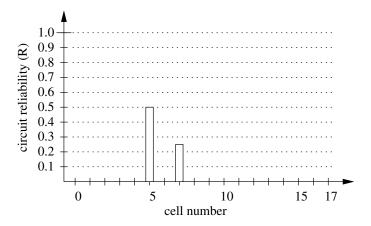

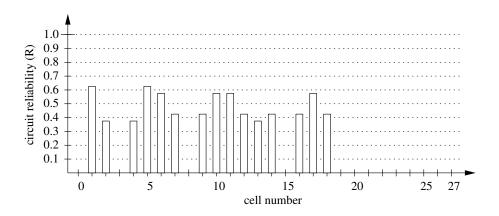

Les outils d'analyses ont été utilisés dans l'évaluation des circuits tolérants aux pannes et l'évaluation des méthodes de prévention de fautes. Plusieurs analyses ont étés possibles, comme le rapport entre la fiabilité des cellules d'un circuit et la fiabilité du circuit. La Fig. 16 montre ce rapport pour les circuits additionneurs classiques de la bibliothèque.

FIG. 16 – Fiabilité des additionneurs classiques 8-bits.

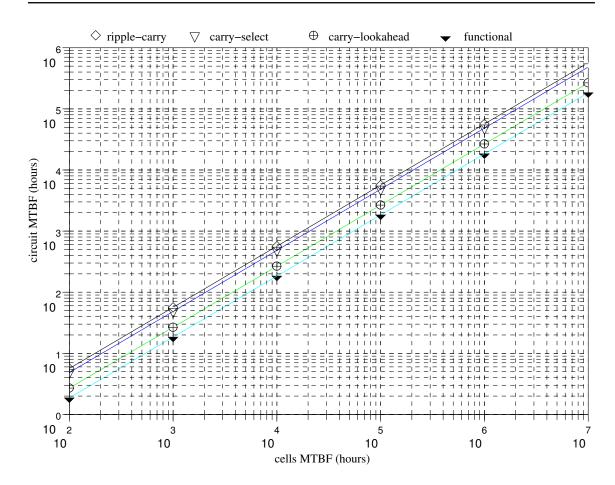

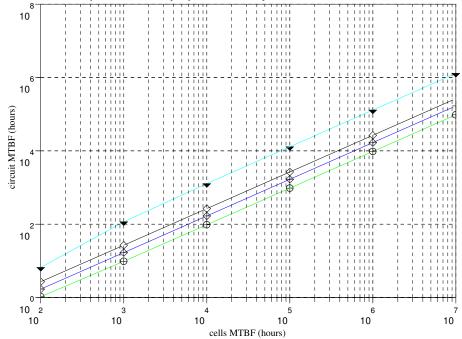

Une autre représentation possible pour les résultats obtenus est la comparaison du temps moyen entre fautes pour les différents circuits, ce qui peut être vu à la Fig.17.

D'autres types d'analyses possibles sont la détermination du taux d'erreurs, la détermination des cellules plus sensibles dans un circuit, l'amélioration de la fiabilité avec le durcissement des cellules spécifiques et le comportement des circuits tolérants aux fautes et auto-contrôlables en présence de fautes multiples.

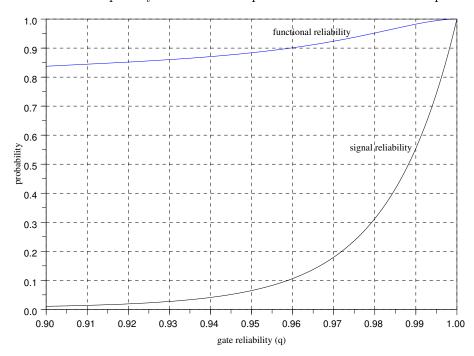

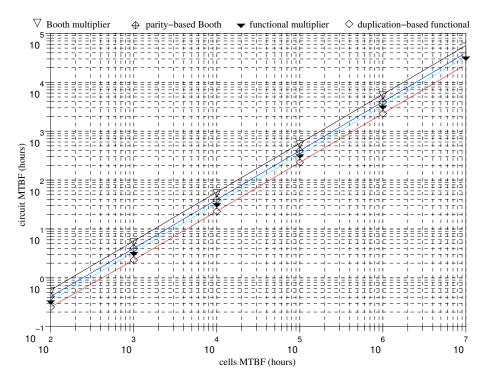

La Fig.18 montre le comportement de la fiabilité fonctionnelle et du signal dans un additionneur du type *carry-lookahead* auto-contrôlable, par rapport à la fiabilité de ses cellules. La fiabilité fonctionnelle est une mesure de la probabilité de détection de fautes du circuit.

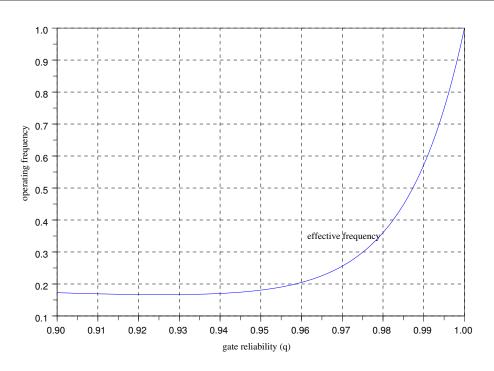

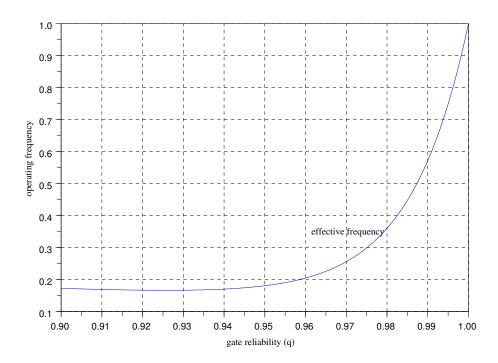

Même si la fiabilité fonctionnelle de l'additionneur est plus importante que la fiabilité du signal, les actions associées à la détection de fautes représentent une perte de performance pour le circuit. La Fig. 19 montre cette perte de performance qui peut être vue comme une réduction de la fréquence d'opération du circuit, ou une fréquence effective.

Le tableau 2 montre l'amélioration de la fiabilité de quelques circuits obtenue avec les méthodes de prévention de fautes. Dans ce cas, les cellules plus vulnérables des circuits ont été répliquées, et le tableau montre l'amélioration de la fiabilité (MTBF) et l'augmentation correspondante de la surface du circuit.

Tous ces types d'analyses ont été faits avec les modèles développés dans le présent

FIG. 17 – Temps moyen entre fautes pour les additionneurs classiques.

FIG. 18 – Fiabilité fonctionnel et du signal dans un additionneur du type carry-lookahead auto-contrôlable.

FIG. 19 – Fréquence effective de fonctionnement de l'additionneur auto-contrôlable.

| Circuit type         | Cell replication approach |          |  |

|----------------------|---------------------------|----------|--|

|                      | MTBF $(\%)$               | Area (%) |  |

| rca                  | 67.5                      | 61.1     |  |

| csa                  | 127                       | 47.5     |  |

| $_{\rm cla}$         | 143                       | 66.0     |  |

| fca                  | 94.0                      | 48.8     |  |

| $\operatorname{fcm}$ | 195                       | 64.3     |  |

| rca tmr              | 722                       | 9.93     |  |

TAB. 2 – Augmentation du MTBF et de la surface avec la réplication des cellules.

travail. Les résultats complets peuvent être vus dans le chapitre 4 de ce rapport.

### Conclusions

L'estimation de la fiabilité des circuits logiques pendant les étapes initiales de projet est un pas fondamental pour la conception des circuits nanométriques. La réduction prévue pour la fiabilité des composants intégrés obligera les concepteurs à l'implémentation des méthodes de durcissement des circuits, mais avec un surcoût très limité. Pour permettre l'application de ces méthodes d'une façon adaptée aux contraintes de projet, l'estimation de la fiabilité doit être intégrée dans le flot de conception. Plusieurs méthodes ont été proposées dans la littérature pour l'estimation de la fiabilité, mais étant donnée la complexité de l'analyse, chaque méthode a des limitations d'application, comme la restriction à une seule faute, la restriction à une seule sortie, la restriction à un seul chemin logique ou la restriction à un sous-ensemble des entrées.

Le présent travail a proposé deux méthodes d'estimation de la fiabilité "flexifles" dans le sens où elles permettent de jouer sur un compromis rapidité et précision. Cette flexibilité peut être utilisée de façon complémentaire tout au long de la conception. Ces méthodes prennent en compte l'occurrence de fautes multiples et sont alors adéquates pour l'étude des circuits nanométriques, plus susceptibles à ce type d'événement.

# Symbols and Abbreviations

| q                    | Gate reliability                               |

|----------------------|------------------------------------------------|

| $1-q,ar{q}$          | Gate unreliability                             |

| M, M(t)              | Maintainability                                |

| $\mu,\mu(t)$         | Repair rate                                    |

| $\lambda,\lambda(t)$ | Failure rate                                   |

| R, R(t)              | Reliability                                    |

| Y                    | Yield                                          |

| ADD                  | Algebraic decision diagram                     |

| ASIC                 | Application specific integrated circuit        |

| BDD                  | Binary decision diagram                        |

| BN                   | Bayesian network                               |

| BOX                  | Buried oxide                                   |

| $\mathbf{CCC}$       | Custom configurable computer                   |

| CAEN                 | Chemically assembled electronic nanotechnology |

| CED                  | Concurrent error detection                     |

| CEG                  | Circuit equivalent graph                       |

| CMOL                 | CMOS-nanowire-molecular structure              |

| CMOS                 | Complementary metal-oxide-semiconductor        |

| CMF                  | Common-mode failure                            |

| CMP                  | Chemical mechanical polishing                  |

| CNN                  | Cellular nonlinear network                     |

| CNT                  | Carbon nanotube                                |

| CPT                  | Conditional probability table                  |

| CWSP                 | Code word state preserving                     |

| DAG                  | Directed acyclic graph                         |

| DFS                  | Depth-first search                             |

| DFM                  | Design for manufacturability                   |

| DRAM                 | Dynamic random access memory                   |

| DSP                  | Digital signal processing                      |

| DTMC                 | Discrete-time Markov chain                     |

| DWAA                 | Dynamic weighted averaging algorithm           |

| DWC                  | Duplication with comparison                    |

|                      |                                                |

| $\mathrm{ECC}$       | Error-correcting code                              |

|----------------------|----------------------------------------------------|

| EDA                  | Electronic design automation                       |

| EDIF                 | Electronic design interchange format               |

| EPP                  | Error propagation probability                      |

| EVIS                 | Evidence pre-propagated importance sampling        |

| FASER                | Fast and accurate SER analysis                     |

| $\operatorname{FET}$ | Field-effect transistor                            |

| FIN                  | Fault injection network                            |

| $\operatorname{FIR}$ | Finite impulse response                            |

| $\operatorname{FIT}$ | Failures in time                                   |

| FPGA                 | Field programmable gate array                      |

| $\mathbf{FS}$        | Fault-secureness                                   |

| $\mathbf{FSM}$       | Finite-state machine                               |

| GA                   | Genetic algorithm                                  |

| GEG                  | Gate equivalent graph                              |

| HHE                  | Hybrid Hall effect                                 |

| IC                   | Integrated circuit                                 |

| ITRS                 | International technology roadmap of semiconductors |

| ISCAS                | International symposium of circuit and systems     |

| ITM                  | Ideal transfer matrix                              |

| LUT                  | Look-up table                                      |

| LIFE-DAG             | Logic induced fault encoded DAG                    |

| MAC                  | Multiply-accumulate                                |

| MDW                  | Moving domain wall                                 |

| MOS                  | Metal-oxide semiconductor                          |

| MOSFET               | Metal-oxide semiconductor FET                      |

| MPU                  | Microprocessor unit                                |

| MRE                  | Magneto resistive element                          |

| MRRNS                | Modulus replication residue number system          |

| MTBF                 | Mean-time-between-failures                         |

| MTTR                 | Mean-time-to-repair                                |

| MTBDD                | Multi-terminal BDD                                 |

| MXML                 | Micro-architectural XML                            |

| NEMS                 | Nano-electromechanical system                      |

| NMR                  | N-modular redundancy                               |

| NW                   | Nanowire                                           |

| OPC                  | Optical proximity correction                       |

| $\mathbf{PA}$        | Availability                                       |

| PBR                  | Probabilistic binomial reliability model           |

| PGM                  | Probabilistic gate model                           |

| PLA                  | Programmable logic array                           |

| PLS                  | Probabilistic logic sampling                       |

| PMC                  | Probabilistic model checking                       |

| $\mathbf{PSM}$       | Phase-shift masking                                |

| PTM                  | Probabilistic transfer matrix                      |

| RESO                  | Recomputing with shifted operands                  |

|-----------------------|----------------------------------------------------|

| $\operatorname{RET}$  | Resolution enhancement technique                   |

| RSFQ                  | Rapid single flux quantum                          |

| RTD                   | Resonant tunneling diode                           |

| RTT                   | Resonant tunneling transistor                      |

| SBD                   | Signed binary digit                                |

| $\operatorname{SCSL}$ | Selective clock skewed-logic                       |

| $\operatorname{SER}$  | Soft error rate                                    |

| SETRA                 | Scalable, extensible tool for reliability analysis |

| $SET_1$               | Single-electron transistor                         |

| $SET_2$               | Single event transient                             |

| SEU                   | Single event upset                                 |

| SIP                   | $\mathbf{System}	ext{-in-package}$                 |

| SOC                   | System-on-chip                                     |

| SOI                   | Silicon-on-insulator                               |

| SPICE                 | Simulation program with integrated circuit emp     |

| $\operatorname{SPR}$  | Signal probability reliability model               |

| SRAM                  | Static random access memory                        |

| $\mathrm{TMR}$        | Triple modular redundancy                          |

| UTB                   | Ultra-thin body                                    |

| VHDL                  | Very high speed integrated circuit hardware de     |

| VLSI                  | Very large scale integration                       |

| XML                   | Extensible markup language                         |

| WAA                   | Weighted averaging algorithm                       |

|                       |                                                    |

|                       |                                                    |

| QCA | Quantum | cellular | automata |

|-----|---------|----------|----------|

|     |         |          |          |

- phasis

- escription language

# Contents

| A  | c <mark>kno</mark> v         | wledgments                                 | 3                     |  |  |  |  |  |

|----|------------------------------|--------------------------------------------|-----------------------|--|--|--|--|--|

| A  | bstra                        | ct                                         | 5                     |  |  |  |  |  |

| Fr | French Summary               |                                            |                       |  |  |  |  |  |

| Sy | Symbols and Abbreviations 28 |                                            |                       |  |  |  |  |  |

| C  | onter                        | ıts                                        | 28                    |  |  |  |  |  |

| 1  | <b>Intr</b><br>1.1<br>1.2    | oduction<br>Motivations                    | <b>31</b><br>31<br>35 |  |  |  |  |  |

| 2  | Rel                          | Reliability in nanoelectronic technologies |                       |  |  |  |  |  |

|    | 2.1                          | Introduction                               | 37                    |  |  |  |  |  |

|    | 2.2                          | Basic concepts                             | 37                    |  |  |  |  |  |

|    | 2.3                          | Yield at nanometric dimensions             | 41                    |  |  |  |  |  |

|    | 2.4                          | Transient faults in logic                  | 45                    |  |  |  |  |  |

|    | 2.5                          | Fault-tolerant design                      | 51                    |  |  |  |  |  |

|    | 2.6                          | Fault prevention                           | 57                    |  |  |  |  |  |

|    | 2.7                          | Fault-tolerant library                     | 60                    |  |  |  |  |  |

|    | 2.8                          | Synthesis results                          | 62                    |  |  |  |  |  |

| 3  | Rel                          | ability analysis                           | 67                    |  |  |  |  |  |

|    | 3.1                          | Introduction                               | 67                    |  |  |  |  |  |

|    | 3.2                          | Prior work                                 | 67                    |  |  |  |  |  |

|    |                              | 3.2.1 Comments                             | 76                    |  |  |  |  |  |

|    | 3.3                          | Probabilistic transfer matrices            | 78                    |  |  |  |  |  |

|    | 3.4                          | The Probabilistic binomial model           | 82                    |  |  |  |  |  |

|    |                              | 3.4.1 Optimizing the model                 | 84                    |  |  |  |  |  |

|    |                              | 3.4.2 Evaluating self-checking circuits    | 85                    |  |  |  |  |  |

|    | 3.5                          | The Signal probability model               | 87                    |  |  |  |  |  |

|    |                              | 3.5.1 SPR DWAA                             | 95                    |  |  |  |  |  |

|    |                              | 3.5.2 SPR multi-pass                       | 99                    |  |  |  |  |  |

|    | 3.6                          | Proposed methodologies                     | 102                   |  |  |  |  |  |

| 4 | Res         | ults                            | 105   |

|---|-------------|---------------------------------|-------|

|   | 4.1         | Introduction                    | 105   |

|   | 4.2         | The analysis tools              | 105   |

|   | 4.3         | The signal reliability          | 110   |

|   | 4.4         | Fault prevention                | 119   |

|   | 4.5         | Comments                        | 121   |

| 5 | Con         | cluding remarks                 | 125   |

| Α | СМ          | OS and beyond                   | 129   |

|   | A.1         | CMOS evolution                  | 129   |

|   | A.2         | Emerging logic devices          | 134   |

|   | A.3         | Defect-tolerant approaches      | 137   |

|   | A.4         | Perspectives                    | 142   |

| в | Fau         | lt-tolerant library             | 147   |

|   | <b>B</b> .1 | Introduction                    | 147   |

|   | B.2         | Standard adders                 |       |

|   |             | B.2.1 Ripple-carry adder        |       |

|   |             | B.2.2 Carry-select adder        |       |

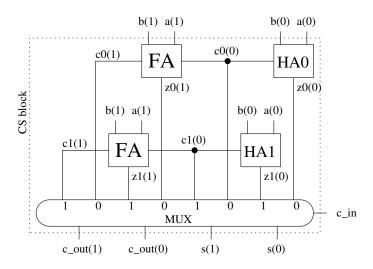

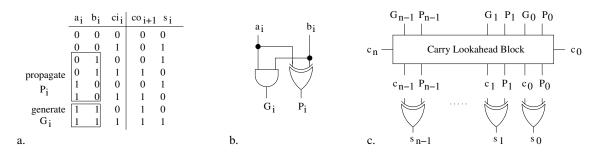

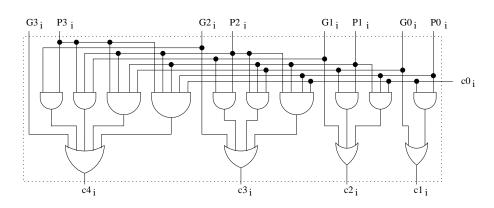

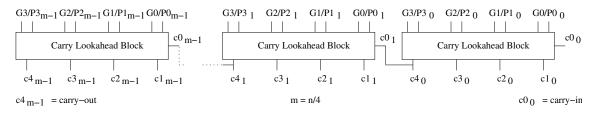

|   |             | B.2.3 Carry-lookahead adder     |       |

|   | <b>B.3</b>  | Carry-free adders               |       |

|   |             | B.3.1 Signed digit (radix-2)    |       |

|   |             | B.3.2 Signed digit (1-out-of-3) |       |

|   | <b>B.4</b>  | Booth multiplier                |       |

|   | <b>B</b> .5 | Concurrent error detection      |       |

|   | B.6         | Parity prediction               |       |

|   | B.7         | 1-out-of-3 checking             |       |

|   | B.8         | Triple modular redundancy       |       |

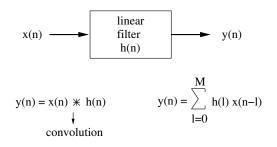

|   | B.9         | Digital filters                 |       |

|   |             | Synthesis results               |       |

|   | 2.10        |                                 | - • • |

### References

182

# Chapter 1

# Introduction

### 1.1 Motivations

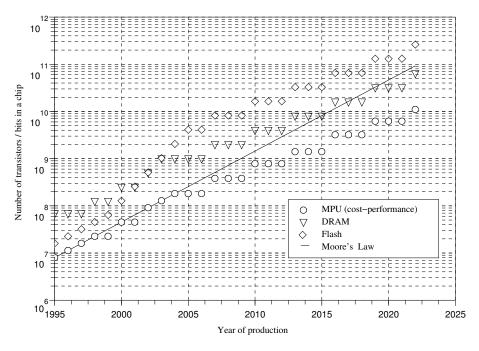

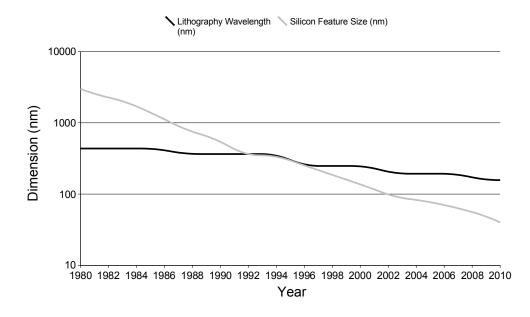

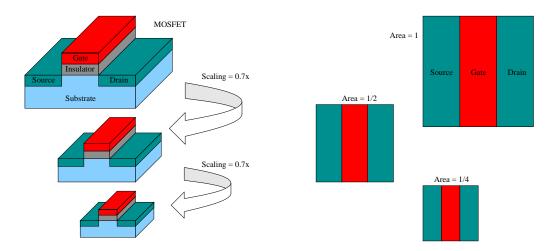

The continuous development of computers and electronic systems, perceived in the last decades, is a consequence of the evolution of integrated circuits (ICs) and its design and manufacturing processes. The basic principle behind this evolution is the reduction, or scaling, in the dimensions of the integrated structures. The ability to create smaller devices enables them to switch faster, makes them cheaper to manufacture and allows improvements in processing power. Fig. 1.1 shows the historical evolution of density in integrated circuits [24], allowed by technology scaling. The improvement in the number of transistors in an IC can be considered as an increase in circuits density, by considering that ICs area remains the same.

Figure 1.1: ICs density evolution.

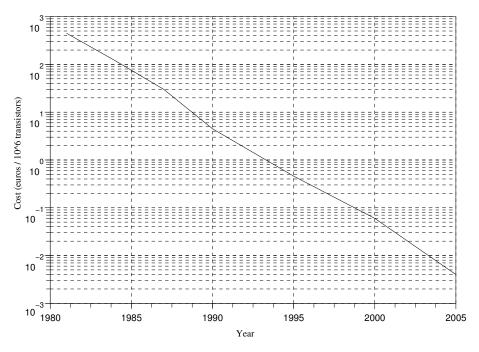

The economical effect of transistors scaling is the reduction of the manufacturing cost of integrated circuits, considering that the area of the circuits can be reduced and the cost is related with circuit's implementation area. Fig. 1.2 shows the historical evolution of the manufacturing cost of one million transistors.

Figure 1.2: Historical evolution of integrated circuits manufacturing cost.

The ICs evolution is responsible for developments in all of the human activities. The tradeoffs between speed, area and power, allowed by the CMOS (complementary metal oxide semiconductor) IC design style, make it adaptable to the constraints of different systems and applications. In telecommunications, for example, low power circuits and large scale integration were fundamental for the establishment of the mobile telephony, and only IC technology scaling can cope with the growing processing and storage demands for this market.

As device-scaling enters the nanometer dimensions, words with the prefix *nano* are becoming mainstream, like nanoscale, nanotechnology and nanoelectronics. The word nanotechnology was introduced in 1974 by Norio Tanigushi [25], and nowadays is used to describe a large field of research that includes nanomaterials, nanoelectronics and nanobiotechnology. In a generic way, nanotechnology refers to the study/manipulation of structures/systems with less than 100-nm in at least one dimension of the space, and that have properties related with their nanometric size. That's the case in the nanoelectronics research field, where the size of the devices (nanodevices or nanoscale devices) brings many challenges to designers and researchers, due to different properties and behaviors associated with their operation at deep-submicrom dimensions.

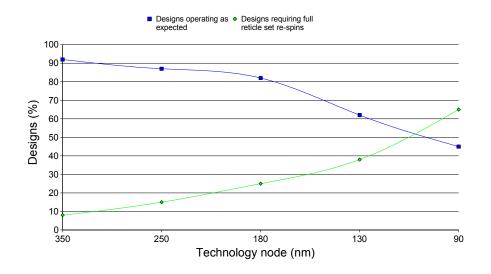

The historical evolution pace of ICs development is seriously menaced, and in some areas it has already slowed down, since the traditional scaling process is reaching the limits of materials, processes and profitability [26]. As devices scale down into nanometric dimensions, design and manufacturing are becoming highly complex, some of the qualities and properties of the materials involved are no longer valid, and some of the manufacturing steps aren't as reliable as desired.

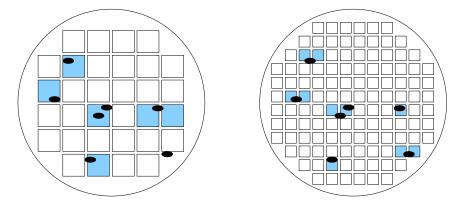

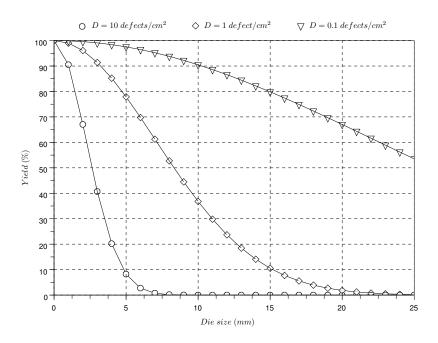

One of the main problems associated with nanoscale devices is the reduced yield expected from the future manufacturing processes [27, 28]. The variability in materials and

limited precision processes are translated into failures/imperfections in the circuits and wafers, leading to a reduction in the manufacturing yield. Another problem is the reliability of logic circuits related to intermittent and transient faults, that will play an increasing role in future technologies [29, 5, 30, 4], and may compromise the gains attained with device-scaling.

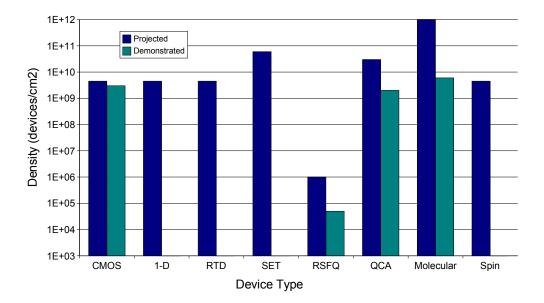

At this point, it's not possible to predict when the CMOS development will find its end, but some solutions and alternatives are being studied to guarantee a continuous evolution pace. Researchers are considering two general paths [31]: the first one is to extend CMOS scaling towards the 11-nm node predicted to arrive in 2022 [24], coping with performance, low power and standby power constraints; the second path is to develop new devices and architectures to replace or, most probably, complement the CMOS structures, aiming to maintain the evolution rates achieved in the last decades for performance, circuit density and power consumption. The areas of interest towards these two paths include emerging devices and materials, new architectures, new data representations and new computing models [32]. According to the ITRS association (International Technology Roadmap of Semiconductors), these two paths are defined as more Moore versus more than Moore.

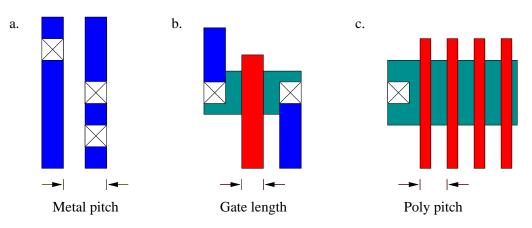

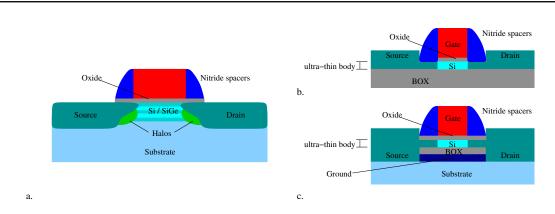

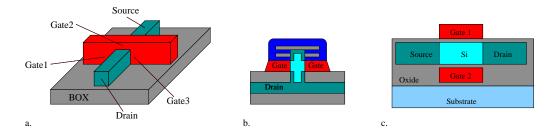

Following the first path means to change considerably the way MOS transistors are designed, by using modified and new materials in a similar structure or by changing the structure itself. These changes in the traditional MOS transistor aim to improve switching speed, reduce static current leakage, limit short channel effects and to improve electrostatic control of the gate over the channel. These advanced CMOS structures are discussed in more detail in appendix A.1 [2], along with some definitions of the scaling process and a brief description of CMOS devices evolution and perspectives.

The introduction of new materials and process steps in the fabrication of CMOS devices also impacts negatively on the yield and reliability of these integrated circuits, since new fabrication methods, design tools and device models must be developed, and high precision manufacturing and test will be necessary.

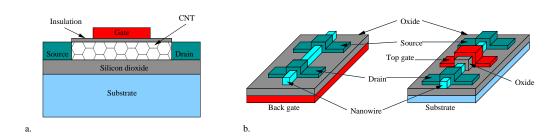

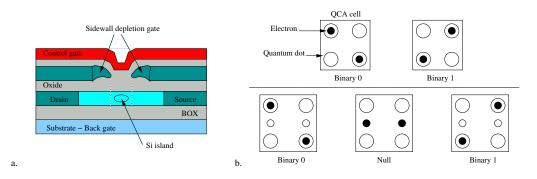

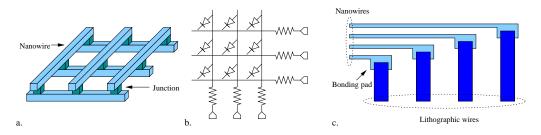

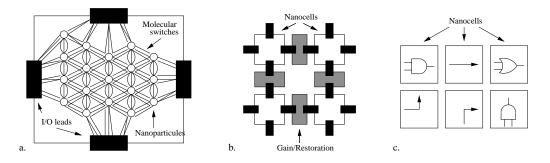

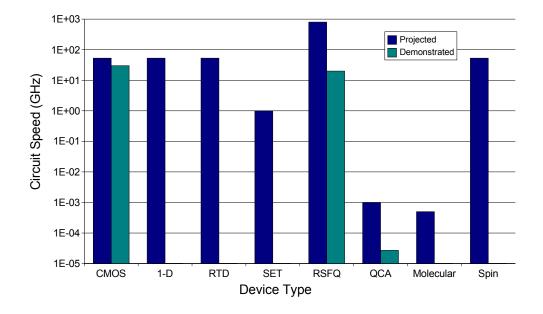

The second path represents the use of breakthrough solutions as the introduction of new device types and new system architectures. The new devices being researched are based on carbon nanotubes (CNT), nanowires, single electron transistors (SETs), spin transistors and molecular devices, among others. These new devices are not considered for direct replacement of the CMOS technology but primarily as complementary structures to be integrated along with CMOS ones, to extend the capacities of the later. A detailed presentation of these emerging logic devices is available in appendix A.2 [2], where their characteristics and perspectives are summarized.

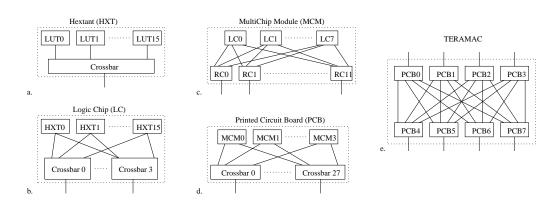

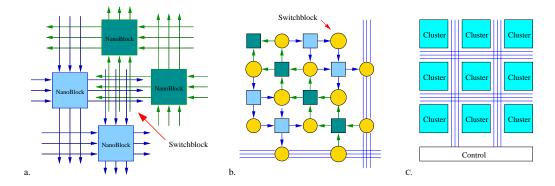

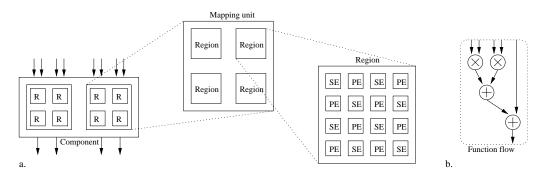

Along with these emerging logic devices, new circuit architectures have been proposed to explore alternative fabrication methodologies, data representation and computing models. These new architectures are mainly based on bottom-up assembly, on matrix topologies and non-volatile storage, in an FPGA-like organization targeted to a finer-grain level. These architectures promise low cost defect-tolerant fabrication and high device density and speed. Some examples of these new architectures and the concepts associated with bottom-up defect-tolerant approaches are presented in more detail in appendix A.3 [2].

Even if the proposed architectures are targeted to defect-tolerant approaches, the yield of these structures remain highly speculative and dependent on post-fabrication steps. On the side of the reliability of these emerging logic devices and architectures, their behavior remains unpredictable due to a lack of precise models, but considering parametric variations, reduced noise margins and the estimated circuit densities, a lower reliability must be expected. Considering this evolution scenario, defect and fault-tolerant design approaches are unavoidable work-arounds in the development of nanoscale systems. These approaches are primarily based on hardware redundancy and can be applied to all of the abstraction levels, from spare transistors to spare processing blocks, from circuit replication to data coding methods. Despite the existence of many studies and proposals to deal with defects and faults in integrated circuits, as the semiconductor industry reaches the nanoscale era, many of the solutions are becoming application-specific [33] and the suitability of a given solution must be determined or adapted according to the application constraints.

As mentioned before, fault-tolerant approaches, e.g., modular redundancy and concurrent error detection (CED), are being considered to improve the reliability of nanoscale circuits. Modular redundancy has been traditionally targeted to mission critical systems, i.e., medical, spatial and military ones, where dependability measures are the main design objectives and the related overheads can be accepted. Concurrent error detection schemes are normally targeted to sequential logic parts of the circuits as memory blocks, register banks and latches, where the resulting overheads can be kept at a reduced level. The use of CED schemes in combinational logic is not as straightforward as in sequential logic but the resulting overheads are reduced compared to modular redundancy.

The use of these fault-tolerant approaches in mainstream applications is constrained by several parameters, i.e., power dissipation, battery autonomy, cost, among others, dependent on the target application. Given these limitations, the application of modular redundancy or CED schemes may not be the best option to improve reliability, and alternative approaches have been proposed, as the implementation of partial replication or the hardening of individual cells. These approaches allow a fine-grain improvement in the reliability figures, limiting their impact on area, propagation time and power consumption.

Given the expected reduction of the reliability and the referred range of possible solutions, an early estimation of circuit's reliability is a valuable feature in the design flow, allowing the implementation of a reliability-aware automated design process. The main obstacle to this workflow is the complexity associated with reliability analysis, since computing the exact values of reliability measures is intractable for practical circuits. Many reliability analysis approaches can be found in the literature but most of these are not compatible or adequate to design flow integration. Despite the promising results obtained in the referenced works, they are generally restricted to single-fault, single-path or singleoutput. Furthermore, the referred approaches are not focused to the same analysis.