# Modulateur $\Sigma\Delta$ passe-haut et application dans la réception multistandards

Hasham Ahmed Khushk

# ► To cite this version:

Hasham Ahmed Khushk. Modulateur  $\Sigma\Delta$  passe-haut et application dans la réception multistandards. Electronique. Télécom ParisTech, 2009. Français. NNT: . pastel-00006055

# HAL Id: pastel-00006055 https://pastel.hal.science/pastel-00006055

Submitted on 10 May 2010  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Thèse

# présentée pour obtenir le grade de docteur

de l'Ecole Nationale Supérieure des Télécommunications

Spécialité : Electronique et Communications

# Hasham Ahmed KHUSHK

# Modulateur $\Sigma\Delta$ passe-haut et application dans la réception multistandards

Soutenance le 27 novembre 2009 devant le jury composé de

Philippe Benabes Dominique Dallet Patrick Garda Dominique Morche Patrick Loumeau Van Tam Nguyen Rapporteurs

Examinateurs

Directeurs de thèse

To my parents, my brothers and sisters.

#### Acknowledgements

This PhD has been performed in the auspices of group SIAM (Systèmes Intégrés Analogiques et Mixtes) of Department COMELEC (Communications & Électronique) of Telecom-ParisTech. The three years of graduate studies here have brought about a remarkable positive change in my attitude towards problem solving. I have learned the essence of research and development and at the same time I have developed a firm belief in the far reaching capabilities of mankind. This has been possible by working and interacting with a group of very intelligent, resourceful and kind personalities. Surely without them, my stay in Telecom-ParisTech would not be as fruitful.

First and foremost, I would like to express my most sincere gratitude to my immediate advisor, Doctor Van Tam Nguyen, who accepted me as his first doctoral candidate, showed confidence in me and gave me numerous advice in academics, research and career. He is a person of great scientific acumen and admirable human values. He was by my side throughout the three years and taught me how to find paths in the dark alleys of research. I extend my utmost thankfulness to my PhD director, Professor Patrick Loumeau for his guidance and encouragement. His experience and expertise in the subject are matchless. Having a highly diverse knowledge base, his suggestions were of immense importance. He was of great help in getting out of many complex circumstances. I take great pride in having worked with these two gentlemen, who are the specialists in the domain of data converters. I have learned a lot from them.

I am indebted to Hussein Fakhoury for his keen interest in my research and for the lengthy and productive discussions on the subject. His profound knowledge and extensive experience in the area of Analog IC Design coupled with his helping nature proved to be a treasure for me. Without his designed op-amps it would not have been possible to validate my modulator designs.

I am extremely grateful to the members of my jury who gave their consent to analyze and consequently validate my work. I feel honored that my work got approved by such well renowned specialists.

The moments spent with many peers is perhaps one of the best memories that I will take with me of my graduate studies. I have very much enjoyed being in the company of friends like Sumanto, Chadi, Farhan, Shivam, Mai, Denis, David, Francisco, Davi, Eric, Gutemberg, Alban, Pietro, Shahkar, Masood, Naveed, Khalil, Leonid, Fahad, Christophe, Nilda, Victoria, Krisztina, Elena, Catherine, Christine, Alexandra, Fatima, Wissam, Manel, Asma, Sami and the list goes on and on. I cherish the memories of my prolonged discussions with Chadi on scientific and philosophical topics, dinner plans with Babu(Sumanto), Farhan and Shivam, happy hour outings on fridays with Mai, Francisco and Davi.

I am most fortunate to have my family: my parents, my brothers and sisters. Their constant encouragement has pushed me to be the best that I can be. I must mention my father's telephonic lectures, which kept me motivated during these three years. I express my heartfelt appreciation of my brothers Zubair and Suhayb, who left no stone unturned right from my childhood to educate me. I am certain that this work has been a product of my family's love and support throughout my life.

#### Abstract

In high-pass (HP)  $\Delta\Sigma$  modulator the signal band is located at  $F_s/2$ , as opposed to dc for the traditional low-pass (LP)  $\Delta\Sigma$  modulator. Thus the noise shaping completely covers the low frequency noises such as 1/f noise and offset, and they have no effect on the performance of the HP modulator, which is not the case in a LP modulator. This inherent immunity against low frequency noises makes HP  $\Delta\Sigma$  modulator the preferred choice for noise-sensitive applications like Discrete-time Fs/2 receivers, bio-medical instrumentation, time-interleaved  $\Delta\Sigma$  architectures etc.

In this thesis, research has been carried out at various abstraction levels to optimize the HP  $\Delta\Sigma$  modulator operation. A top-down approach is adopted to achieve this objective. Beginning with the RF receiver architecture, the newly created Fs/2 receiver is selected for its enhanced compatibility with HP  $\Delta\Sigma$  modulator as compared to other state of the art receiver architectures namely zero-IF and low-IF receivers.

After the receiver topology, the next level of design i-e  $\Delta\Sigma$  modulator architecture is addressed. For this, a detailed study on state-of-the-art LP  $\Delta\Sigma$  modulator topologies is carried out, including various second-order topologies, higher-order single loop structures and MASH structures. We illustrate the latest generation of MASH structures which are free from digital cancellation filters and thus do not require digital calibration techniques to counter the mismatch between analog and digital components: Multi-stage closed loop (MSCL) and its enhanced version Generalized multi stage closed loop (GMSCL). The system-level modeling of various circuit level parameters of traditional second-order structure called Boser structure is illustrated. This study provides us with specifications for transistor level design.

Since the low-frequency noise problem poses challenges for the use of LP modulators in high-resolution applications, the contemporary topologies of LP modulators are converted for HP operation. We also propose a new second-order unity-STF architecture which is advantageous over other topologies in terms of complexity and performance. Behavioral modeling of the proposed structure's circuit-level parameters is carried out, which furnishes us with its specifications. These specifications are compared with other secondorder topologies. Since the second-order modulator is unable to provide the required performance, the cascaded or MASH structures for HP operation are explored and a novel technique to improve the traditional MASH topologies in terms of input dynamic range and highest-achieved SNR is proposed. The proposed single-stage second-order topology is used as an individual stage of this new cascade structure. But the mismatch and noise leakage problems still exist in this structure, so GMSCL topology is adopted for HP operation and its structure is modified to incorporate the proposed second-order topology. A recently proposed technique is applied on the quantizer to increase the dynamic range of the converter and to eliminate the need of Dynamic Element Matching (DEM) by diminishing DAC non-linearities. Detailed comparison of performance in the face of circuit non-idealities is performed between HP and LP modulators' various toplogies. It provides interesting information about various shortcomings and advantages of HP structures over LP ones.

The next level of design is the conception of a suitable switched-capacitor high-pass

filter for HP  $\Delta\Sigma$  modulator. The absence of a suitable HP filter has been the main bottle-neck in the realization of HP modulators. Traditional implementations of HP filters revolved around switched capacitor integrator to extract HP filter function. These were inadequate as they resulted in increased power consumption, surface area and reduced bandwidth. But a new scheme has been recently introduced, which resolves these issues and brings the performance of HP filter close to an integrator. We study and analyse three different types of switched-capacitor implementations of HP filter and compare them on the basis of consumption, noise immunity and speed and finally select the best one which has a performance comparable to that of switched-capacitor integrator.

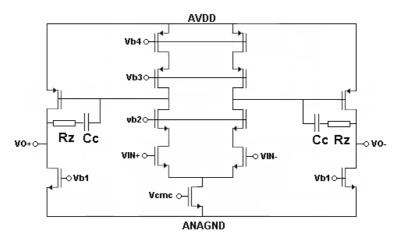

The final abstraction level is the transistor level design of the proposed GMSCL HP architecture, which is performed in 65nm CMOS process. Much attention is given to the design of operational transconductance amplifier since it is the major building block of high pass filters and is the most power consuming element. The target applications are UMTS with 3.84MHz conversion band at 80dB dynamic range and WiMAX with 25MHz bandwidth at 52dB dynamic range.

# Résumé Étendu

### Introduction

La prolifération des standards sans fil et la diminution de la taille des terminaux radio en même temps pousse vers la matérialisation du concept nouvellement créé de Software Defined Radio (SDR). Ce système de communication est prévu pour réaliser des terminaux radio multibande, multimode en définissant des fonctionnalités de la radio dans les logiciels [1]. De cette façon, le terminal radio est adapté aux différents protocoles et personnalisé pour divers services par seulement une reprogrammation de la fonctionnalité de la radio.

Cependant, ceci rend difficile la conception de récepteurs RF. Dans un SDR idéal, la solution pour augmenter à la fois l'intégration et la reconfiguration du récepteur est fourni par le transfert de l'interface de conversion analogique-numérique juste après l'antenne. L'avantage intrinsèque de ce plan est que le traitement du signal numérique supprime les non idéalités associées au traitement du signal analogique: bruit dispositif, les non-linéarités, désappariements des composants, etc. L'évolution des technologies CMOS vers des transistors de plus petites tailles est également favorable à une augmentation du niveau de traitement du signal numérique dans la mise en œuvre du récepteur [2].

Aujourd'hui, le traitement numérique peut fonctionner à une fréquence très élevée et peut ainsi traiter des signaux à haute fréquence. La limite entre le front-end RF et bande de base numérique est déplacé à plus haute fréquence, mais pas encore à la fréquence RF. Un des points limitant majeur est la conception du convertisseur analogique-numérique (CAN) qui peut convertir le signal aux hautes fréquences. Avec les technologies CMOS actuelles, il n'est pratiquement pas possible de concevoir un CAN qui convertit le signal directement en RF.

Cependant, le traitement doit être effectué autant que possible dans le numérique en raison de la faiblesse des coûts, de la possibilité de reconfiguration et de stabilité. Pour avancer dans cette direction, un récepteur fondé sur le sous-échantillonnage a été proposé. Le signal RF est sous-échantillonné dès que possible. La descente en fréquence est réalisé par le sous-échantillonneur avec le traitement des signaux en temps discret. Un cas particulier de récepteur RF qui utilise un sous-échantillonnage temps discret est Fs/2 IF récepteur [3, 4]. Cette architecture réduit la fréquence du signal de RF à un IF de Fs/2 (moitié de la fréquence d'échantillonnage), rendant ainsi le modulateur  $\Sigma\Delta$  passehaut (PH) le choix naturel pour les CAN. Ce CAN est d'une complexité très réduite par rapport au modulateur  $\Sigma\Delta$  passe-bande (PB).

Outre l'avantage de convertir directement en IF, le modulateur  $\Sigma\Delta$  PH a le potentiel

d'éliminer efficacement les DC-offsets et les bruits à basse fréquence, comme le bruit de scintillement [5, 6, 7], qui sont une source de préoccupation dans les modulateurs  $\Sigma\Delta$  passe-bas traditionnels. Cette caractéristique est particulièrement intéressante pour les convertisseurs  $\Sigma\Delta$  à entrelacement temporel où l'offset du canal est suffisamment enlevé par une opération PH [8].

En dépit de ces avantages potentiels, le concept de modulation  $\Sigma\Delta$  PH n'a pas reçu beaucoup d'attention, principalement en raison de sa mise en œuvre difficile et les incertitudes quant à sa stabilité et ses performances en présence de non-idéalités de circuit. La difficulté a été la mise en œuvre du filtre passe-haut, qui a la même importance qu'un intégrateur pour le modulateur  $\Sigma\Delta$  passe-bas. La mise en œuvre traditionnelle implique une boucle autour d'un intégrateur; c'est une solution très coûteuse en raison de l'augmentation de la consommation d'énergie et de la surface. Toutefois, récemment, une nouvelle architecture du filtre PH a été proposée. Elle permet de se débarrasser des inconvénients de l'architecture traditionnelle et propulse donc un intérêt renouvelé pour les modulateurs  $\Sigma\Delta$  PH.

Compte tenu de ses potentialités, cette thèse est axée sur la modulation  $\Sigma\Delta$  PH en général et son application au mode multi-récepteurs sans fil en particulier. Nos objectifs consistent à étudier son principe, ses performances et la stabilité et à le comparer à des modulateurs passe-bas, d'une part et de l'appliquer pour atteindre multi-modal fonction-nalité du récepteur sans fil sur l'autre.

Pour atteindre ces objectifs, une nouvelle architecture de modulateur  $\Sigma\Delta$  PH simple boucle à fonction de transfert de signal (STF) unitaire a été proposée. Elle est ensuite utilisée pour construire une architecture PH: "Generalized-Multi-Stage-Closed-Loop (GM-SCL)". Le modulateur PH proposé doit fournir les spécifications du standard EDGE/GSM, tandis que la structure GMSCL PH est utilisée pour les standards UMTS/WLAN.

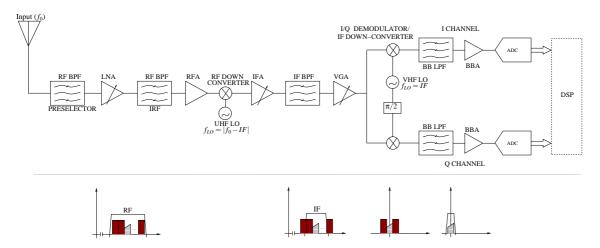

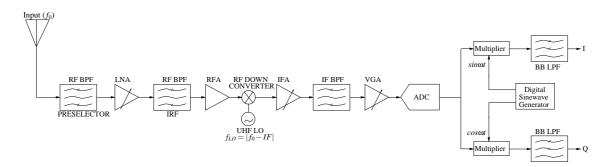

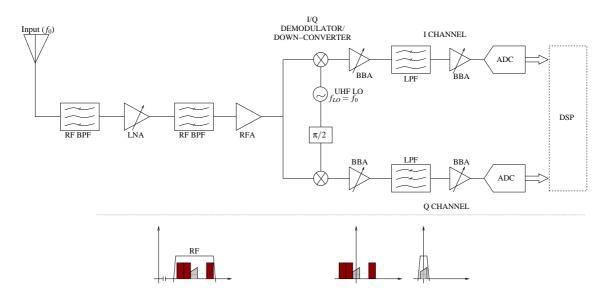

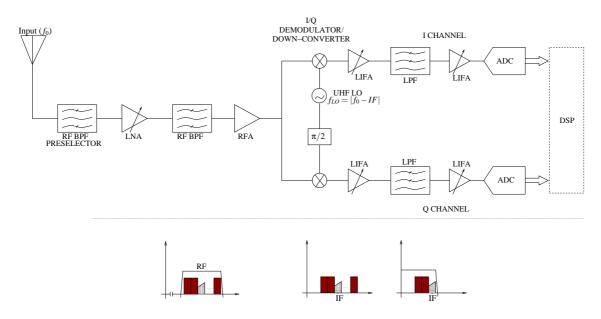

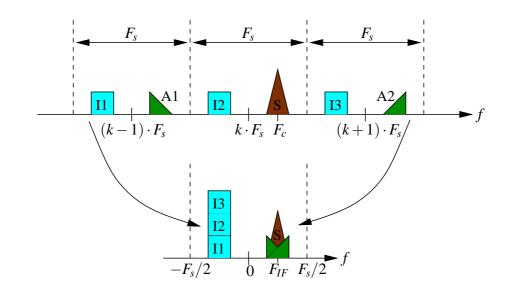

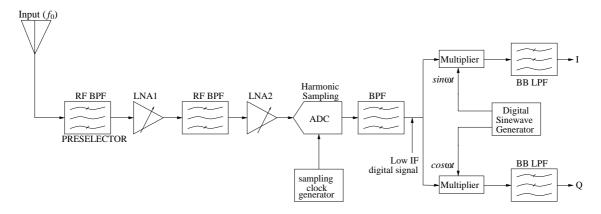

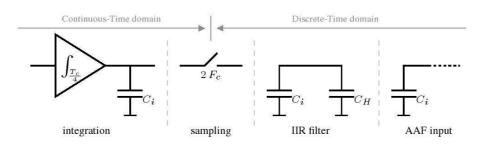

### Architecture du Récepteur RF

Les front-end RF de différentes architectures de récepteur radio concurrentes, sont discutés dans ce chapitre. La topologie Superhétérodyne de récepteur RF est la plus populaire commercialement en raison de sa performance. Pour répondre à l'augmentation des contraintes sur le frontal du récepteur, y compris l'intégrabilité et de reconfiguration, de nouvelles topologies de récepteur sont en cours d'introduction. Le récepteur Digital IF est exposé, qui est un type d'architecture superhétérodyne où le signal est numérisé au niveau de IF. Le récepteur à conversion directe présente l'avantage de la simplicité et le nombre de composants réduit. Il se débarrasse des éléments qui ne sont pas intégrables. Mais il a des problèmes de désappariement entre les voies I et Q, du DC-offset et du bruit de scintillement qui corrompent le signal. Le récepteur Low-IF se débarrasse des problèmes associés au récepteur à conversion directe, mais il introduit son propre problème de l'image. Pour cela, les filtres de rejet d'images doivent être utilisés mais sont coûteux en consommation et en surface. Pour rendre les récepteurs intégrables, reconfigurable et flexible (réalisation du concept de radio logicielle), la technique d'échantillonnage passe-bande est utilisée. Elle contribue à réduire le nombre de composants analogiques en numérisant le signal à des stades antérieurs dans le frontal du récepteur. Une application de cette technique de réception est l'architecture récemment introduit :  $F_s/2$  IF récepteur. Son schéma de principe est illustré dans la Fig. 1.

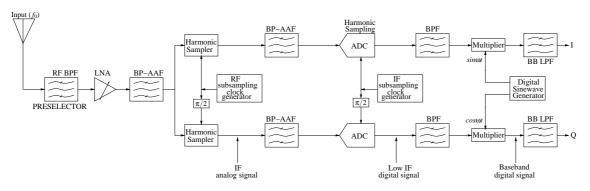

Figure 1: L'architecture du Récepteur  $F_s/2$  IF

Il résout les problèmes des récepteurs à conversion directe et des récepteurs à faible IF, tout en conservant les avantages de chacun d'eux. Dans cette architecture, la fréquence d'échantillonnage est choisie de telle sorte que après la descente en fréquence, le signal utile tombe à la moitié de la fréquence d'échantillonnage. En conséquence, l'image est le conjugué du signal, et donc évite des filtres de rejection de la bande image. En outre, puisque le signal est centré à  $IF = F_s/2$ , le DC-offset des différents composants, bruit de scintillement et les produits des non-linéarités du second ordre (IP2) ne dégrade pas le signal. Le bruit de scintillement est bien ce qui limite généralement les implémentations CMOS des architectures zéro-IF, pour des normes à bande étroite. Pour numériser directement ce signal, un type spécial de CAN avec des modulateurs  $\Sigma \Delta$  PH est nécessaire.

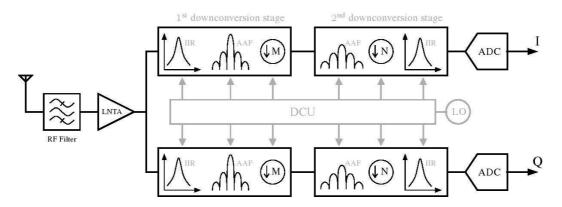

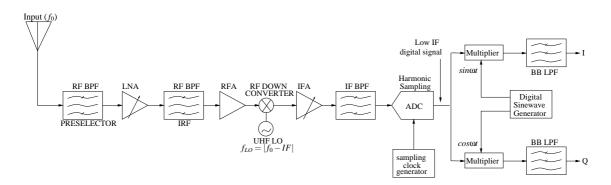

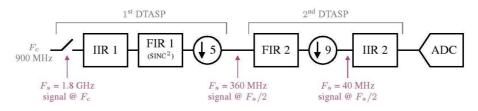

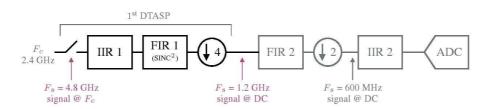

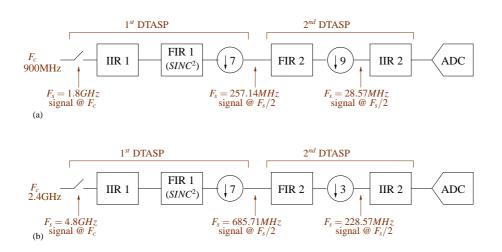

Une chaîne de réception RF de ce type qui traite les deux protocoles sans fil: GSM et WiFi est défini dans [3]. L'architecture de récepteur est illustrée à la Fig. 2.

Figure 2: Dual-Mode  $F_s/2$  Récepteur d'échantillonnage en temps discret [3]

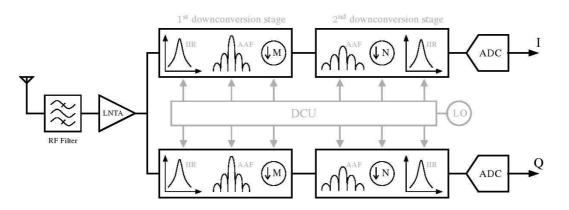

Il se compose d'un filtre RF, un Low Noise Transconductance Amplifier (LNTA), deux étages de traitement du signal à temps discret analogiques (DTASPs) et d'un CAN. Le signal d'entrée RF est d'abord filtré, amplifié et converti en un courant. Il est ensuite transmis à la première tranche DTASP, où il est filtré et remis en quadrature à la première fréquence intermédiaire. Une deuxième étape de translation vers les basses fréquences décime encore le taux d'échantillonnage et filtre le signal IF, avant qu'il soit enfin numérisé.

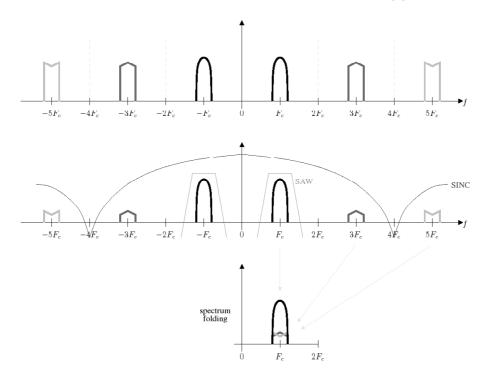

#### Les Plans de Fréquence proposés

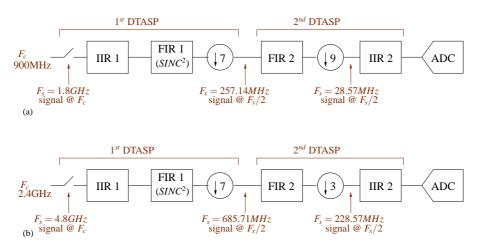

Après l'étude de l'état-de-l'art des récepteurs RF, et compte tenu des performances des CANs disponibles, le plan de fréquences illustré à la Fig. 3 est proposé. Notez que contrairement au frontal du récepteur présenté plus tôt [3], l'architecture  $F_s/2$  est adoptée à la fois pour les deux protocoles pour ne pas être sensible au bruit de scintillement et au DC-offset dans le traitement du signal.

Figure 3: (a) Plan de Fréquence en mode GSM, (b) Plan de Fréquence en mode WIFI

Le CAN pour le mode GSM fonctionne à la vitesse 28.57MHz, tandis que le CAN pour le mode WiFi est configuré pour fonctionner à 228.57MHz.

Dans les travaux de recherche effectués dans notre laboratoire, tous les blocs dans la chaîne de récepteur multi-mode de fonctionnement ont déjà été conçus [3], avec un accent particulier sur la conception d'un filtre anti-repliement [9]. L'objectif de ce travail de recherche est de proposer et de concevoir un CAN à partir d'un modulateur  $\Sigma\Delta$  PH qui peut prendre en charge plusieurs normes sans fil et être intégré dans la chaîne de réception déjà conçue.

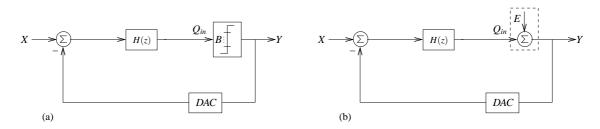

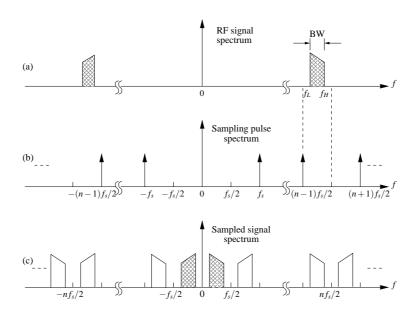

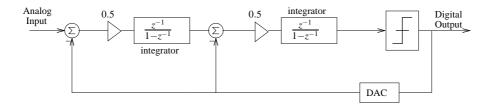

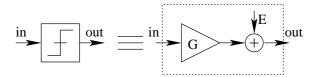

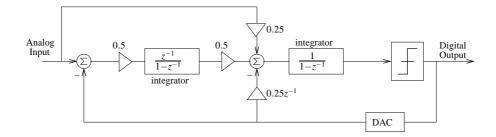

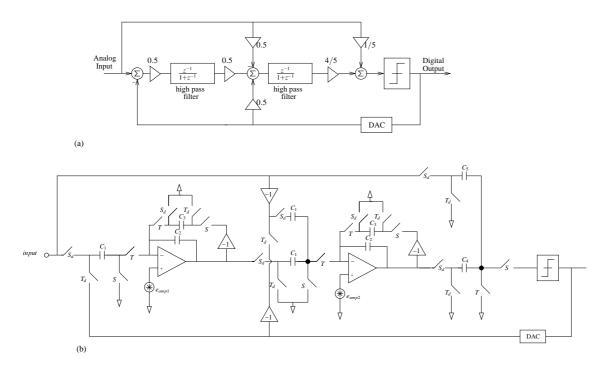

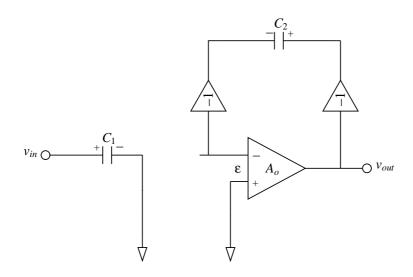

### Modulateur $\Sigma\Delta$ et Sa Modélisation au Niveau Système

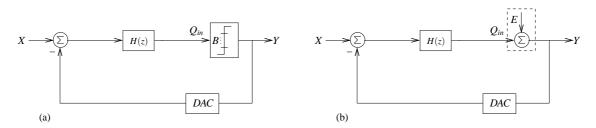

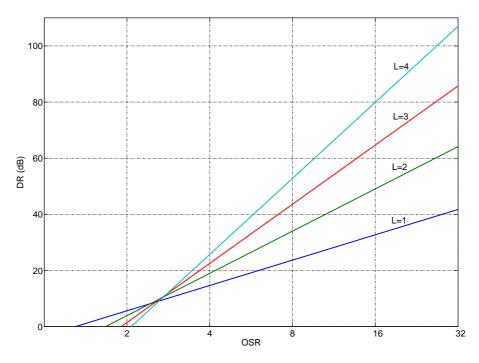

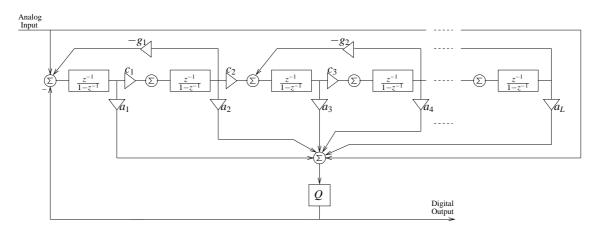

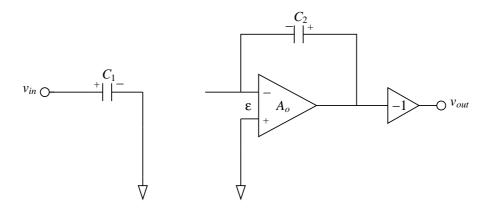

Le principe de base du CAN  $\Sigma\Delta$  est qu'il échange la résolution de sortie avec la vitesse de conversion. Dans un tel CAN, le signal analogique est converti en un code de faible résolution à une fréquence beaucoup plus élevée que le taux de Nyquist, et puis le bruit de quantification en excès est éliminé par les filtres numériques [10]. Ainsi, plus le rapport de suréchantillonnage du CAN  $\Sigma\Delta$  est élevé, plus les contraintes sur les blocs analogiques sont relâchées. Fig. 4 montre le schéma de base d'un modulateur  $\Sigma\Delta$  et de son modèle linéaire correspondant. Le modulateur Sigma-Delta se compose d'un chemin feedforward formé par un filtre de boucle et un quantificateur de *B*-bits, et un chemin de rétroaction négative qui les entoure, en utilisant un convertisseur numérique-analogique (CNA) à *B*-bits aussi [11]. Dans le modèle linéaire comme l'illustre dans la Fig. 4, le CNA est supposé être idéal et l'erreur de quantification injectée est supposée être un bruit blanc additif. Bien que cette approximation n'est pas valable pour les quantificateurs avec une faible résolution, il est néanmoins utilisé pour la simplicité des calculs.

Figure 4: Modulateur  $\Sigma\Delta$  de Base (a) Schéma, (b) Correspondant modèle linéaire

Le filtre de boucle est tout simplement un intégrateur qui peut être facilement mis en œuvre avec des techniques à capacités commutées. Pour un modulateur  $\Sigma\Delta$  généralisé d'ordre L, les fonctions de transfert sont:

$$STF(z) = z^{-L} \tag{1}$$

$$NTF(z) = (1 - z^{-1})^L$$

(2)

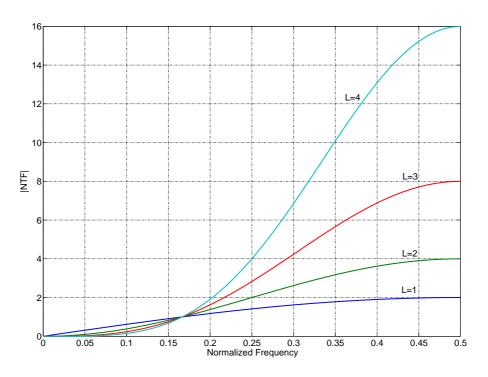

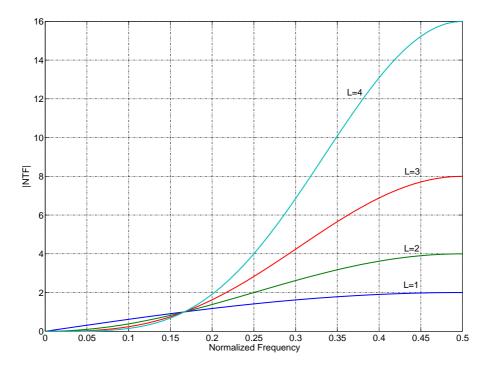

Pour parvenir à une fonction de transfert d'ordre L, L blocs de base soit L intégrateurs sont nécessaires. Fig. 5 montre les réponses en fréquence des NTFs pour différentes valeurs de L. Lorsque l'ordre du modulateur est supérieur à un, la réponse en fréquence de la NTF présente la caractéristique des filtres passe-haut. Plus on augmente l'ordre du modulateur, plus le bruit sera rejeté en basses fréquences.

De cette façon, le signal de sortie pour le modèle idéal linéaire peut être écrite comme:

$$Y(z) = X(z)z^{-L} + E(z)(1 - z^{-1})^{L}$$

(3)

Le modulateur  $\Sigma\Delta$  du second ordre est populaire car il fournit un bon compromis entre performance et complexité. Il peut également être utilisé comme un bloc de base pour des modulateurs d'ordre supérieur. Plusieurs architectures de second ordre sont proposées dans la littérature, notamment Boser-structure [12], Silva-structure [13] et Oberst-structure [14]. Leurs avantages et inconvénients sont examinés en détails. Puisque le modulateur de second ordre ne produit pas une performance suffisante pour de nombreuses applications, d'autres modulateurs qui permettent une mise en forme du bruit d'ordre supérieur sont étudiés en détail. Il existe deux grandes familles de modulateur d'ordre supérieur 1) les modulateurs d'ordre supérieur en simple boucle, 2) les multi-boucles ou des structures

Figure 5: Réponses en fréquence de NTFs pour modulateurs des ordres L différentes

MASH (Multi-stAge noise SHaping). Quatre techniques importantes pour une mise en forme de bruit plus élevée en simple boucle existent: le Cascade d'Intégrateurs avec Distributed Feedback (CIFB), le Cascade de Résonateurs avec Distributed Feedback (CRFB), le Cascade de Intégrateurs avec Distributed Feedforward (CIFF), le Cascade de Résonateurs avec Distributed Feedforward (CRFF). Dans les structures MASH, les topologies les plus performantes sont Generalized Multi-Stage Closed Loop (GMSCL) [15, 16] et les modulateurs  $\Sigma\Delta$  MASH robustes [17].

#### Modélisation au Niveau Système

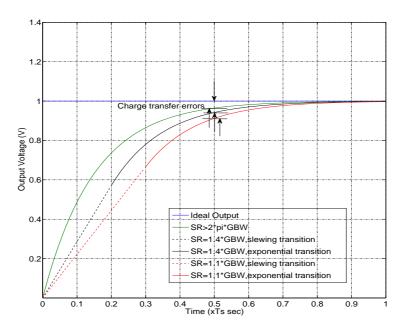

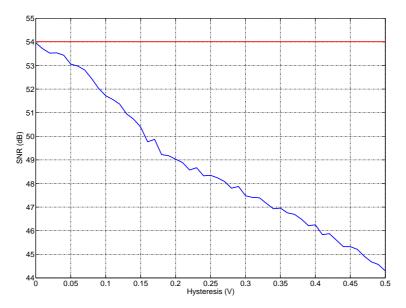

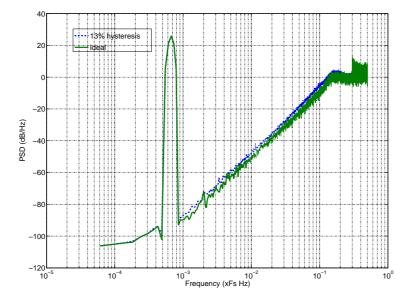

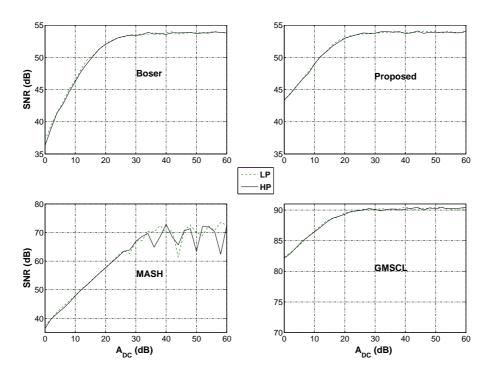

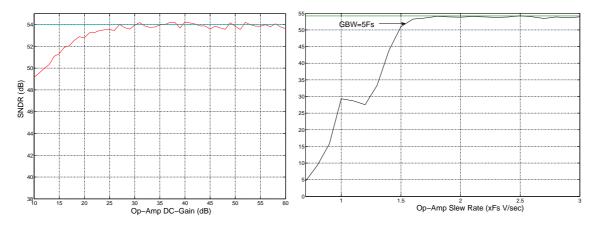

La modélisation au niveau système aide à déterminer les spécifications des éléments constitutifs fondamentaux de modulateur  $\Sigma\Delta$ . Elle est la première étape dans la conception de circuits intégrés analogiques. Aux fins de la modélisation au niveau système, la structure classique de Boser [12] est choisie. La modélisation est effectuée pour la gigue d'horloge, le bruit thermique du commutateur et le bruit des amplificateurs-operationnels (ampli-op). La modélisation au niveau des ampli-op comprend la saturation, le gain-DC fini, le produit gain-bande passante fini et le "slew rate" fini. Les non-idéalités du comparateur: le DC-offset et l'hystérésis sont également pris en compte. Il se trouve qu'on a besoin d'un ampli-op avec  $\pm 1.3Vref$  de dynamique de sortie, 40dB de gain-DC,  $5F_s$  de produit GBW et  $1.8F_s$  SR pour atteindre une performance proche de l'état idéal.

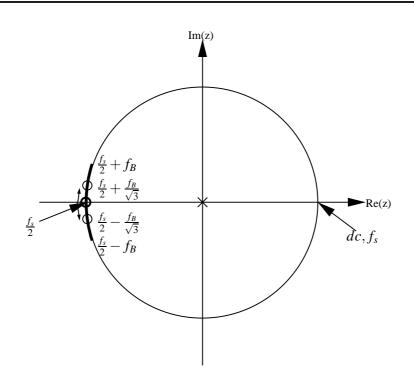

### Modulateur $\Sigma\Delta$ Passe-Haut

Le principe de fonctionnement du modulateur  $\Sigma\Delta$  PH est le même que celui du modulateur  $\Sigma\Delta$  passe-bas: le bruit de quantification est mis en forme hors de la bande du signal par un filtre de boucle. La différence réside dans le placement de la bande du signal. Dans le cas de modulateur  $\Sigma\Delta$  PH, il se situe à  $F_s/2$ , où  $F_s$  est la fréquence d'échantillonnage, par rapport à une bande passante en bande de base pour le modulateur  $\Sigma\Delta$  passe-bas. Ainsi, la transformation d'un passe-bas en modulateur passe-haut est une transformation passe-haut à passe-bas de la fonction de transfert bruit de quantification. Cette transformation permet au modulateur  $\Sigma\Delta$  PH d'être complètement insensible aux bruits de basses fréquences.

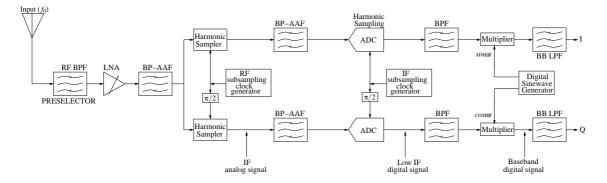

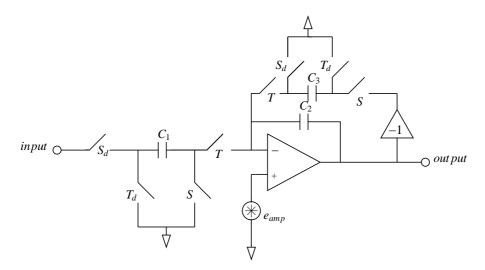

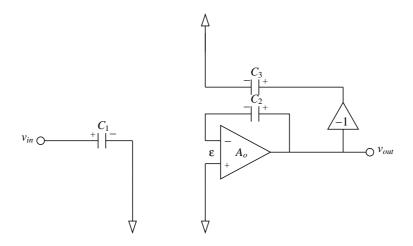

#### Structure d'Unité-STF proposée

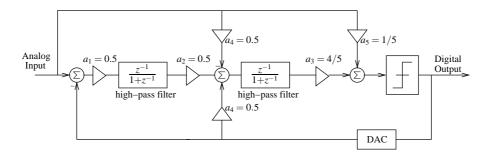

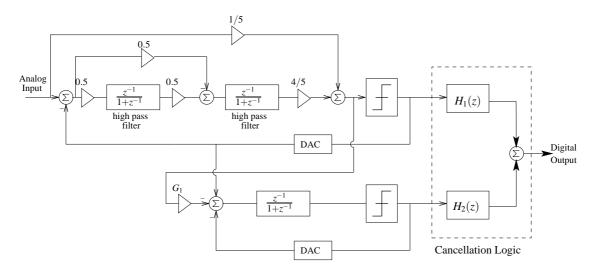

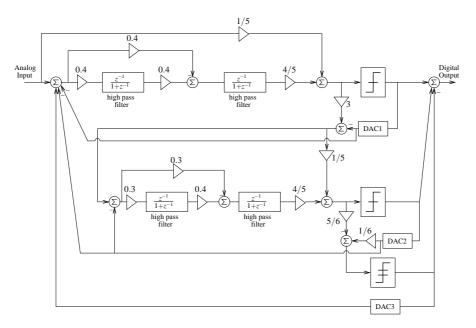

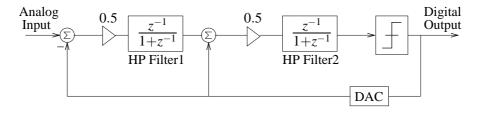

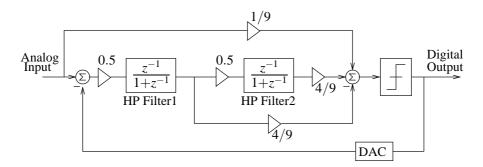

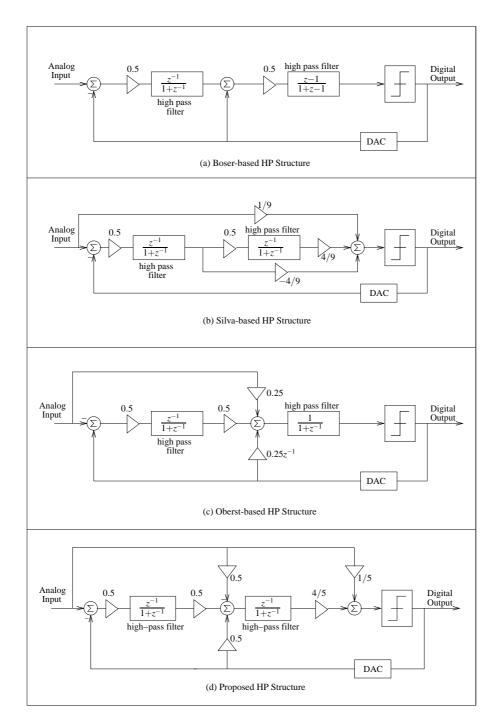

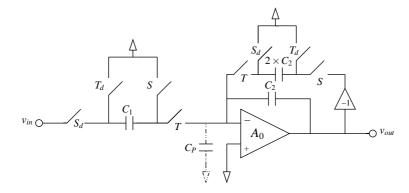

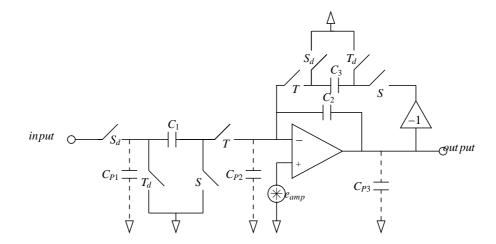

Une nouvelle structure dont la STF est unitaire et qui pallie les insuffisances des architectures de modulateur existantes est proposée. Cette topologie de conversion passe-haut est illustrée à la Fig. 6. Il s'agit d'une structure mixte "feedforward-feedback" dans laquelle le signal attaque le comparateur directement. Le signal utile est annulé à l'entrée de deux filtres passe-haut. Ainsi le problème des distorsions du signal utile par le deuxième ampliop, associé à l'architecture à base de Oberst, a été adressé. Les filtres passe-haut sont mis en œuvre à l'aide de filtres à retard, ce qui élimine la question de l'augmentation de la charge sur l'ampli-op mis en œuvre dans le premier filtre passe-haut, ce qui n'est pas le cas dans la structure de base Oberst. Les problèmes relatifs à la topologie à base de Silva ont été résolus en changeant le chemin auxiliaire feedforward, tel que montré dans la Fig. 6.

Figure 6: Structure proposée pour l'unité-STF modulateur  $\Sigma\Delta$  passe-haut

Ceci détend les exigences imposées à l'additionneur puisqu'il n'y a que deux branches à ajouter comparé aux trois branches requises dans la structure à base de Silva. Dans ce cas, l'implémentation de cet additionneur passivement, implique une atténuation plus faible du signal ce qui réduit les exigences de conception du quantificateur. La charge sur le premier ampli-op a également été réduite car il n'y a pas de condensateur feedforward à charger.

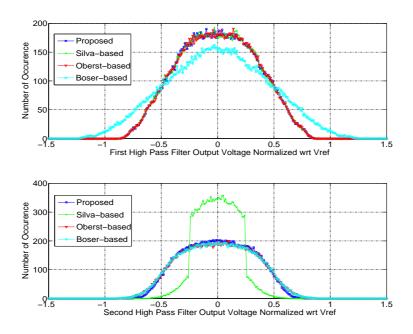

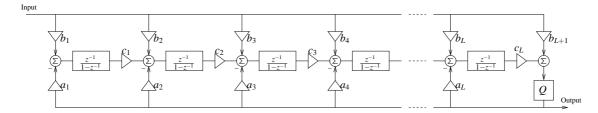

#### Analyse Comparative des Modulateurs $\Sigma\Delta$ PH Boucle Unique

Nous comparons les quatre architectures (Boser, Silva, Oberst, Proposée) en prenant comme critère, les contraintes imposées à l'ampli-op. Les excursions de filtres passe-haut sont un paramètre important pour la comparaison, car ils sont directement liés à la variation de tension de l'ampli-op mise en œuvre dans les filtres passe-haut. Nous voulons garder ces excursions à un niveau minimal pour simplifier la conception des ampli-op. D'autres non-idéalités comme le gain-DC fini, le GBW fini et SR fini dépendent de l'architecture du modulateur et du flux du signal dans la topologie.

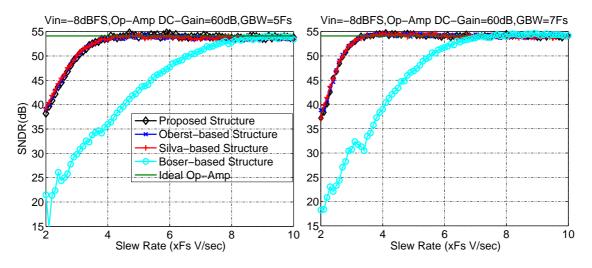

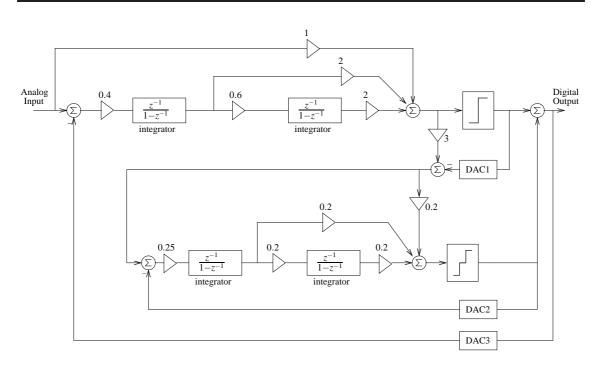

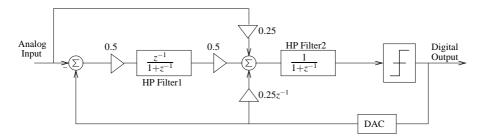

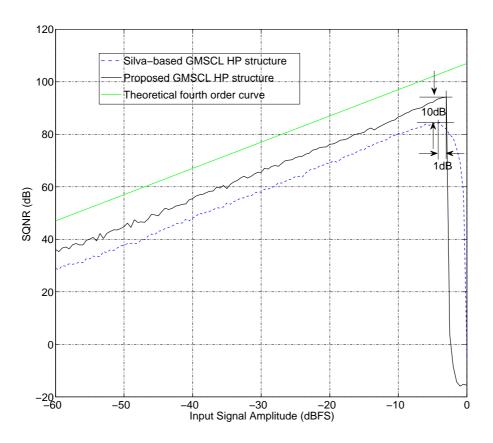

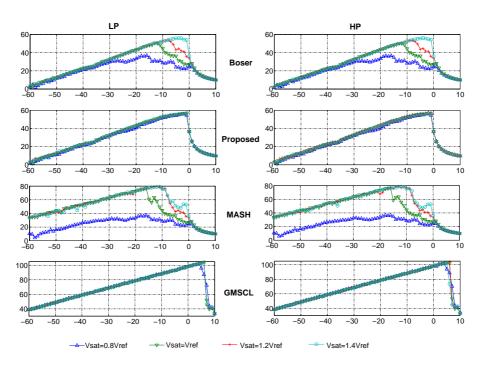

Les quatre architectures avec les valeurs des coefficients, utilisées pour l'analyse de comparaison sont présentées dans la Fig. 7.

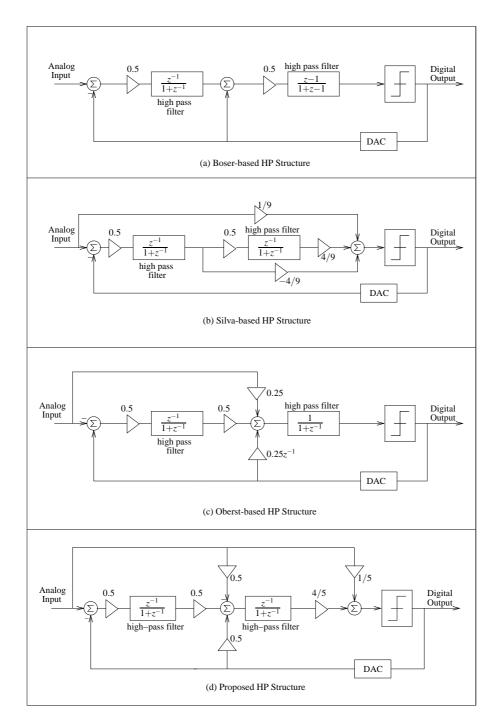

#### Excursions de Sortie des Filtres Passe-Haut

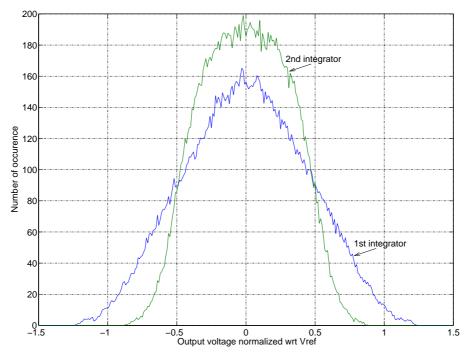

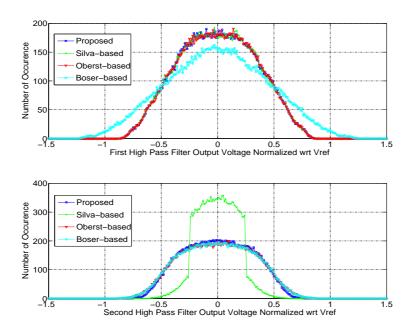

Les histogrammes montrant les excursions de sortie de deux filtres passe-haut dans les quatre topologies en compétition sont présentés sur la Fig. 8

Les résultats présentés sur la Fig. 8 montrent que la structure PH basée sur celle de Boser a la plus grande excursion pour le premier filtre, ce qui est normal puisque il traite à la fois le signal utile et le bruit de quantification. Toutes les autres structures ont les mêmes excursions pour le premier filtre passe-haut parce qu'elles traitent juste le bruit de quantification. Ces excursions sont bien dans la fourchette des  $-Vref \leftrightarrow Vref$ , soit le pas de quantification et sont facilement réalisables. La tension de saturation de l'amplificateur opérationnel est normalement fixée par le pas de quantification soit la gamme de tension  $-Vref \leftrightarrow Vref$ , mais puisque les excursions de la structure basée sur celle de Boser dépasse cette gamme, nous devons concevoir des ampli-op avec des dynamiques de sortie plus élevées, ce qui augmentera la consommation électrique, qui peut devenir importante dans les technologies à basse tension.

L'excursion du deuxième filtre passe-haut est très inférieur pour la structure à base de Silva, puis vient l'architecture proposée, et enfin les structures de Boser et Oberst. Mais tous sont bien à l'intérieur de l'excursion de la quantification et sont donc faciles à réaliser.

#### L'effet des Non-Idéalités de l'Ampli-Op

La performance du filtre passe-haut est directement liée à la performance fournie par son ampli-op. Les non-idéalités des amplificateurs opérationnels dont le DC-gain fini et non linéaire, le fini GBW et le SR fini provoquent un transfert incomplet de la charge dans les capacités commutées (SC) mise en œuvre dans le filtre passe-haut qui est une cause majeure de dégradation des performances de modulateurs  $\Sigma\Delta$  PH.

**DC-Gain Fini** la résolution les équations de transfert de charge pour le filtre PH standard, en présence de l'ampli-op avec un DC-gain fini révèle que la fonction de transfert exacte pour le premier filtre PH est la suivante:

$$H_{practical}(z) = 0.5 \frac{\frac{A_0}{A_0 + 3.51} z^{-1}}{1 + \frac{A_0 - 0.99}{A_0 + 3.51} z^{-1}}$$

(4)

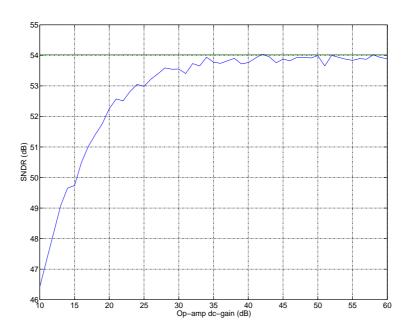

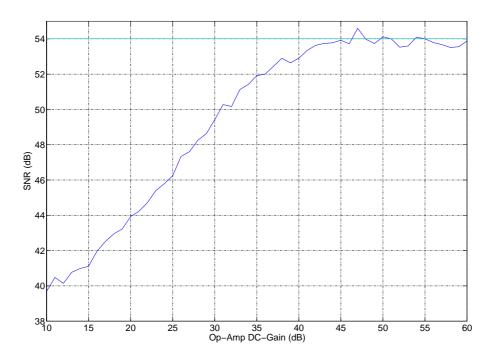

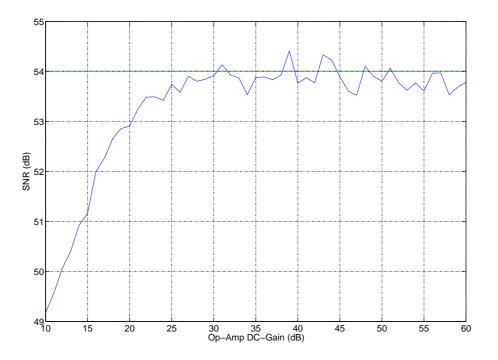

Où  $A_0$  représente le gain-DC de l'ampli-op. En utilisant l'Éqn. 4 comme la fonction de transfert pour le premier filtre passe-haut, toutes les architectures discutées plus tôt ont été simulées pour différentes valeurs de  $A_0$  pour comparer l'effet de cette non-idéalité

Figure 7: Quatre structures utilisées pour l'analyse comparative

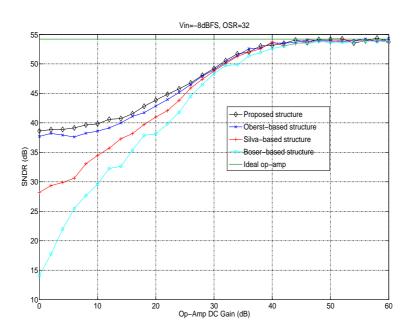

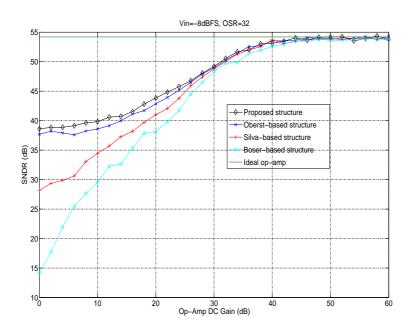

sur les différentes architectures. Le signal d'entrée est une sinusoïde avec une amplitude de 0,4 normalisée par rapport à l'étape de quantification soit -8dBFS et sa fréquence vaut  $0.4993F_s$ . Le résultat de la simulation est montré dans la Fig. 9.

Figure 8: Comparaison d'excursion de sortie des filtres passe-haut à Vin=-8dBFS

Figure 9: SNR vs. DC-Gain d'Ampli-Op

Cette figure montre que toutes les architectures requièrent un ampli-op avec un gain-DC de 45 dB pour acquérir le rapport signal sur bruit de quantification (SQNR) pour l'amplitude d'entrée fixée. On peut constater que l'architecture proposée est plus robuste que les autres architectures en présence d'un gain-DC faible. Le Gain-Bandwidth Product Fini et Le Slew Rate Fini avec les contraintes supplémentaires de GBW fini et SR fini, la fonction de transfert du filtre HP devient:

$$v_{out}(t) = v_{out}(nT_s - T_s) + V_s - sgn(V_s)SR_s\tau e^{-(\frac{T_s}{2\tau} - \frac{|V_s|}{SR_s\tau} + 1)}$$

(5)

où  $V_s$  est donné par:

$$V_s = -(1+\beta)v_{out}(nT_s - T_s) + b\alpha v_{in}(nT_s - T_s/2)$$

(6)

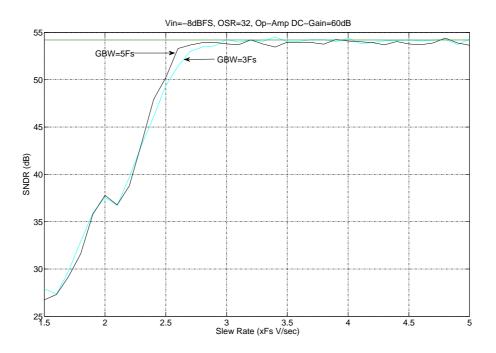

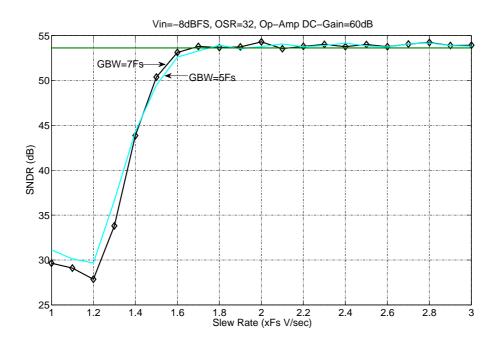

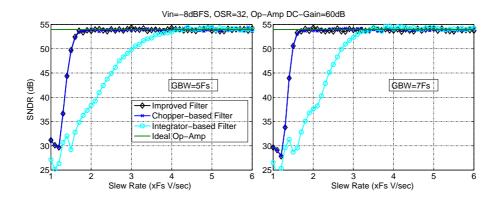

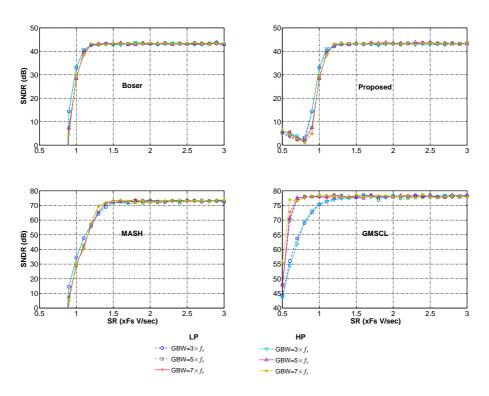

où  $v_{out}$  est la sortie du filtre,  $T_s = 1/F_s$  est la période d'échantillonnage,  $v_{in}$  est l'entrée du filtre et  $\tau = (3 + b)/2\pi GBW$  est la constante de temps de l'ampli-op utilisé dans le filtre. La valeur de la constante de temps  $\tau$  est dérivée dans l'annexe. B. Le GBW fini et le SR fini de l'ampli-op produisent des harmoniques dans le spectre de la sortie dégradant ainsi le SNDR. Nous avons effectué des simulations de différentes architectures en faisant varier les valeurs de SR et nous avons observé le SNDR. Cette procédure est répétée pour deux valeurs différentes de GBW de l'ampli-op. Les résultats sont illustrés dans la Fig. 10:

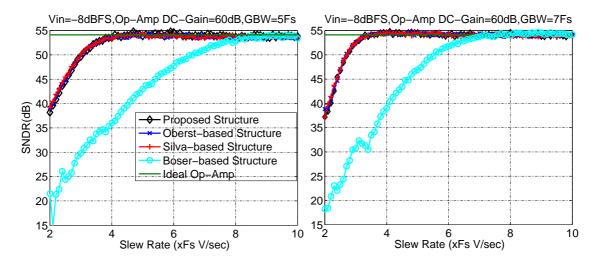

Figure 10: La dégradation des SNDR pour différentes architectures en fonction de SR d'ampli-op

Les résultats montrent qu'au moins un SR de  $4F_s(V/sec)$  est nécessaire pour les structures feedforward pour établir la performance requise, tandis que pour la structure à base de Boser, un SR de  $8.5F_s(V/sec)$  est nécessaire pour garantir le SNDR optimal pour un GBW de  $5F_s$ . Toutes les architectures feedforward ont des meilleures performances comparées à la structure de Boser.

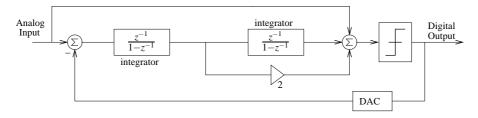

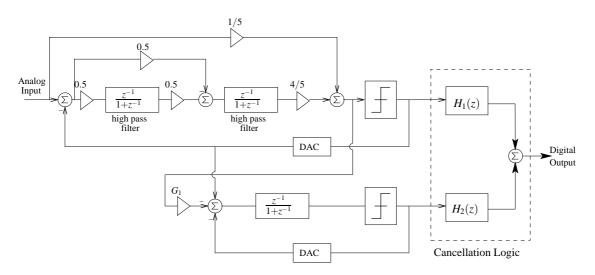

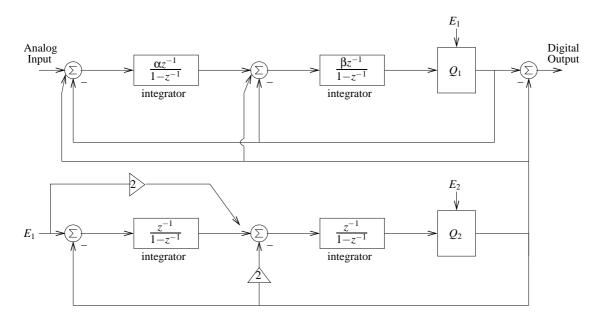

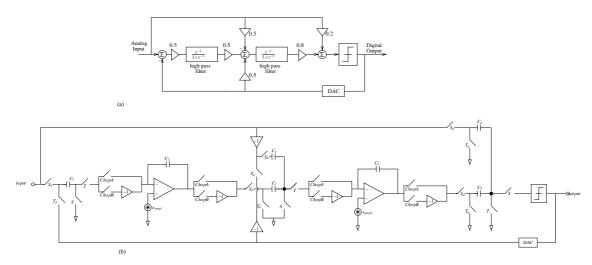

#### Les Structures des Modulateurs $\Sigma\Delta$ PH à Boucles Multiples

Dans une structure multi-étages ou MASH, chaque étage est réalisé par un modulateur  $\Sigma\Delta$  différent. L'erreur de quantification d'un étage est l'entrée de l'étage suivant. La sortie de l'étage suivant est donc une approximation de cette erreur de quantification. Les filtres

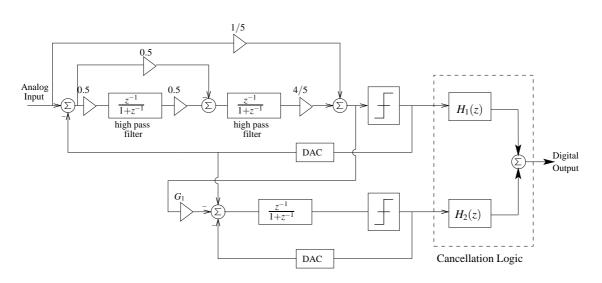

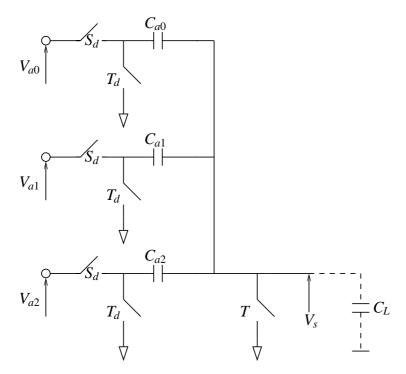

numériques sont conçus de manière à annuler les erreurs de quantification de tous les étages sauf le dernier. La Fig. 11 montre une architecture générique du modulateur  $\Sigma\Delta$  Cascade 2-1 PH basé sur la topologie proposée du modulateur de seconde ordre.

Figure 11: Architecture générique de la cascade de modulateur  $\Sigma\Delta$  HP basé sur la structure proposée

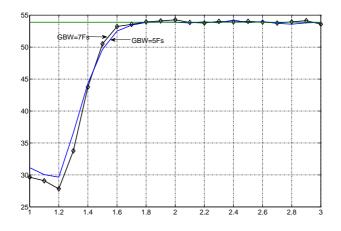

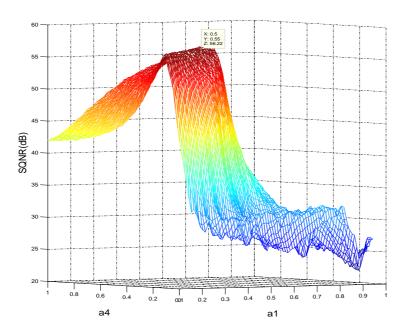

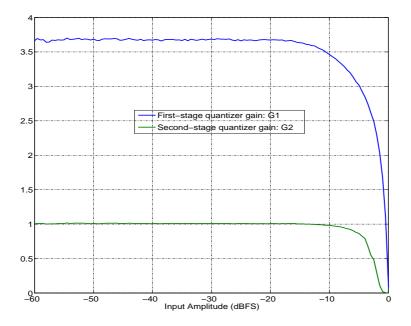

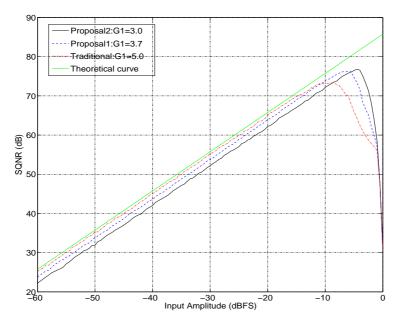

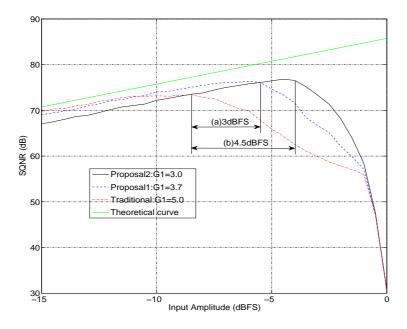

G1 est l'estimation du gain de quantification du premier étage. Nous montrons que l'amélioration des performances peut être obtenue par une approximation plus précise et systématique du gain de quantification G1 comme l'illustré à la Fig. 12.

Le problème associé à des structures MASH, c'est qu'il faut qu'il y ait un bon appariement entre les filtres numériques et la NTF analogique. En cas de discordance, le SNDR se dégrade. Du point de vue de la fabrication, les filtres numériques sont assez précis alors qu'il ya un degré d'imprécision dans la mise en œuvre de la partie analogique. L'inexactitude des coefficients analogiques est une conséquence directe du désappariement des rapports des condensateurs dans le circuit. D'autres imperfections analogiques qui changent la NTF et STF des différents étages de MASH et par conséquent entraînent une fuite du bruit de quantification en raison de l'inadéquation des filtres numériques avec des circuits analogiques sont dus aux gain-DC fini, GBW fini et SR fini des amplificateurs. La correction adaptative numérique de ces erreurs analogique est une zone très étudiée. Cette calibration peut être effectuée hors ligne [18], en ligne [19, 20, 21, 22, 23] ou par injection de signal de test [24]. Toutes ces techniques sont au prix d'une augmentation de la complexité des circuits et de la consommation.

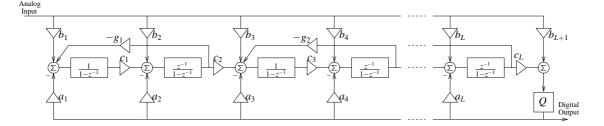

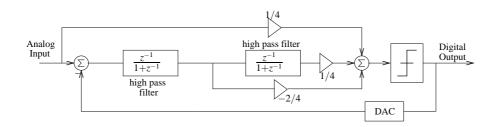

#### L'architecture Generalized Multi Stage Close Loop

Le problème du désappariement entre les composants analogiques et les filtres numériques dans les structures traditionnelles de MASH en raison de nonidéalitiés a conduit à une nouvelle génération de structures MASH qui sont exemptes de filtres d'annulation du bruit de quantification. De cette façon, nous réduisons la complexité des circuits mais augmen-

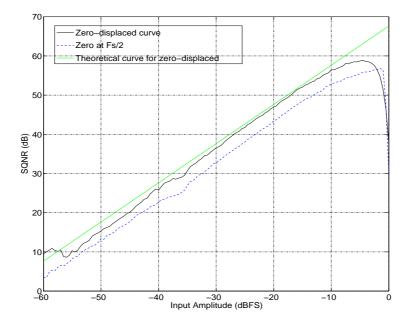

Figure 12: SNR en fonction du signal d'entrée pour trois cascade  $\Sigma\Delta$  PH modèles, (une augmentation) de la plage dynamique atteint par la proposition 1 de plus de l'architecture classique (b) Augmentation de la plage dynamique réalisé par Proposition 2 sur l'architecture classique

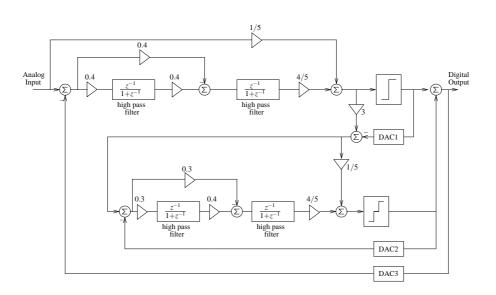

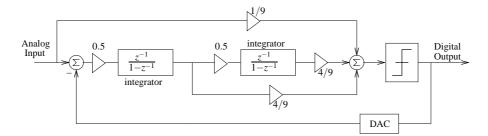

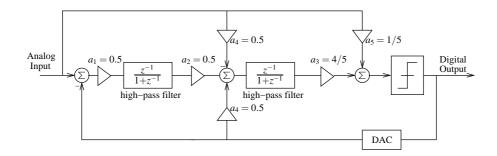

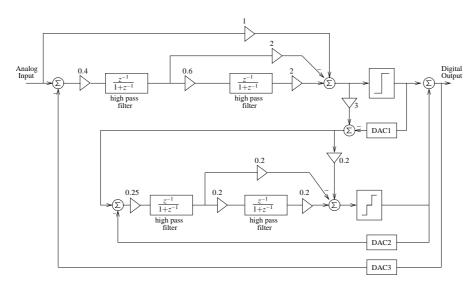

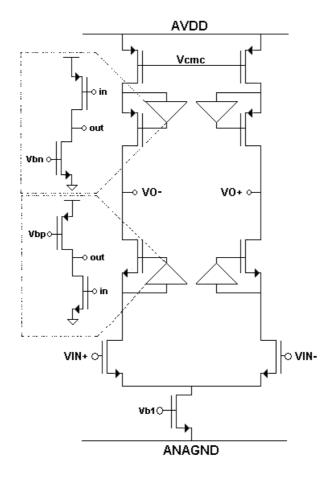

tons la robustesse du circuit en éliminant la sensibilité aux imperfections du circuit. La première architecture de cette nature est présentée dans [25]. Cette structure est appelée multi-stage closed loop (MSCL). Chaque étage de cette structure est un modulateur simple d'ordre un et une réaction globale est introduite à partir de la sortie, qui est la somme de la production de tous les comparateurs. Une version améliorée de cette structure est Generalized multi-stage closed loop (GMSCL). Il s'agit essentiellement d'une structure cas-cade 2-2, mise en œuvre à chaque étape comme une structure feedforward, et une réaction globale est utilisée à partir de la sortie comme le montre la Figure. 13.

Il est à noter que l'additionneur avant le premier étage de comparaison peut être réalisée passivement dans le GMSCL PH proposé et montré dans la Fig. 13, puisque les deux coefficients sont inférieurs à l'unité.

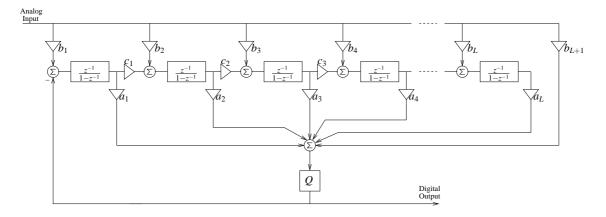

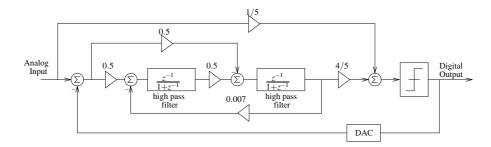

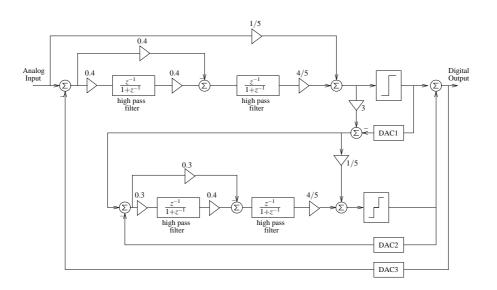

# L'architecture Generalized Multi Stage Close Loop avec Plage Dynamique Étendue

La structure de GMSCL HP proposée souffre des non-linéarités du CNA 2.5bit dans la boucle de rétroaction. Pour contrer ce problème, une technique récemment proposée [26] a été appliquée au modulateur. Elle évite l'utilisation coûteuse des techniques traditionnelles comme Dynamic Element Matching (DEM) et augmente la plage dynamique globale du modulateur. La technique consiste à utiliser un quantificateur linéaire (1 bit ou 1.5bits) dans la boucle principale, puis d'en extraire le bruit de quantification et en l'amenant à

Figure 13: GMSCL PH structure basée sur la structure proposée

un quantificateur auxiliaire multi-bits. Les sorties des deux quantificateurs principaux et auxiliaires sont renvoyées à la boucle via leur CNAs respectifs. La configuration qui en résulte est un modulateur de la Fig. 14.

Figure 14: GMSCL PH proposé avec DR étendu

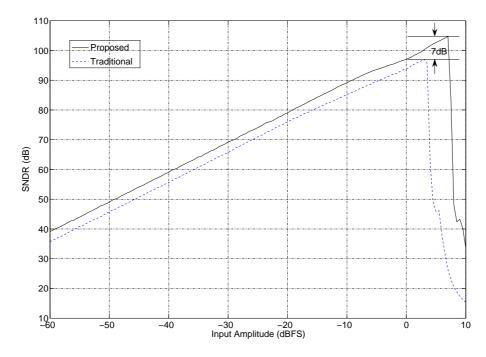

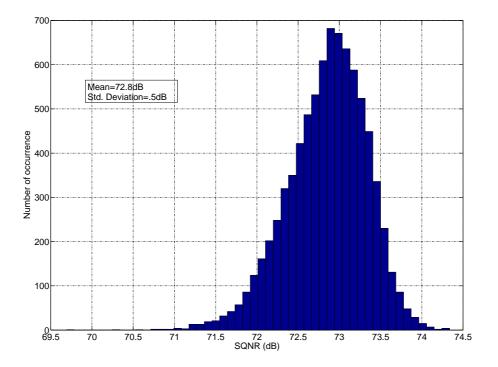

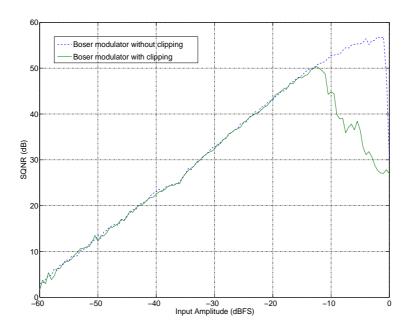

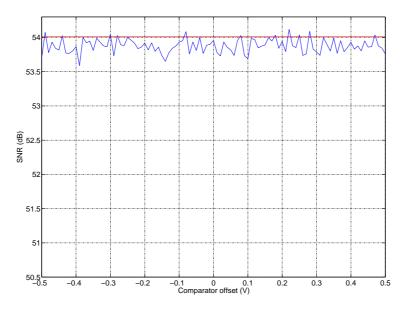

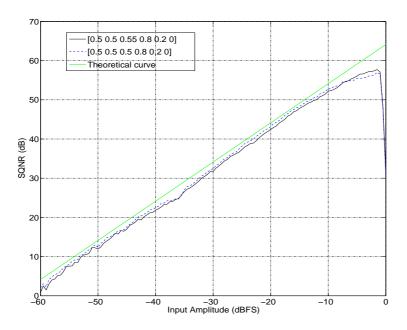

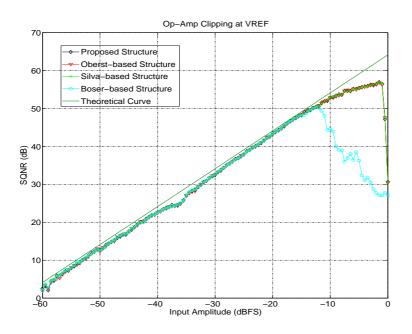

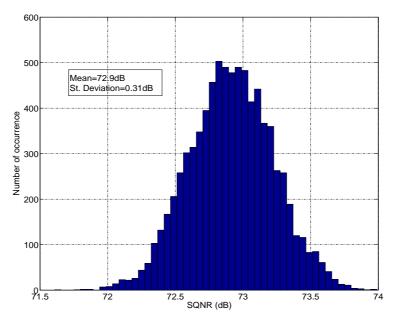

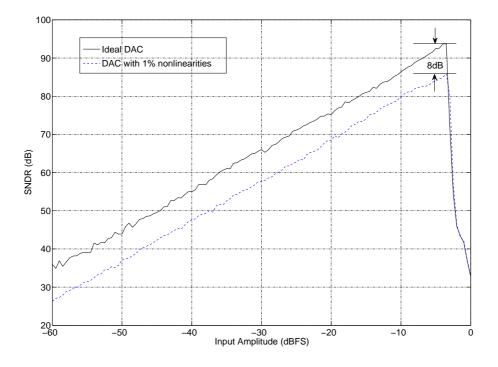

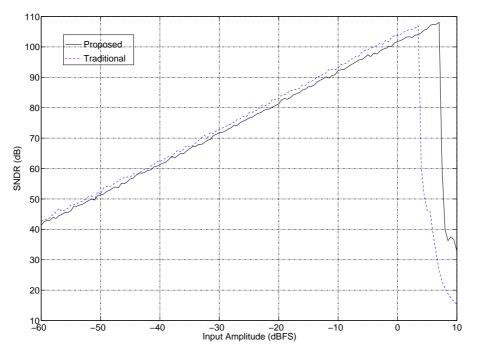

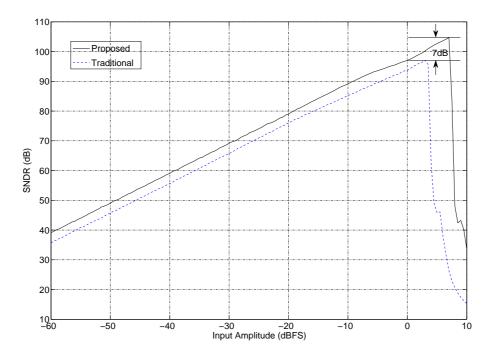

Pour montrer l'efficacité de l'architecture proposée, des simulations comportementales ont été réalisées dans MATLAB. Pour comparer les architectures équivalentes, le quantificateur du deuxième étage de la topologie en Fig. 13 a été réalisé avec 5-niveaux de sortie et il utilise quatre comparateurs. L'architecture proposée (Fig. 14) a un comparateur et un quantificateur auxiliaire 4-niveaux dans la deuxième étape et donc quatre comparateurs. La modélisation des non-linéarités du CNA de moyenne 0 et de variance 1% a été introduite dans ces deux structures. Le résultat de la simulation présentée à la Fig. 15 montre que la structure proposée fournie une performance 7dB meilleure que l'architecture traditionnelle du point de vue du SNR et 4dB d'amélioration de la performance du point de vue de la DR.

Figure 15: Comparaison des performances de deux structures GMSCL PH avec 1% non-linéarités du CNA

### L'implémentation du Filtre Passe-Haut

Le filtre passe-haut est une composante majeure de modulateur  $\Sigma\Delta$  PH. La fonction de transfert pour le filtre PH est réalisé en appliquant la transformation,  $z \rightarrow -z$ , à un intégrateur basé sur un circuit à capacités commutées:

$$H_{passe-bas}(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{7}$$

Il en résulte:

$$H_{PH}(z) = \frac{-z^{-1}}{1+z^{-1}} \tag{8}$$

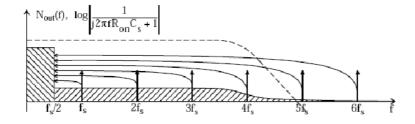

Ce filtre a un zéro à DC par opposition à un zéro à  $F_s/2$  pour l'intégrateur à capacités commutées. Il y a trois filtres PH dans l'état de l'art: filtre à base d'intégrateur, filtre à base de chopper et filtre amélioré.

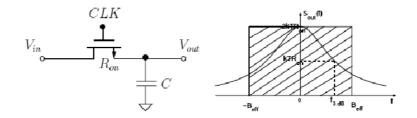

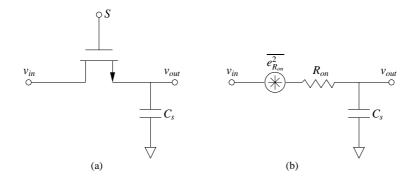

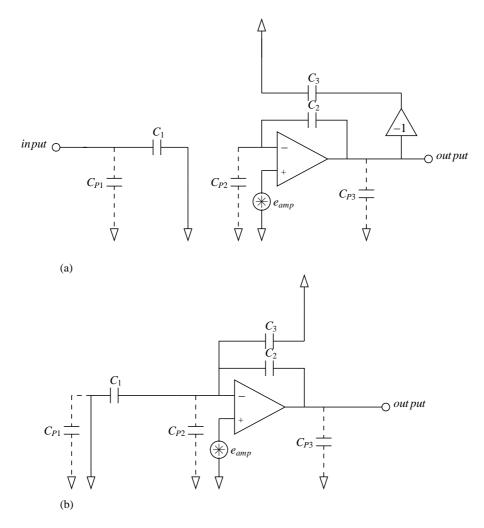

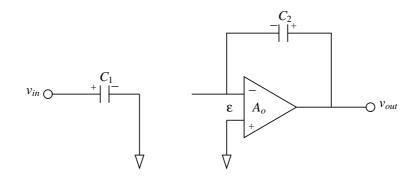

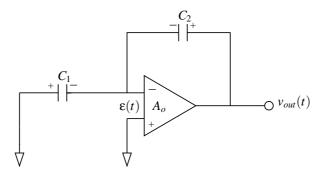

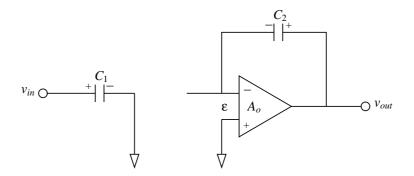

#### Le Filtre à Base d'Intégrateur

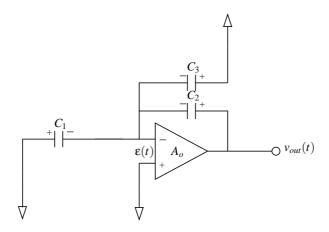

La première mise en œuvre du filtre PH illustrée dans la Fig. 16 a été présenté dans [27] pour l'implémentation du modulateur  $\Sigma\Delta$  passe-bande.

Figure 16: Filtre PH faite par une boucle de rétroaction autour de l'intégrateur

Il est conçu par l'introduction d'une boucle supplémentaire de feed-back autour de l'intégrateur, de telle sorte que la fonction de transfert pour le filtre HP est réalisé. Les problèmes associés à cette mise en œuvre comprennent une sensibilité accrue au bruit des ampli-op [28], une haute contribution du bruit thermique des interrupteurs, une grande superficie et une consommation d'énergie élevée.

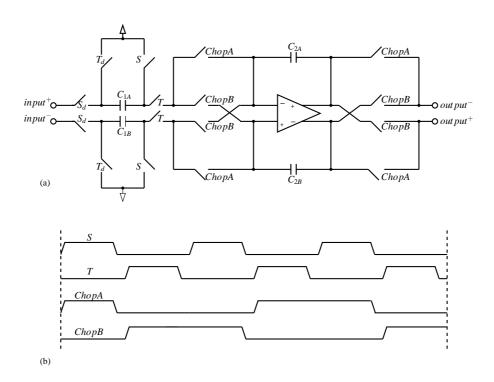

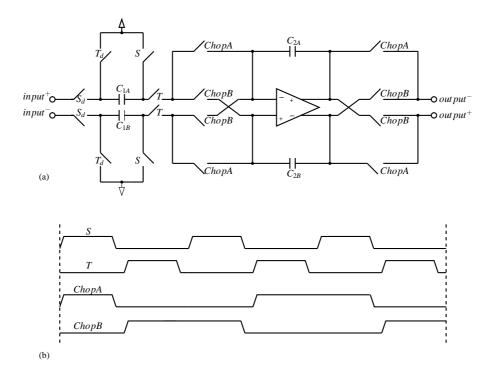

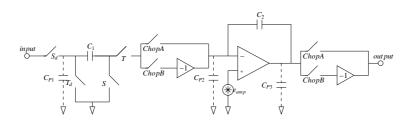

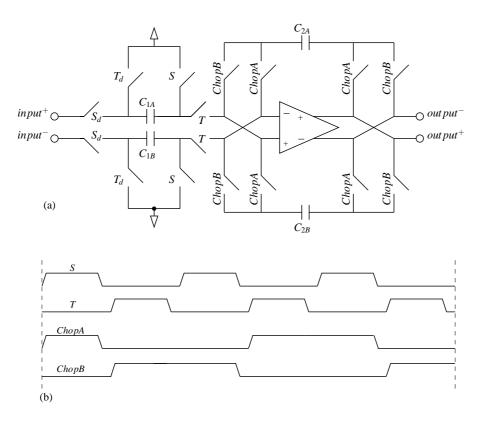

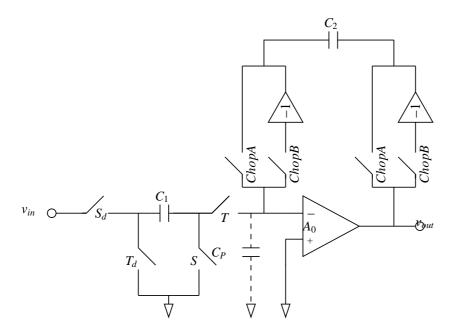

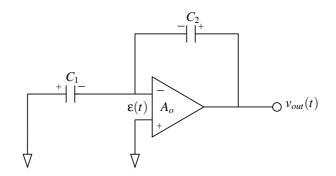

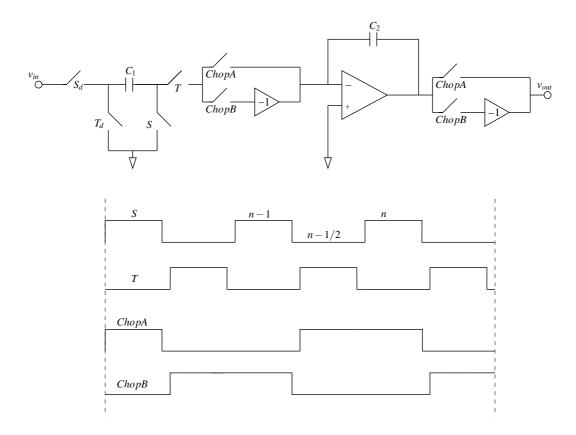

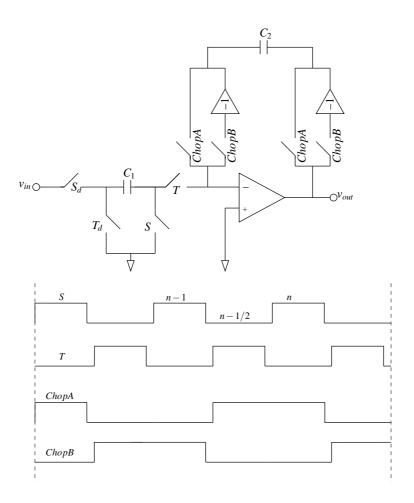

#### Le Filtre à Base de Chopper

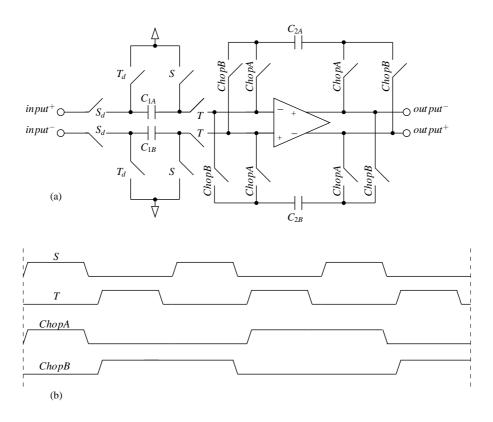

La deuxième implémentation montrée dans la Fig. 17, est basée sur l'approche de la modulation du signal d'entrée pour le ramener en bande de base, puis le signal est intégré par l'intégrateur, et ensuite modulé pour remonter à la fréquence IF.

Toutefois, le traitement du signal se produit encore en bande de base au sein de l'intégrateur. Les avantages obtenus par le déplacement à IF sont perdues une fois que le signal est modulé vers la bande de base dans le domaine analogique, réintroduisant la nécessité d'utiliser les techniques dites de "chopper stabilization (SHC)" et "correlated double sampling (CDS)".

Figure 17: (a) Filtre PH fait en hachant l'entrée et la sortie du signal d'intégrateur, (b) Son chronogramme associé

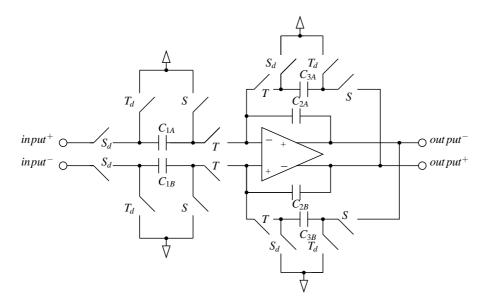

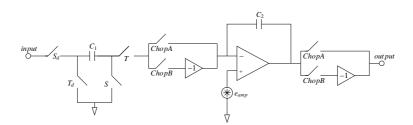

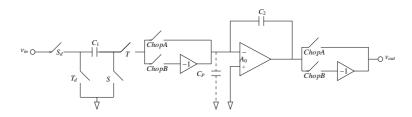

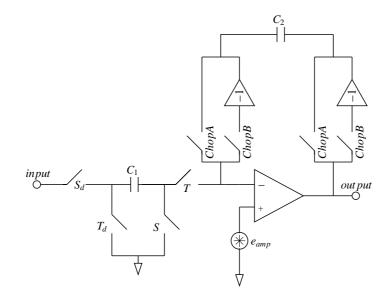

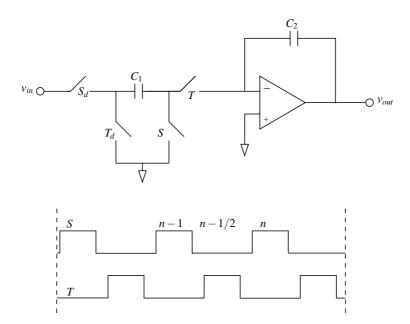

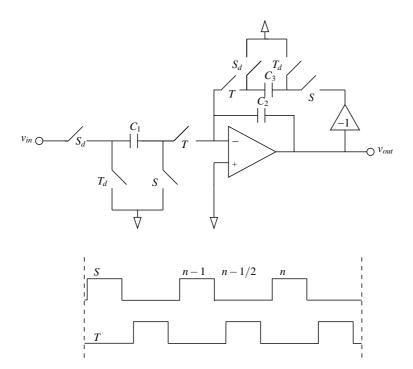

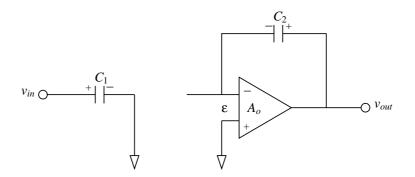

#### Le Filtre Amélioré

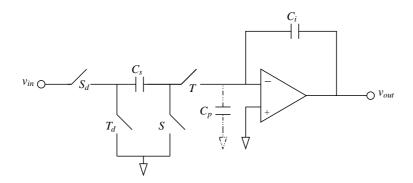

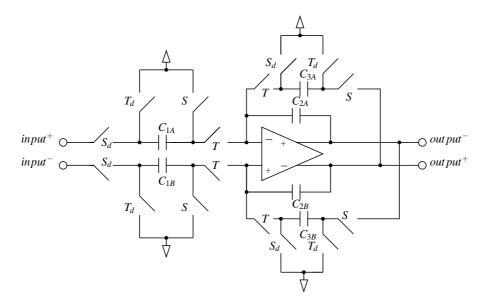

Une meilleure implémentation du filtre PH est proposée dans [29] et est représentée dans la Fig. 18. Cette mise en œuvre ne souffre pas des inconvénients des deux précédentes implémentations. L'opération de base est telle que la charge est échantillonnée sur  $C_{1A}$ au cours de la phase S. Sur la phase T, cette charge est transférée à  $C_{2A}$  pour les cycles d'horloge impairs et à  $C_{2B}$  sur des cycles d'horloge pairs.  $C_{1B}$  fonctionne d'une manière similaire.

Cette mise en œuvre est meilleure que le filtre à base d'intégrateur parce qu'il n'y a pas de boucle de rétroaction supplémentaire autour de l'intégrateur. Cela a des implications différentes avantageuses: elle prend beaucoup moins de superficie, il réduit la charge capacitive sur l'ampli-op et par conséquent la consommation d'énergie, il améliore les performances de bruit du filtre et il améliore la stabilité car elle ne dépend plus de l'appariement exact des condensateurs. Cette structure résout également le problème des bruits de basse fréquence associés à la structure à base de chopper, tout le traitement du signal est complété au niveau IF de fréquence, donc le DC-offset et le bruit 1/f ne bruitent plus le signal utile.

Figure 18: (a) Filtre PH amélioré, (b) Son chronogramme associé

#### La Comparaison Analytique

Les trois implémentations de filtre PH sont comparées théoriquement du point de vue de leur immunité contre le bruit du commutateur, le bruit d'ampli-op, les capacités parasites et non-idéalités d'ampli-op soit finie DC-gain, finie GBW et SR. Cette analyse est présentée de façon concise dans le Tableau. 1.

Ces résultats prouvent que le filtre PH amélioré est le meilleur parmi les trois implémentations. Non seulement il est à l'abri du bruit de scintillement et DC-offsets, il offre également la résistance maximum contre les bruits de commutateur, le bruit d'ampli-op et ces non-idéalités.

#### La Comparaison Pratique

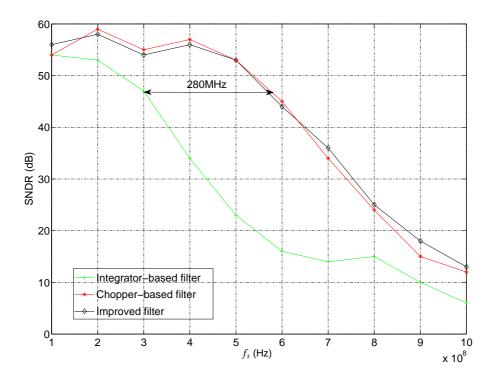

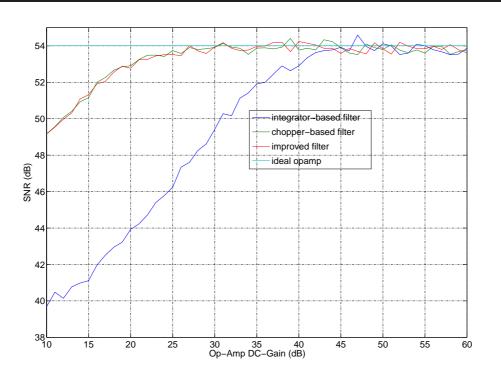

L'analyse comparative analytique est prouvée par la simulation des circuits avec le simulateur électrique: SPECTRE de Cadence. A cet effet, les modèles-macros des blocs de base sont utilisés. Dans la première expérience, on mesure le SNDR du modulateur en faisant varier la fréquence d'échantillonnage pour chaque type de filtre tout en gardant l'ampli-op GBW constant.

Le résultat se reflète dans la Fig. 19:

Cela montre que le filtre à base de chopper et le filtre amélioré peuvent fonctionner à

| Paramètre              | À Base d'Intégrateur                                   | À Base de Chopper                                      | Amélioré                                              |

|------------------------|--------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|

| Bruit Commutateur      | $\frac{5kT}{C_{\circ}}$                                | $\frac{4kT}{C_{\circ}}$                                | $\frac{4kT}{C_{e}}$                                   |

| Bruit Ampli-Op         | $41 \times \frac{\overline{e_{amp1}^2}}{F_s} \times B$ | $17 \times \frac{\overline{e_{amp1}^2}}{F_s} \times B$ | $1 \times \frac{\overline{e_{amp1}^2}}{F_s} \times B$ |

| DC-Gain Fini           | $\alpha = \frac{A_0}{A_0 + 3.5}$                       | $\alpha = \frac{A_0}{A_0 + 1.5}$                       | $\alpha = \frac{A_0}{A_0 + 1.5}$                      |

| GBW Fini               | $\tau = \frac{3+b}{2\pi GBW}$                          | $\tau = \frac{1+b}{2\pi GBW}$                          | $\tau = \frac{1+b}{2\pi GBW}$                         |

| Bruit de Scintillement | Non                                                    | Oui                                                    | Non                                                   |

| DC-Offset              | Non                                                    | Oui                                                    | Non                                                   |

| Superficie             | Elevée                                                 | Faible                                                 | Faible                                                |

Table 1: La performance de trois filtres PH en présence de bruit et de non-idéalités

Figure 19: Performance du modulateur PH proposé en utilisant trois filtres PH à haute fréquence d'échantillonnage

une fréquence d'échantillonnage qui est supérieure à 280MHz par rapport à la fréquence d'échantillonnage la plus élevées possible pour le filtre à base d'intégrateur en utilisant la même ampli-op. En d'autres termes, à la même consommation d'énergie, le modulateur réalisé avec un filtre à base d'intégrateur peut convertir moins de bande passante que le modulateur construit avec les deux autres topologies de filtre.

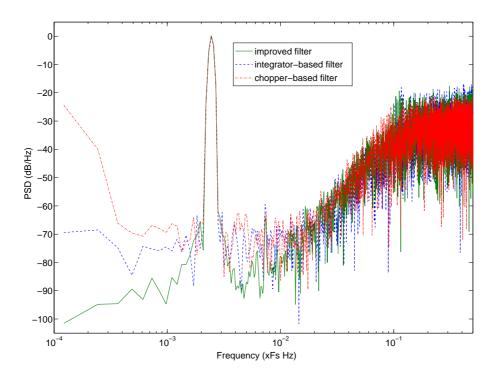

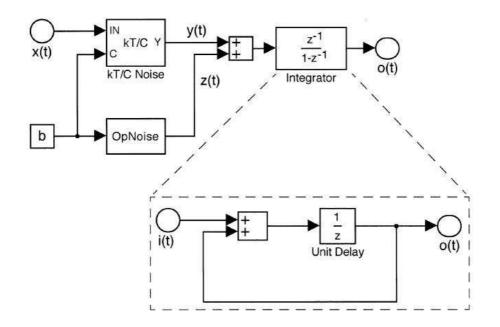

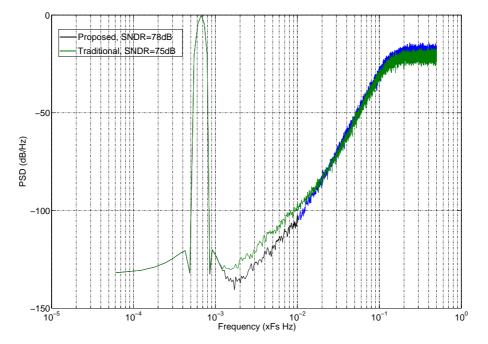

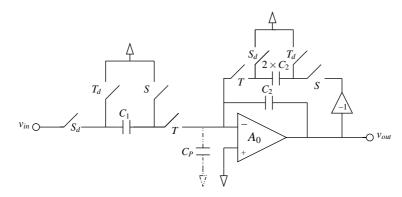

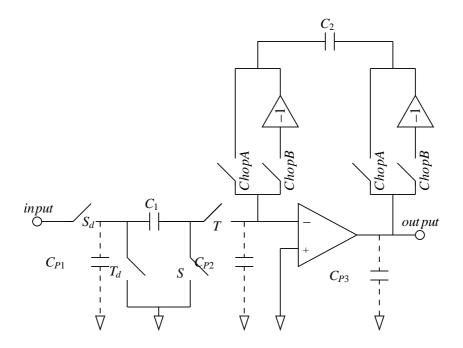

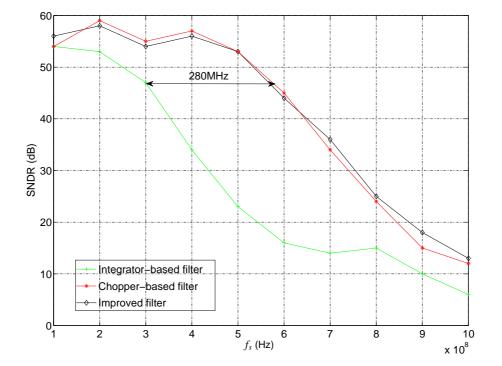

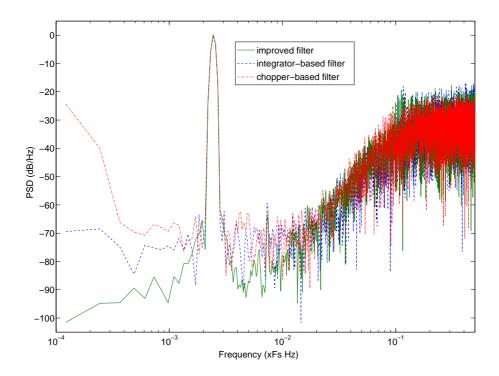

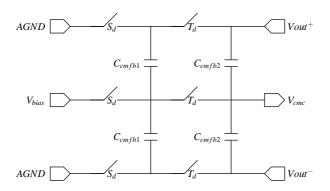

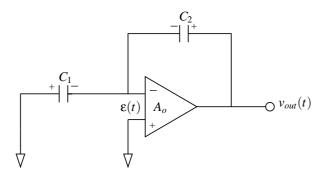

Dans la deuxième expérience, nous prouvons la réjection excellente du bruit obtenu par le filtre amélioré par rapport aux deux autres topologies. Le bruit de l'amplificateur opérationnel ramené à l'entrée a été généré en MATLAB. Il est injecté dans le circuit en ajoutant une source de tension à chaque entrée de l'ampli-op. Les valeurs de cette source de tension sont lues à partir de MATLAB. Le circuit pour le modulateur PH proposé, construit avec la topologie de filtre amélioré, y compris les sources de bruit de l'ampli-op est illustré dans la Fig. 20.

Figure 20: Injection de bruit dans le modulateur

$e_{amp}^+$  et  $e_{amp}^-$  sont les sources de bruit généré en MATLAB et lu directement dans SPECTRE. Le résultat de la simulation de l'injection du bruit dans les trois filtres est indiqué sur la Fig. 21.

Cette figure montre que le filtre à base d'intégrateur et le filtre amélioré réussissent à éviter le bruit de basse fréquence-bruit de scintillement, tandis que dans le filtre à base de chopper, le bruit de scintillement corrompt la bande du signal et en résulte la réduction de la SNR. Pour un OSR de 32, le filtre à base d'intégrateur, le filtre à base de chopper et le filtre amélioré donnent une SNDR de 55dB, 52dB et 21dB respectivement. Ainsi, 3dB de SNR est perdu à cause de la désavantageuse mise en forme du bruit d'ampli-op à haute fréquence dans la structure à base d'intégrateur et 30dB sont gaspillées en raison de la corruption du signal utile par le bruit à basse fréquence dans la structure à base de chopper. Ces caractéristiques font du filtre amélioré un choix idéal pour la grande vitesse et haute résolution à consommation réduite.

Figure 21: Spectre de sortie de modulateur en présence de bruit d'ampli-op pour les trois filtres

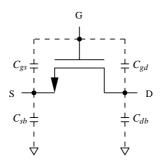

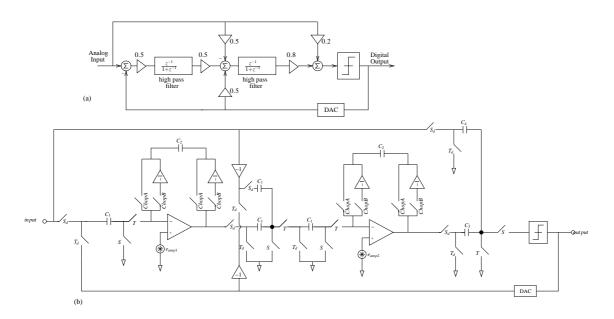

### La Conception en 65nm CMOS

Le CAN développé au niveau système dans les chapitres précédents a été conçu au niveau transistor en CMOS 65nm. Ce CAN est conçu pour satisfaire les exigences de performance des normes spécifiées dans le Tableau. :

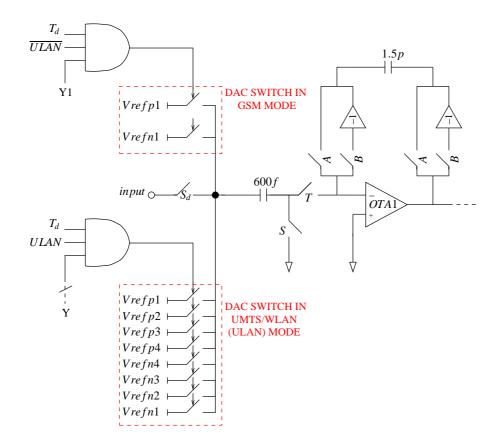

Au vu de la diversité des exigences de performance, il devient évident que le CAN doit être reconfigurable. La reconfiguration est fournie par le changement de la fréquence d'échantillonnage  $(F_s)$  et de l'ordre du modulateur (M). Dans le mode GSM/EDGE, puisque la bande passante du signal est faible, une  $F_s$  de 28.57MHz ( $OSR = \frac{28.57MHz}{2\times135KHz} \approx 105$ ) et une mise en forme du 2ème ordre du bruit avec un seul bit de quantification sont utilisés. Ainsi, le deuxième étage de la structure GMSCL PH est désactivée dans le mode GSM/EDGE pour réduire la consommation. Pour le mode de fonctionnement UMTS/WLAN, la fréquence d'échantillonnage est élevée à 228.57MHz et l'ordre du modulateur est porté à 4, avec un étage supplémentaire de quantificateur auxiliaire.

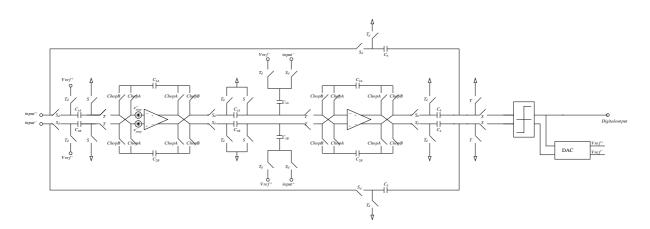

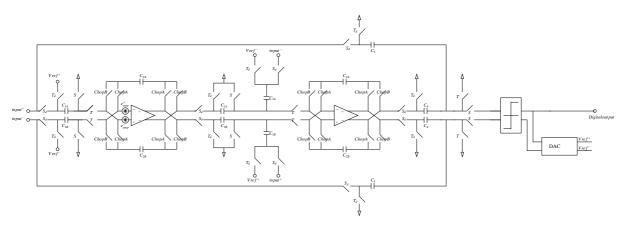

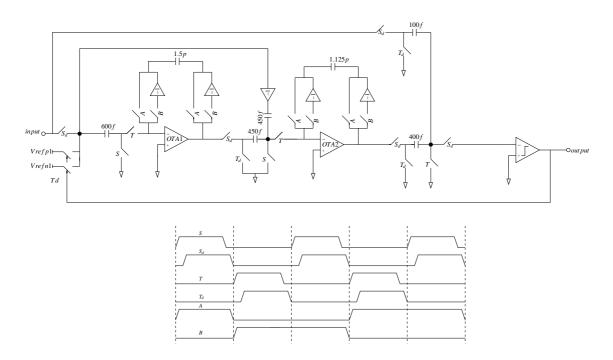

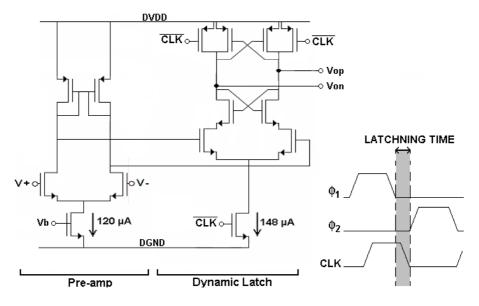

#### Le Schéma Global du Circuit

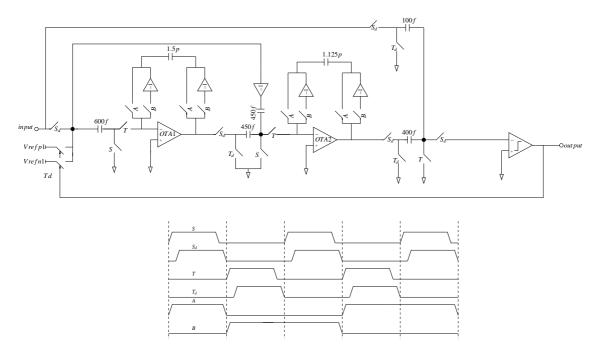

Le schéma du modulateur en mode GSM est présenté dans sa version non différentielle pour plus de simplicité dans la Fig. 22. Le commutateur d'entrée du modulateur est de type "bootstrap" pour satisfaire les exigences de linéarité. Les autres commutateurs sont des commutateurs CMOS. La capacité d'échantillonnage à l'entrée du modulateur est choisie

| Standard                            | <b>GSM/EDGE</b> | UMTS             | WLAN                |

|-------------------------------------|-----------------|------------------|---------------------|

| Taux de conversion                  | 270KHz          | 3.84MHz          | $25 \mathrm{MHz}$   |

| Bande passante du signal            | 135kHz          | 1.92MHz          | $12.5 \mathrm{MHz}$ |

| Fréquence d'échantillonnage $(F_s)$ | 28.57MHz        | 228.57MHz        | 228.57MHz           |

| Ordre du Modulateur $(P)$           | 2               | 4+aux. quantizer | 4+aux. quantizer    |

| SNR                                 | 80dB            | 80dB             | 52dB                |

Table 2: ADC Spécification

égale à 600fF pour répondre aux spécifications de bruit thermique.

Figure 22: Modulateur global non différentiel en mode GSM avec son chronogramme associé

Le modulateur utilisé est du 2ème ordre avec l'architecture proposée et un quantificateur 1 bit. Ce modulateur fournit les performances nécessaires de SNDR pour un OSR de 84. La taille des condensateurs diminue avec le flux de signal en raison de l'augmentation de la mise en forme du bruit.

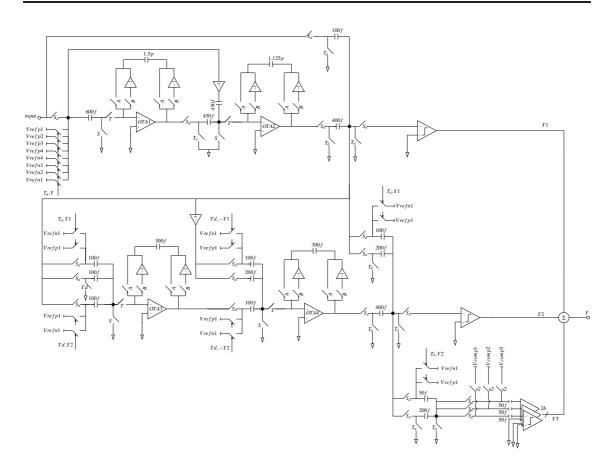

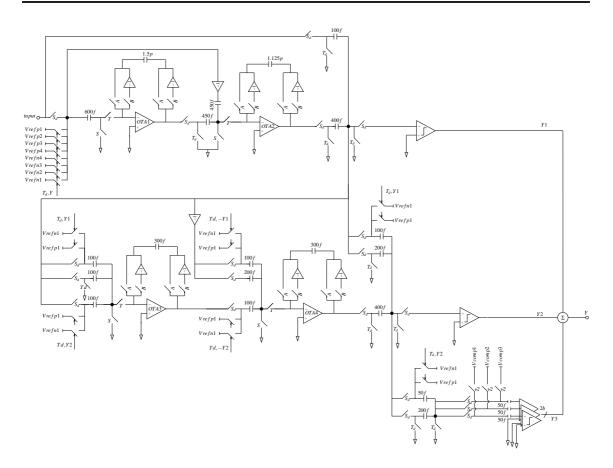

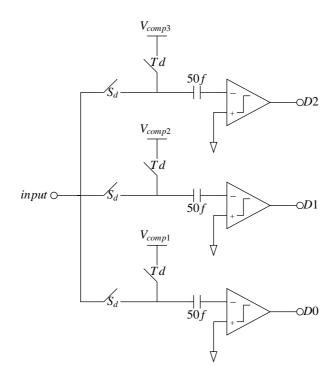

Le schéma du modulateur non différentiel en mode ULAN est présenté sur la Fig. 23. Il utilise la structure proposée-GMSCL PH avec une dynamique améliorée par l'ajout d'un quantificateur auxiliaire dans le dernier étage comme décrit précédemment.

La mise en œuvre au niveau transistor d'un CAN multi-mode fonctionnant sur le principe du modulation  $\Sigma\Delta$  passe-haut est présenté. Le CAN a deux modes de fonc-

Figure 23: Modulateur global non différentiel en mode UMTS/WLAN

tionnement: GSM/EDGE et UMTS/WLAN. Cette reconfiguration permet une économie d'énergie significative.

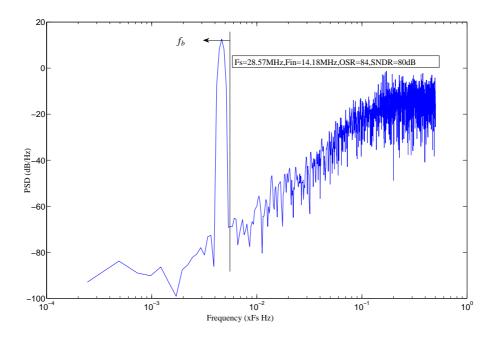

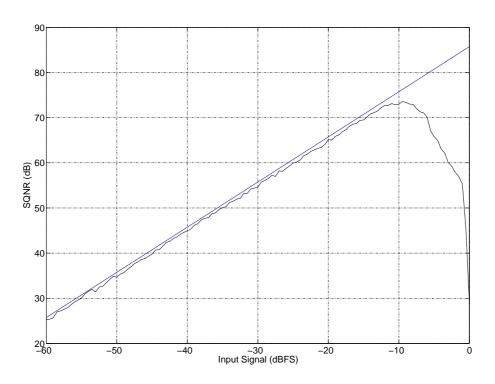

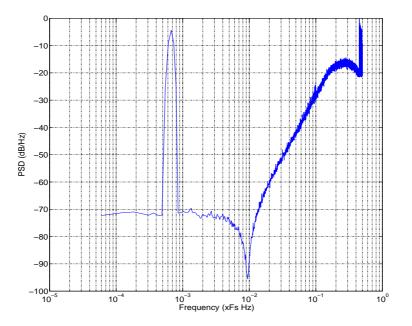

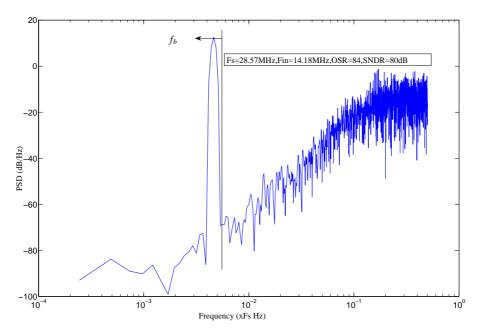

#### Les Résultats de Simulations

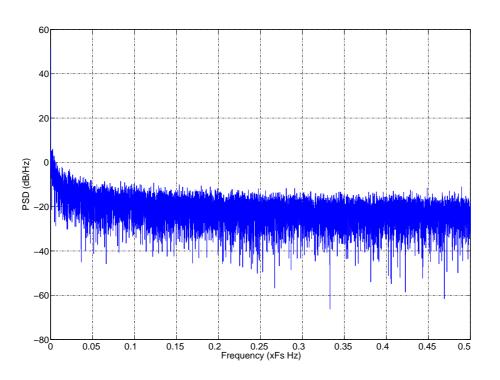

La simulation électrique avec des OTA (et le circuit CMFB), quantificateur et CNA implementés au niveau transistor est effectuée avec succès pour le mode GSM. Le spectre de sortie à l'entrée pleine échelle est illustré dans la Fig. 24. Comme présenté dans la figure, la résolution de 80-dB est atteinte à l'OSR minimum de 84 et de la fréquence d'échantillonnage de 28.57MHz.

Pour les modes UMTS/WiFi de fonctionnement, une distorsion importante est observée dans la bande du signal. Le résultat de la simulation propre de ces modes est prévu dans une extension éventuelle de ce travail de recherche.

Figure 24: Résultat de simulation en mode GSM

## Conclusion

La première partie de cette thèse a présenté les architectures de récepteur radio pour les systèmes de communication sans fil d'aujourd'hui du point de vue de la reconfiguration, intégrabilité et consommation d'énergie. Un pas en avant important vers la mise en œuvre de la notion de SDR sont les récepteurs d'échantillonnage RF qui utilisent le sous-échantillonnage pour réduire la fréquence de signal de RF à IF. De cette façon, le traitement du signal en temps discret, qui est fortement intégrable, est introduit dès le début. En utilisant le sous-échantillonnage, les exigences de vitesse sur les blocs suivants sont assouplies. Le défi dans ce scénario est le filtrage anti-repliements pour minimiser la corruption du signal par des brouilleurs en-bande et hors-bande. Ceci est accompli par des filtres à capacités commutées passifs. L'état de l'art des récepteurs utilise une downconversion en deux étapes, chaque étape à l'aide de sous-échantillonnage, afin de parvenir à un compromis acceptable entre la fréquence du signal abaissée en fréquence et le filtrage anti-repliement. Bien que, avec l'augmentation des performances des CAN, il est devenu possible d'utiliser la "downconversion" en une seule étape pour diminuer le nombre de composants. Le sous-échantillonnage est réalisé de telle manière que le signal est placé à  $F_s/2$  pour profiter des avantages des deux: zéro-IF et low-IF. Dans ce scénario, le candidat naturel pour le CAN est le modulateur  $\Sigma \Delta$  PH.

La deuxième partie de cette thèse a examiné l'état de l'art des modulateurs  $\Sigma\Delta$ . Commençant par des architectures classiques feed-back, ensuite les récentes architectures feedforward sont discutés avec leurs avantages et leur inconvénients. Les modulateurs d'ordre supérieur à boucle unique et modulateurs en plusieurs étages, qui sont inévitables pour des applications nécessitant une haute résolution, sont également exposés. La modélisation au niveau du système du modulateur classique: Boser second ordre [12] est effectuée afin de démontrer les exigences relatives pour les ampli-op dans cette topologie.

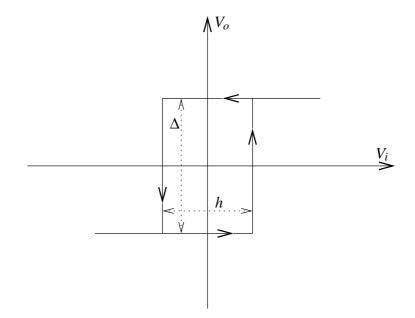

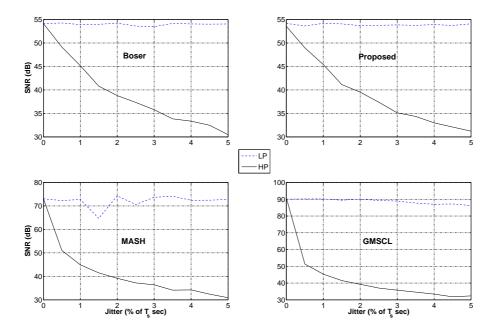

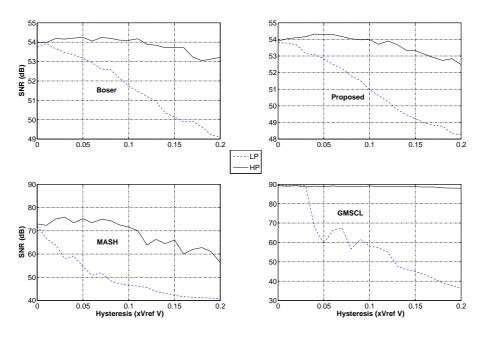

La troisième partie est liée à l'étude du modulateur  $\Sigma\Delta$  PH. Ce dernier rejette le bruit de quantification en basse fréquence. La bande du signal est située à environ la moitié de la fréquence d'échantillonnage, il est donc compatible avec le récepteur  $F_s/2$  IF en temps discret et, en outre, totalement à l'abri des DC-offsets et du bruit de scintillement. Diverses topologies existantes de modulateur  $\Sigma\Delta$  passe-bas sont présentées après leur adaptation au fonctionnement PH, et une nouvelle architecture du second ordre avant une STF unitaire est proposée. Elle soulage les problèmes liés à l'architecture traditionnelle feedforward en supprimant la nécessité d'un additionneur actif. Une nouvelle technique pour concevoir des structures en cascade ou MASH est également proposée ce qui augmente la dynamique en entrée du modulateur. Cette technique est basée sur l'étude systématique du gain de quantification du premier étage et l'adaptation de filtres numériques avec ce gain. Un état de l'art des architectures des modulateurs  $\Sigma\Delta$  multi-étages, ce qui est libre de filtres numériques d'annulation, appelé Generalized-Multi-Stage-Closed-Loop (GMSCL) est conçu pour un fonctionnement PH. Enfin, un quantificateur auxiliaire est ajouté dans le deuxième étage, afin d'augmenter la gamme dynamique en entrée et de diminuer l'effet des non-linéarités du CAN global. Une comparaison entre les modulateurs  $\Sigma\Delta$  PH et passe-bas est également réalisée. Elle révèle que les modulateurs PH sont plus sensibles à la gigue d'horloge ce qui augmente les contraintes sur le circuit de génération d'horloge. Les modulateurs passe-bas d'autre part sont de plus en plus sensibles à l'hystérésis dans le comparateur nécessitant un plan pour réduire les exigences sur le comparateur.

La quatrième partie de ce travail de recherche visait à sélectionner la meilleure architecture du filtre PH qui est l'élément de base de modulateur  $\Sigma\Delta$  PH. Après une analyse comparative approfondie des trois topologies en compétition, celle qui a été introduite récemment et basée sur l'alternance des condensateurs est sélectionnée. Ses avantages de réduction de la consommation et du bruit sont prouvés analytiquement et par simulations.

Enfin, une implementation multi-standard, multi-mode d'un CAN en CMOS 65nm est présentée. Il a trois modes de fonctionnement: GSM, UMTS et WiFi/WiMax. En mode GSM, le modulateur  $\Sigma\Delta$  PH de second ordre proposé est utilisé, tandis que pour l'UMTS et le WiFi/WiMax le modulateur GMSCL PH du quatrième ordre avec un quantificateur auxiliaire est utilisé pour la conversion.

# Contents

| 1        | Introduction                                         |                                                                                                           |          |  |  |  |

|----------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|

|          | 1.1                                                  | Motivation and Goals                                                                                      | 39       |  |  |  |

|          | 1.2                                                  | Organization                                                                                              | 40       |  |  |  |

| <b>2</b> | $\mathbf{RF}$                                        | F Receiver Architecture 43                                                                                |          |  |  |  |

|          | 2.1                                                  | Introduction                                                                                              | 43       |  |  |  |

|          | 2.2                                                  | Superheterodyne Receiver                                                                                  | 44       |  |  |  |

|          | 2.3                                                  | 0                                                                                                         | 45       |  |  |  |

|          | 2.4                                                  | Direct Conversion Receiver                                                                                | 46       |  |  |  |

|          | 2.5                                                  | Low-IF Receiver                                                                                           | 48       |  |  |  |

|          | 2.6                                                  | Bandpass Sampling Receiver                                                                                | 49       |  |  |  |

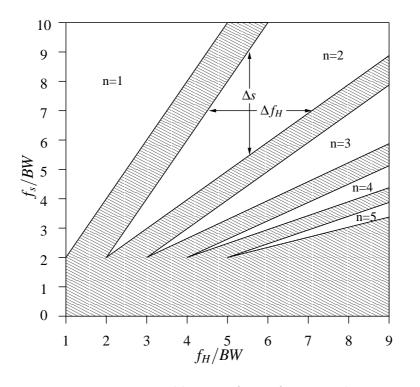

|          |                                                      | 2.6.1 Theory of bandpass sampling                                                                         | 50       |  |  |  |

|          |                                                      |                                                                                                           | 51       |  |  |  |

|          |                                                      | 1 0                                                                                                       | 53       |  |  |  |

|          |                                                      |                                                                                                           | 55       |  |  |  |

|          |                                                      |                                                                                                           | 57       |  |  |  |

|          |                                                      | 0                                                                                                         | 57       |  |  |  |

|          |                                                      | 0                                                                                                         | 58       |  |  |  |

|          |                                                      | 1 5                                                                                                       | 59       |  |  |  |

|          |                                                      |                                                                                                           | 60<br>61 |  |  |  |

|          | 2.7                                                  | .7 Conclusion                                                                                             |          |  |  |  |

| 3        | 3 $\Delta\Sigma$ Modulator and System Level Modeling |                                                                                                           |          |  |  |  |

|          | 3.1 Introduction                                     |                                                                                                           |          |  |  |  |

|          | 3.2 Working Principle                                |                                                                                                           | 64       |  |  |  |

|          |                                                      | 3.2.1 Stability $\ldots$ | 67       |  |  |  |

|          | 3.3                                                  | Second-Order $\Delta\Sigma$ Modulator Architectures                                                       | 68       |  |  |  |

|          |                                                      | 3.3.1 Boser Structure                                                                                     | 68       |  |  |  |

|          |                                                      | 3.3.1.1 Linear Analysis                                                                                   | 69       |  |  |  |

|          |                                                      | 3.3.1.2 Disadvantage of Boser Structure                                                                   | 70       |  |  |  |

|          |                                                      | 3.3.2 Silva Structure                                                                                     | 70       |  |  |  |

|          |                                                      | 3.3.2.1 Linear Analysis                                                                                   | 71       |  |  |  |

|          |                                                      | 3.3.2.2 Disadvantages of Silva Structure                                                                  | 71       |  |  |  |

|   |     | 3.3.3  | Oberst S           | Structure                                                  | 71  |  |  |

|---|-----|--------|--------------------|------------------------------------------------------------|-----|--|--|

|   |     |        | 3.3.3.1            | Linear Analysis                                            | 72  |  |  |

|   |     |        | 3.3.3.2            | Disadvantages of Oberst Structure                          | 72  |  |  |

|   | 3.4 | Higher | -Order $\Delta$    | $\Sigma$ Modulator Architectures                           | 73  |  |  |

|   |     | 3.4.1  |                    | oop Higher-Order                                           | 73  |  |  |

|   |     |        | 3.4.1.1            | Cascade of integrators with distributed feedback (CIFB)    |     |  |  |

|   |     |        |                    | structure                                                  | 74  |  |  |

|   |     |        | 3.4.1.2            | Cascade of resonators with distributed feedback (CRFB)     |     |  |  |

|   |     |        |                    | structure                                                  | 75  |  |  |

|   |     |        | 3.4.1.3            | Cascade of integrators with distributed feedforward (CIFF) |     |  |  |

|   |     |        |                    | structure                                                  | 75  |  |  |

|   |     |        | 3.4.1.4            | Cascade of resonators with distributed feedforward (CRFF)  |     |  |  |

|   |     |        |                    | structure                                                  | 76  |  |  |

|   |     | 3.4.2  | Multi-St           | age Modulators                                             | 76  |  |  |

|   |     | 3.4.3  |                    | Cascade 2-1 MASH Structure                                 | 77  |  |  |

|   |     |        | 3.4.3.1            | Linear Analysis                                            | 78  |  |  |

|   |     | 3.4.4  |                    | d MASH Structures                                          | 79  |  |  |

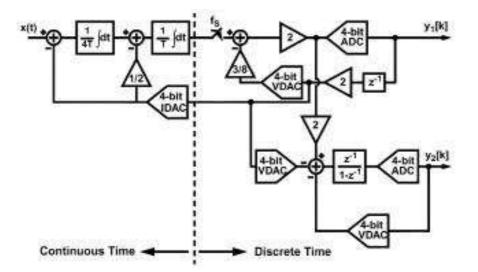

|   | 3.5 | Multik |                    | ators                                                      | 80  |  |  |

|   | 3.6 |        |                    | he and Hybrid (Continuous Time/Discrete Time) Modulators   | 82  |  |  |

|   | 3.7 |        |                    |                                                            |     |  |  |

|   |     | 3.7.1  |                    | tter                                                       | 85  |  |  |

|   |     | 3.7.2  |                    | and Op-Amp Noise                                           | 85  |  |  |

|   |     |        | 3.7.2.1            | Switch Thermal Noise                                       | 85  |  |  |

|   |     |        | 3.7.2.2            | Op-amp Noise                                               | 87  |  |  |

|   |     | 3.7.3  | Op-amp             | Non-Idealities                                             | 87  |  |  |

|   |     |        | 3.7.3.1            | Saturation                                                 | 87  |  |  |

|   |     |        | 3.7.3.2            | Finite DC-Gain                                             | 89  |  |  |

|   |     |        | 3.7.3.3            | Finite Gain-Bandwidth Product and Slew Rate                | 91  |  |  |

|   |     | 3.7.4  | Compara            | ator Non-Idealities                                        | 93  |  |  |

|   | 3.8 | Conclu | usion              |                                                            | 96  |  |  |

|   |     |        |                    |                                                            |     |  |  |

| 4 | -   |        | $\Delta \Sigma$ Mo |                                                            | 97  |  |  |

|   | 4.1 |        |                    |                                                            | 97  |  |  |

|   | 4.2 |        |                    |                                                            | 97  |  |  |

|   | 4.3 |        | -                  | $P \Delta \Sigma$ Modulator Structures                     | 99  |  |  |

|   |     | 4.3.1  |                    | ased Structure                                             | 99  |  |  |

|   |     | 4.3.2  |                    | sed Structure                                              |     |  |  |

|   |     | 4.3.3  |                    |                                                            | 101 |  |  |

|   |     | 4.3.4  | -                  | d Unity-STF Structure                                      |     |  |  |

|   |     |        | 4.3.4.1            | Linear Analysis                                            |     |  |  |

|   | 4 4 | C      | 4.3.4.2            | Refining the Proposed Architecture                         |     |  |  |

|   | 4.4 | -      |                    | nalysis of Single-Loop HP Modulators                       |     |  |  |

|   |     | 4.4.1  | -                  | ss Filter Output Excursion                                 |     |  |  |

|   |     | 4.4.2  | Op-Amp             | Non-Idealities Effect                                      | 110 |  |  |

|   |                                 |         | 4.4.2.1 Finite DC-Gain                                                                                                                      |     |  |  |  |  |  |

|---|---------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

|   |                                 |         | 4.4.2.2 Finite Gain-Bandwidth Product and Slew Rate                                                                                         |     |  |  |  |  |  |

|   | 4.5                             | Multi-  | Stage HP $\Delta\Sigma$ Modulator Structures                                                                                                |     |  |  |  |  |  |

|   |                                 | 4.5.1   | Cascade 2-1 HP Delta Sigma Modulator Structure                                                                                              |     |  |  |  |  |  |

|   |                                 | 4.5.2   | Quantizer Linear Model and Quantizer Gain Calculation                                                                                       |     |  |  |  |  |  |

|   |                                 | 4.5.3   | Quantization Noise Cancellation Filters' Designing                                                                                          |     |  |  |  |  |  |

|   |                                 |         | 4.5.3.1 Second-Stage Quantizer Gain $G2$                                                                                                    |     |  |  |  |  |  |

|   |                                 |         | 4.5.3.2 First-Stage Quantizer Gain $G1$                                                                                                     |     |  |  |  |  |  |

|   |                                 | 4.5.4   | Generalized Multi Stage Close Loop                                                                                                          |     |  |  |  |  |  |

|   |                                 | 4.5.5   | Generalized Multi Stage Close Loop with Extended Dynamic Range                                                                              | 122 |  |  |  |  |  |

|   | 4.6                             | Conclu  | $sion \ldots \ldots$ | 125 |  |  |  |  |  |

| 5 | High-Pass Filter Implementation |         |                                                                                                                                             |     |  |  |  |  |  |

|   | 5.1                             | Introd  | uction                                                                                                                                      | 129 |  |  |  |  |  |

|   | 5.2                             | Integra | ator-based Structure                                                                                                                        | 130 |  |  |  |  |  |

|   |                                 | 5.2.1   | Switch Noise                                                                                                                                | 130 |  |  |  |  |  |

|   | 5.3                             | Op-An   | np Noise                                                                                                                                    | 132 |  |  |  |  |  |

|   |                                 | 5.3.1   | Parasitic Capacitances                                                                                                                      | 136 |  |  |  |  |  |

|   |                                 | 5.3.2   | Op-Amp Non-Idealities                                                                                                                       | 138 |  |  |  |  |  |

|   |                                 |         | 5.3.2.1 Finite DC-Gain                                                                                                                      | 138 |  |  |  |  |  |

|   |                                 |         | 5.3.2.2 Finite Gain-Bandwidth Product and Slew Rate                                                                                         | 139 |  |  |  |  |  |

|   | 5.4                             | Chopp   | er-based Structure                                                                                                                          | 141 |  |  |  |  |  |

|   |                                 | 5.4.1   | Switch Noise                                                                                                                                | 141 |  |  |  |  |  |

|   |                                 | 5.4.2   | Op-Amp Noise                                                                                                                                | 142 |  |  |  |  |  |

|   |                                 | 5.4.3   | Parasitic Capacitances                                                                                                                      |     |  |  |  |  |  |

|   |                                 | 5.4.4   | Op-Amp Non-Idealities                                                                                                                       |     |  |  |  |  |  |

|   |                                 |         | 5.4.4.1 Finite DC-Gain                                                                                                                      |     |  |  |  |  |  |

|   |                                 |         | 5.4.4.2 Finite Gain-Bandwidth Product and Slew Rate                                                                                         |     |  |  |  |  |  |

|   | 5.5                             | -       | ved Structure                                                                                                                               | 149 |  |  |  |  |  |

|   |                                 | 5.5.1   | Switch Noise                                                                                                                                | 150 |  |  |  |  |  |

|   |                                 | 5.5.2   | Op-Amp Noise                                                                                                                                |     |  |  |  |  |  |

|   |                                 | 5.5.3   | Parasitic Capacitances                                                                                                                      | 154 |  |  |  |  |  |

|   |                                 | 5.5.4   | Op-Amp Non-Idealities                                                                                                                       |     |  |  |  |  |  |

|   |                                 |         | 5.5.4.1 Finite DC-Gain                                                                                                                      |     |  |  |  |  |  |

|   |                                 |         | 5.5.4.2 Finite Gain-Bandwidth Product and Slew Rate                                                                                         |     |  |  |  |  |  |

|   |                                 | 5.5.5   | High Frequency Performance Analysis                                                                                                         |     |  |  |  |  |  |

|   |                                 | 5.5.6   | Noise Analysis                                                                                                                              |     |  |  |  |  |  |

|   |                                 |         | 5.5.6.1 Noise Generation $\ldots \ldots \ldots$                       |     |  |  |  |  |  |

|   |                                 |         | 5.5.6.2 Noise Injection in Circuit                                                                                                          |     |  |  |  |  |  |

|   | 5.6                             | -       | arative Analysis between Low-Pass and High-Pass $\Delta\Sigma$ Modulators                                                                   |     |  |  |  |  |  |

|   |                                 | 5.6.1   | Clipping                                                                                                                                    |     |  |  |  |  |  |

|   |                                 | 5.6.2   | Op-Amp DC-Gain                                                                                                                              |     |  |  |  |  |  |

|   |                                 | 5.6.3   | Op-Amp GBW and SR                                                                                                                           |     |  |  |  |  |  |

|   |                                 | 5.6.4   | Clock Jitter                                                                                                                                | 163 |  |  |  |  |  |

|   |                                 |         |                                                                                                                                             |     |  |  |  |  |  |

|              | 5.7                                                                 | 5.6.5 Comparator Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |  |  |  |  |  |  |