# Conversion analogique numérique Sigma Delta reconfigurable à entrelacement temporel

Chadi Jabbour

#### ▶ To cite this version:

Chadi Jabbour. Conversion analogique numérique Sigma Delta reconfigurable à entrelacement temporel. Electronics. Télécom ParisTech, 2010. English. NNT: . pastel-00609650

### HAL Id: pastel-00609650 https://pastel.hal.science/pastel-00609650

Submitted on 19 Jul 2011

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Reconfigurable Parallel Delta Sigma Analog to Digital Converters

Chadi Jabbour

Supervisors: Van Tam Nguyen Patrick Loumeau

July 19, 2011

### Remerciments

Cette thèse a été menée au sein du groupe SIAM (systèmes intégrés analogiques et mixtes) du département COMELEC (communication et électronique) à Télécom ParisTech. J'adresse tout d'abord mes remerciements au Professeur Patrick Loumeau, coordinateur du groupe SIAM et directeur de ma thèse et à Dr. Van Tam Nguyen co-directeur de ma thèse, pour la confiance et le soutien qu'ils ont su m'accorder tout le long de ces trois ans. Merci beaucoup Patrick, Merci Beaucoup Van Tam.

Je voudrais aussi adresser mes sincères remerciements à mes rapporteurs Professeurs Georges Gielen et Andreas Kaizer pour le regard critique et les remarques constructives qu'ils ont amené à ce travail. Je remercie également le Professeur Patrick Garda d'avoir accepter de présider mon jury de thèse et Dr. Dominique Morche et Dr. Patrice Gamand pour avoir examiné mes travaux.

J'aimerai profiter aussi pour remercier tous les permanents du Groupe SIAM et surtout Hervé Petit pour sa gentillesse et sa disponibilité.

Je tiens à remercier énormément tous mes collègues et amis avec qui j'ai eu l'immense chance de travailler. Je remercie d'abord David Camarero et Hussein Fakhoury qui m'ont énormément appris et qui m'ont surtout transmis cette passion pour le Slew rate et le Bootstrap. Je remercie également Hasham Khushk et Ali Beydoun avec qui le travail était une vraie partie de plaisir. Je remercie aussi Fatima Ghanem et Germain Pham (42) qui ont dû penser profiter de moi au bon sens du terme mais je vous assure que ça fut réciproque.

Un très grand merci à tous mes amis à l'école pour tous les moments qu'on a passé ensemble, pour toutes les discussions souvent tordues pendant les déjeuners, pour tous les gâteaux parfois ratés qu'on a pu manger pendant les pauses cafés, pour tous les matchs de foot et de ping pong, pour tous les footings, pour toutes les soirées plus ou moins arrosées. Vraiment merci Alban, Ali, Anis, Antoine, Asma, Corina, Davi, David, Denis, Dimitri, Eric, Fatima, Farhan, Germain, Gutenberg, Hasham, Lina, Mai, Manel, Marcia, Mariem, Maya, Michel, Mireille, Mélanie, Qing, les 2 Sami, Shivam, Sumantha, Yang, Zizou, et à tous ceux que j'ai pu oublié. (Le classement des noms s'est fait par ordre croissant d'intelligence)

Finalement, et surtout pour éviter de se faire déshériter, je remercie, bien sûr, mes parents et ma famille pour leur support inconditionné et leur implication pour l'aboutissement de ce travail.

### Abstract

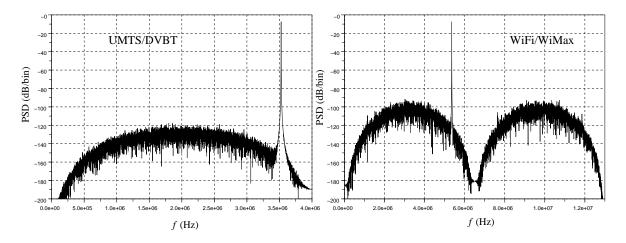

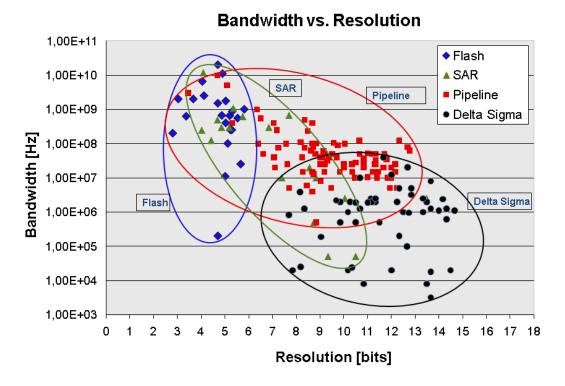

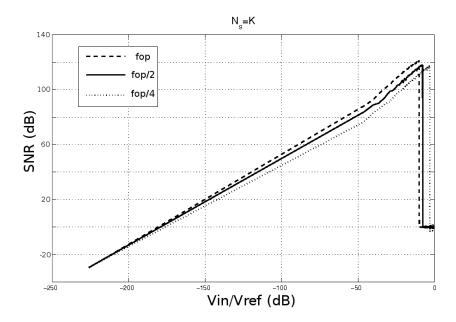

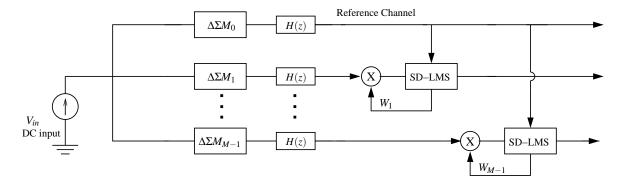

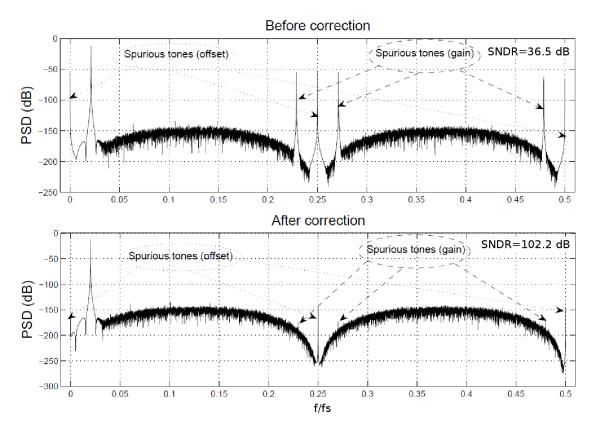

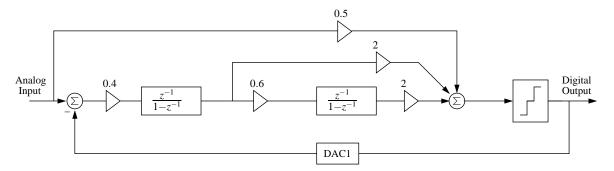

Nowadays, communication devices are supporting an increasing number of standards. The diversity of the requirements in terms of speed and resolution, makes the design of a single low power analog to digital converter (ADC) suitable for all the scenarios very problematic. Reconfigurable ADCs are a solution to this problem, where resolution would be exchanged for bandwidth. Classical  $\Delta\Sigma$  ADCs offer an easy way to perform this exchange by adjusting their oversampling ratios. However, they are not suitable for wideband applications. Parallelizing  $\Delta\Sigma$  ADCs overcomes this problem and in addition, increases the reconfigurability of the ADC.

In this work, a fully reconfigurable Time-interleaved  $\Delta\Sigma$  ADC is proposed. Its reconfigurability permits it to perform resolution-bandwidth trade-off as well as power consumption-bandwidth trade-off by adjusting the operation frequency, the number of active channels, the oversampling ratio and the modulator order. A novel interpolation technique is also proposed. It allows to downscale the capacitor sizes that may otherwise reach unreasonable values if large resolutions are required and relaxes the constraints on the anti-alias filter as well.

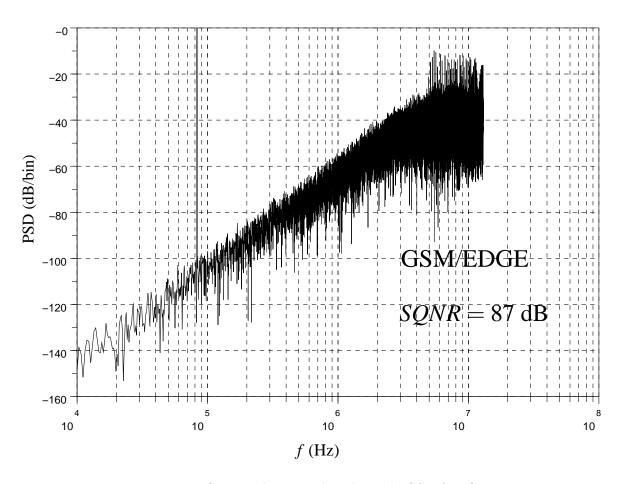

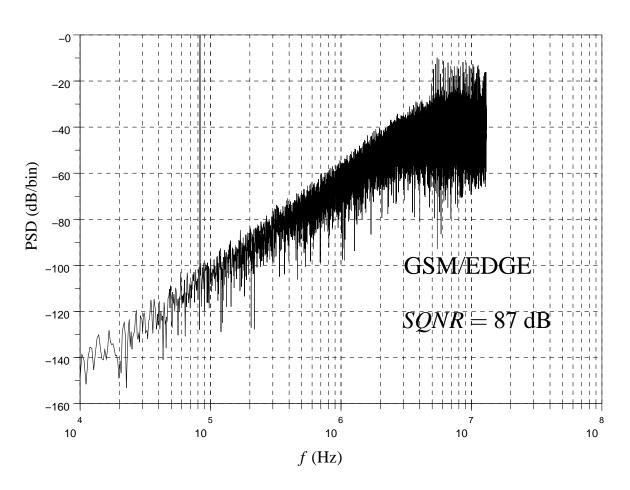

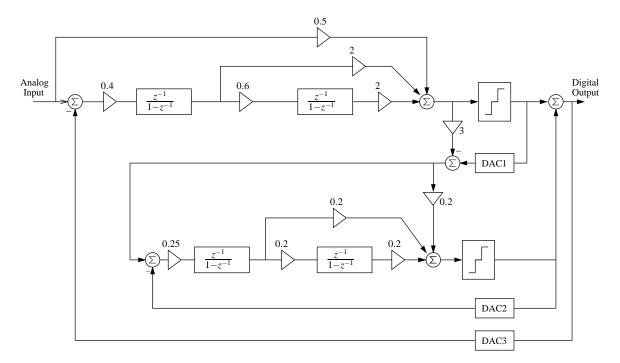

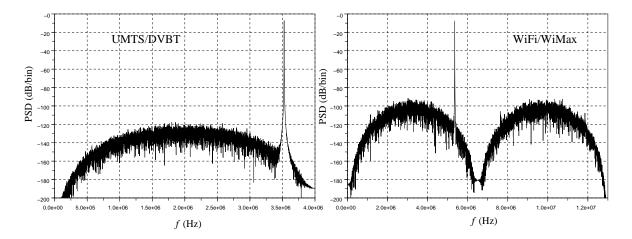

A prototype of the presented Time-interleaved  $\Delta\Sigma$  ADC has been realized in a 1.2 V 65 nm CMOS technology. It was designed to fulfill the requirements of GSM, EDGE, UMTS, DVBT, WiFi and WiMax standards. For the GSM/EDGE scenario, a 80 dB SNR was measured. For the rest of scenarios, the performances were not secured but the functionality was tested successfully.

# Contents

| Re | emer           | ciment            | SS .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iii          |

|----|----------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Al | ostra          | ct                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{v}$ |

| Li | st of          | Abbre             | veriations and Symbols         xi           ngais         xiiii           tion         3           vations         3           mization         4           ributions         5           m         7           r consumption vs frequency         7           rbacks of parallel circuits         11           Time-interleaved circuits         11           2.2.1.1 Gain mismatch         12           2.2.1.2 Offset mismatch         13           2.2.1.3 Clock skew         13           2.2.1.4 Bandwidth mismatch         15           Frequency interleaved circuits         16           dusion         17           ulators         19           operation         19           General         19           Noise shaping         21           Resolution and stability         22           rete time vs continuous time vs Hybrid         23           Operation         24           3.2.1.1 Discrete Time Modulators         24           3.2.1.2 Continuous Time Modulators         24           3.2.1.3 Hybrid Modulators         24           3.2.1.3 Hybrid Modulators         24           Coeffi |              |

| Re | ésum           | é Fran            | çais                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xiii         |

| 1  | Intr           | oducti            | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3            |

|    | 1.1            | Motiva            | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3            |

|    | 1.2            | Organ             | <mark>ization</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4            |

|    | 1.3            | Contri            | butions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5            |

| 2  | Para           | allelisn          | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7            |

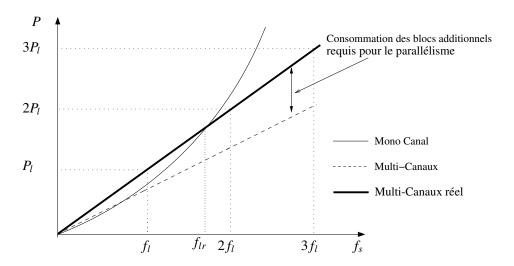

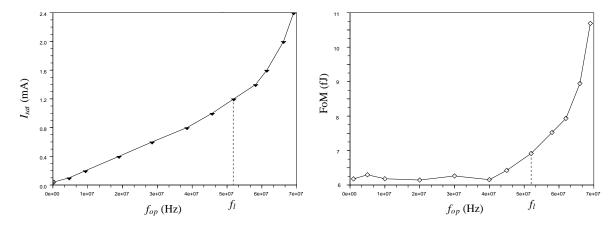

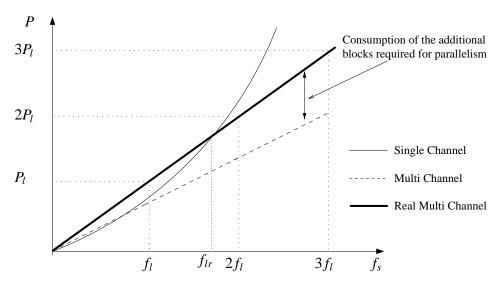

|    | 2.1            | Power             | consumption vs frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7            |

|    | 2.2            | Drawb             | packs of parallel circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11           |

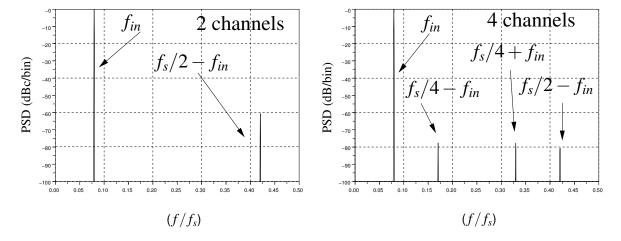

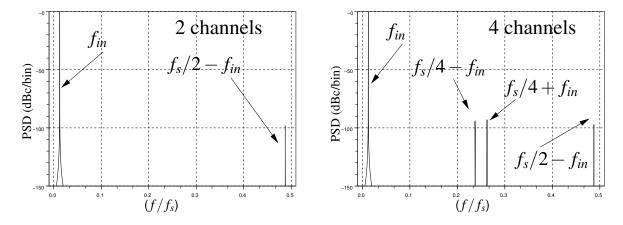

|    |                | 2.2.1             | Time-interleaved circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11           |

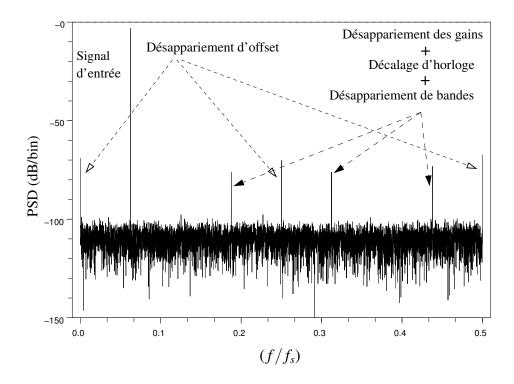

|    |                |                   | 2.2.1.1 Gain mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12           |

|    |                |                   | 2.2.1.2 Offset mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13           |

|    |                |                   | 2.2.1.3 Clock skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13           |

|    |                |                   | 2.2.1.4 Bandwidth mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15           |

|    |                | 2.2.2             | Frequency interleaved circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16           |

|    | 2.3            | Conclu            | <u>ısion</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17           |

| 3  | $\Delta\Sigma$ | Modul             | lators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19           |

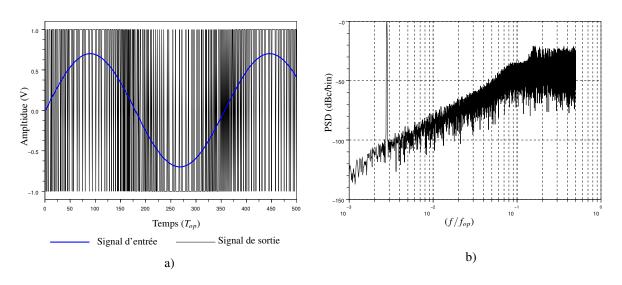

|    | 3.1            | $\Delta\Sigma$ op | peration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19           |

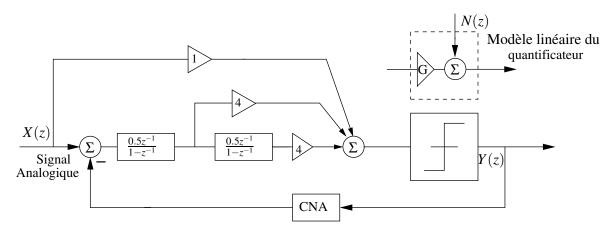

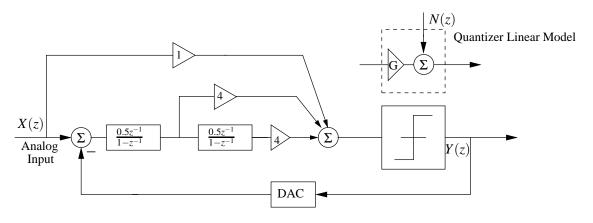

|    |                | 3.1.1             | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19           |

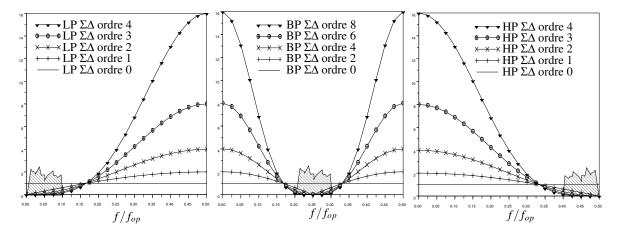

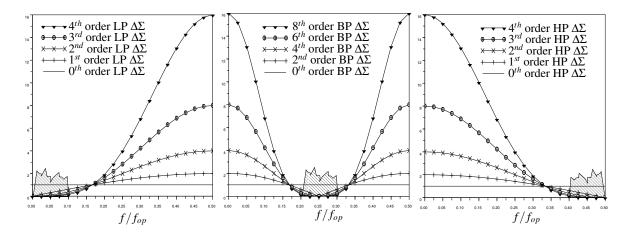

|    |                | 3.1.2             | Noise shaping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21           |

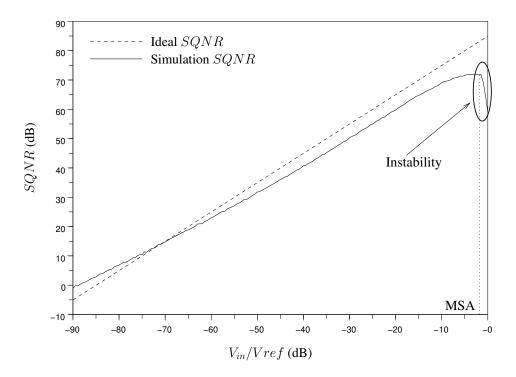

|    |                | 3.1.3             | Resolution and stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22           |

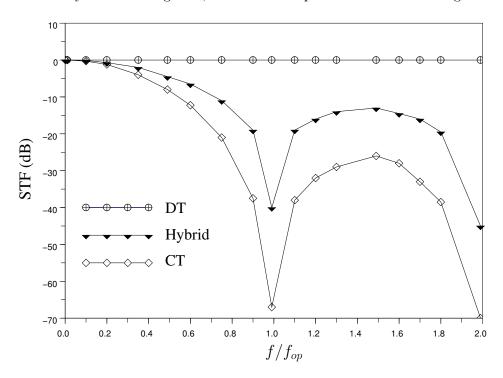

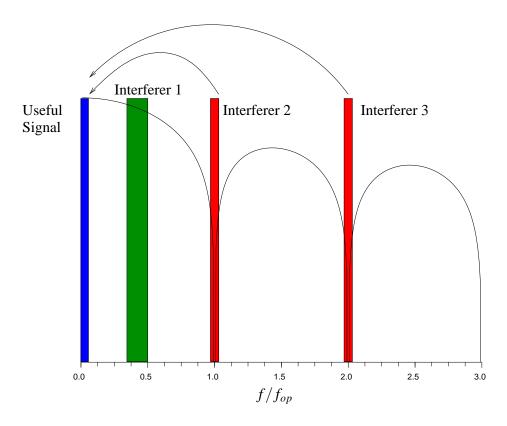

|    | 3.2            | Discre            | ete time vs continuous time vs Hybrid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23           |

|    |                | 3.2.1             | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24           |

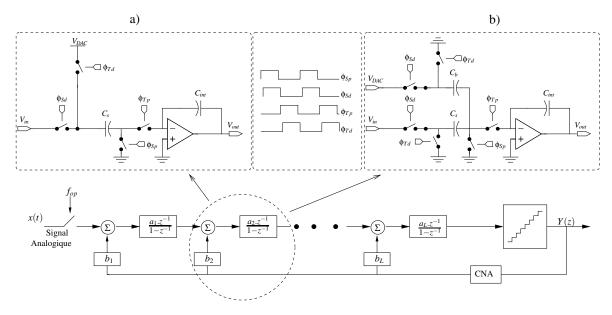

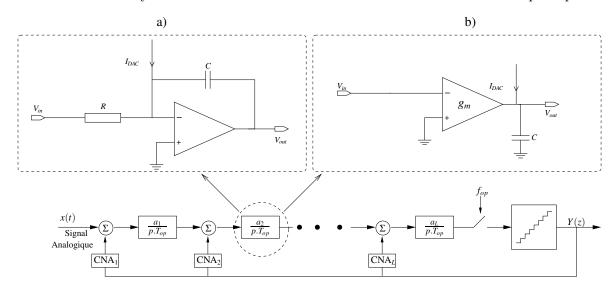

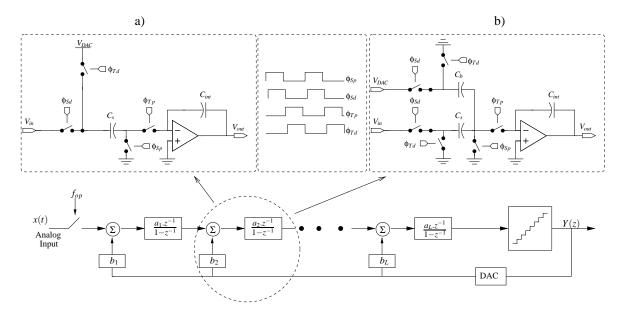

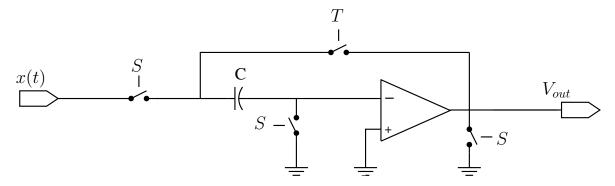

|    |                |                   | 3.2.1.1 Discrete Time Modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

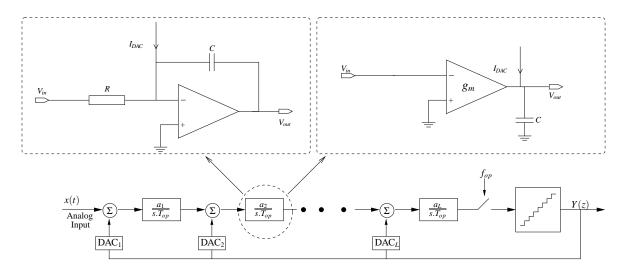

|    |                |                   | 3.2.1.2 Continuous Time Modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24           |

|    |                |                   | 3.2.1.3 Hybrid Modulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|    |                | 3.2.2             | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|    |                | 3.2.3             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

|    |                | 3.2.4             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

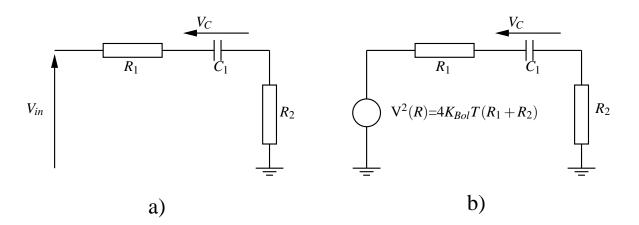

|    |                | 3.2.5             | Thermal noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30           |

viii CONTENTS

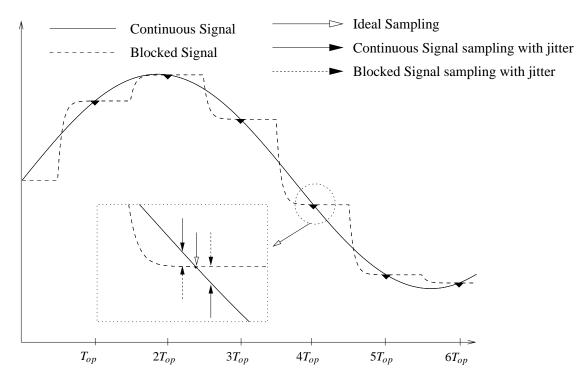

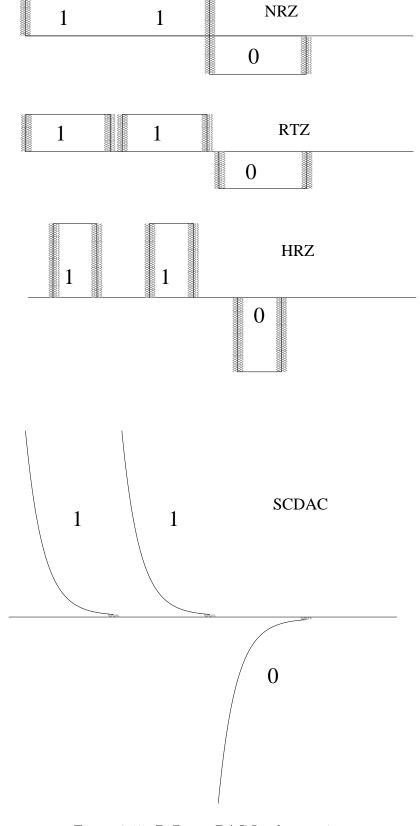

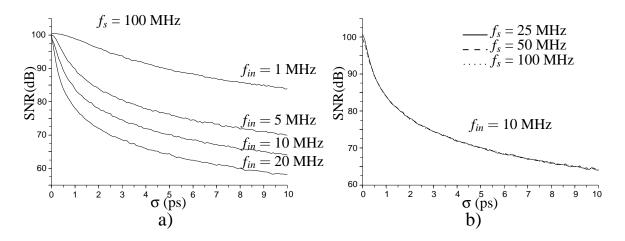

|   |     | 3.2.6   | Jitter                                                                         |

|---|-----|---------|--------------------------------------------------------------------------------|

|   |     |         | 3.2.6.1 Switches                                                               |

|   |     |         | 3.2.6.2 Quantizer                                                              |

|   |     |         | 3.2.6.3 DAC                                                                    |

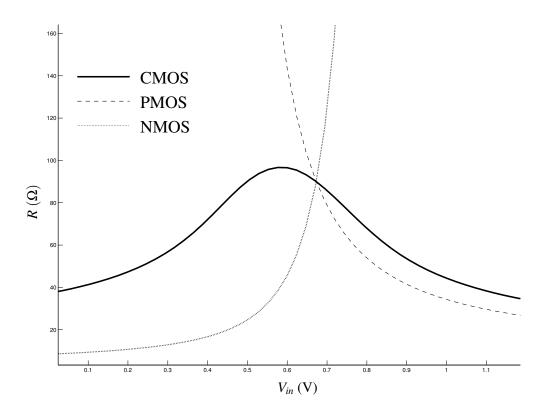

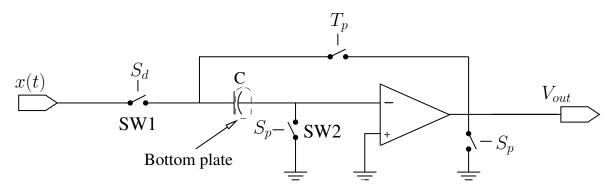

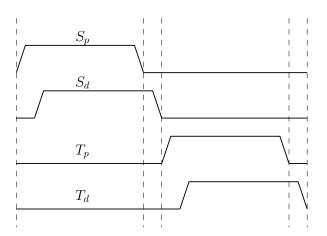

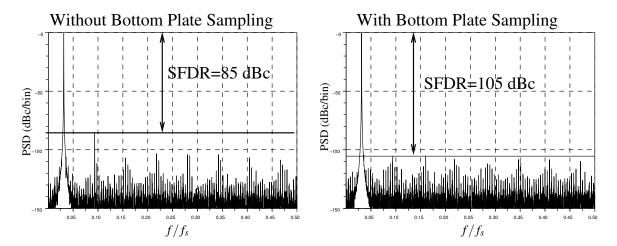

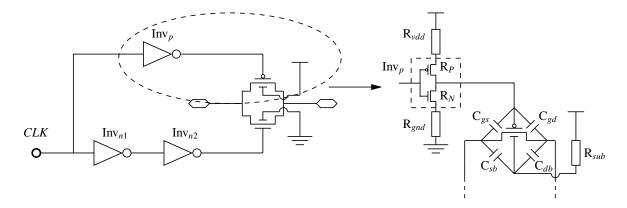

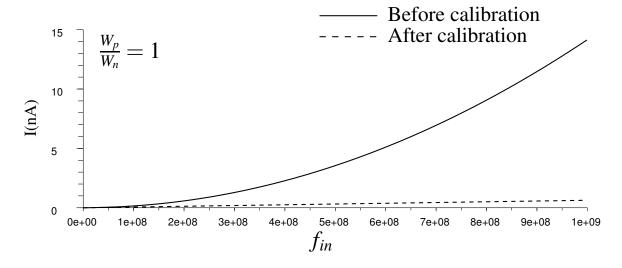

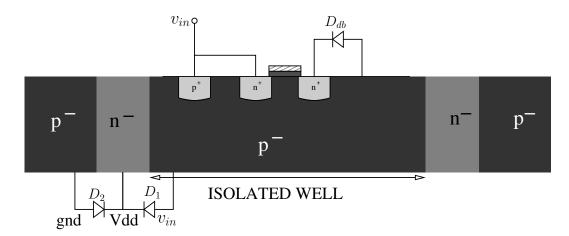

|   |     | 3.2.7   | Switch linearity requirements                                                  |

|   |     | 3.2.8   | Conclusion                                                                     |

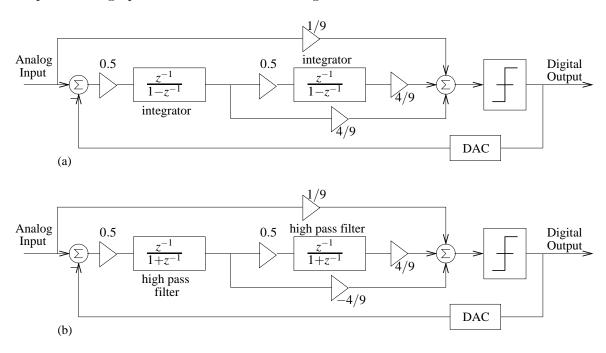

|   | 3.3 | Low P   | ass vs High Pass modulators                                                    |

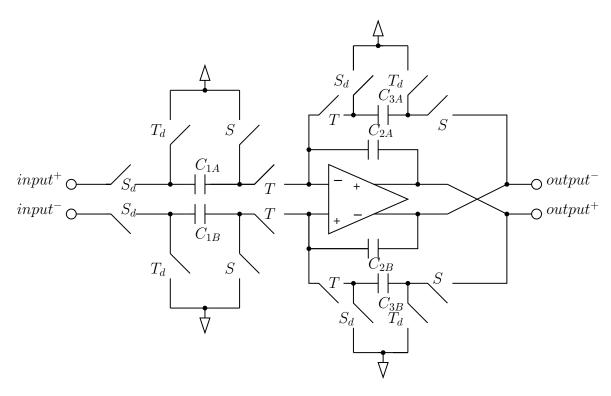

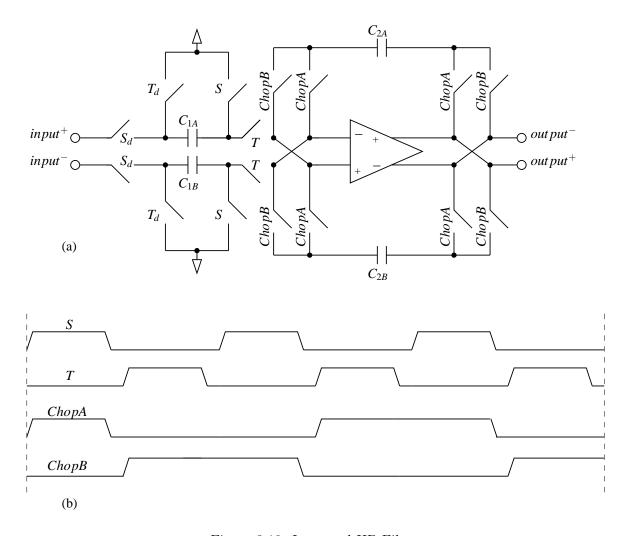

|   |     | 3.3.1   | High-Pass Filter/Mirrored-Integrator Implementation                            |

|   |     |         | 3.3.1.1 Integrator Based High-Pass Filter                                      |

|   |     |         | 3.3.1.2 Improved High-Pass Filter                                              |

|   |     |         | 3.3.1.3 Comparative Analysis                                                   |

|   |     | 3.3.2   | OTA Non-Idealities                                                             |

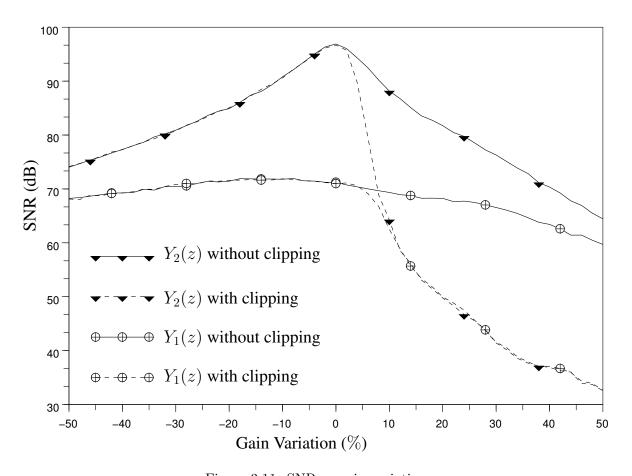

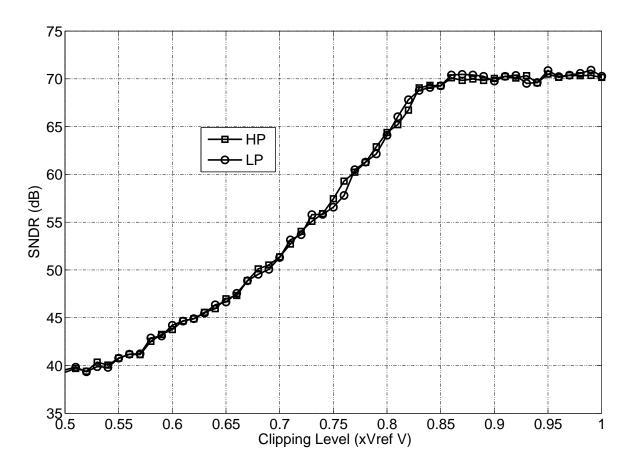

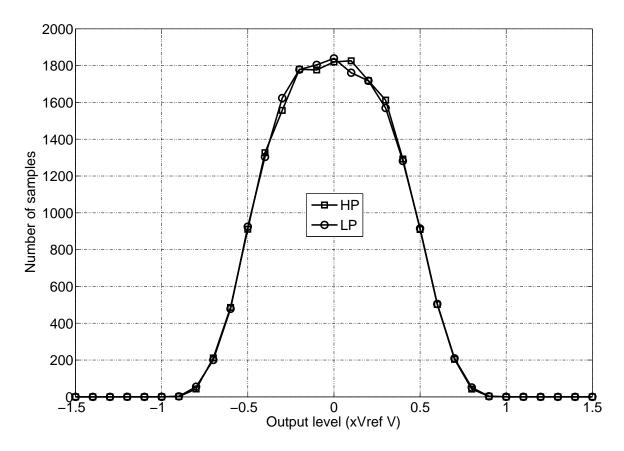

|   |     | 0.0.2   | 3.3.2.1 Clipping                                                               |

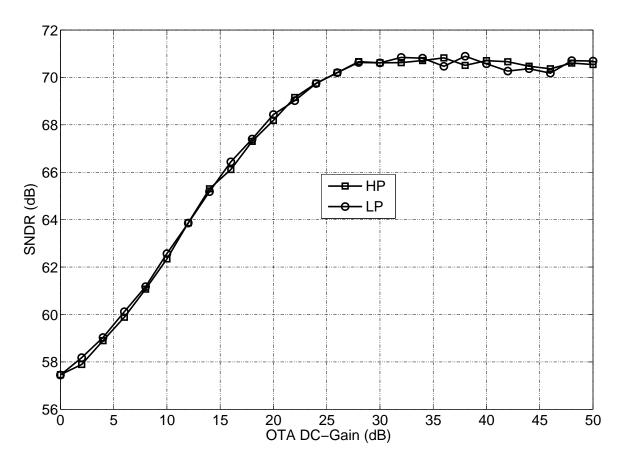

|   |     |         | 3.3.2.2 DC-Gain                                                                |

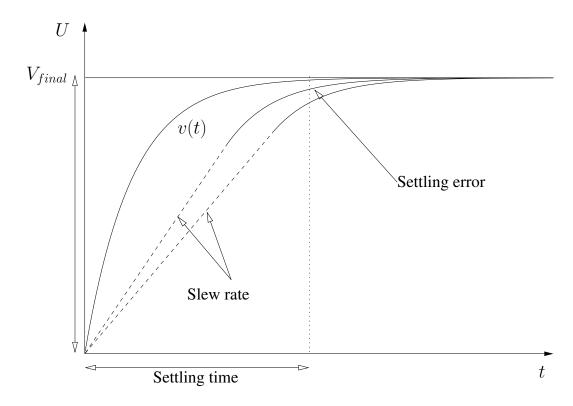

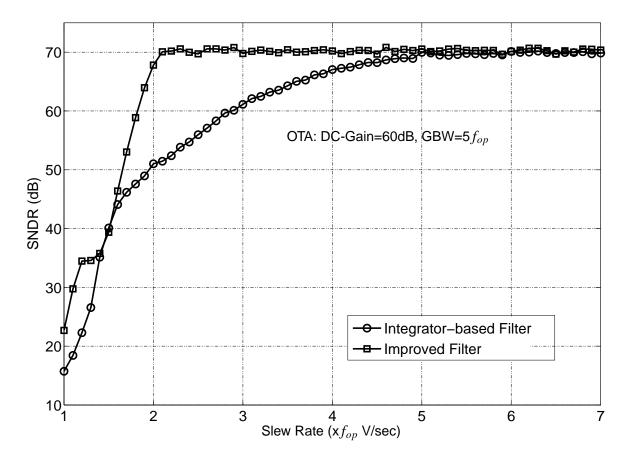

|   |     |         | 3.3.2.3 Gain Bandwidth Product and Slew Rate                                   |

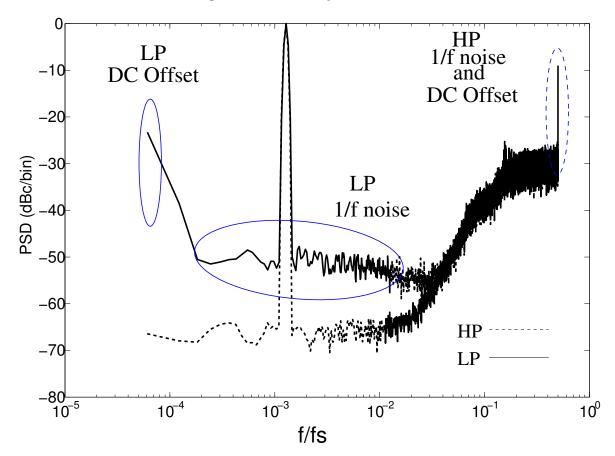

|   |     | 3.3.3   | DC-Offset, 1/f Noise and Thermal Noise                                         |

|   |     | 3.3.4   | Quantizer Non-Idealities                                                       |

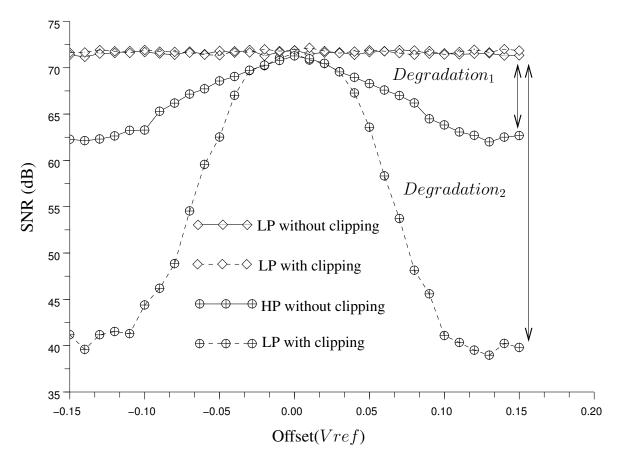

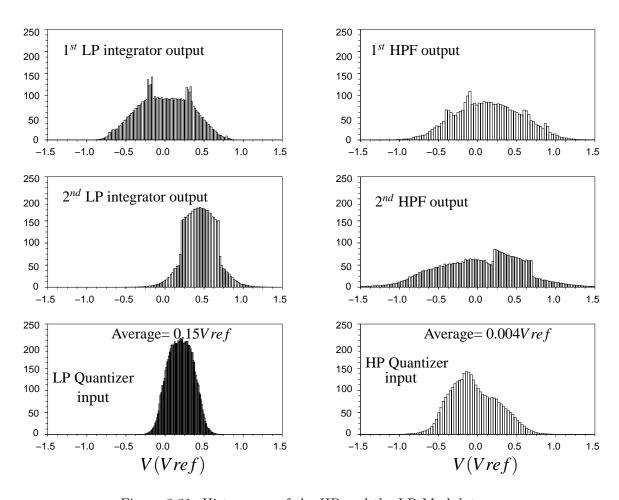

|   |     | 0.0.4   | 3.3.4.1 Offset                                                                 |

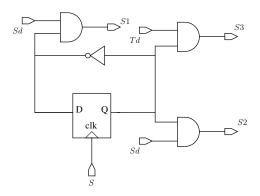

|   |     |         | 3.3.4.2 Metastability                                                          |

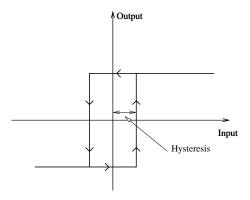

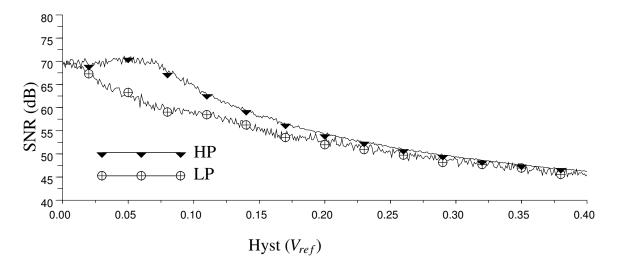

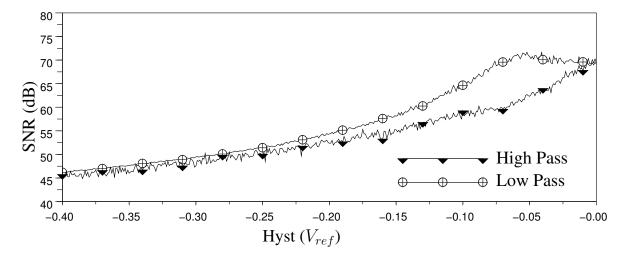

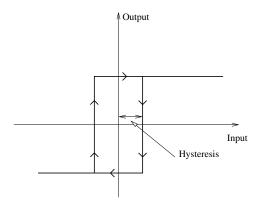

|   |     |         | 3.3.4.3 Hysteresis                                                             |

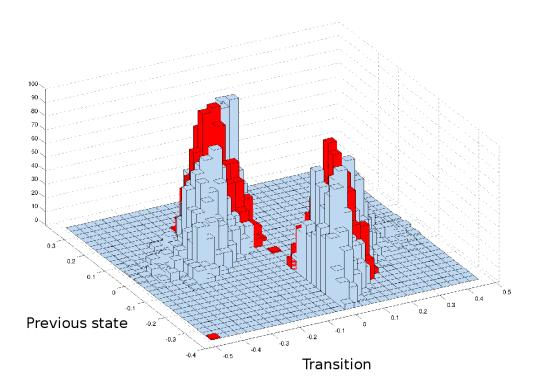

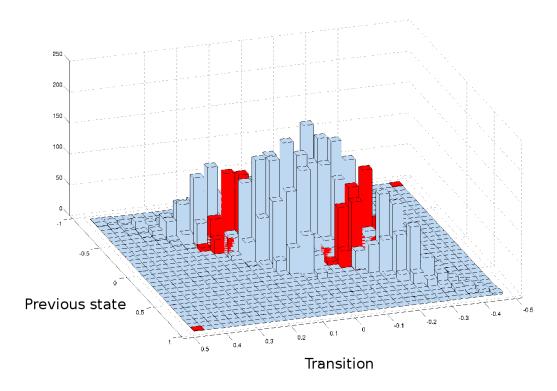

|   |     | 3.3.5   |                                                                                |

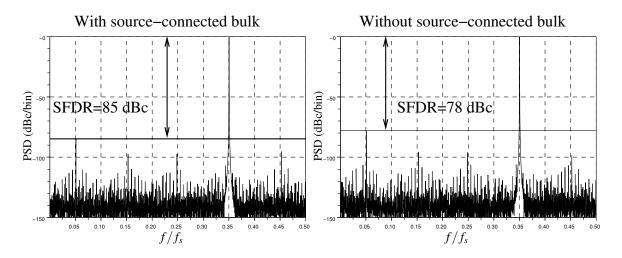

|   |     | 5.5.5   | 1 0 1                                                                          |

|   |     |         |                                                                                |

|   |     | 2.2.6   | 3.3.5.2 Jitter                                                                 |

|   |     | 3.3.6   | Conclusion                                                                     |

| 4 | Par | allel A | $\Sigma$ Modulators 63                                                         |

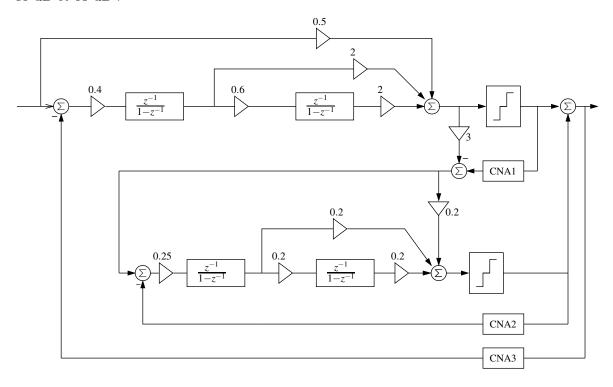

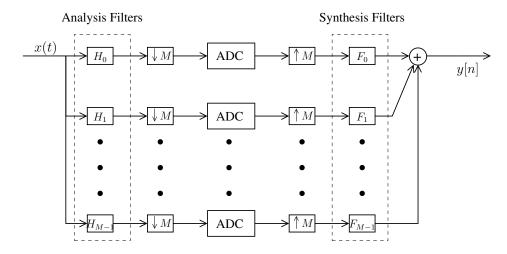

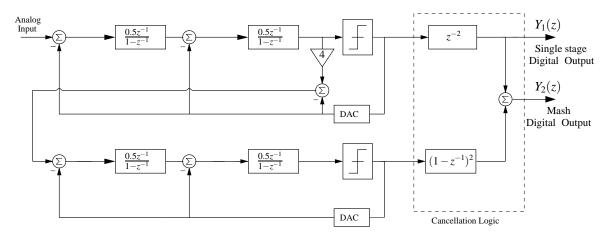

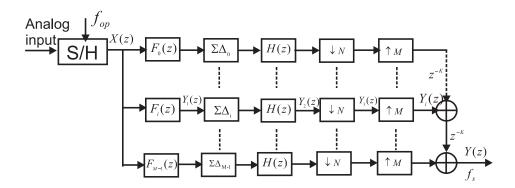

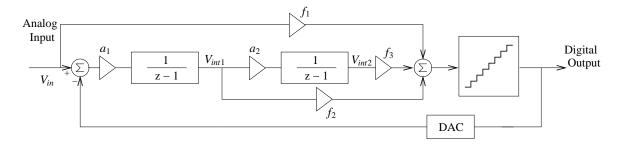

| • | 4.1 |         | el $\Delta\Sigma$ Modulators Architectures                                     |

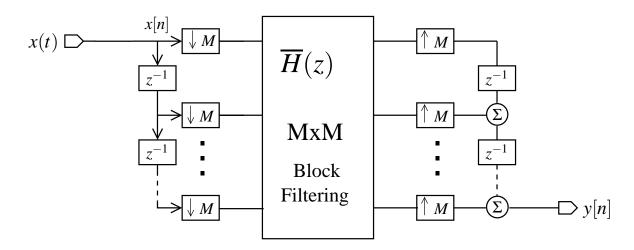

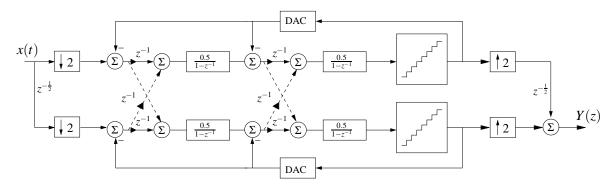

|   | 1.1 | 4.1.1   | Block filtering $\Delta\Sigma$ ADC                                             |

|   |     | 4.1.2   | $\Pi\Delta\Sigma$ ADC                                                          |

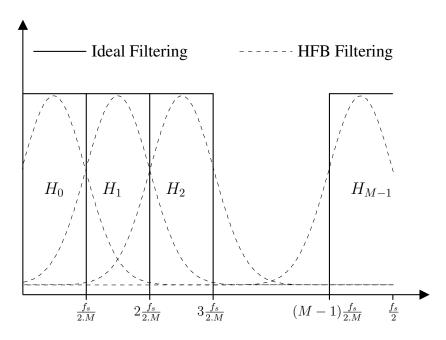

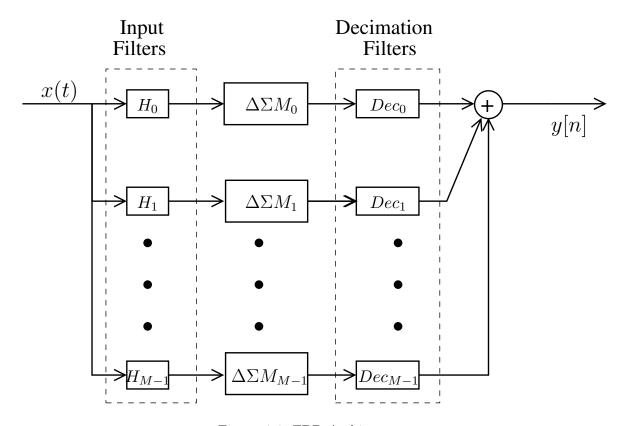

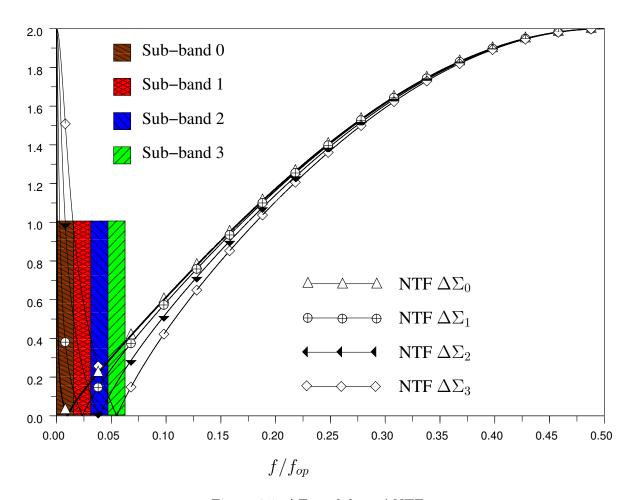

|   |     | 4.1.3   | Frequency band decomposition                                                   |

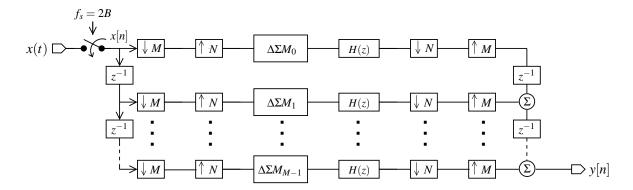

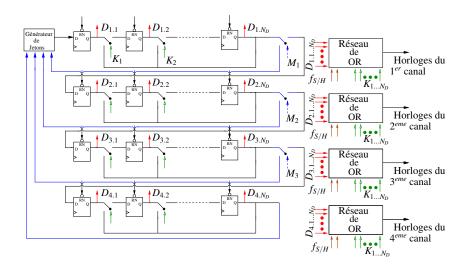

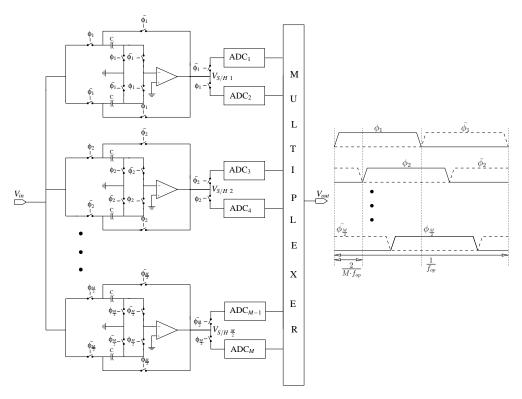

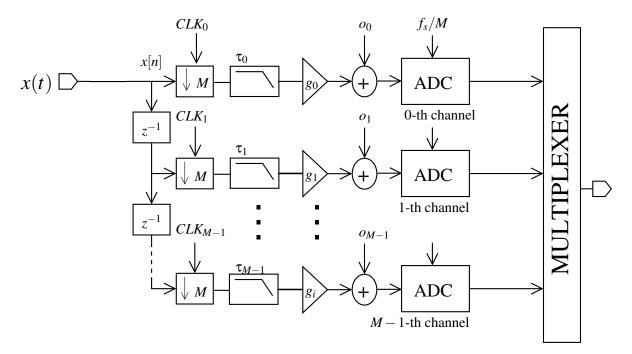

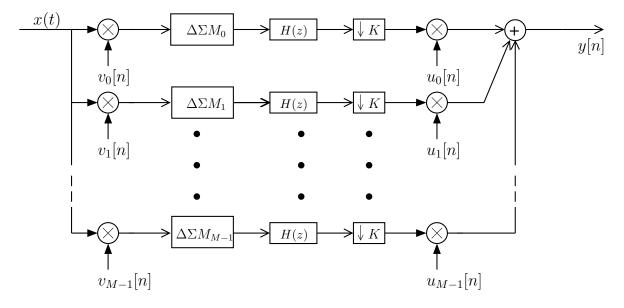

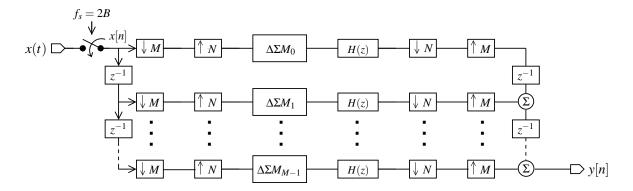

|   |     | 4.1.4   | Time interleaved $\Delta\Sigma$ ADC                                            |

|   |     | 4.1.5   | Conclusion                                                                     |

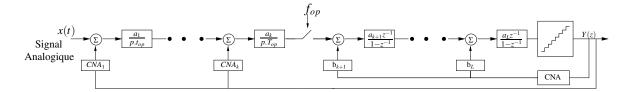

|   | 4.2 |         | $\Delta \Sigma$ ADC with novel interpolation technique                         |

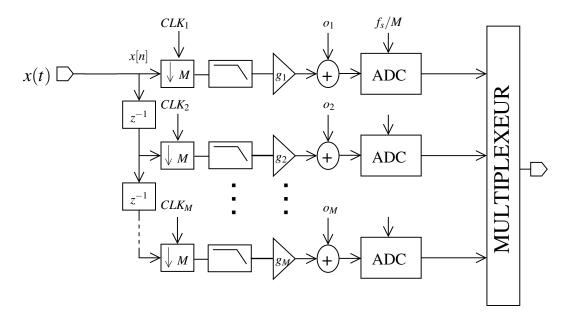

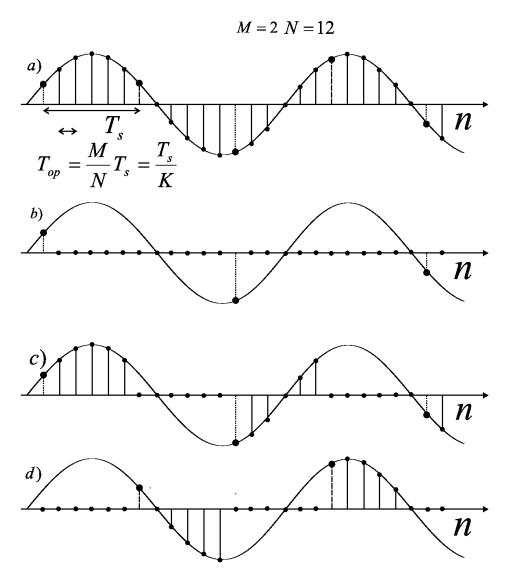

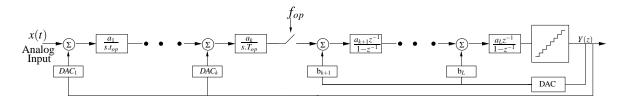

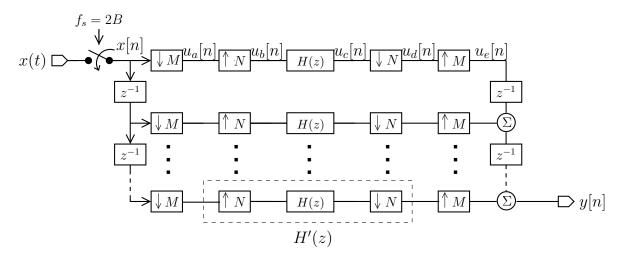

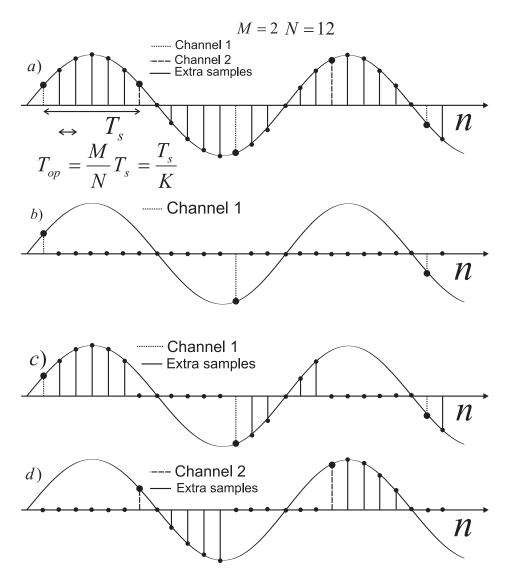

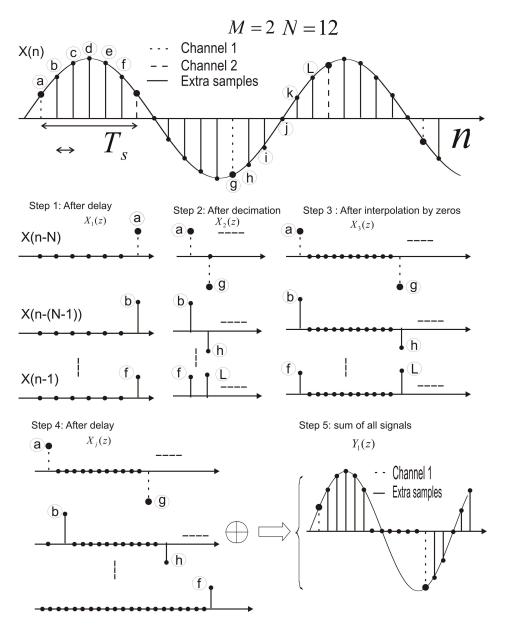

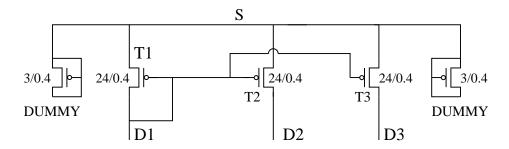

|   | 4.2 | 4.2.1   | Classical Time interleaved $\Delta\Sigma$ ADC                                  |

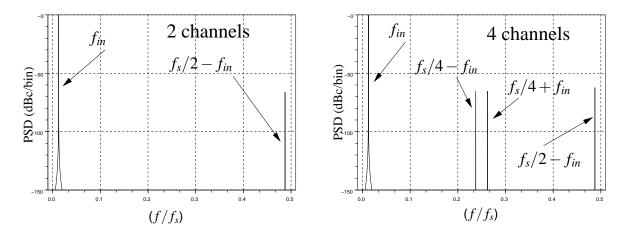

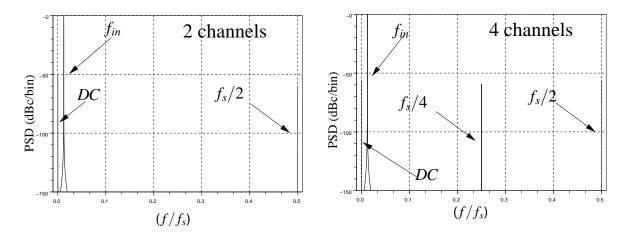

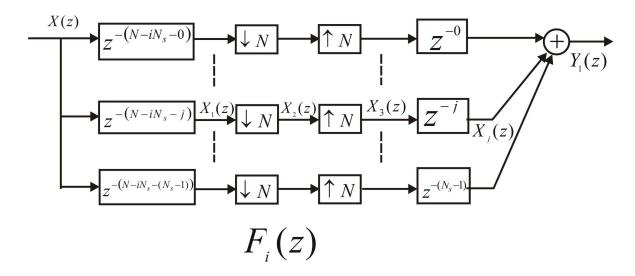

|   |     | 4.2.1   | 4.2.1.1 Signal transfer function of the Time interleaved $\Delta\Sigma$ ADC 70 |

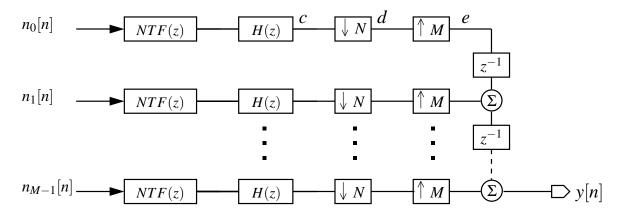

|   |     |         |                                                                                |

|   |     |         |                                                                                |

|   |     |         |                                                                                |

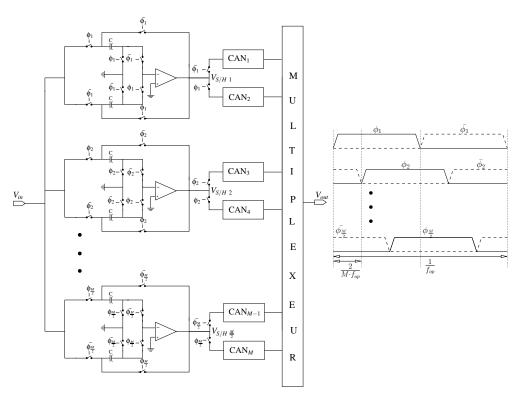

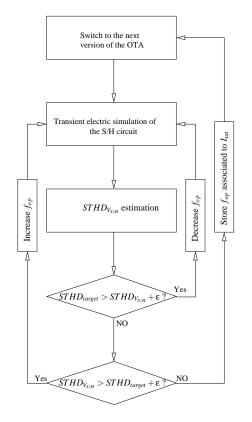

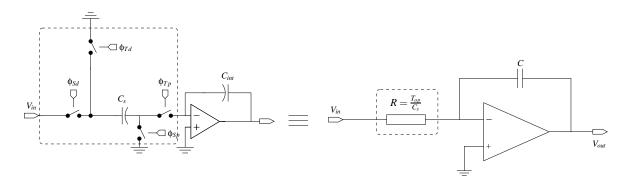

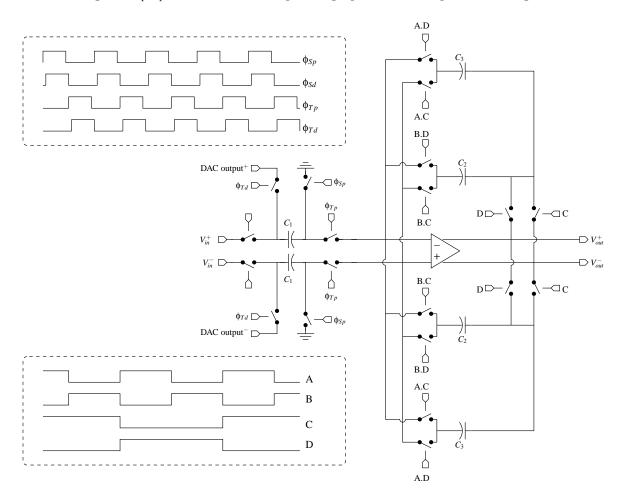

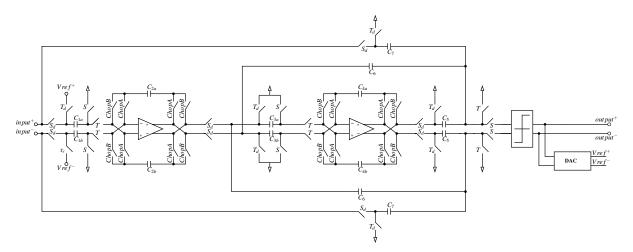

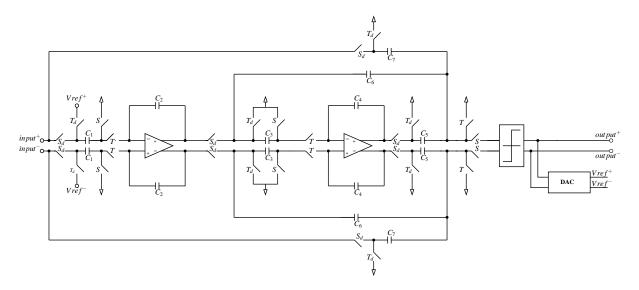

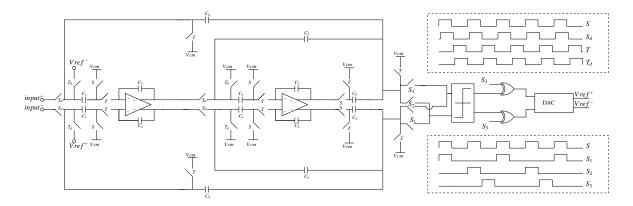

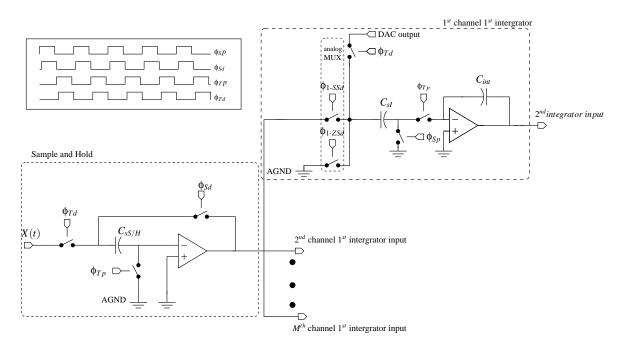

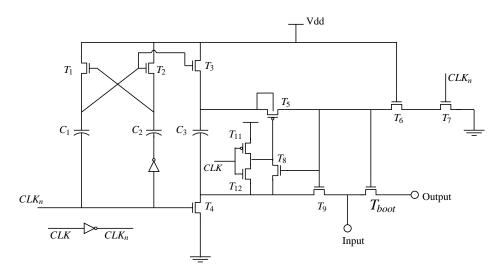

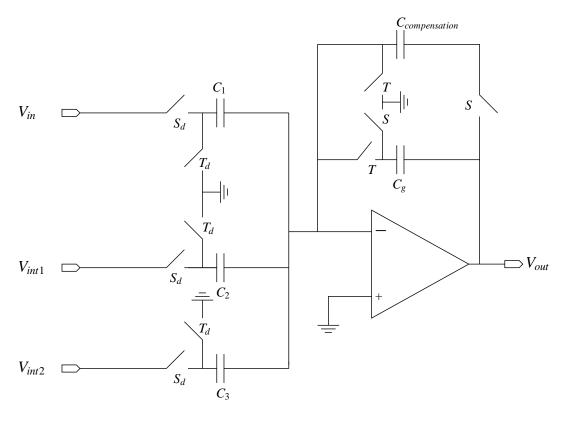

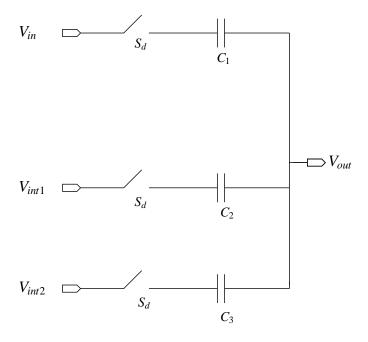

|   |     | 400     | 4.2.1.4 Analog front-end implementation                                        |

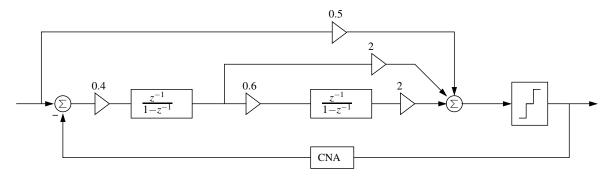

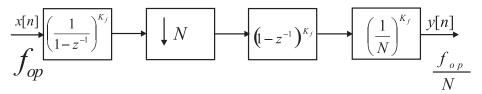

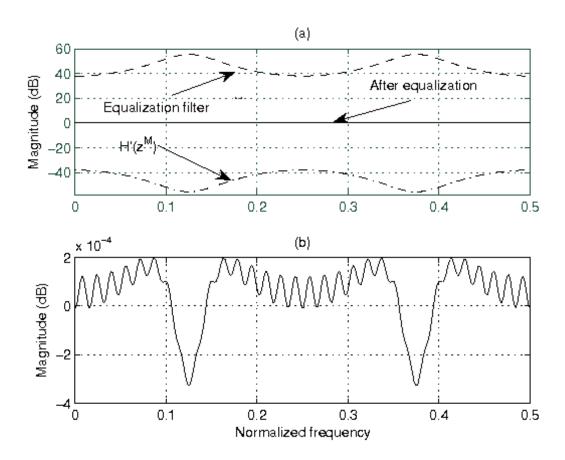

|   |     | 4.2.2   | The proposed interpolation technique                                           |

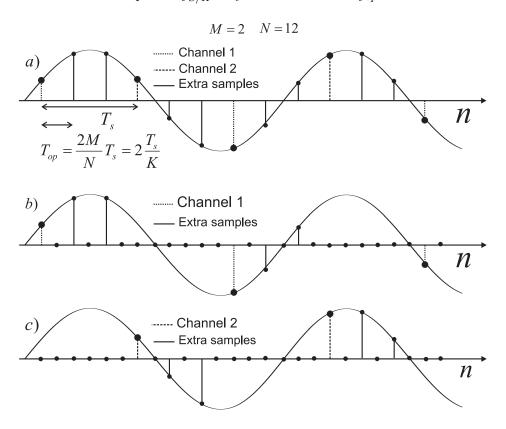

|   |     |         | 4.2.2.1 Principle                                                              |

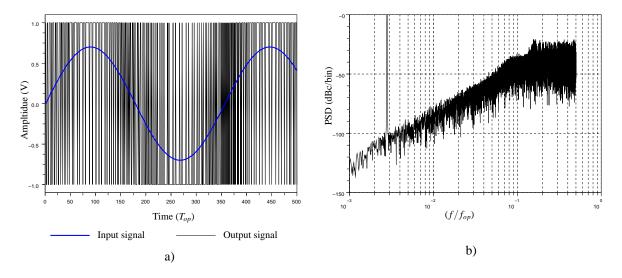

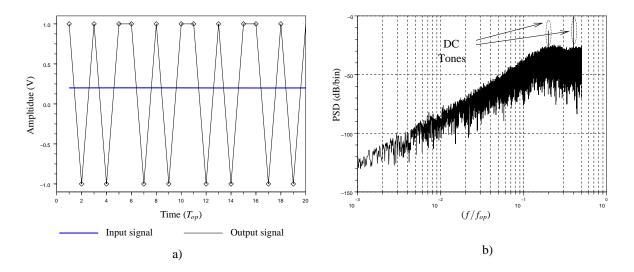

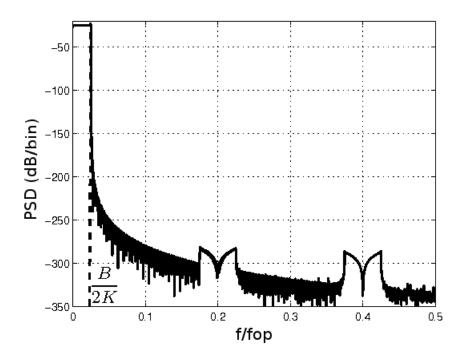

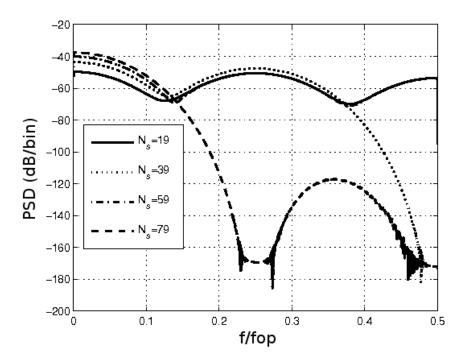

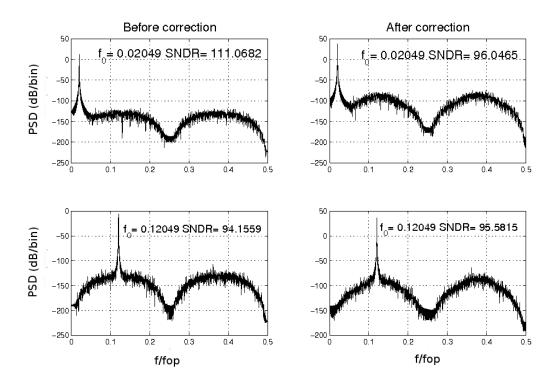

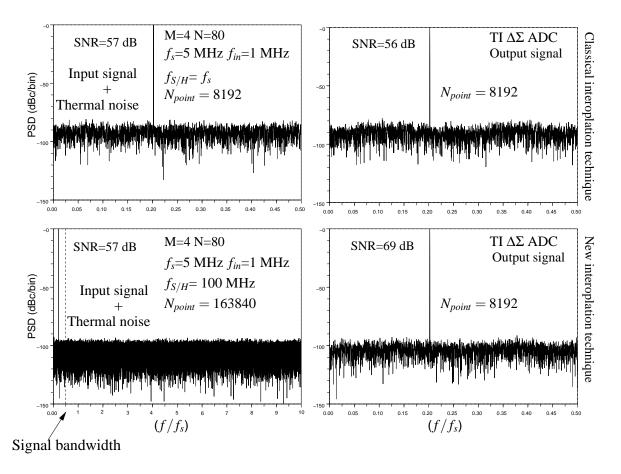

|   |     |         | 4.2.2.2 Simulation results                                                     |

|   |     |         | 4.2.2.3 Equalization filter complexity                                         |

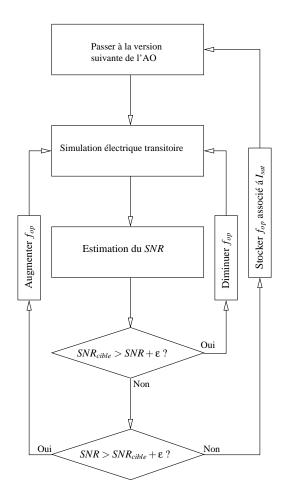

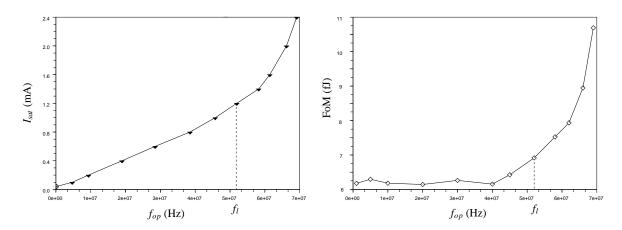

|   |     | a       | 4.2.2.4 Choice of the operation frequency of the S/H                           |

|   | 4.3 |         | ation                                                                          |

|   |     | 4.3.1   | Clock skew and bandwidth mismatch                                              |

|   |     |         |                                                                                |

|   | 4.4 | 4.3.2   | Offset and gain mismatch                                                       |

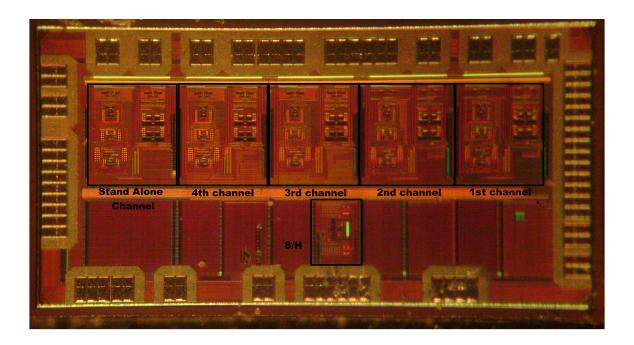

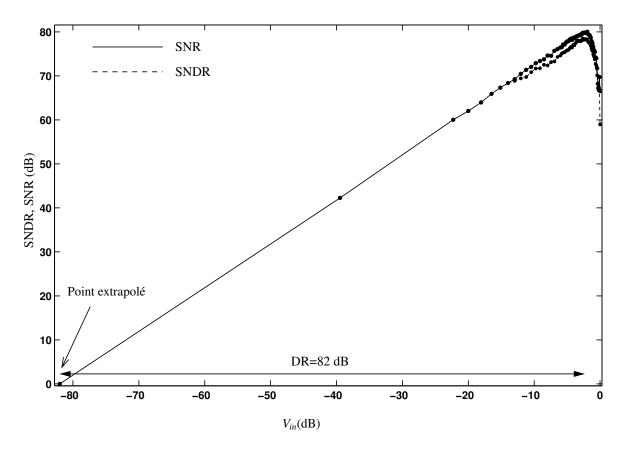

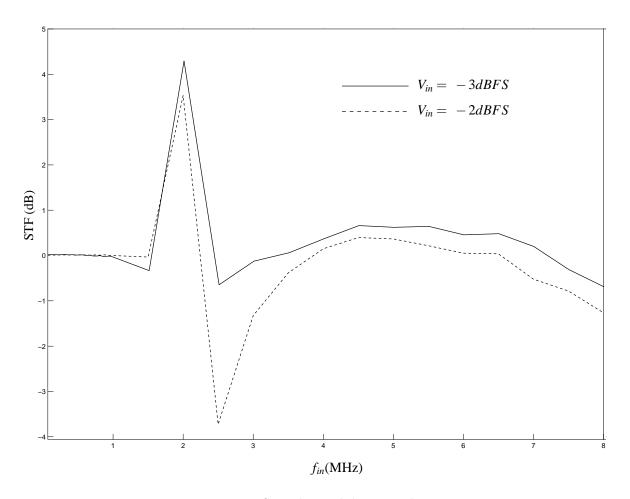

| <b>5</b> | Pro | totype                                     | 93         |

|----------|-----|--------------------------------------------|------------|

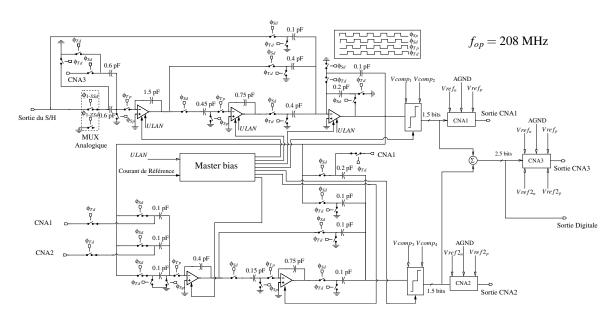

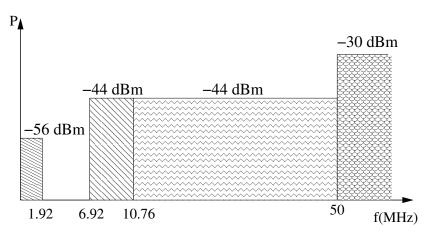

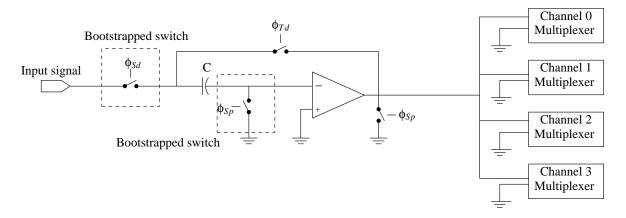

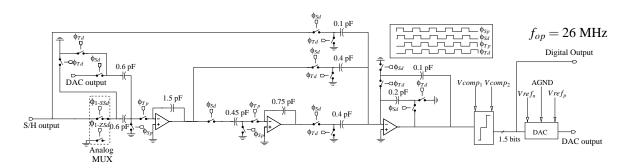

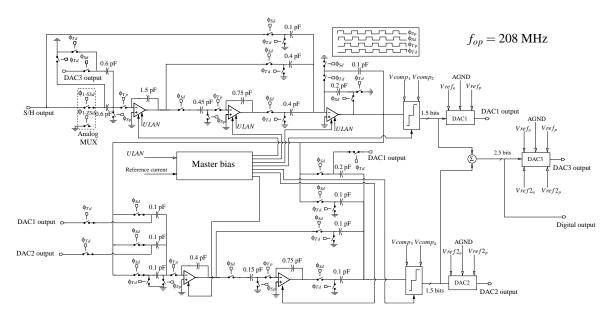

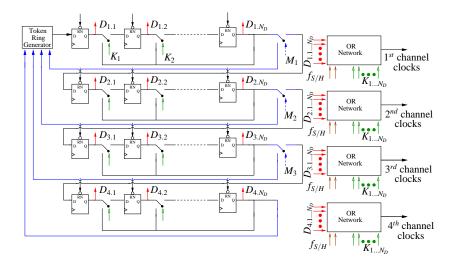

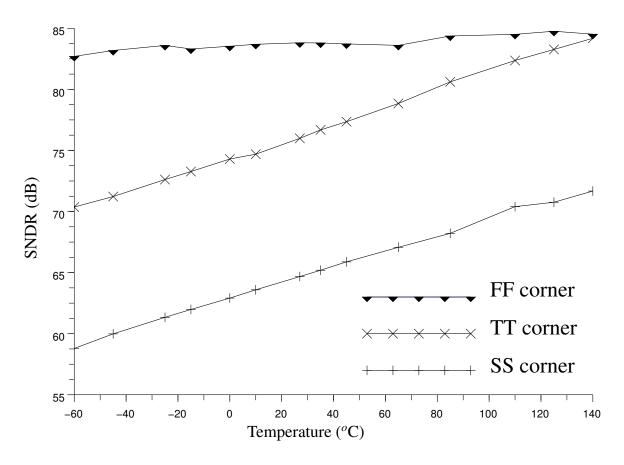

|          | 5.1 | System Design                              | 93         |

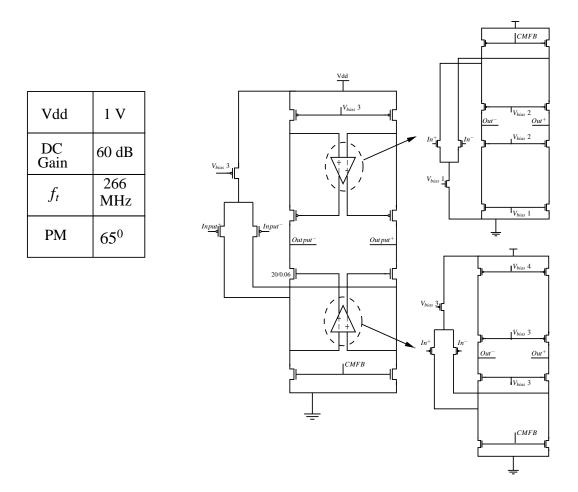

|          | 5.2 | Electrical Design                          | 97         |

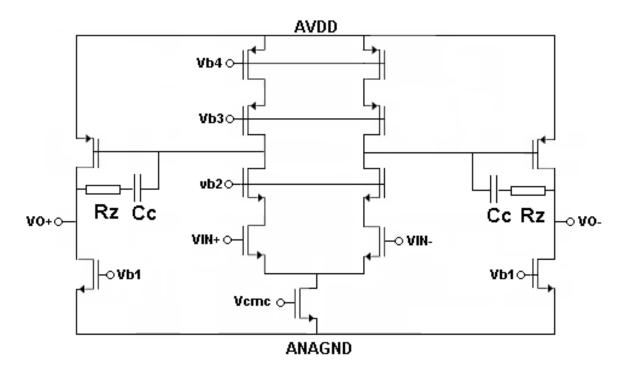

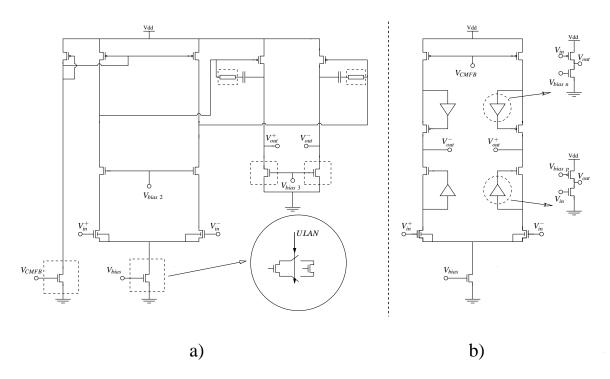

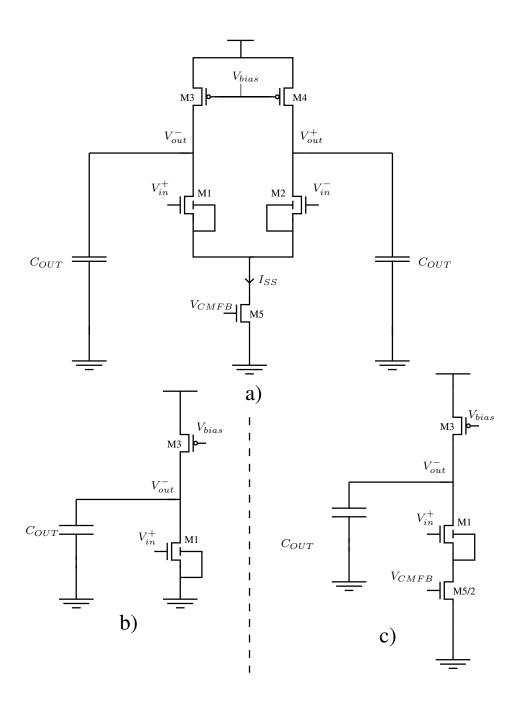

|          |     | 5.2.1 Analog design                        | 97         |

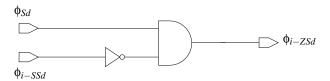

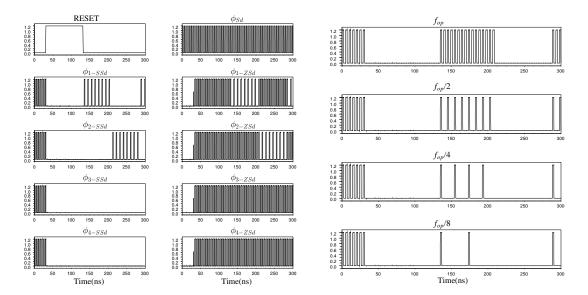

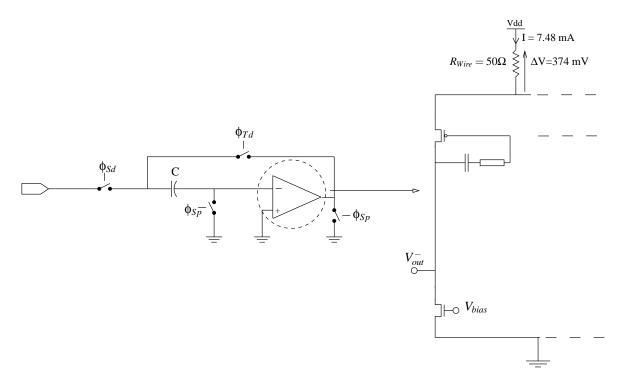

|          |     | 5.2.2 Interpolation network implementation | 100        |

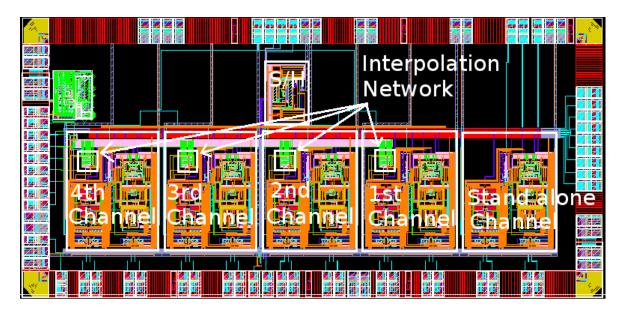

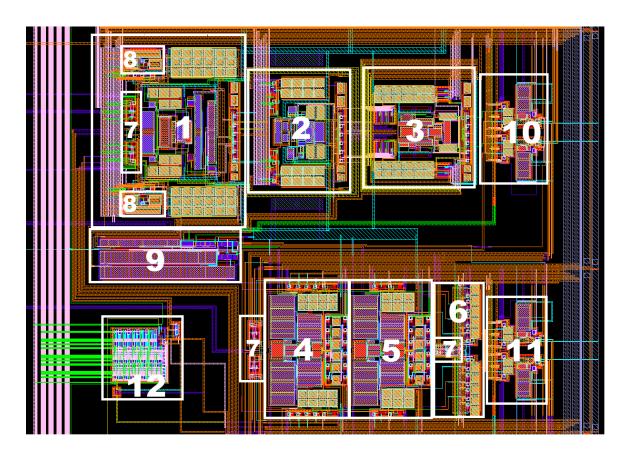

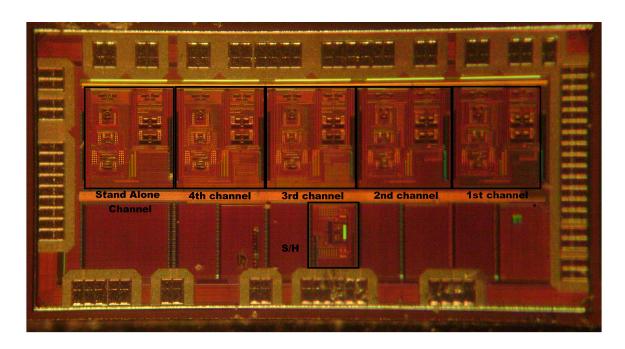

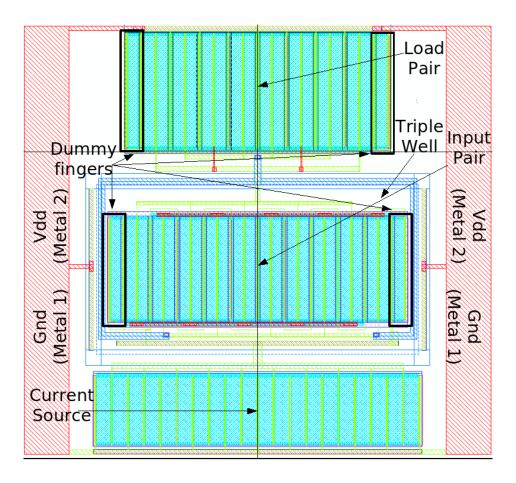

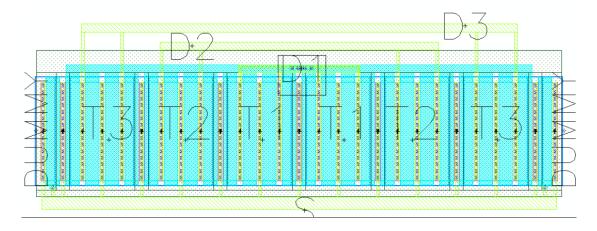

|          | 5.3 | Layout                                     | 104        |

|          | 5.4 | ·                                          | 105        |

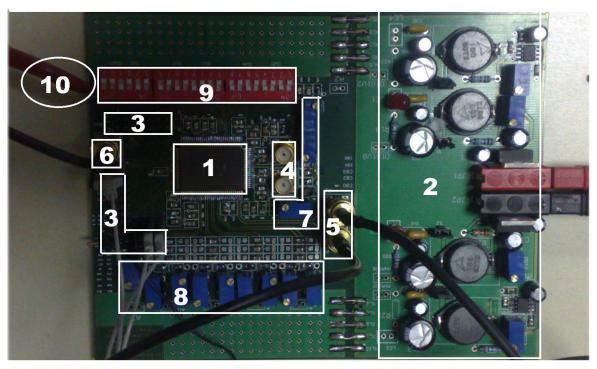

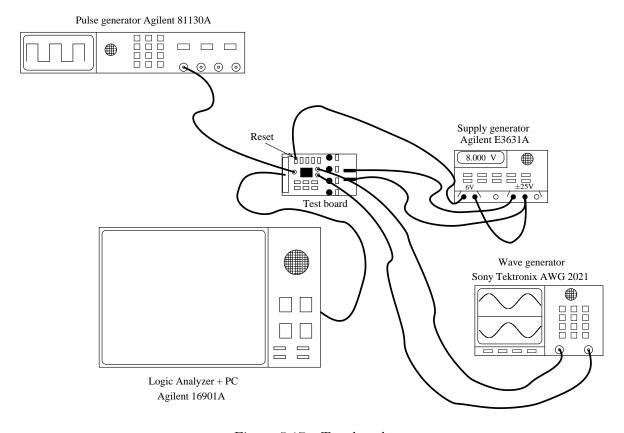

|          |     | 5.4.1 Test setup                           | 105        |

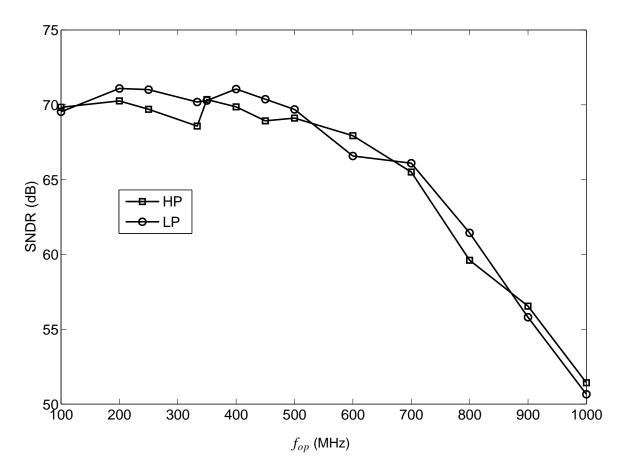

|          |     | •                                          | 105        |

|          |     | ·                                          | 105        |

|          |     |                                            | 105        |

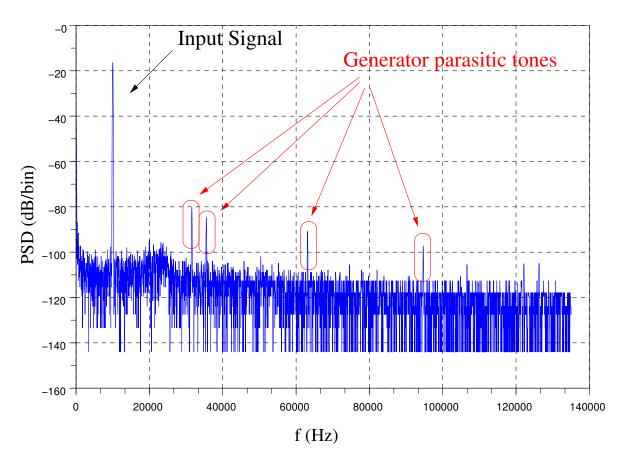

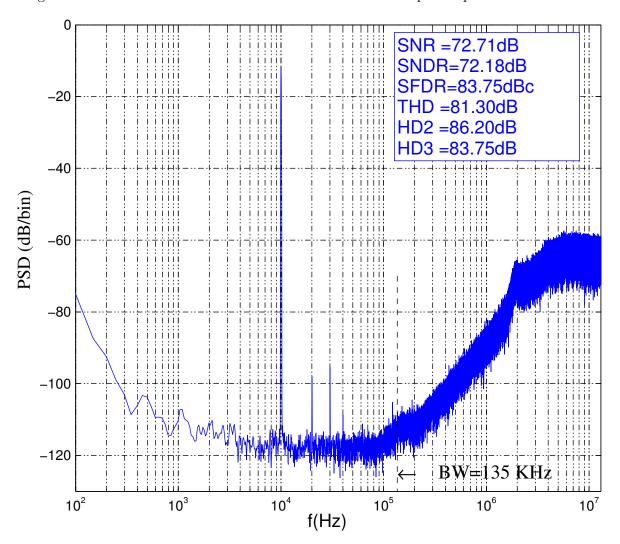

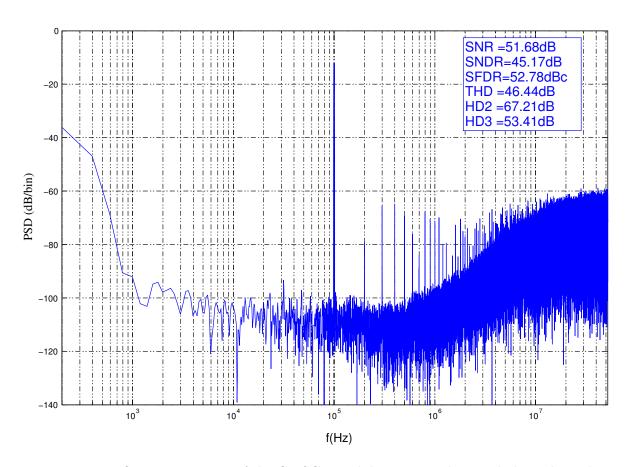

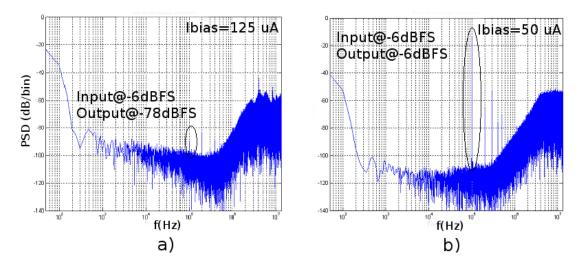

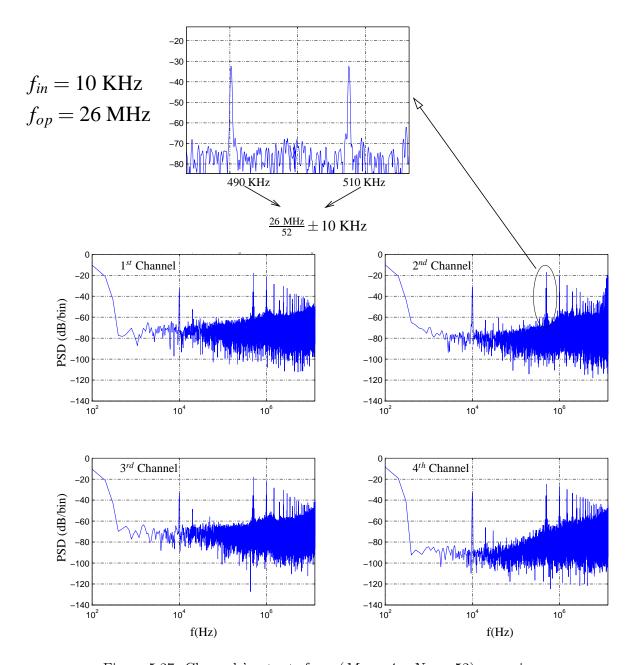

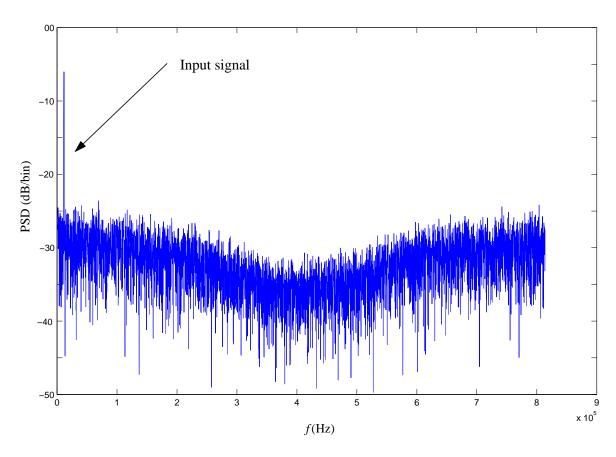

|          |     |                                            | 110        |

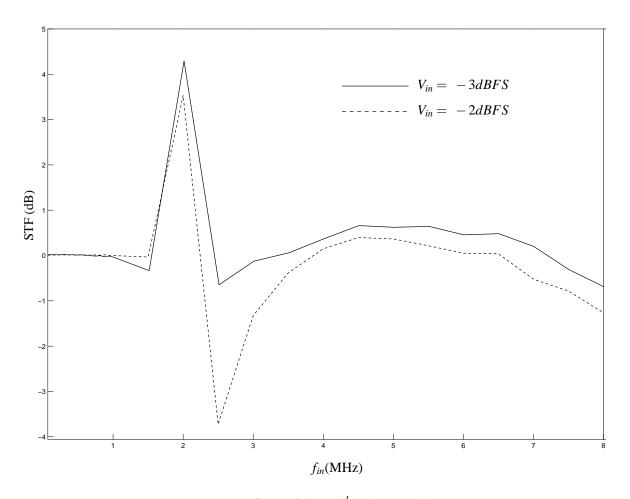

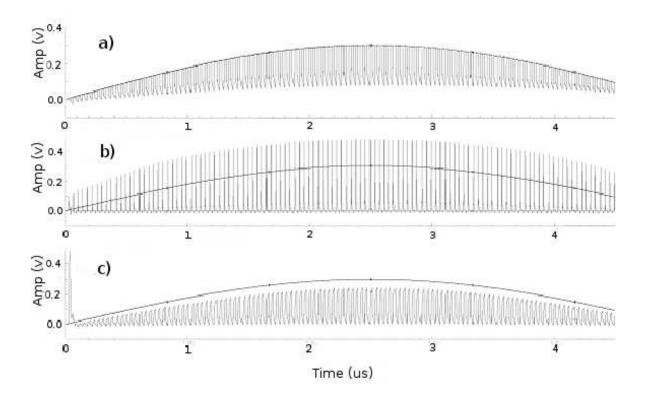

|          |     |                                            | 110        |

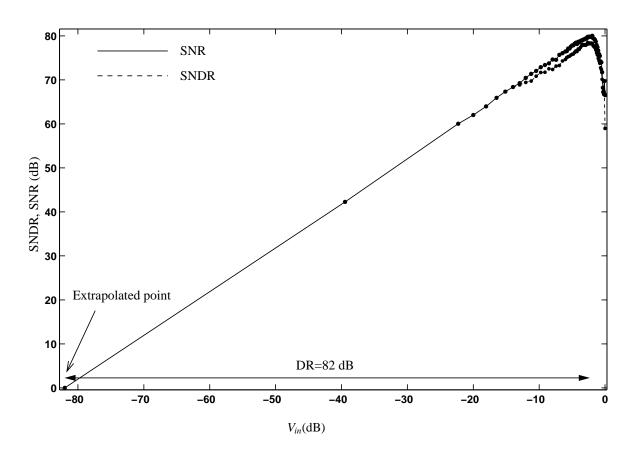

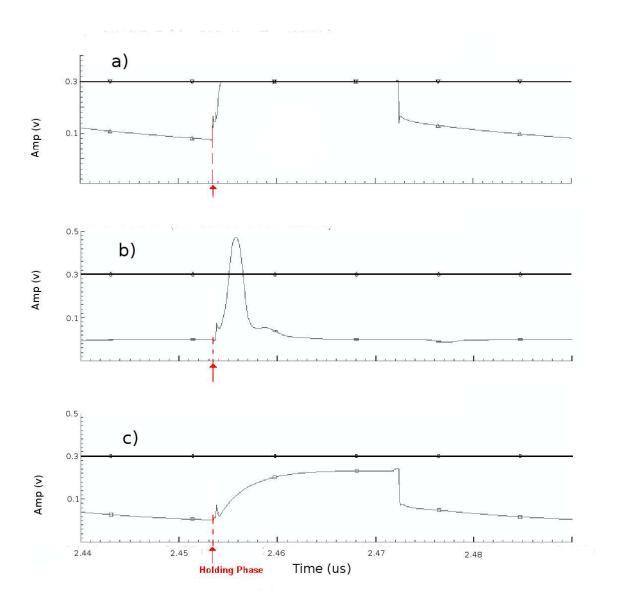

|          |     | ·                                          | 114        |

|          | 5.5 |                                            | 122        |

|          |     |                                            |            |

| 6        | Con | 1 1                                        | 25         |

|          | 6.1 |                                            | 125        |

|          | 6.2 | Perspectives                               | 126        |

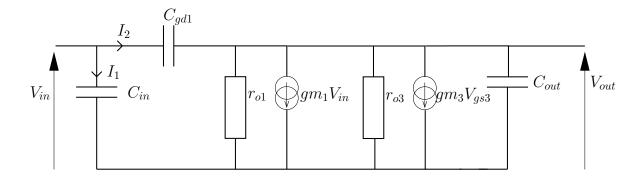

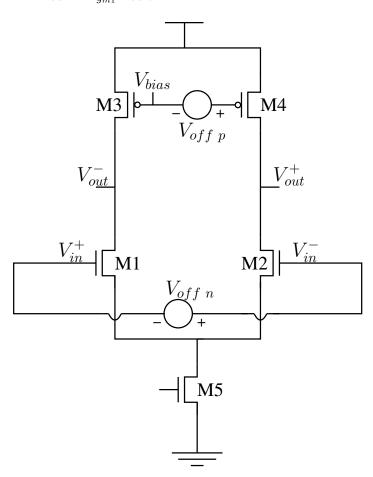

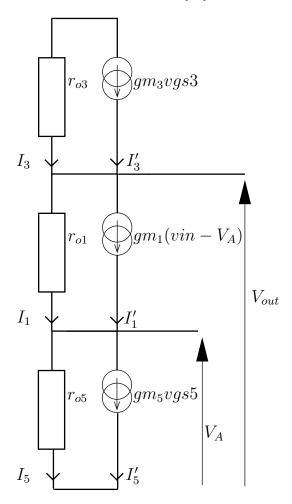

| ٨        | CM  | OS Design                                  | 27         |

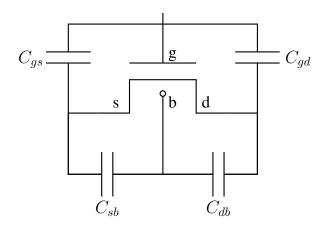

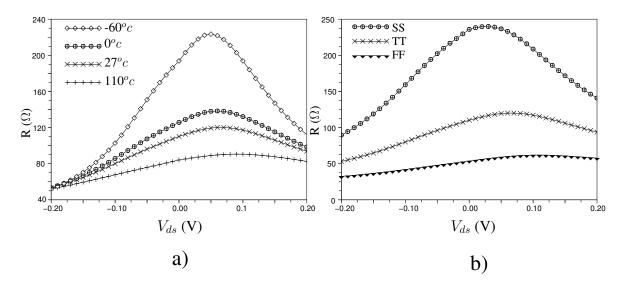

| A        |     | <u> </u>                                   | 127        |

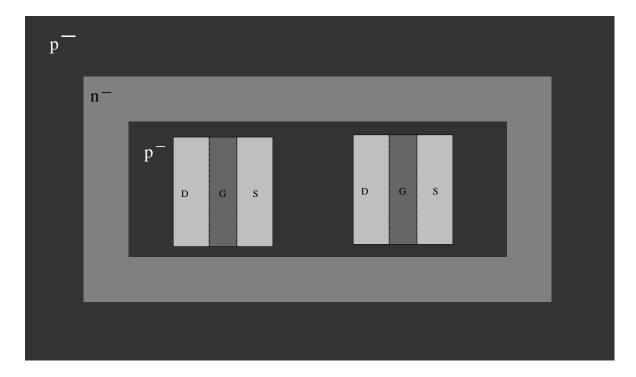

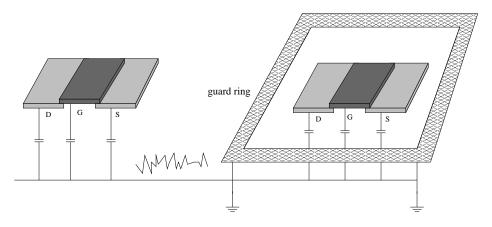

|          | Λ.1 |                                            | 127        |

|          |     |                                            | 128        |

|          |     | - · · · · · · · · · · · · · · · · · · ·    | 128        |

|          |     |                                            | 128        |

|          |     |                                            | 132        |

|          |     |                                            | 133        |

|          |     |                                            | 134        |

|          |     |                                            | 134<br>134 |

|          |     |                                            | 134        |

|          |     |                                            | 136        |

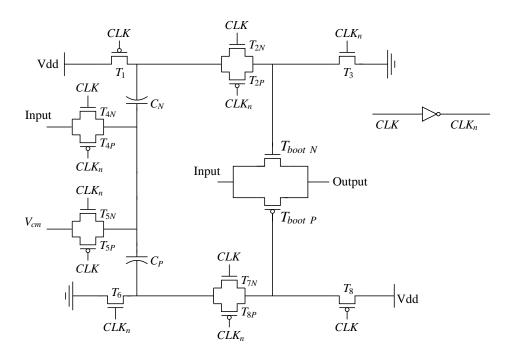

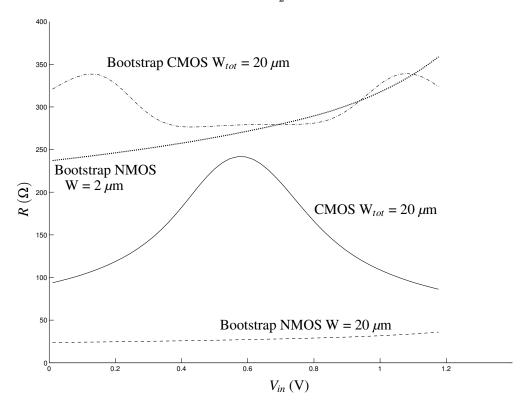

|          | A 9 |                                            | 136        |

|          | A.Z |                                            | 138        |

|          |     |                                            | 138        |

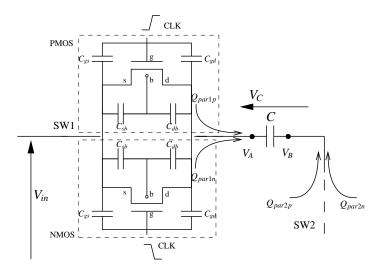

|          |     |                                            | 139        |

|          |     |                                            |            |

|          |     |                                            | 141<br>142 |

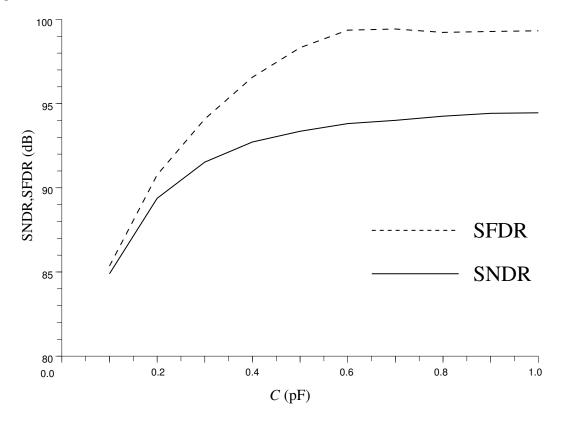

|          |     |                                            | 142<br>144 |

|          |     |                                            | 144 $147$  |

|          |     | 1 0                                        | 147        |

|          |     |                                            |            |

|          |     |                                            | 151        |

|          |     |                                            | 153        |

|          |     |                                            | 154        |

|          |     |                                            | 154        |

|          |     |                                            | 157        |

|          | 1 0 |                                            | 157        |

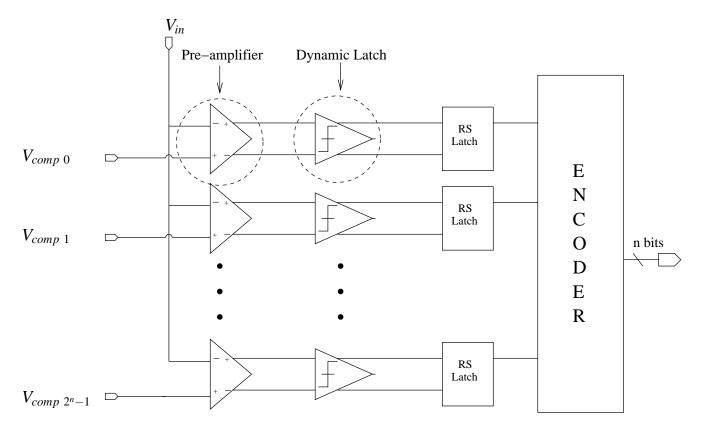

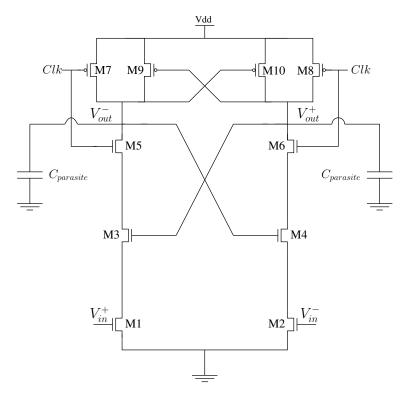

|          | A.3 | Quantizer                                  | 160        |

X CONTENTS

|    |       | A.3.1         | A.3.1.1 Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .60<br>.62<br>.62 |

|----|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|    | A.4   | Adder         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .62               |

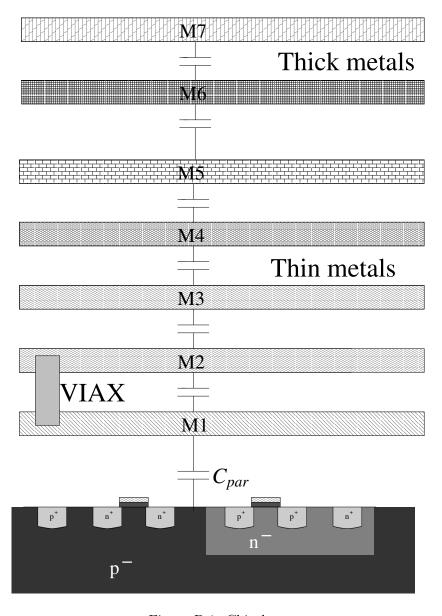

| В  | Lay   | out coi       | nsiderations and techniques 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65                |

|    | B.1   | Genera        | ul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                |

|    |       | B.1.1         | Wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65                |

|    |       |               | B.1.1.1 Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                |

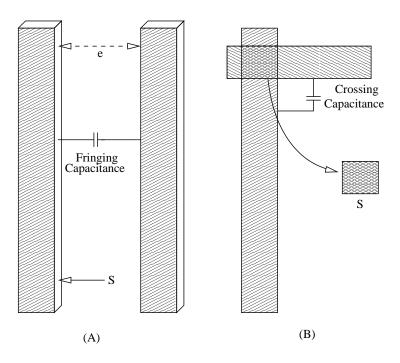

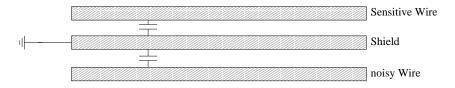

|    |       |               | B.1.1.2 Parasitic capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                |

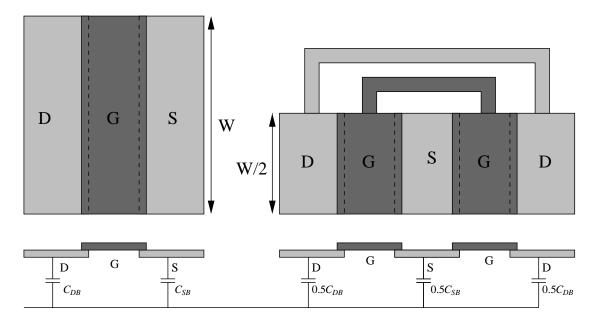

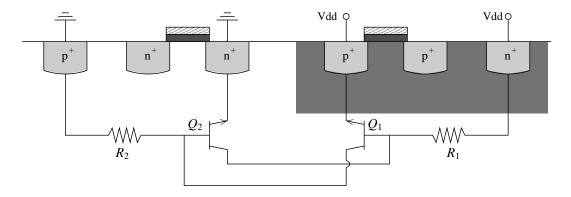

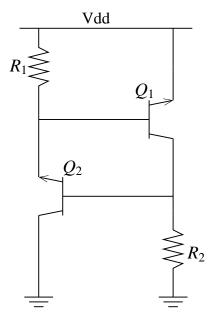

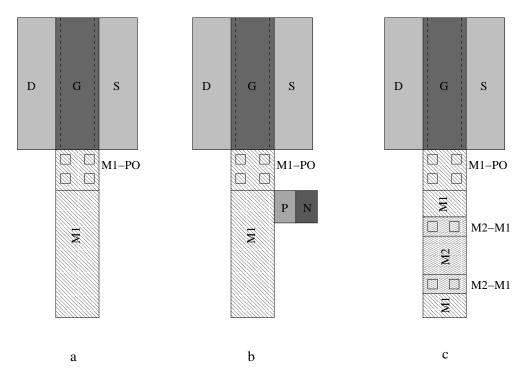

|    |       | B.1.2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67                |

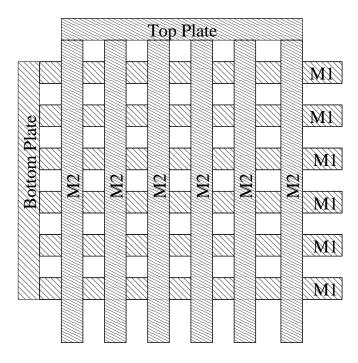

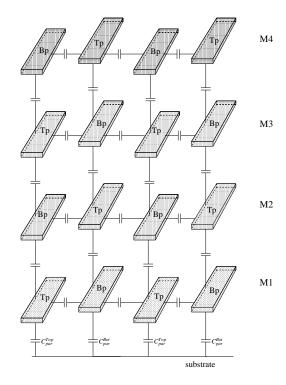

|    |       | B.1.3         | Capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68                |

|    | B.2   | Match         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70                |

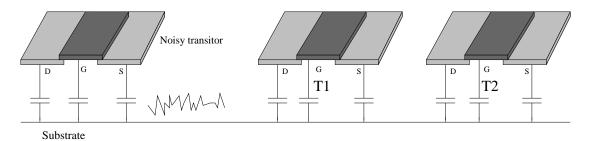

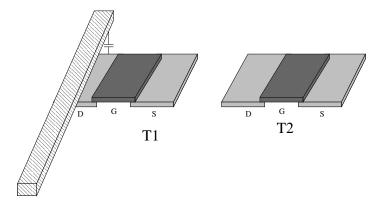

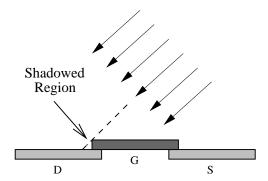

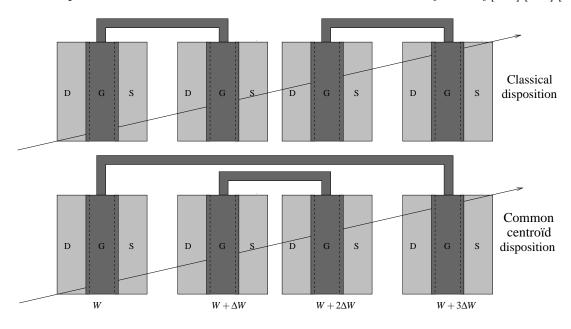

|    |       | B.2.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74                |

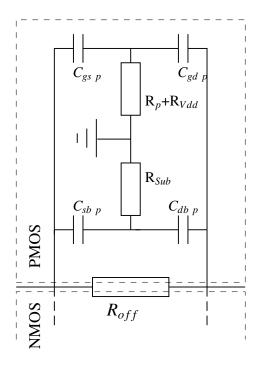

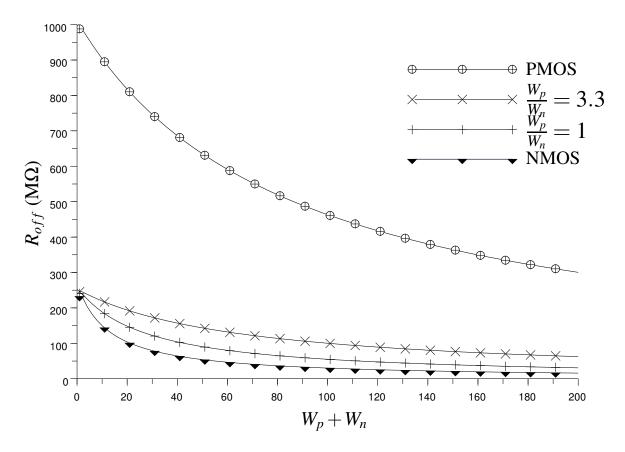

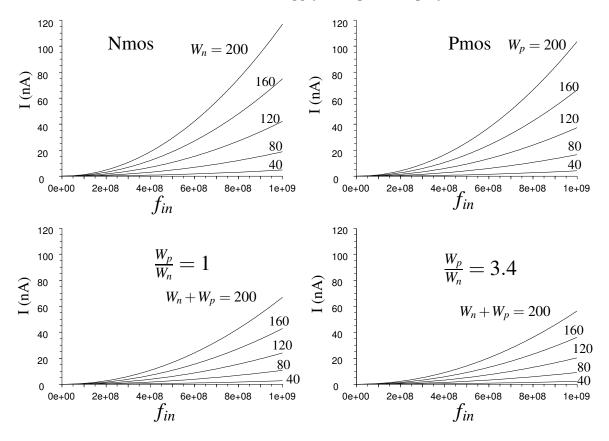

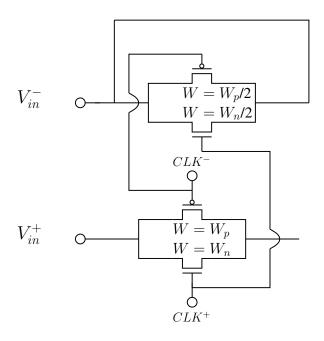

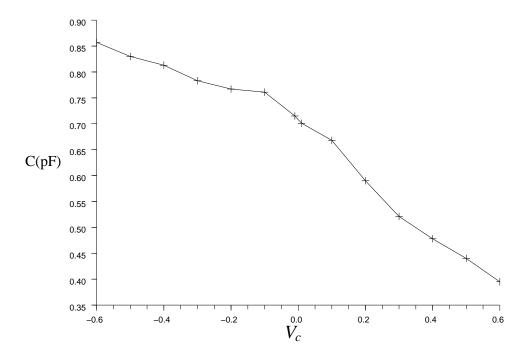

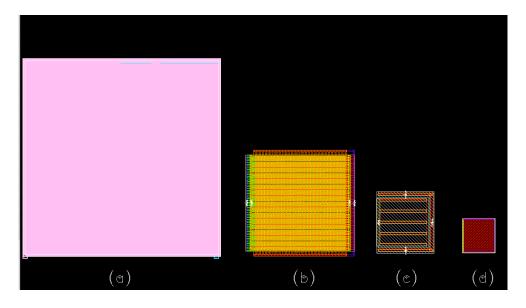

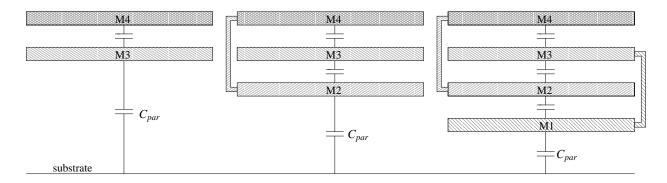

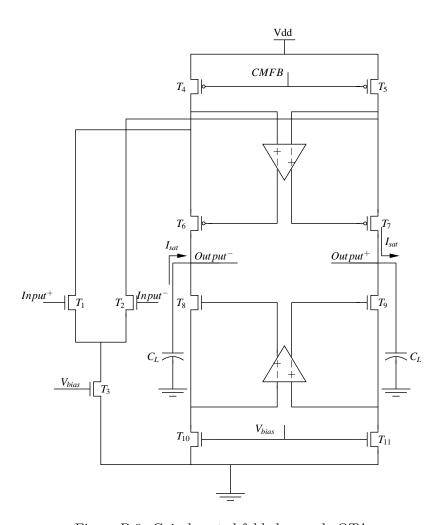

|    |       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74                |