# AMS/RF Design for Reliability Methodology: a Reliable RF Front-end Design

Pietro Maris Ferreira

## ▶ To cite this version:

Pietro Maris Ferreira. AMS/RF Design for Reliability Methodology: a Reliable RF Front-end Design. Electronics. Télécom ParisTech, 2011. English. NNT: . pastel-00628802

# HAL Id: pastel-00628802 https://pastel.hal.science/pastel-00628802

Submitted on 4 Oct 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **Thèse**

présentée pour obtenir le grade de docteur de l'Ecole Nationale Supérieure des Télécommunications Spécialité : Electronique et Communications

# Pietro MARIS FERREIRA

Méthodologie de conception AMS/RF pour la fiabilité : conception d'un frontal RF fiabilisé

Soutenance le 23 septembre 2011 devant le jury composé de

Fernando Silveira

Patrice Gamand

Amara Amara

Lírida Alves de Barros Naviner

Hervé Petit

Jean-François Naviner

Rapporteurs

**Examinateurs**

Directeurs de thèse

My dear Flavia.

## **ACKNOWLEDGEMENTS**

First of all, I would like to thank the sponsoring gave to my PhD research from Institut TELECOM. Also, STIC-AmSud had an important role in my work while funding the project NANORadio a cooperation of TELECOM ParisTech, Universidad de la Republica (Uruguay), Universidade Federal do Rio Grande do Sul (Brazil) and Universidade Federal do Rio de Janeiro (Brazil). Both funding made possible my dream to become a PhD in reality. Although I wished to personally thank each one of my colleagues at TELECOM ParisTech, I think that I cannot express my acknowledgements to them in this single page. Unfortunately, I may miss some of them.

I would like to express my love to my Lord who advised me and to my wife Flavia Tovo who had held up me. Both had guided me in this challenge of a PhD degree in France. Moreover, I would like to thank my family while seeding the valors during my background education. I also would like to express my pleasure to be advised by Jean-François Naviner and Hervé Petit. They have presented a special team play with complementary qualities and activities, while directing my PhD research.

In few words, I express my greetings to TELECOM ParisTech, the Department COMELEC and especially to the research group SIAM, as they welcome me with open heart. Inside such a group, I have shared a lot of experience with: Alban Gruget and Mariem Slimani, since the beginning; Fatima Ghanem, Germain Pham, and Hao Cai, after the first-half path. I realize that the discussions with Hussein Fakhoury had grown in great ideas; and the Arwa Ben Dhia's revision has improved my thesis and my writing skills. Furthermore, I am glad with the friendship found in all members of the group. I fell I am not able to enumerate all of them and highlight their participation in my achievement.

The inspiration in the end of this PhD life step and the beginning of my professional next step is found in George E. P. Box's thought. As it is: "Essentially, all models are wrong, but some are useful."

## RÉSUMÉ ÉTENDU

#### Introduction

Le développement des technologies CMOS à l'échelle nanométrique a fait émerger de nombreux défis sur le rendement et la fiabilité des composants [1]. Les prochaines générations de circuits AMS et RF souffriront d'une augmentation du taux de défaillance durant le temps d'opération. La méthode classique de conception des circuits sur puce repose sur les compromis entre : surface, consommation de puissance et vitesse d'opération. L'optimum est le point où on obtient le maximum ou le minimum spécifié pour les caractéristiques du circuit.

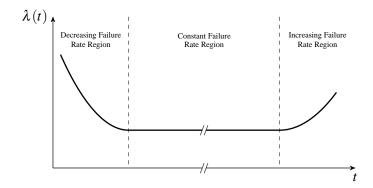

L'augmentation de la variabilité et la diminution de la fiabilité des transistors a prouvé que ce point optimal est devenu une région étant donné que le rendement attendu se déplace sous l'effet du vieillissement. La combinaison de ces deux événements impose de nouveaux défis au concepteur par rapport à la méthode classique de conception des circuits sur puce. Le rendement est le rapport entre le nombre des puces qui sont conformes aux spécifications de conception et la totalité produite. Cette grandeur est mesurée au début du temps d'opération des circuits et juste après la production des puces, c'est-à-dire à t=0. Pourtant, le rendement ne prend pas en compte l'évolution du taux de défaillance en fonction du temps. La fiabilité peut être définie comme la probabilité qu'un dispositif exécute une fonction exigée dans des conditions indiquées pendant une période indiquée [1].

Depuis l'avènement des téléphones mobiles, les architectures de frontal RF ont nécessité des innovations technologiques accrues dans un temps de commercialisation réduit. A côté de la recherche des architectures de frontal radio, les technologies des circuits intégrées sur puce ont suivi la célèbre Loi de Moore. Ces technologies ont permis d'obtenir les dimensions réduites, une faible consommation d'énergie et une augmentation de la vitesse. C'est pour cela que la surface, la consommation d'énergie et la vitesse sont devenues les éléments clés d'un compromis pour les circuits sur puce en général. Pour les circuits analogiques d'autres critères de performance sont définis, comme : le gain, le bruit et la linéarité. Le défi sera de trouver le compromis entre ces éléments.

Avec l'accroissement de la variabilité, la conception proche du point optimal est maintenant une région composée par un, deux ou trois  $\sigma$  selon le rendement souhaité. La solution la plus simple est de concevoir selon les caractéristiques maximales et minimales spécifiées en prenant le pire cas de ces caractéristiques selon la variabilité. Le coût imposé par ces marges mène à un circuit surdimensionné.

Les phénomènes de vieillissement des transistors MOS sont connus depuis les années 70, mais on sait que le circuit doit être soumis à un environnement qui va au delà de ses conditions normales de fonctionnement. Ce sujet avait disparu de l'état-de-l'art pendant quelques décennies puis est réapparu avec les circuits nanométriques. Pourquoi le vieillissement est-il devenu aujourd'hui si important? Les tendances du vieillissement sont très préoccupantes parce que la tension de seuil et la tension d'alimentation n'ont pas suivi le même rythme durant l'évolution des nœuds technologiques des circuits sur puce. Par conséquent, les conditions de fonctionnement auparavant très improbables qui pourraient contraindre le circuit sont devenues des conditions d'environnement courantes.

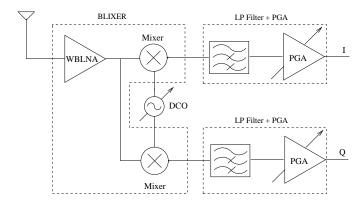

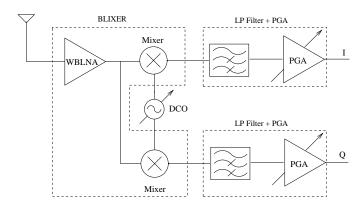

Dans ce scénario, nous sommes motivés à innover dans la conception d'un frontal RF en CMOS 65 nm (voir Figure 1). Nous proposons de nouvelles méthodologies d'analyse et de synthèse, qui comprennent la variabilité et le vieillissement en mettant en évidence les compromis présents parmi les critères de la conception. Le frontal RF a trois principaux blocs de construction: le BLIXER [2], re-

groupant un balun, un amplificateur large bande à faible bruit et un mélangeur I-Q; l'oscillateur contrôlé numériquement (DCO) [3], et l'amplificateur de gain programmable (PGA) avec le filtre passe-bas [4].

Figure 1: L'architecture du frontal radio pour les applications multistandards de communication sans fils : illustration [5].

L'objectif principal de ce travail est d'améliorer la conception de circuits du frontal RF basée sur la recherche des nouveaux compromis imposés par la variabilité du transistor et la dégradation par vieil-lissement. En proposant sur ces deux agents de variation des caractéristiques des circuits sur puce comme critères de conception, nous concevrons un frontal radio fiable pour une application RF multistandard. Ainsi, nous pouvons énumérer nos sous-objectifs qui compléteront cet objectif principal, comme

- 1. L'étude de la physique des phénomènes de vieillissement et des conditions de conception du circuit pour éviter le vieillissement et la variabilité des transistors

- 2. L'étude des sources de dégradation (vieillissement et variabilité) et ses tendances dans les technologies à l'échelle nanométrique

- 3. L'étude des méthodes de conception classique, comparant avec les besoins imposés par la variabilité et la fiabilité des composants

- 4. Une proposition de conception des circuits fiables pour le cas d'étude dans une approche montante (*bottom-up* )

- 5. Une proposition de conception de l'architecture fiable pour le cas d'étude dans une approche descendante (*top-down*)

- 6. Une proposition de généralisation de la méthode de synthèse qui relie les approchesb *bottom-up* et *top-down*

- 7. La comparaison des compromis imposés par le vieillissement et par la variabilité des composants pour la technologie CMOS 65 nm

#### LA VARIABILITÉ ET LA FIABILITÉ DANS LES TECHNOLOGIES AVANCÉES

La variation du processus d'intégration est observée comme la déviation de la valeur des paramètres des circuits sur puce. Ces variations sont dues à différentes causes et ont de nombreuses conséquences. La variabilité du circuit est l'ensemble des variations de paramètres du processus de fabrication, l'imperfection des masques d'intégration et les impacts sur la qualité des circuits entre les différents échantillons.

La variation de performance des circuits intégrés est liée à deux groupes de facteurs [6] :

- Facteurs environnementaux Ils interviennent durant l'opération du circuit comme la source de l'alimentation, le couplage de bruit et la température. Ils sont appelés variations dynamiques et sont fortement dépendant des agents externes et du schéma du circuit.

- Facteurs physiques Ils apparaissent durant la fabrication et ils changent la structure physique des circuits. Ils incluent les RDF (Random Dopant Fluctuations) et la LER (Line Edge Roughness).

Ainsi, les variations des paramètres physiques peuvent être classées en deux catégories : D2D (*Die-to-die*) et WID ( *Within-die*) [7]. Les variations du type D2D sont des variations globales entre différentes puces. Les variations du type WID sont des variations internes à une puce et entre les différents composants qui forment les fonctions intégrées.

La conception de circuits RF plus fiables requiert la connaissance des phénomènes physiques qui réduisent la fiabilité. Les principaux phénomènes physiques à l'origine du vieillissement des dispositifs sont :

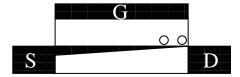

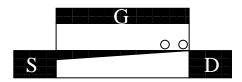

Hot Carrier Injection (HCI) - un phénomène irréversible où une charge a assez d'énergie pour franchir une barrière de potentiel, (généralement du côté du drain, comme illustré par la Figure 2) en créant un défaut d'interface. Il a lieu quand V<sub>GD</sub> est plus grand que zéro et V<sub>GS</sub> est très élevée [1]. Il peut être évité en réduisant le temps pendant lequel les transistors sont en inversion forte, par le contrôle de V<sub>GD</sub> et V<sub>GS</sub>.

Figure 2: Phénomène HCI: illustration.

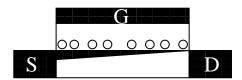

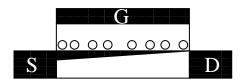

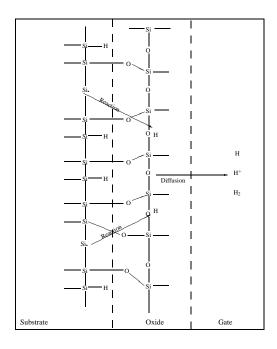

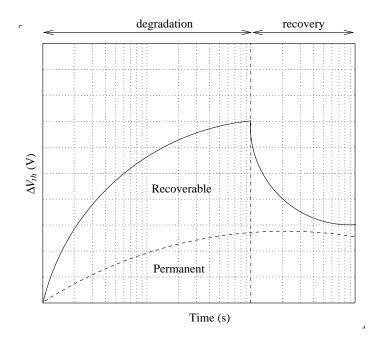

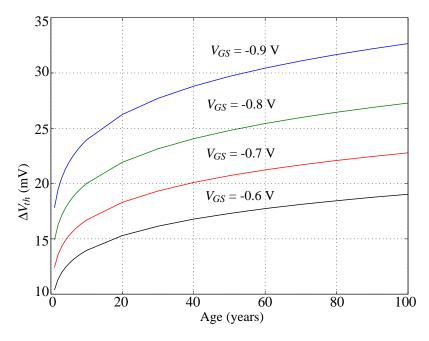

Negative Bias Temperature Instability (NBTI) - un phénomène réversible de dérive des paramètres électriques du transistor sous une tension négative sur la grille et à hautes températures (illustré par la Figure 3). La récupération des paramètres a lieu quand les stress sont arrêtés. Cela implique qu'il est possible d'avoir moins d'impact si le temps de récupération est proportionnellement plus grand que le temps de stress.

Figure 3: Phénomène NBTI: illustration.

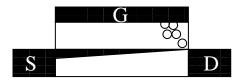

- *Time Dependent Dielectric Breakdown (TDDB)* un phénomène statistique de rupture continue du diélectrique (illustré par la Figure 4), qui par conséquent induit un manque de performance. La probabilité d'avoir le TDDB peut être réduite en contrôlant le courant de fuite par le biais de la réduction de la tension de grille et de la surface du transistor [8].

- *Electromigration (EM)* un phénomène de transport de masse dans la couche de métal. L'EM peut être évitée par la réduction de la longueur et l'augmentation de la largeur des connexions. Aussi, les circuits qui n'utilisent pas de composants passifs (sujet à l'EM) sont plus robustes.

Il n'existe pas de modèle universellement accepté pour la dégradation de fiabilité due aux phénomènes physiques du vieillissement des composants. Nous présenterons les plus importants de l'état-de-l'art.

Figure 4: Phénomène TDDB: illustration.

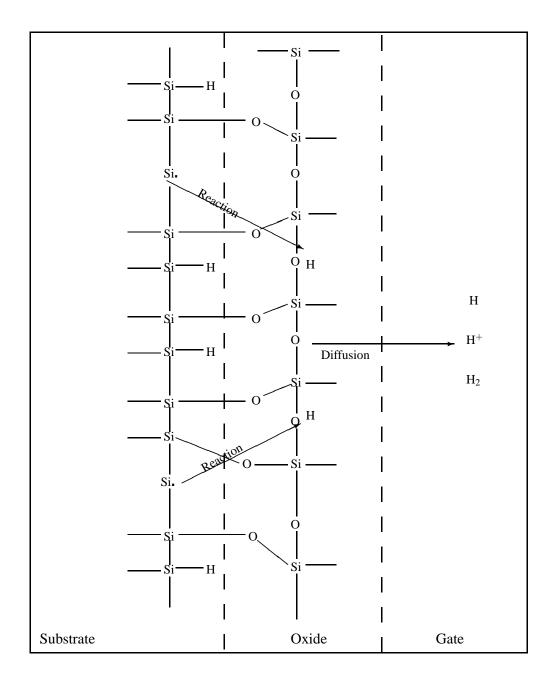

LE MODÈLE DE RÉACTION ET DIFFUSION Le NBTI et le HCI ont des modèles similaires, car les paramètres électriques changent de la même façon après stress. Le modèle le plus accepté est le modèle dit de Réaction et Diffusion. Il est décrit en deux parties :

- 1. **Réaction**: processus de rupture de liaison chimie Si-H dans un défaut d'interface oxyde/substrat et hydrogène libre;

- 2. *Diffusion*: mouvement de l'hydrogène vers l'oxyde jusqu'à la grille.

Le processus de génération de défaut est décrit pour une loi de puissance du temps de stress, et la solution du modèle de Réaction et Diffusion est présenté en [9]. Le modèle de Réaction et Diffusion peut être illustré par la Figure 5

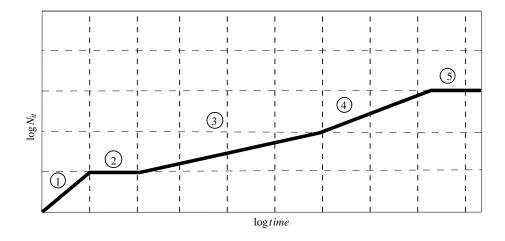

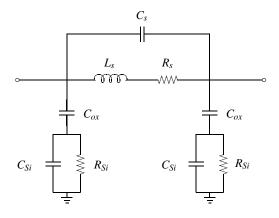

LE MODÈLE DE RUPTURE DE L'OXYDE La probabilité de défaillance pour un événement TDDB est bien décrite avec une distribution de Weibull [10]

$$F(x) = 1 - \exp\left(\left(-\frac{x}{\alpha}\right)^{\beta}\right);\tag{1}$$

où F est la probabilité cumulative de défaut, x peut être charge ou temps,  $\alpha$  est la vie caractéristique pour 63% de probabilité de défaillance et  $\beta$  est le paramètre de forme de Weibull. Après rupture, le chemin de conduction est modélisé par une admittance de faible valeur [11]. Ceci modélise bien les courants de fuite, l'augmentation du bruit, la réduction de fréquence d'opération et la transconductance du transistor.

LE MODÈLE DE L'ELECTROMIGRATION La dégradation par l'EM est évaluée avec le temps moyen de défaillance (MTTF), qui est une méthode d'approximation statistique décrite par [12]

$$MTTF = AJ_e^n \exp\left(\frac{E_a}{kT}\right); \tag{2}$$

où A est une constante caractéristique de la couche de métal et du processus de fabrication,  $J_e$  est la densité de courant,  $E_a$  est l'énergie d'activation de l'EM, k est la constante de Boltzmann et T la température. n est dépendant du résidu de stress et de la densité de courant [13]. Après l'EM, la couche de métal perd sa caractéristique de haute conductance et est modélisée par une résistance parasite en série.

#### ETAT-DE-L'ART DES MÉTHODOLOGIES DE CONCEPTION

L'utilisation des technologies CMOS nanométriques entraîne d'importants défis imposés aux méthodologies de conception de circuits. Défis comprenant [14] :

- L'apparition de courants de fuite non négligeables et l'impact sur la consommation d'énergie;

- L'augmentation de la variabilité des paramètres du procédé technologique ( $V_{th}$ , le niveau de dopage, largeurs, longueurs, et autres);

- La réduction de la source d'alimentation sans que la tension de seuil suive ce rythme, ce qui réduit la dynamique du signal disponible pour les circuits AMS/RF;

- L'apparition de nouveaux matériaux, comme les diélectriques à haut k, et de nouveaux dispositifs, comme FinFET et CNT-FET;

- L'importance croissante des phénomènes de dégradation bien connus, comme HCI, NBTI et EM, et l'avènement de phénomènes de dégradation qui n'étaient pas observés avant, comme SDB et SM.

Ainsi, nous avons réalisé une étude de l'état-de-l'art des méthodes de conception classique, comparant les besoins imposés par la variabilité et la fiabilité des composants.

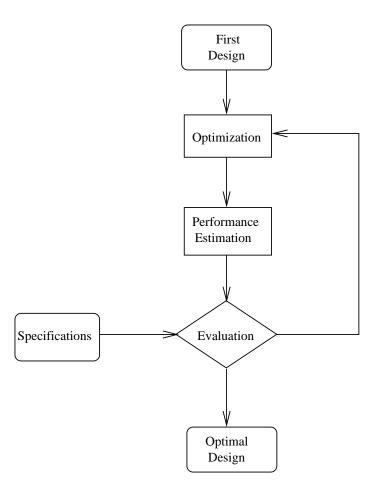

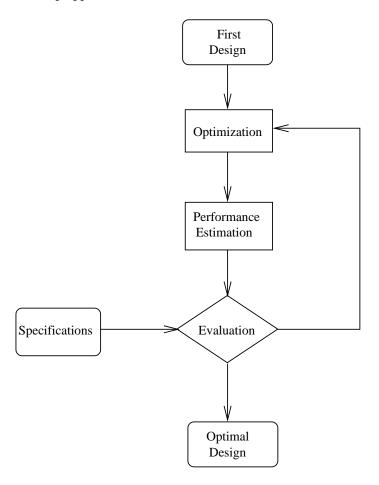

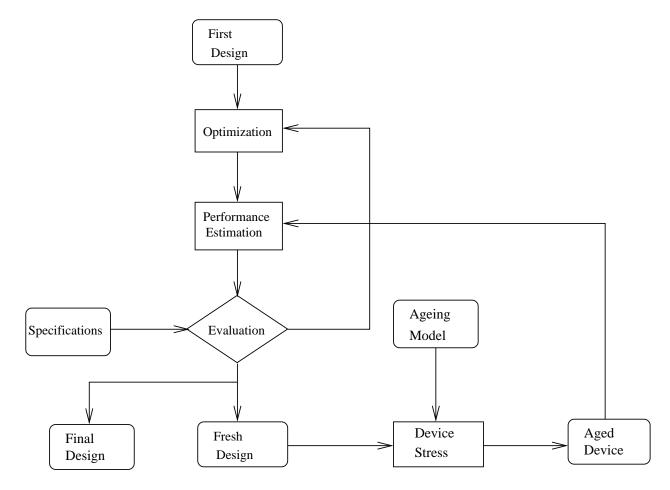

MÉTHODES CLASSIQUES DE CONCEPTION La conception des circuits intégrés peut être divisée en trois parties : la validation de l'architecture en utilisant des modèles comportementaux, la réalisation des schémas électriques, la synthèse des masques d'intégration. La plupart des méthodes de conception dans les différents niveaux hiérarchiques s'appuient sur de puissants outils d'optimisation numérique couplés à des outils d'estimation des caractéristiques, comme illustré dans la Figure 6. Dans l'ensemble de cette partie, nous discutons les avantages et les désavantages des approches *top-down* et *bottom-up*. Ensuite, nous présentons l'état-de-l'art des outils d'optimisation numérique et des outils d'estimation des performances.

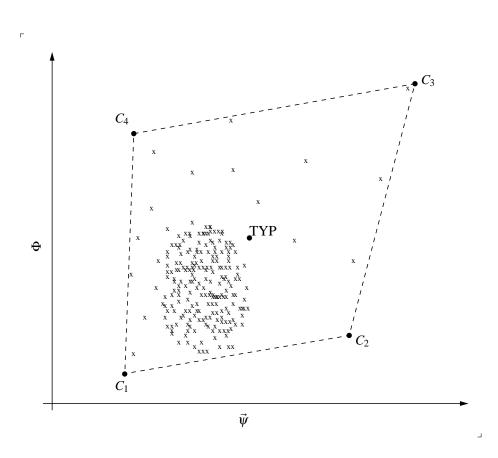

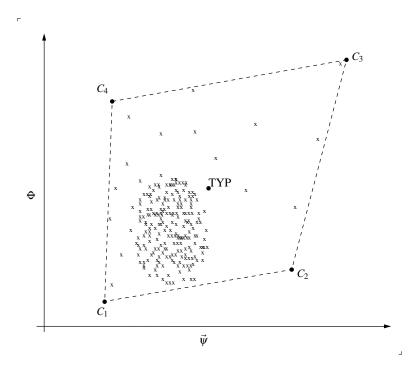

Les méthodes de conception est souvent réalisée par un changement de l'estimateur des caractéristiques des circuits. Les solutions les plus utilisées peuvent être distinguées entre la simulation des *corners* du circuit au pire cas et la simulation de Monte Carlo (illustré dans la Figure 7). Les plus grands désavantages d'une solution basée sur un simulateur sont le coût de calcul et le faible couplage avec l'outil d'optimisation. L'avantage est la précision qui peut être obtenue en utilisant des modèles physiques et des résultats de la caractérisation de circuit sur puce. Une autre solution est de changer l'évaluation dans l'optimisateur en utilisant aussi l'écart-type de la caractéristique et le rendement désiré. Cette solution réduit le coût de calcul et augmente le couplage entre l'estimateur et l'optimisateur au prix de l'utilisation d'un modèle coûteux et moins précis.

L'état-de-l'art ne présente pas un consensus dans le choix de la prise en compte de la variabilité en utilisant des outils commerciaux avec un seul outil de conception automatique. Depuis 2000, S. Nassif a souligné les besoins d'une conception qui prend en compte la variabilité [15]. Actuellement, G. Yu et P. Li ont proposé que la conception analogique soit optimisée non seulement pour les performances nominales, mais aussi pour la prise en compte de la variabilité, afin de maintenir un rendement raisonnable [16]. H. Onodera va plus loin en proposant que les méthodes et les outils de conception automatique doivent tolérer, atténuer, ou même exploiter la variabilité par des techniques appropriées à la conception avec la variabilité [17]. En 2009, V. Wang et al. ont introduit la formulation d'un modèle simplifié pour réduire la lacune entre les méthodes statistiques existantes et la conception de circuits [18].

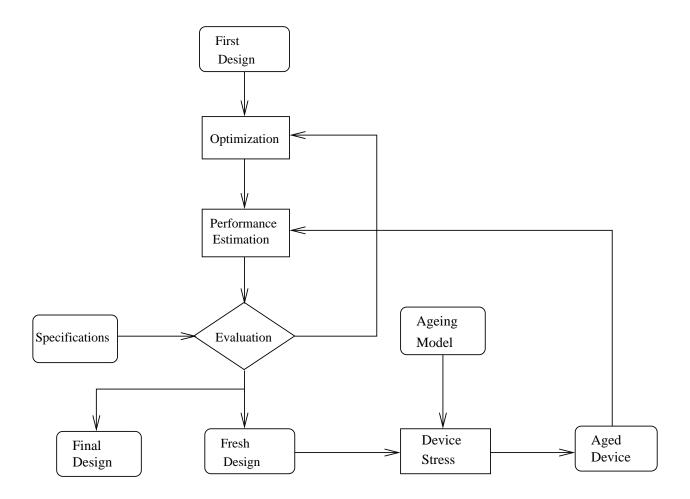

LES MÉTHODES DE CONCEPTION POUR LA FIABILITÉ La prise en compte de la fiabilité dans les méthodes de conception est, à l'état-de-l'art, le développement de l'estimateur des caractéristiques des circuits vieillis (illustré dans la Figure 8). Ce concept a été ouvert avec les outils BERT (*Berkeley Reliability Tools*) et il est utilisé dans la modélisation des phénomènes de vieillissement [19], dans la simulation électrique des circuits vieillis [20, 21] et dans le calcul du temps de vie des composants [22].

L'avantage d'une approche de simulation électrique est la précision des résultats et le désavantage est le coût du calcul. Pourtant, la prise en compte de la fiabilité reste très peut utilisée dans les outils de simulation et les kits d'intégration commerciaux. Ainsi d'un côté, la recherche actuelle vise à améliorer les outils de simulation sans être liée aux données des kits d'intégration commerciaux, d'un autre côté

elle vise à améliorer les techniques de modélisation des phénomènes de vieillissement. Dans l'analyse de la fiabilité on peut distinguer : l'analyse pour un corner nominal, c'est-à-dire sans prendre en compte la variabilité ou en prenant un pire cas de variabilité ; et l'analyse en prenant en compte la variabilité, c'est-à-dire la fiabilité des points de simulation de type Monte Carlo.

#### CONCEPTION D'UN FRONTAL RADIO FIABLE DANS UNE APPROCHE bottom-up

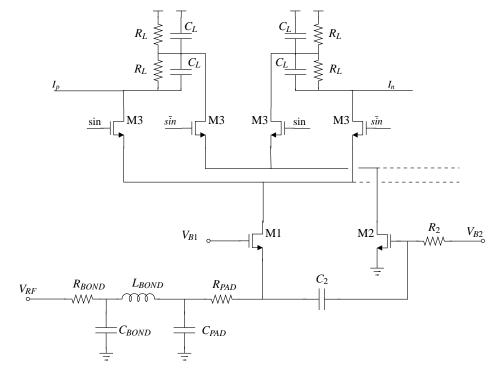

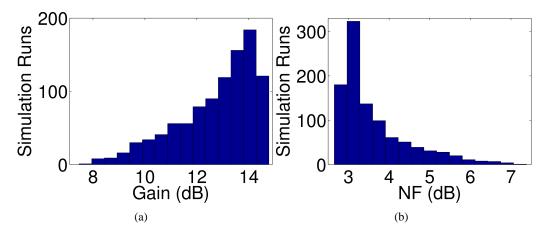

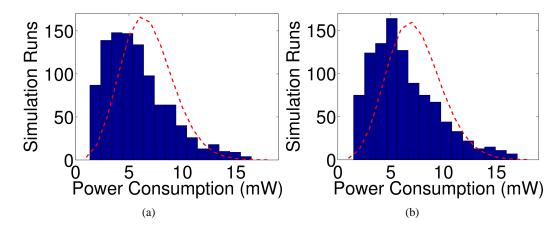

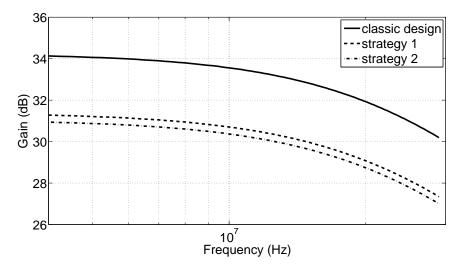

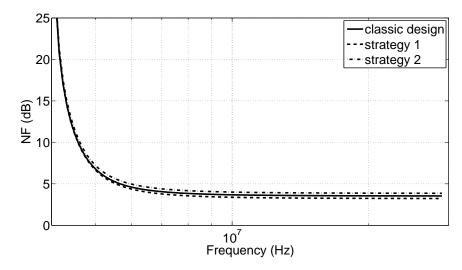

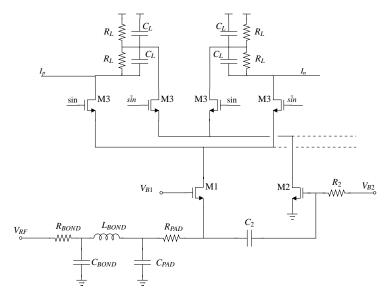

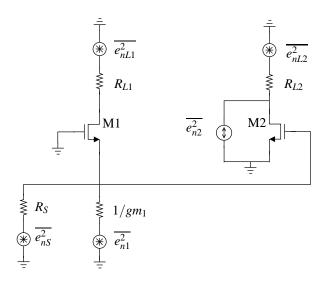

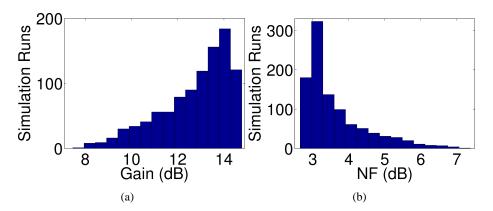

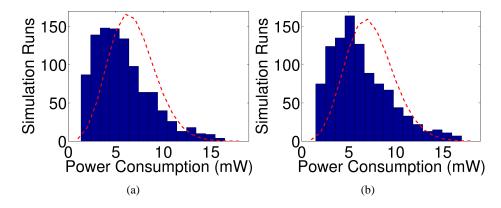

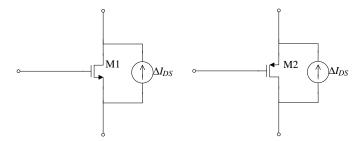

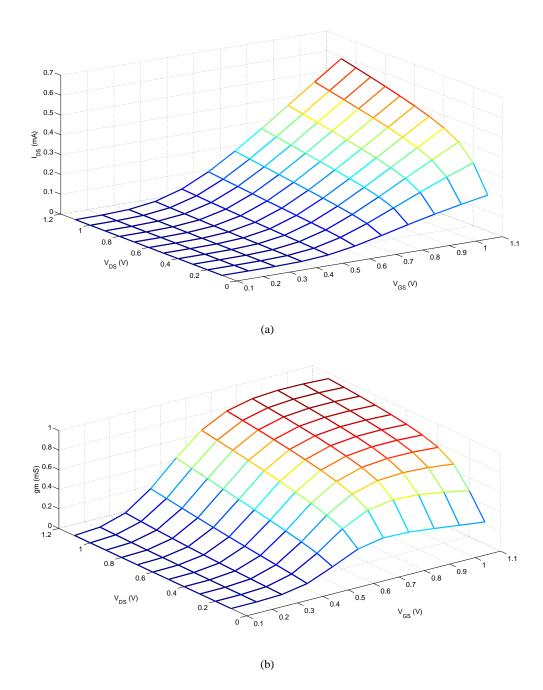

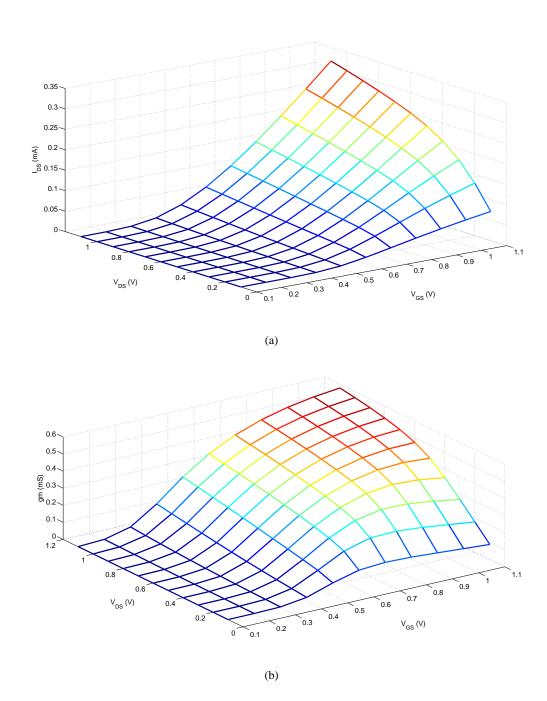

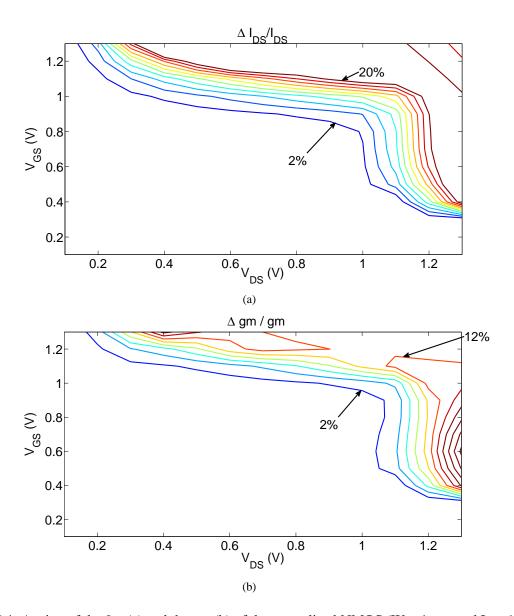

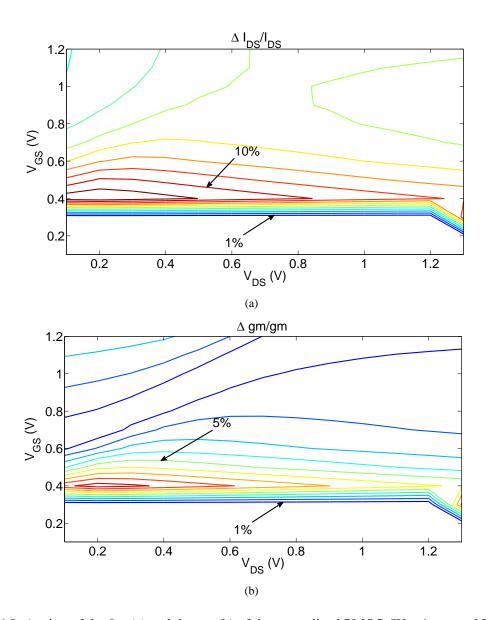

BLIXER Nous avons proposé la conception d'un BLIXER fiable (schéma illustré dans la Figure 9). D'abord, nous avons caractérisé la variabilité et le vieillissement présent en CMOS 65 nm en utilisant les caractéristiques de courant de drain et de transconductance du transistor. Ensuite, nous avons proposé un modèle constructif pour estimer les caractéristiques du BLIXER et la variation des ses caractéristiques par rapport à la variation de courant de drain et de transconductance des transistors. Avec une analyse de sensibilité, nous avons identifié les transistors les plus sensibles et les impacts imposés au BLIXER en raison de la variation des caractéristiques des transistors. Avec ces informations, nous avons trouvé les conditions de polarisation et de dimensionnement qui réduisent les phénomènes de vieillissement. Les résultats obtenus sont illustrés parle Tableau 1 et les Figures 10 et 11.

| Frequency (GHz)        | 1.0   | 2.4   | 5.0    |

|------------------------|-------|-------|--------|

| Power (mW)             | 5.55  | 5.56  | 5.59   |

| Consumption            |       |       |        |

| Differential Gain (dB) | 13.5  | 13.5  | 14.3   |

| $NF_{max}$ (dB)        | 4.0   | 4.5   | 5.3    |

| IP3 (dBm)              | 4.4   | 3.4   | -0.73  |

| S11 (dB)               | -17.6 | -15.4 | - 13.3 |

Table 1: Résultats de simulation du BLIXER : performance typique.

Ces résultats de simulation du circuit typique sont cohérents avec les spécifications d'un frontal radio multistandard. Malgré la variabilité des processus d'intégration et la disparité des dimensions, nous avons observé que les caractéristiques du BLIXER sont conformes aux spécifications pour un rendement supérieur à 90 %. Par ailleurs, le vieillissement du BLIXER est négligeable selon la distribution de Poisson de la consommation de puissance ajusté avec 99,9 % de confiance [23].

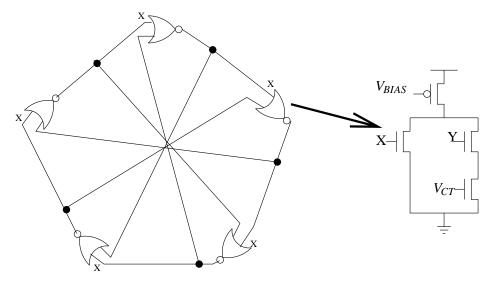

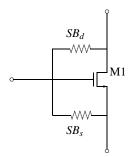

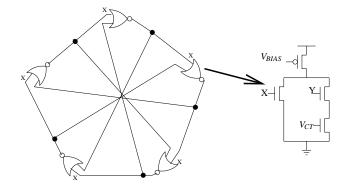

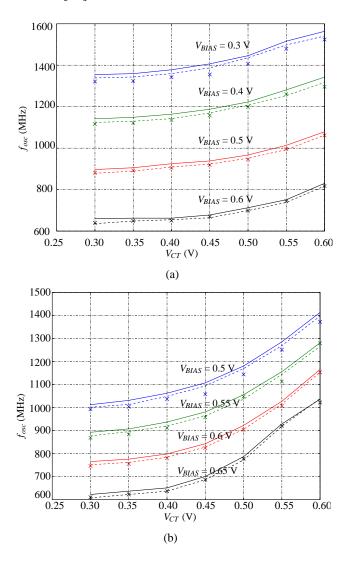

DCO Nous avons proposé une comparaison entre deux DCO: l'un conçu sans les contraintes de vieil-lissement et variabilité et l'autre comme un circuit fiabilisé. Pour cela, nous avons choisi de concevoir un DCO pour les applications à 1 GHz avec le schéma proposé par [24] (illustré dans la Figure 12). Pour la conception classique du DCO, nous avons évalué le compromis entre bruit de phase, plage de fréquence pour le verrouillage et la consommation de puissance. Pour la conception du DCO fiabilisé, nous avons estimé la variation de ces caractéristiques par rapport à la variabilité et le vieillissement.

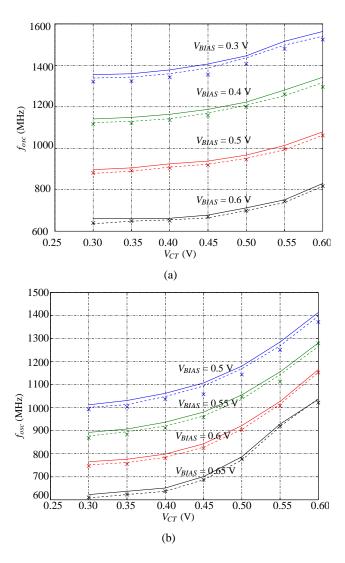

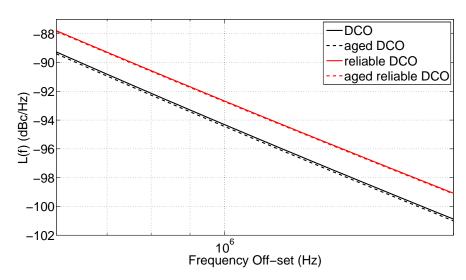

Nous avons développé une analyse de fiabilité du DCO qui nous donne les informations nécessaires pour la conception des circuits plus fiables. En concevant le DCO fiabilisé et non-fiabilisé, nous obtenons une réduction de la dégradation de la fréquence d'une valeur entre 15% et 30 %. Egalement, le DCO fiabilisé a un temps de vie cinq fois plus grand que le non-fiabilisé, si nous fixons la dégradation de la fréquence a un maximum de 2 %. Les inconvénients de la conception du DCO fiabilisé sont l'augmentation du bruit de phase et la réduction de la plage de fréquence disponible pour le verrouillage. Ceci pourrait être négligé dans la spécification d'un standard radio [25].

Les résultats du DCO sont illustrés pas les Figures 13(a), 13(b), 14(a), 14(b), 15(a), 15(b), 16, 17(a), 17(b), 18(a), 18(b).

Figure 5: Le modèle de Réaction et Diffusion: illustration.

Figure 6: Flot de conception classique : illustration des étapes de conception.

Figure 7: L'analyse des corners du circuit au pire cas et la simulation de Monte Carlo: illustration.

Figure 8: L'état-de-l'art des méthodes de conception avec l'analyse du vieillissement.

Figure 9: Schéma du BLIXER conçu [2].

Figure 10: 1000 points de simulation de Monte Carlo du BLIXER typique pour (a) le Gain et (b) le  $NF_{max}$  avec 1 GHz de signal d'éntrée.

Figure 11: 1000 points de simulation de Monte Carlo du BLIXER (a) typique et (b) après 30 ans de vieillissement pour la consommation de puissance en utilisant la bibliothèque de modèle obtenu.

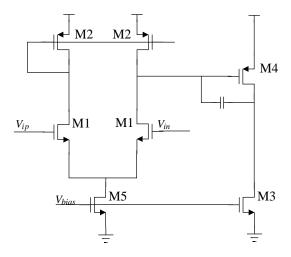

Figure 12: Schéma du DCO conçu [24].

Figure 13: Fréquence d'oscillation du DCO ( $f_{OSC}$ ) simulé à 27  $^{o}$ C pendant 30 ans de dégradation pour (a) le DCO et (b) le DCO fiable. Le résultat avant le stress est représenté par la ligne continue, après le stress par une ligne pointillée et le modèle de vieillissement marquée par x.

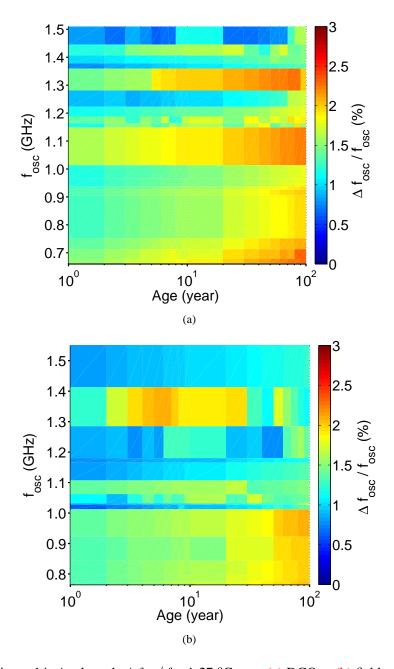

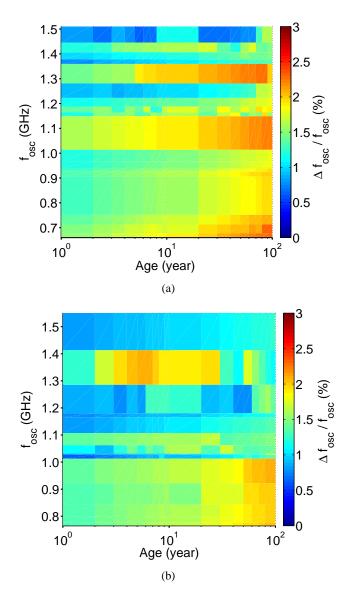

Figure 14: Analyse du  $\Delta f_{osc}/f_{osc}$  à 27  $^{o}{\rm C}$  pour (a) DCO et (b) fiable.

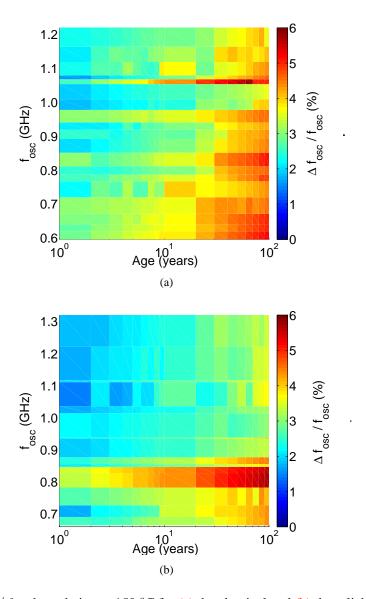

Figure 15: Analyse du  $\Delta f_{osc}/f_{osc}$  à 150  $^{o}{\rm C}$  pour (a) DCO et (b) DCO fiable.

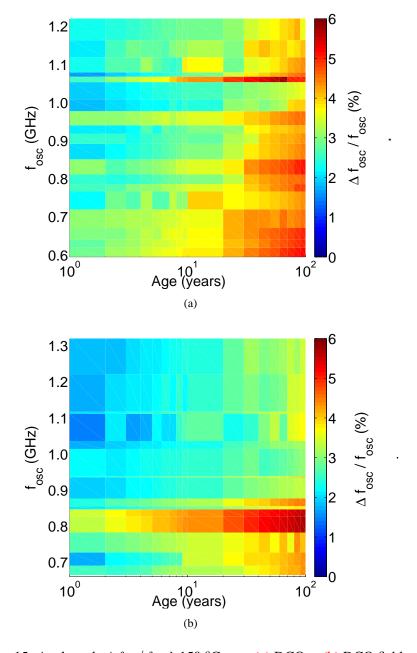

Figure 16: Simulation du bruit de phase du DCO et fiable pour  $f_{osc}=1~\mathrm{GHz}.$

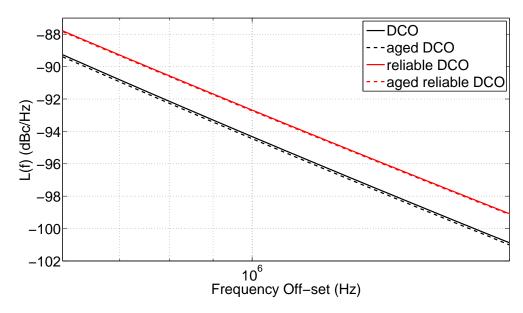

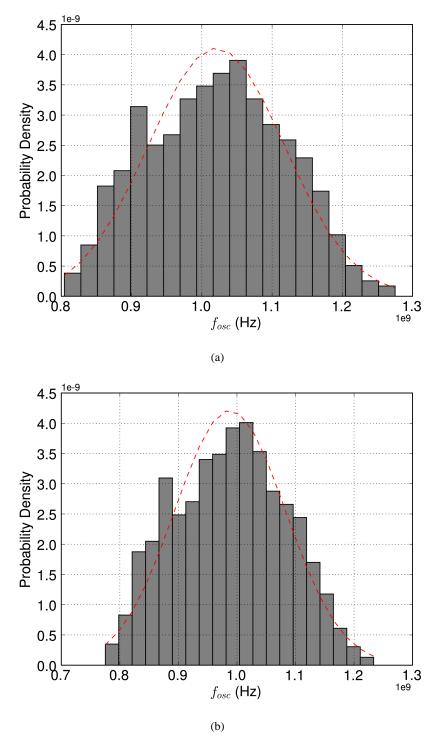

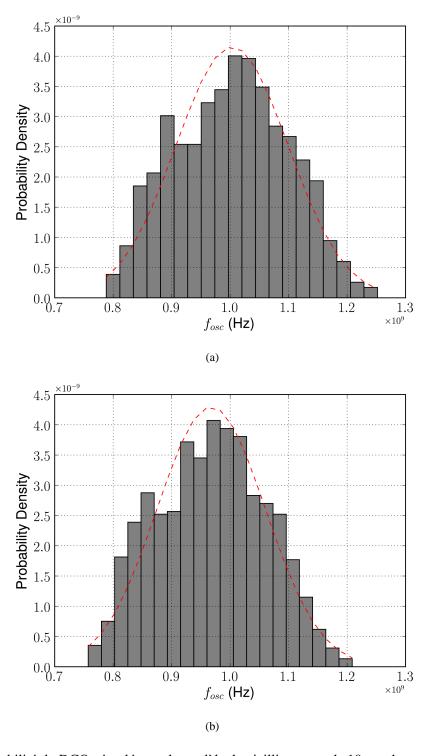

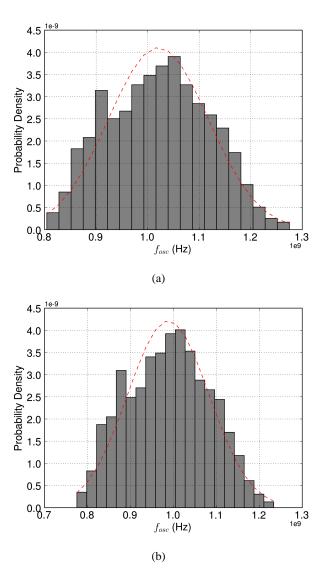

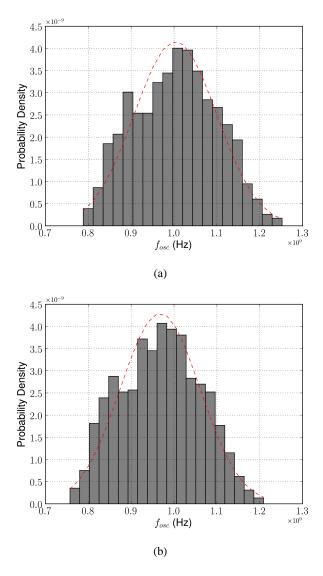

Figure 17: Variabilité du DCO, simulé stress avec  $f_{osc}=1$  GHz pour 1000 de simulation Monte Carlo. (a) DCO avec  $\mu=1.020$  GHz and  $\sigma=97.1$  MHz; et (b) DCO fiable avec  $\mu=0.988$  GHz and  $\sigma=94.7$  MHz.

Figure 18: Variabilité du DCO, simulé avec le modèle de vieillissement de 10 ans de stress avec  $f_{osc}=1$  GHz pour 1000 de simulation Monte Carlo. (a) DCO avec  $\mu=1.003$  GHz et  $\sigma=95.9$  MHz; et (b) DCO fiable avec  $\mu=0.967$  GHz et  $\sigma=92.7$  MHz.

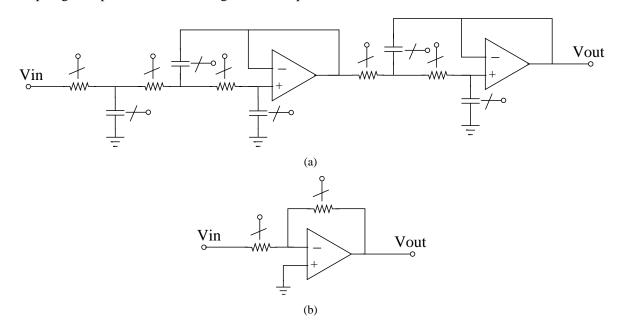

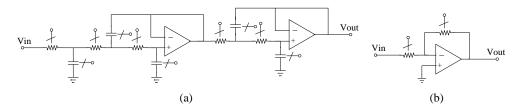

PGA Dans cette partie, nous présentons pourquoi le circuit PGA (illustré dans les Figures 19(a) et 19(b)) est naturellement fiable en utilisant la méthode d'analyse et synthèse développée dans les cas précédents. La topologie la plus courante dans les applications multistandard est composée d'un filtre RC actif et d'un amplificateur [4]. L'analyse de la variation des caractéristiques du PGA montre que le choix des compromis dans une conception non-fiabilisée mène à un ensemble de caractéristiques de l'environnement qui dégrade très peu le transistor. Une autre caractéristique notable est la versatilité de la topologie en permettant la reconfiguration des paramètres du circuit.

Figure 19: Schéma du PGA multi-bande : (a) filtre de bande base et (b) stage de gain programmable.

En ce qui concerne les contraintes de conception, la méthodologie de conception de circuits fiables est capable de montrer que le PGA est naturellement insensible au vieillissement comme présenté dans la conception du BLIXER. La fiabilité du PGA est ainsi directement contrôlée par la fiabilité des circuits de contrôle. Ces circuits sont pour la pluspart des circuits numériques dont la fiabilité n'est pas traitée dans ce travail.

#### CONCEPTION D'UN FRONTAL RADIO FIABLE DANS UNE APPROCHE top-down

La conception d'un frontal radio fiable vis-à-vis des contraintes imposées par la variabilité et le vieillissement passe d'abord par une modélisation de l'architecture choisie. En connaissant les résultats obtenus dans l'approche *bottom-up*, nous pouvons réaliser une analyse des impacts de la défaillance que les blocs de construction peuvent causer aux caractéristiques spécifiées pour un frontal radio multistandard. Les résultats obtenus durant l'analyse de sensibilité sont suffisants pour proposer des stratégies de conception qui vont réduire les impacts aux caractéristiques du frontal radio. La fiabilisation du frontal radio se concrétise en deux solutions différentes qui sont compatibles avec les caractéristiques spécifiées pour un frontal radio multistandard. Ces deux solutions sont ainsi simulées en complétant le flot de conception du frontal radio. Ces résultats de simulation sont comparés au résultat de l'approche *bottom-up* pour conclure les compromis qui sont pris en compte dans chaque stratégie.

MODÉLISATION DU FRONTAL RADIO La modélisation du frontal radio est faite en deux parties : modèles comportemental et analytique. D'abord, nous avons proposé une modélisation comportementale en VerilogA pour pouvoir simuler l'architecture au niveau système. La plupart des blocs de construction et modèles comportementaux sont disponibles pour la mise en œuvre de l'architecture du frontal

radio [26]. Toutefois, l'ensemble des modèles ne dispose pas de caractéristiques nécessaires à la mise en œuvre de la conception des circuits fiabilisés. Ainsi, nous présentons ces détails complémentaires de mise en œuvre du modèle comportemental pour chaque bloc de construction. Les codes VerilogA sont disponibles en annexe.

Ensuite, nous avons développé un modèle constructif pour l'architecture choisie. Ce modèle analytique nous permettra d'évaluer les caractéristiques du circuit et les variations de ces caractéristiques en fonction des défaillances dans les blocs de construction. Le système des équations du modèle analytique obtenu est aussi suffisamment complet pour permettre l'optimisation des caractéristiques de l'architecture et des variations de ses caractéristiques.

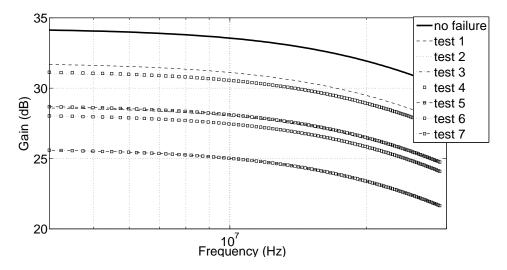

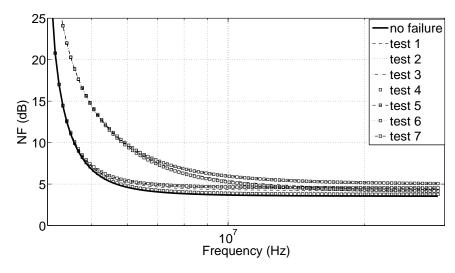

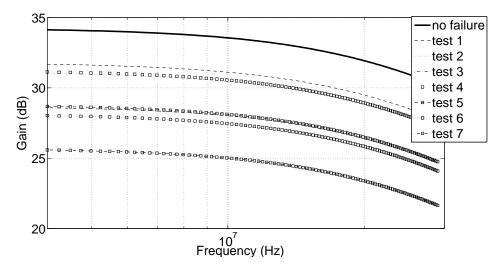

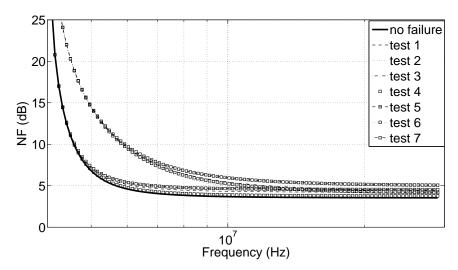

ANALYSE DE DÉFAILLANCE DES BLOCS DE CONSTRUCTION Pour mettre en évidence l'analyse de sensibilité de l'approche top-down, nous avons généré des conditions de défaillance hypothétiques pour les blocs de construction. Ainsi, nous avons évalué l'impact que la défaillance peut causer sur les caractéristiques de l'architecture. Pour cela, nous avons décrit un tableau de tests qui couvrent tous les cas de défaillance des blocs de construction. Les résultats de l'analyse de défaillance des blocs de construction sont illustrés par le Tableau 2 et les Figure 20 et 21

| Cas                | PGA         | DCO         | BLIXER      |

|--------------------|-------------|-------------|-------------|

|                    | défaillance | défaillance | défaillance |

| Pas de défaillance | non         | non         | non         |

| teste 1            | non         | non         | oui         |

| teste 2            | non         | oui         | non         |

| teste 3            | non         | oui         | oui         |

| teste 4            | oui         | non         | non         |

| teste 5            | oui         | non         | oui         |

| teste 6            | oui         | oui         | non         |

| teste 7            | oui         | oui         | oui         |

Table 2: Tableau des cas de test de défaillance pour le frontal.

Figure 20: Résultats de simulation du Gain du frontal radio pour les cas de teste d'analyse de défaillance.

Figure 21: Résultats de simulation du NF du frontal radio pour les cas de teste d'analyse de défaillance.

| Table 3: Résultats de s | simulation du IP3 du fron | tal radio pour les cas de | teste d'analyse de défaillance. |

|-------------------------|---------------------------|---------------------------|---------------------------------|

|                         |                           |                           |                                 |

| Cas                | IP3 (dBm) |

|--------------------|-----------|

| Pas de défaillance | 1.125     |

| teste 1            | 2.127     |

| teste 2            | 1.126     |

| teste 3            | 2.127     |

| teste 4            | 1.125     |

| teste 5            | 2.127     |

| teste 6            | 1.126     |

| teste 7            | 2.127     |

Nous avons trouvé les éléments sensibles et les variations de performance les plus importantes. Nous avons identifié l'amplificateur à gain programmable (PGA) en tant que bloc de construction le plus sensible. La défaillance du circuit PGA est responsable de la dégradation du gain, du bruit, et de la linéarité de l'architecture. Dans les signaux basse fréquence, l'oscillateur à commande numérique (DCO) devient la principale source de dégradation de bruit. Par contre, c'est l'amplificateur de faible bruit (BLIXER) qui est la principale source de dégradation de bruit en haute fréquence [27].

CONCEPTION DU FRONTAL RADIO FIABILISÉ En connaissant les sensibilités des blocs de construction et les impacts des défaillances sur les caractéristiques de l'architecture du frontal radio, nous avons proposé une optimisation des caractéristiques de chaque bloc visant un meilleur compromis entre les caractéristiques, la variabilité et le vieillissement.

D'abord, nous présentons le résultat d'analyse de l'architecture conçue par la méthode classique en connaissant les caractéristiques des blocs de construction. Ensuite, nous discutons un ensemble de stratégies qui peuvent guider une conception fiabilisée du frontal radio. Visant l'équilibre des contraintes dans les compromis de la conception, nous présentons deux solutions possibles dans la prise de la décision pour un frontal radio fiabilisé.

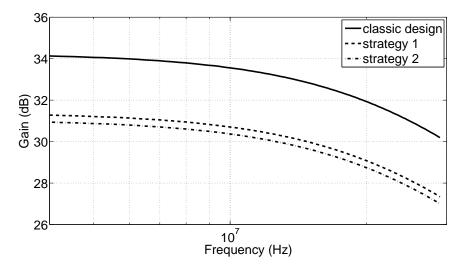

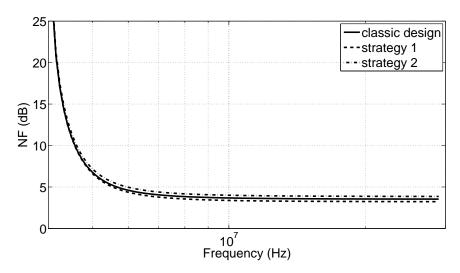

SIMULATION DU FRONTAL RADIO Le résultat obtenu par la méthode classique est comparé aux deux solutions présentées, visant à démontrer les compromis qui ont été pris parmi les caractéristiques des blocs de construction. Nous présentons les résultats simulés pour le gain, le bruit et la linéarité du frontal radio. Ces résultats sont illustrés pas les Tableaux 4, 5 et 6; et Figures 22 et 23.

| Table 4: Performances estimées pour les blocs des constructions du frontal radio. | Table 4: Performances | estimées pour | r les blocs des | s constructions | du frontal radio. |

|-----------------------------------------------------------------------------------|-----------------------|---------------|-----------------|-----------------|-------------------|

|-----------------------------------------------------------------------------------|-----------------------|---------------|-----------------|-----------------|-------------------|

| BLIXER                     | PGA            | DCO                          | Architecture                |

|----------------------------|----------------|------------------------------|-----------------------------|

| G = 14 dB                  | G = 20  dB     | $V_{LO} = 0.25 \text{ V}$    | G = 34.1  dB                |

| NF = 3.5 dB                | NF = 10 dB     | L(1 MHz) =                   | NF=                         |

|                            |                | - 120 dBc/Hz                 | 6.87 dB@5 MHz               |

| $f_{RF} = 5.0 \text{ GHz}$ |                | $f_{LO} = 5.004 \text{ GHz}$ | $f_{IF} = 4 \text{ MHz}$    |

| IP3 = 1.1 dBm              | IP3 = 10.0 dBm |                              | IP3 = $1.12 \text{ dBm}$    |

| $R_{in} = 53 \Omega$       |                |                              | $S_{11} = -15.0 \text{ dB}$ |

Table 5: Performances estimées pour les blocs des constructions du frontal radio fiabilisé avec la stratégie 1.

| BLIXER                     | PGA            | DCO                          | Architecture                |

|----------------------------|----------------|------------------------------|-----------------------------|

| G = 13.9  dB               | G = 16.8  dB   | $V_{LO} = 0.24 \text{ V}$    | G = 30.6  dB                |

| NF = 3.51 dB               | NF = 10 dB     | L(1 MHz) =                   | NF=                         |

|                            |                | - 120 dBc/Hz                 | 6.65 dB@5 MHz               |

| $f_{RF} = 5.0 \text{ GHz}$ |                | $f_{LO} = 5.004 \text{ GHz}$ | $f_{IF} = 4 \text{ MHz}$    |

| IP3 = 1.09 dBm             | IP3 =10.05 dBm |                              | IP3 =1.09 dBm               |

| $R_{in}=61~\Omega$         |                |                              | $S_{11} = -10.0 \text{ dB}$ |

Table 6: Performances estimées pour les blocs des constructions du frontal radio fiabilisé avec la stratégie 2.

| BLIXER                     | PGA            | DCO                          | Architecture                |

|----------------------------|----------------|------------------------------|-----------------------------|

| G = 13.9  dB               | G = 16.8  dB   | $V_{LO} = 0.25 \text{ V}$    | G = 30.8  dB                |

| NF = 3.84 dB               | NF = 10 dB     | L(1 MHz) =                   | NF=                         |

|                            |                | - 119.5 dBc/Hz               | 7.26 dB@5 MHz               |

| $f_{RF} = 5.0 \text{ GHz}$ |                | $f_{LO} = 5.004 \text{ GHz}$ | $f_{IF} = 4 \text{ MHz}$    |

| IP3 = 0.16 dBm             | IP3 =10.05 dBm |                              | IP3 = 0.16 dBm              |

| $R_{in} = 53 \Omega$       |                |                              | $S_{11} = -14.8 \text{ dB}$ |

Avec les résultats de simulation du frontal radio, nous avons démontré la validité des discussions développées durant l'analyse de sensibilité. En plus, nous présentons de manière très claire les compromis présents possibles dans la prise de décision pour un frontal radio fiabilisé. Ainsi, les deux solutions de conception du frontal radio fiabilisé vont constituer des points d'équilibre entre l'optimum de la caractéristique spécifiée et les variations des caractéristiques dues à la variabilité et au vieillissement.

Figure 22: Simulation du gain du frontal radio, et les fiabilisées par les stratégies 1 et 2.

Figure 23: Simulation du NF du frontal radio, et les fiabilisées par les stratégies 1 et 2.

## FLOT DE CONCEPTION DES CIRCUITS FIABLES

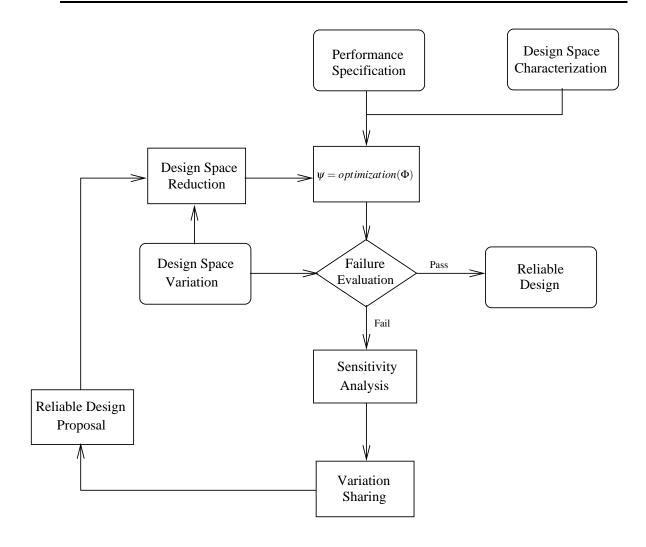

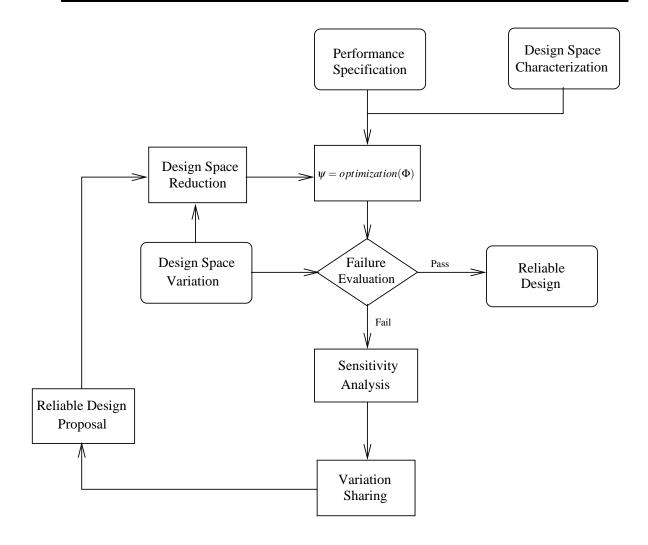

A partir des expériences obtenues dans la conception du frontal radio, nous avons rassemblé les étapes importantes du flot de conception des circuits fiables. Ainsi, nous proposons un nouveau flot de conception pour les circuits AMS/RF qui prend en compte les compromis de la variabilité et du vieil-lissement. Ensuite, nous pouvons démontrer comment ces compromis peuvent influencer les stratégies de conception.

Le flot classique de conception de circuits a besoin des spécifications minimum et maximum des performances. Souvent, les informations sur la technologie d'intégration et les blocs de construction sont disponibles. L'ensemble de ces informations vont constituer ce qu'on appelle l'espace de conception, c'est-à-dire la description des caractéristiques en fonction des choix de conception (par exemple dimensionnement et polarisation).

Prenant en compte les spécifications de performance et la caractérisation de l'espace de conception, une méthode de conception classique permet d'obtenir l'optimum pour les caractéristiques ( $\psi$ ) des dis-

positifs de bas niveau à partir des caractéristiques ( $\Phi$ ) des dispositifs de haut niveau. Si l'optimisation prend déjà en compte la variabilité (comme en [18]) et que le stress de vieillissement n'est pas assez élevé en comparaison aux besoins de fiabilité, il est possible que ce circuit optimal satisfasse à l'évaluation de défaillance. Donc, nous avons un circuit optimal et fiable comme il est apparu dans les exemples de conception des circuits BLIXER et PGA. Pourtant, si la variation des caractéristiques du dispositif n'est pas nulle, cela signifie qu'il a souffert soit de variabilité, soit de vieillissement.

C'est clair qu'il est important de refaire l'étape d'optimisation, mais il faut apporter des éléments qui guideront l'optimiseur vers une solution aussi fiable. Donc, nous avons proposé l'analyse de sensibilité des dispositifs comme point de départ de la fiabilisation du circuit. Cette analyse est appliquée au même modèle utilisé dans l'étape d'optimisation et va conduire à une mesure de faiblesse des dispositifs. Avec l'expérience des concepteurs, ces chiffres vont constituer des poids pour le partage de la variation estimée dans l'étape précédente entre les variations autorisées aux caractéristiques des dispositifs de bas niveau.

Le partage des variations est un problème classique de prise de décision qui peut converger à un optimum ou présenter des points d'équilibre. Ainsi, nous discutons les stratégies possibles qui guideront la prise de décision. Dans la conception du DCO, nous avons présenté une stratégie assez simple guidée par les informations sur la variation de l'espace de conception. Cela signifie spécifier un nouveau jeu des caractéristiques pour atteindre les spécifications du circuit pour un certain rendement et fiabilité. Pourtant, ces stratégies peuvent être plus complexes et aboutir à un certain compromis pour relâcher la conception d'un bloc et rendre stricte la conception d'autres blocs, comme dans l'exemple présenté dans l'approche top-down.

Finalement, l'optimisation sera bouclée avec un nouveau jeu des caractéristiques à atteindre et un espace de conception réduit. Il est bien possible que l'optimisation ne soit pas capable d'obtenir le nouvel optimum qui va aboutir à la faisabilité du circuit avec ses spécifications de performance, rendement et fiabilité. Par contre, s'il existe un optimum il pourra être fiable ou pas, ce qui va aboutir au besoin de fiabilisation du circuit. La fiabilisation du circuit, que nous avons élaborée, constitue un nouveau flot de conception qui prend en compte la variabilité et le vieillissement. Ce flot de conception des circuits fiables est résumé dans la Figure 24.

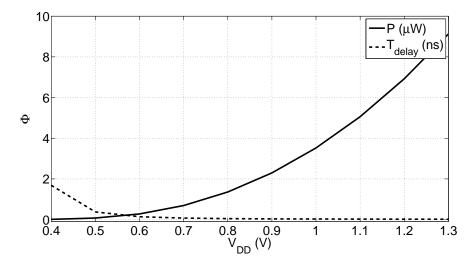

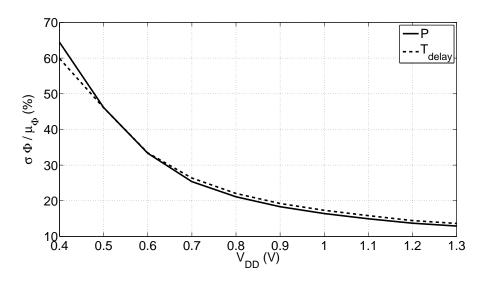

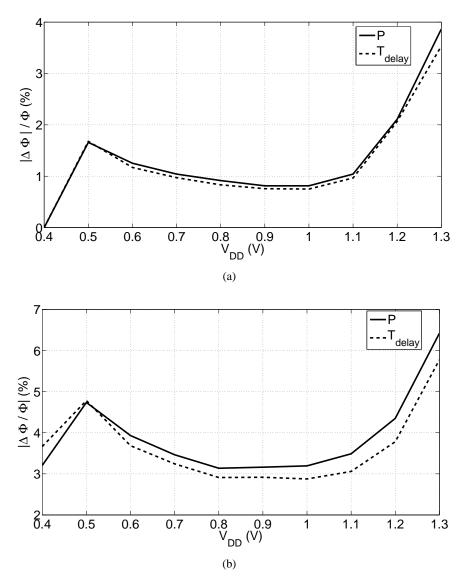

Pour mettre en évidence la faisabilité des circuits dans les compromis existants parmi leurs spécifications de performance, rendement et fiabilité, nous démontrons ces compromis pour un oscillateur en anneau avec 13 portes inverseurs. L'oscillateur en anneau est un circuit souvent utilisé pour évaluer une technologie d'intégration. Faisant varier la tension d'alimentation, nous pouvons analyser le compromis entre consommation de puissance de chaque porte et sa vitesse par le délai de la porte.

Pourtant ces deux spécifications vont certainement changer avec la variabilité et le vieillissement des transistors. Pour cela, nous allons simuler ce circuit conçu en CMOS 65 nm sous un stress de 27°C de température, jusqu'à une tension d'alimentation 10 % plus grande que la valeur spécifiée dans la technologie d'intégration et 30 ans de vieillissement. Nous mettons en évidence une variabilité proche de 30 % et un vieillissement proche de 1 % pour le point optimum du compromis entre consommation de puissance et vitesse. Donc, nous mettrons en évidence que le vieillissement sera souvent négligeable par rapport à la variabilité dans l'optimisation des compromis des performances en utilisant la technologie CMOS 65 nm sous un stress comparable aux conditions d'environnement courantes.

#### Conclusion

Ce travail de thèse a proposé un nouveau flot de conception des circuits fiables en s'appuyant sur la conception d'un frontal radio. Ainsi, nous arriverons à notre but principal qui était d'améliorer la conception de circuits du frontal RF. Durant ce travail, nous sommes à la recherche de nouveaux compromis imposés par la variabilité du transistor et dégradation par vieillissement. D'après ce nouveau compromis, nous avons proposé des stratégies de partage de la variation des caractéristiques des circuits entre les caractéristiques des blocs de construction.

Dans la recherche de l'état-de-l'art, nous avons étudié la physique des phénomènes de vieillissement

Figure 24: Flot de conception des circuits fiables: illustration des étapes de conception.

et des conditions de conception du circuit qui permettent d'éviter le vieillissement et la variabilité des transistors. Ensuite, nous avons étudié les sources de dégradation (vieillissement et variabilité) et ses tendances dans les technologies à l'échelle nanométrique. Enfin, nous avons présenté les méthodologies de conception classiques, comparant les besoins imposés par la variabilité et la fiabilité des composants.

Nous avons mis en œuvre des circuits fiables pour le cas d'étude du frontal radio dans une approche bottom-up. Par ailleurs, nous avons mis en œuvre l'architecture fiable pour le cas d'étude du frontal radio dans une approche top-down. Ainsi, nous avons pu lier les étapes de la conception top-down et bottom-up dans une méthode générale qui est la proposition d'un nouveau flot de conception des circuits fiables.

La conception des circuits fiables met en évidence le nouveau compromis entre les performances nominales désirées, les attentes de rendement et de temps de vie pour le circuit. Par la démonstration des compromis imposés par le vieillissement et la variabilité des composants en CMOS 65 nm, nous sommes capables de prédire les tendances dans les technologies à venir et mettre en évidence le besoin d'un flot de conception des circuits AMS/RF qui prend en compte les dégradations des performances pour le vieillissement et la variabilité.

## **ABSTRACT**

In this work, we have been motivated to innovate in RF front-end design. New analysis and synthesis methodologies have been proposed including the variability and the ageing degradation in the center of the design trade-off. Moreover, the variability and the ageing degradation criteria have motivated us to propose changes in the classical design methodology with aim of a variability-aware and ageing-aware synthesis. Thus, the main objective of this work has been to improve the design of AMS/RF front-end circuits based on the investigation of a new trade-off imposed by transistor variability and ageing degradation. Aiming the proposition of both agents of characteristics variation as design criteria, we have designed a reliable RF front-end for a multi-standard application.

This state-of-the-art research has described, as best as we know, the sources and the trends of the device-performance variations. Variations will be separated as static or at time zero, and dynamic or time-dependent variation. The *static* variations will be represented by integration of process variability and devices mismatch. The *dynamic* variations will be represented by probabilistic events and device ageing. The knowledge of the physical mechanisms of variability and ageing has been essential to propose an improved design methodology aiming at more reliable devices. Furthermore, we have described, as best as we know, the state-of-the-art of design methodologies. The challenges and solutions for AMS/RF design in advanced CMOS technology have been presented. The classical design methodologies have been divided in three parts: architectural behavioral-model validation, electrical schematic implementation, layout synthesis. Most of variability-aware design methodologies have presented worstcorner and Monte Carlo simulation for design verification and performance estimation. However, some few works have been describing the variability-aware design methodologies using behavioral modeling and so improving the design optimization. Moreover, the reliability-aware design methodologies have been mostly concentrated on reliability analysis around a nominal corner. Few works have presented the combination of variability and ageing phenomena under a reliability analysis. Hence, we have identified an opportunity to innovate by proposing the reliability estimation in early design stages.

We have innovated by proposing AMS/RF circuit reliability improvements during the design of the multi-standard RF front-end using a bottom-up approach. First, the reliable-BLIXER design with a failure evaluation has been proposed in [23]. Next, the validation of a reliable-circuit synthesis method using a DCO design has been conducted. By designing a classical- and a reliable-DCO, we have published such analysis and discussions in [27] and [28]. Then, the PGA and the required elements to design a reliable-PGA have been analyzed. Furthermore, we have innovated by proposing architecture reliability improvements during the design of the RF front-end using a top-down approach. In this case, we have discussed the design of a reliable architecture for RF front-end and the variation sharing strategies to avoid an overdesign. We have published such analysis and discussions in [27]. Therefore, we have innovated linking top-down and bottom-up approaches in a general method which has been the proposition of a new AMS/RF design flow increasing the circuit reliability. The design of reliable circuits has highlighted a new trade-off among typical performance specification, the yield requirements and the circuit lifetime.

Therefore, our major objective has been successfully achieved; while improving the design of AMS/RF front-end circuits based on the investigation of new trade-offs imposed by transistor variability and ageing. Finally, we could point some research perspectives in: new analysis tools, new design models, and new synthesis methods; linking variability and ageing.

## LIST OF SYMBOLS

AMS Analog Mixed Signal

CMOS Complementary Metal Oxide Semiconductor

CAD Computer-Aided Design

DE Differential Evolution

DoE Design of Experiments

$\Delta\Phi$  Variation of  $\Phi$  (defined by  $\Phi_{worst} = \Phi_{typ} \pm \Delta\Phi$ )

D2D Die-to-die

EA Evolutionary Algorithms

EDA Electronic Design Automation

EM Electromigration

GP Geometric Program

HBD Hard Oxide Breakdown

HCI Hot Carrier Injection

IC Integrated Circuit

IP Intellectual Property

IP3 Third-order Input Intercept Point

LER Line Edge Roughness

LHS Latin Hypercube Sampling

MC Monte Carlo

MOS Metal Oxide Semiconductor MTTF Median Time to Failure

NBTI Negative Bias Temperature Instability

NMOS n type MOS transistor

OTA Operational Transconductance Amplifier  $\Phi$  a general circuit or system performance  $\psi$  a general circuit or system parameter

PA Power Amplifier

PDF Probability Density Function

PDK Process Design Kit

PMOS p type MOS transistor

QMC Quasi Monte Carlo

RDF Random Dopant Fluctuations

RF Radio Frequency

RSM Response Surface Model

SA Simulated Annealing

SBD Soft Oxide Breakdown

SiP Systems in a Package

SM Stress Migration

SoC Systems on Chip

SOI Silicon-On-Insulator

TDDB Time Dependent Dielectric Breakdown

$V_{DS}$  Drain-to-source voltage  $V_{GD}$  Gate-to-drain voltage  $V_{GS}$  Gate-to-source voltage

$V_{ov}$  Overdrive voltage  $V_{ov} = V_{GS} - V_{th}$

$V_{SB}$  Source-to-bulk voltage  $V_t$  Thermal voltage  $V_{th}$  Threshold voltage

VLSI Very Large Scale Integration

WID Within-die

# **CONTENTS**

| A  | cknow   | vledgements                                        | iii  |

|----|---------|----------------------------------------------------|------|

| Ré | ésumé   | é Étendu                                           | v    |

| Al | bstrac  | et 2                                               | xxix |

| Li | st of S | Symbols                                            | xxxi |

| 1  | Intr    | roduction                                          | 1    |

|    | 1.1     | Motivation                                         | 2    |

|    | 1.2     | Study Case Design                                  | 4    |

|    | 1.3     | Objective                                          | 4    |

|    | 1.4     | Organization                                       | 5    |

| 2  | Vari    | iability and Ageing in Advanced Technologies       | 7    |

|    | 2.1     | Introduction                                       | 7    |

|    | 2.2     | Sources of Variability                             | 8    |

|    |         | 2.2.1 Die-to-die (D2D) variations                  | 8    |

|    |         | 2.2.2 Within-die (WID) variations                  | 9    |

|    | 2.3     | Variability Trends                                 | 9    |

|    | 2.4     | Ageing Physical Phenomena                          | 10   |

|    |         | 2.4.1 Hot Carrier Injection (HCI)                  | 10   |

|    |         | 2.4.2 Negative Bias Temperature Instability (NBTI) | 12   |

|    |         | 2.4.3 Time Dependent Dielectric Breakdown (TDDB)   | 13   |

|    |         | 2.4.4 Electromigration (EM)                        | 15   |

|    | 2.5     | Ageing Trends                                      | 16   |

|    |         | 2.5.1 Hot Carrier Injection (HCI)                  | 16   |

|    |         | 2.5.2 Negative Bias Temperature Instability (NBTI) | 16   |

|    |         | 2.5.3 Time Dependent Dielectric Breakdown (TDDB)   | 16   |

|    |         | 2.5.4 Electromigration (EM)                        | 17   |

|    | 2.6     | Ageing Degradation Mechanisms                      | 18   |

|    |         | 2.6.1 Microscopic model                            | 18   |

|    |         | 2.6.1.1 SiO <sub>2</sub> /poly-Si technology       | 18   |

|    |         | 2.6.1.2 SiON/metal-gate technology                 | 19   |

|    |         | 2.6.1.3 High-k/metal-gate technology               | 19   |

|    |         | 2.6.2 Reaction-Diffusion model                     | 20   |

|    | 2.7     | Conclusion                                         | 23   |

| 3 | State | e-of-the | -art of Design Methodologies 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1   |          | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 3.2   |          | ral Design Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |       | 3.2.1    | Top-down and Bottom-up EDA approaches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |       | 3.2.2    | Optimization Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |       |          | 3.2.2.1 Gradient Descent Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |       |          | 3.2.2.2 Geometric Programming Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |       |          | 3.2.2.3 Simulated Annealing Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |       |          | 3.2.2.4 Evolutionary Algorithms Optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |       | 3.2.3    | Performance Estimation Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

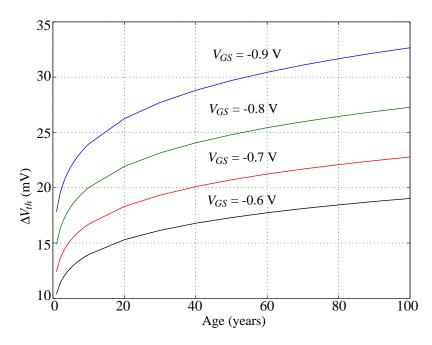

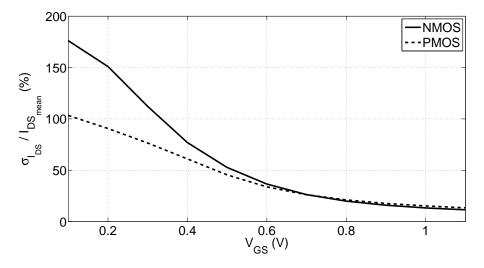

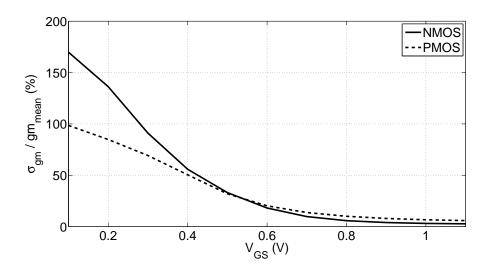

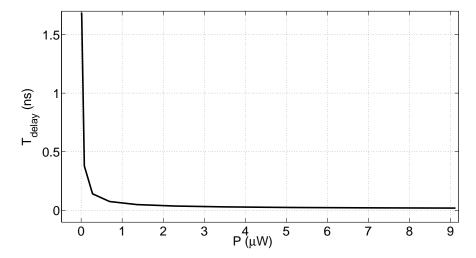

|   |       |          | 3.2.3.1 Performance Behavioral Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |