## Network on chip based multiprocessor system on chip for wireless software defined cognitive radio

Muhammad Imran Taj

### ► To cite this version:

Muhammad Imran Taj. Network on chip based multiprocessor system on chip for wireless software defined cognitive radio. Other. Université Paris-Est, 2011. English. NNT: 2011PEST1050. pastel-00665786

### HAL Id: pastel-00665786 https://pastel.hal.science/pastel-00665786

Submitted on 2 Feb 2012  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Doctorate Thesis / Thèse de doctorat

Université Paris-Est, ESIEE Paris, Laboratoire LIGM, École Doctorale Maths STIC, Spécialité: Electronique, Optronique et Systèmes

Presented and defended publicly by / Présentée et soutenue publiquement par

## **Muhammad Imran TAJ**

12<sup>th</sup> September 2011/ le 12 Septembre 2011

Title / Titre:

# Network on chip based Multiprocessor System on Chip for Wireless Software Defined and Cognitive Radios

Thesis supervised by: / Thèse dirigée par:

Prof. M. Akil (LIGM, ESIEE Paris, France). Prof. O. Hammami (LEI, ENSTA ParisTech, France).

### **Jury Composition :**

| Professeur Yves LOUËT (SUPELEC Rennes, France )                   | Rapporteur   |

|-------------------------------------------------------------------|--------------|

| Professeur Jiří MASOPUST (FEL Plzeň, République Tchèque)          | Rapporteur   |

| Professeur Geneviève BAUDOIN (ESYCOM, ESIEE Paris, France)        | Examinatrice |

| Professeur Serge WEBER (Université Henri Poincare Nancy, France ) | Examinateur  |

| Professeur Mohamed AKIL (LIGM, ESIEE Paris, France)               | Directeur    |

| Professeur Omar HAMMAMI (LEI, ENSTA ParisTech, France)            | Co-directeur |

## Acknowledgements

First of all, I acknowledge my deepest gratitude and appreciation to my supervisor Professor M.Akil for his guidance and persistent help throughout my doctoral studies. Your professional support helped me to identify and to understand actual research problems and to pursue their solutions. Thank you for your patience, for countless thoughtful long technical discussions and for your friendly attitude as it has greatly contributed to my professional and personal growth and made it possible to complete this work.

Thanks to the co-supervisor Professor Hammami for having introduced me to the academic team at ESIEE Paris. Without his initial support and advice, this work could not have started. He has played an invaluable part in both my graduate studies and PhD Work. My acknowledgements are equally due for Professor Huggins for his guidance about the technical management which I used throughout this thesis.

I am grateful to all members of the jury for taking their time reading this thesis. Professor Louet's excellent comments helped me to immensely improve the manuscript. The remarks of Professor Masopust also helped to increase the readability of this manuscript. Professor Baudoin, apart from being external examiner, has been very kind to me throughout the thesis. She sent me all the relevant passwords to access IEEE articles and other online libraries. She has created a very wonderful research environment at ESIEE, without which I would have never been able to make it up. My thanks are equally due for Professor Weber, who very kindly accepted to participate as an external examiner.

I wish to express my thanks to the administrative staff at both universities, ESIEE and ENSTA for their kind help and assistance during the course of this research.

My sincere thanks go to my dear colleagues and friends from both the laboratories in ESIEE and ENSTA. The last three years have been an unforgettable experience for me and it has been a great pleasure to spend these moments with them, either in the laboratory or simply around a table during the pause-café.

My best friends, Laurent Fontaine and Ali Iqbal, have always been there for me throughout this period. I am highly indebted to them for their indirect positive impact on this work. Laurent's parents, Dominique and Jean François, have been a constant source of support and encouragement. Last, but truly not least, I want to thank to my parents for being with me and for having taught me to live and to love the moments of life we have. The work done in this thesis is a result of their indirect efforts and sacrifices they have made during whole of my childhood and youth. It would have never been possible without their unconditional love, support and understanding.

## Abstract

Software Defined Radio (SDR) and Cognitive Radio (CR) are entering mainstream. These high performance and high adaptability requiring devices with agile frequency operations hold promise to:

- 1. address the inconsistency between hardware and software advancements,

- 2. real time mode switching from one radio configuration to another and

- 3. efficient spectrum management in under-utilized spectrum bands.

Framed within this statement, in this thesis we have implemented a SDR waveform on 16 Processing Element (PE) Network on chip (NoC) based general purpose Multiprocessors System on chip (MPSoC), with access to four external DDR2 memory banks, which is implemented on a single chip Xilinx Virtex-4 FPGA. We shifted short term development of a waveform into software domain by designing an efficient parallelization and synchronization strategy for each waveform component, individually. We enhance our designed waveform functionality by proposing and implementing three Artificial Neural Networks Schemes: Self Organizing Maps, Linear Vector Quantization and Multi-Layer Perceptrons as effective techniques for reconfiguring CR Transceiver after recognizing the specific standard based on input parameters, pertaining to different layers, extracted from the signal. Our proposed adaptive solution switches to appropriate Artificial Neural Network, based on the features of input signal sensed. We designed an efficient synchronization and parallelization strategy to implement the Artificial Neural Networks based CR Transceiver Algorithms on the aforementioned MPSoC chip. The speed up we obtained for our SDR waveform and CR Transceiver algorithms demonstrated that the general purpose MPSoC devices are the most efficient answer to the acquisition challenge for major organizations that invest or plan to invest in SDR and CR based devices, thereby allowing us to avoid expensive hardware accelerators. We address the case of a complex signal composed of many modulated carriers by dividing the PEs in individual groups, thus received signal with more than one Standard is processed efficiently. We add further functionality in our designed Multi-standard CR Transceiver possessing SDR Waveform by proposing a new approach for radio spectrum management, perhaps the most important aspect of CR. We make our designed waveform Spectrum efficient by modelling the primary user signal Radio Frequency features as a Non-linear Autoregressive Exogenous (NARX) time series, which is then given as input to Elman Recurrent Neural Network that predicts the evolution of Radio Frequency Time Series to decide if the secondary user can exploit the Spectrum band. We exploit the inherent cyclostationary in primary signals for NARX Time Series Modeling of Radio Frequency features, as predicting one RF feature needs the previous knowledge of other relevant RF features. We observe a similar trend between predicted and actual values.

Ensemble, our designed Spectrum Efficient SDR waveform with a Universal Multi-standard Transceiver answers the SDR and CR performance requirements under resource constraints by efficient algorithm design and implementation using lateral thinking that seeks a greater cross-domain interaction.

**<u>Key-words</u>:** SDR waveform, CR Multi-standard Transceiver, MPSoC, Artificial Neural Networks, Spectrum Evolution Prediction.

# **Abstract (in French)**

La Radio Logicielle (SDR : Software Defined Radio) et la Radio Cognitive (CR : Cognitive Radio) deviennent d'un usage courant car elles répondent à plusieurs enjeux technico-économiques majeurs dans le domaine des télécommunications. Ces systèmes radio permettent de combler l'écart de développement technologique qui existe entre la partie matérielle et la partie logicielle des systèmes de communication, en permettant la gestion optimale des bandes de fréquences sous-utilisées par la commutation en temps réel d'une configuration radio à une autre.

Dans ce cadre, cette thèse présente la mise en œuvre d'une chaîne de traitements Radio Logicielle (appelé SDR waveform) dans un Système Multiprocesseurs sur Puce (MPSoC) à usage général (implémenté dans un FPGA de type Xilinx Virtex-4). Cette plate forme est basée autour d'un Réseau sur Puce (NoC) interconnectant 16 processeurs élémentaires (appelés PE) disposant de quatre blocsmémoires externes DDR2. Nous avons proposé des implémentations temps réel et embarquées sur MPSoC de différentes briques de traitements d'une chaîne SDR, en concevant une stratégie efficace de parallélisation et de synchronisation pour chaque composante élémentaire de la « waveform ». Nous avons amélioré la fonctionnalité de la chaîne de traitement Radio Logicielle, en intégrant un Transceiver reconfigurable basé sur différents modèles de Réseaux de Neurones Artificiels (RNA) : les Cartes Auto-Organisatrices (SOM), les Réseaux de Neurones Compétitifs (LVQ) et enfin les Réseau Multi-Couches de Perceptrons (MLP). Ces trois RNA permettent la reconnaissance de la norme spécifique basée sur les paramètres d'entrée extraits du signal et la reconfiguration du Transceiver de CR. La solution adaptative que nous avons proposée commute vers le RNA le plus approprié en fonction des caractéristiques du signal d'entrée détecté. Il est important de pourvoir prendre en compte des signaux complexes et multi-porteuses. Dans ce cadre, nous avons adressé le cas d'un signal complexe composé de plusieurs porteuses, ainsi en divisant les PEs en différents groupes indépendants, nous affectons chaque groupe de PEs au traitement d'une nouvelle porteuse. Nous avons conçu une stratégie efficace de synchronisation et de parallélisation de ces trois RNA pour CR Transceiver. Nous l'avons appliquée, par la suite pour l'implantation des nos algorithmes sur le MPSoC déjà cité.

L'accélération que nous obtenons pour la SDR waveform et pour les algorithmes de Transceiver de CR démontre que les MPSoC à usage général sont une réponse pertinente, entre autres, aux contraintes de performances sur une telle plate forme. Le système que nous proposons apporte une réponse aux défis technico-économiques des grandes entreprises qui investissent ou prévoient d'investir dans des équipements basés sur des SDR ou des CR, puisqu'il permet d'éviter de recourir à des équipements d'accélération coûteux.

Nous avons, par la suite, ajouté d'autres fonctionnalités à notre waveform avec un « CR Transceiver multinormes », en proposant une nouvelle approche pour la gestion du spectre radio. Ceci étant l'aspect le plus important de CR. Nous rendons ainsi notre waveform spectralement efficace en modélisant les caractéristiques radiofréquences (RF) du signal utilisateur primaire sous la forme d'une série temporelle multi-variées. Cette série temporelle est ensuite fournie comme entrée dans un Réseau de Neurones Récurrent d'Elman (ERNN) qui prédit l'évolution de la série temporelle de RF pour déterminer si l'utilisateur secondaire peut exploiter la bande de fréquences. Nous avons exploité la cyclo-stationnarité inhérente des signaux primaires pour la Modélisation Non-Linéaire Autorégressive Exogène (NARX : Non-linear AutoRegressive Exogenous) des séries temporelles des caractéristiques RF, car la prédiction d'une caractéristique RF demande d'abord de connaître les autres caractéristiques radios pertinentes. Nous avons observé une tendance similaire pour les valeurs prédites et observées.

En résumé, nous avons proposé des algorithmes pour SDR waveform à efficacité spectrale avec un Transceiver Universel, ainsi que leurs implantations parallèles sur MPSoC. Notre conception de waveform répond aux exigences en performances et aux contraintes de ressources embarquées des applications dans le domaine.

# **Table of contents**

| List of Figures | . 14 |

|-----------------|------|

| List of Tables  | . 17 |

| Cha | Chapter 1: Motivation and Context    |      |  |

|-----|--------------------------------------|------|--|

| 1.  | Introduction:                        | . 19 |  |

| 2.  | First Contribution [183, 184, 185]:  | . 20 |  |

| 3.  | Second Contribution [186, 187]:      | . 21 |  |

| 4.  | Third Contribution [188, 189]:       | . 23 |  |

| 5.  | Conclusions and Thesis Organization: | . 24 |  |

| <u>Ch</u> | apter | <u>2</u> : Se | oftware Defined Radio- State of the art          | 26 |

|-----------|-------|---------------|--------------------------------------------------|----|

| 1.        | Soft  | ware          | Defined Radio-Definition:                        | 26 |

| 1         | .1    | Feat          | tures of SDR:                                    | 30 |

|           | 1.1.1 | 1.            | Portability:                                     | 31 |

|           | 1.1.2 | 2.            | Reconfigurability:                               | 31 |

|           | 1.1.3 | 3.            | Seamless Mobility:                               | 31 |

|           | 1.1.4 | 4.            | Interoperability:                                | 32 |

| 2.        | Issu  | es in         | SDR:                                             | 32 |

| 2         | .1    | App           | lication Engineering:                            | 33 |

| 2         | 2     | Con           | nputational Capacity:                            | 33 |

| 2         | .3    | Ana           | log to Digital and Digital to Analog Conversion: | 34 |

| 2         | .4    | Soft          | ware Download:                                   | 35 |

| 2         | .5    | Proc          | cessing Elements Choice:                         | 35 |

| 2         | .6    | Stan          | dardization and Certification:                   | 36 |

| 2         | .7    | Sma           | rt Antenna Design:                               | 37 |

| 3.        | SDF   | R Arc         | hitecture:                                       | 37 |

| 4.        | Soft  | ware          | Communication Architecture:                      | 40 |

| 5.        | Aca   | demi          | c SDR Reference Implementations:                 | 43 |

| 5         | .1    | SCA           | ARI [18]:                                        | 43 |

| 5         | .2    | OSS           | SIE [7]:                                         | 45 |

|           | 5.2.  | 1.            | Waveform Workshop – Tools of OSSIE [8]:          | 46 |

| 6.        | Con   | nmero         | cial SDR [19]:                                   | 46 |

| 6         | 5.1   | SDF           | R-4000 [19]:                                     | 47 |

| 7. | Conclusion: | 49 |

|----|-------------|----|

|----|-------------|----|

| Chapte  | e <u>r 3</u> : Cognitive Radio - State of the art: | 51 |

|---------|----------------------------------------------------|----|

| 1. Intr | troduction:                                        | 51 |

| 1.1     | Definition:                                        | 54 |

| 2. The  | eoretical Research Issues:                         | 55 |

| 2.1     | Sensing:                                           | 56 |

| 2.2     | Decision making process:                           | 56 |

| 2.3     | Learning Process:                                  | 57 |

| 2.4     | Architecture Implementation:                       | 57 |

| 2.5     | Equipment Test Procedures and Certifications:      | 58 |

| 2.6     | Interaction with all Layers of Protocol Stack:     | 58 |

| 2.7     | RF Design:                                         | 58 |

| 2.8     | SoC Implementation:                                | 59 |

| 2.9     | Accurate and Secure Primary User Detection:        | 59 |

| 2.10    | Interoperability:                                  | 60 |

| 2.11    | Security:                                          | 60 |

| 3. Co   | gnitive Radio Architecture:                        | 61 |

| 4. Ma   | achine Learning:                                   | 63 |

| 4.1     | Memorization:                                      | 64 |

| 4.2     | Swarm Intelligence:                                | 64 |

| 4.3     | Genetic Algorithms:                                | 65 |

| 4.4     | Fuzzy Logic:                                       | 66 |

| 4.5     | Other Methods:                                     | 67 |

| 4.6     | Artificial Neural Networks:                        | 68 |

| 5. Ma   | ajor Cognitive Radio Projects and Achievements:    | 70 |

| 5.1     | IDROMeL [37]:                                      | 70 |

| 5.2     | GRACE[38]:                                         |    |

| 5.3     | End to End Reconfigurability (E2R) [39]:           |    |

| 6. Co   | onclusions:                                        | 73 |

| <u>Ch</u> | Chapter 4: Embedded System Implementation and Optimization of SDR |    |  |

|-----------|-------------------------------------------------------------------|----|--|

| 1.        | Introduction:                                                     | 75 |  |

| 2.        | SDR Embedded Implementation Efforts:                              | 76 |  |

| 3.        | MPSoC and FPGA Technology:                                        | 78 |  |

| 4. Th   | ne Multiprocessor Platform:                                      |  |

|---------|------------------------------------------------------------------|--|

| 4.1     | External Constraints:                                            |  |

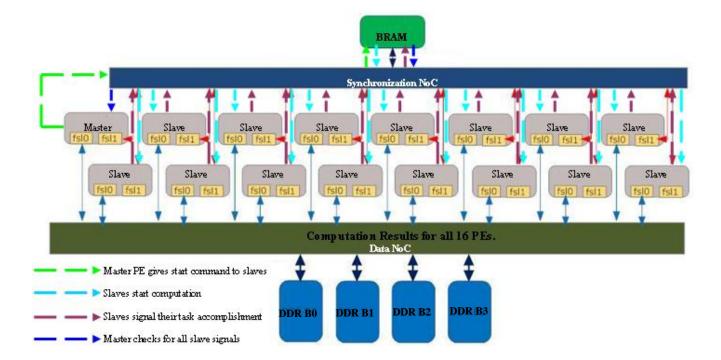

| 4.2     | MPSoC Architecture:                                              |  |

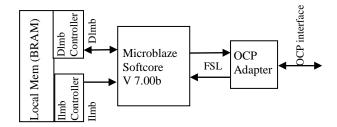

| 4.3     | Processing Element:                                              |  |

| 4.4     | OCN:                                                             |  |

| 5. 05   | SSIE Core Framework:                                             |  |

| 5.1     | OSSIE Signal Processing Library:                                 |  |

| 6. Pe   | rformance Evaluation of OSSIE SigProc on Embedded Platform       |  |

| ML-40   | 3 Board:                                                         |  |

| 6.1     | Microblaze cache:                                                |  |

| 7. 05   | SSIE Signal Processing Function Performance Enhancements         |  |

| through | Parallelization:                                                 |  |

| 7.1     | The Parallelization Primitives:                                  |  |

| 7.2     | Parallelization Description:                                     |  |

| 8. Ac   | lditional Functionality in SDR waveform:                         |  |

| 8.1     | FFT Parallelization Strategy:                                    |  |

| 8.2     | Viterbi Decoding Parallelization Strategy:                       |  |

| 9. Ex   | perimental Results for FFT and Viterbi decoding Parallelization: |  |

| 10.     | Other Functions to be realized:                                  |  |

| 11.     | Conclusions:                                                     |  |

####

| 1. | Intro | Dduction: 1                                                                   | .07 |

|----|-------|-------------------------------------------------------------------------------|-----|

| 2. | Neu   | ral Networks Review:                                                          | .09 |

| 2  | .1    | Structure and Architecture of Artificial Neural Networks: LVQ, SOM and MLP: 1 | 11  |

| 3. | Rela  | nted Work:1                                                                   | 12  |

| 4. | Our   | proposed Approach: 1                                                          | 13  |

| 4  | .1    | SOM, LVQ and MLP for CR Standard Identification: 1                            | 14  |

| 4  | .2    | SOM and LVQ Implementation:                                                   | 17  |

| 4  | .3    | MLP Implementation:                                                           | 21  |

| 4  | .4    | Standard Recognition Experimentation Results: 1                               | 23  |

| 5. | Para  | Illelization and Implementation Strategy:1                                    | 28  |

| 5  | .1    | SOM and LVQ Parallel Implementation: 1                                        | 28  |

| 5  | .2    | MLP Parallel implementation:                                                  | 30  |

| 6. | Spee  | ed up Results:                                                                | 31  |

| 7. Conclusions: |

|-----------------|

|-----------------|

#### Chapter 6: Cognitive Radio Spectrum Evolution Prediction using Artificial Neural Networks 1. 2. 2.1 2.2 Energy Detection: 139 2.3 2.4 3. 4. 5. ERNN Implementation: 146 6. 7. 8.

| Chapter 7: Final Word and Perspectives |

|----------------------------------------|

|----------------------------------------|

| Publications | 159 |

|--------------|-----|

| References   | 160 |

# **List of Figures**

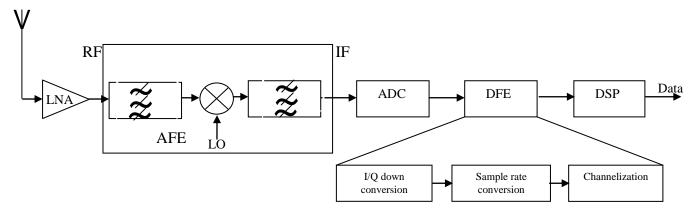

| Fig. 1. The practical SDR Block Diagram at receiver side                                                                                                    | 28   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

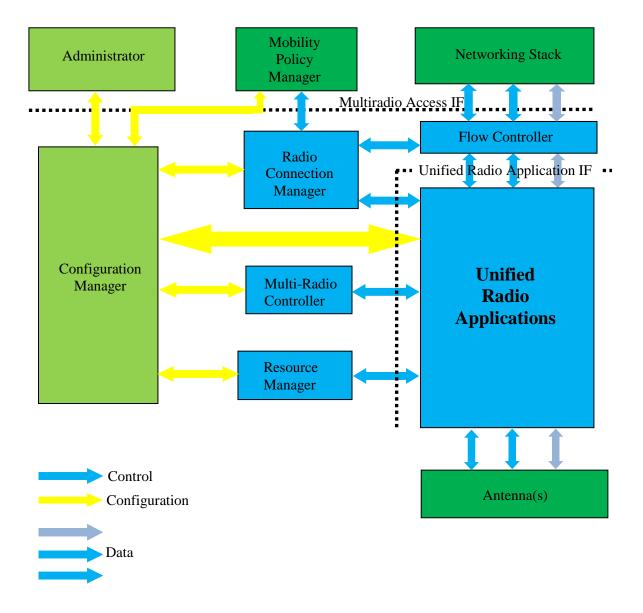

| Fig. 2. Functional Architecture of ETSI's [15] SDR Radio Computer                                                                                           | 39   |

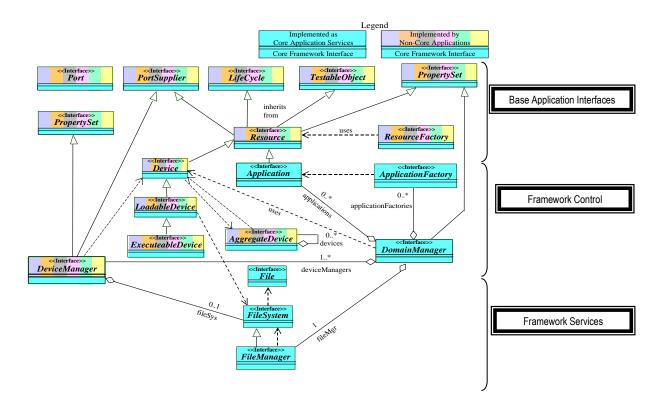

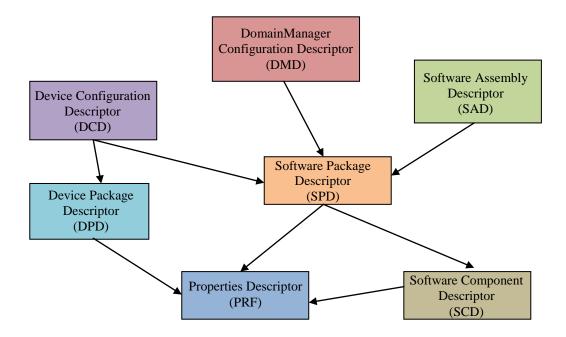

| Fig. 3. Classes making up Software Communication Architecture( page 97 of Book at [181])                                                                    | 42   |

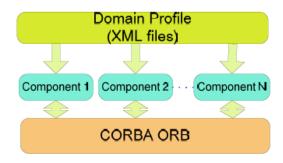

| Fig. 4. The Domain Profile –XML Files                                                                                                                       | 42   |

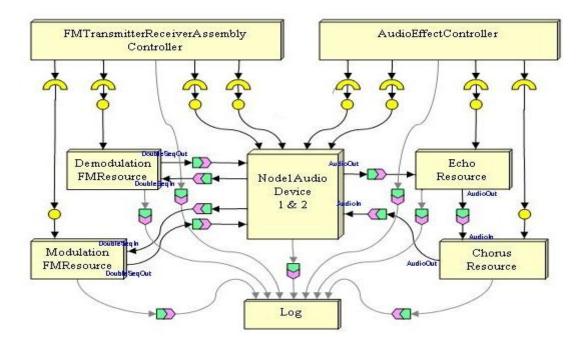

| Fig. 5. SCARI example waveform.(taken from [18])                                                                                                            | 44   |

| Fig. 6. OSSIE Block Diagram                                                                                                                                 | 45   |

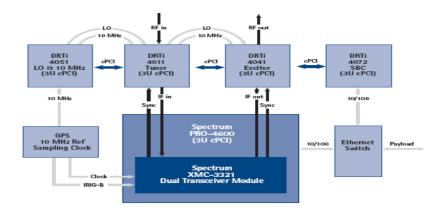

| Fig. 7. SDR-400 Block Diagram. (taken from[19])                                                                                                             | 49   |

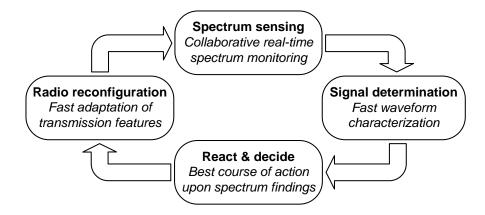

| Fig. 8. Cognition Cycle [23]                                                                                                                                | 53   |

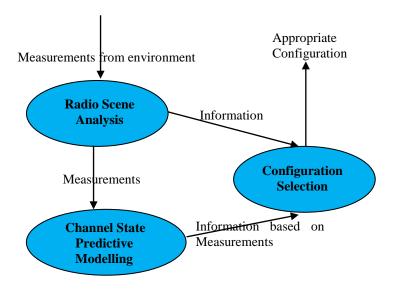

| Fig. 9. Reconfigurable Cognitive Radio Cycle.                                                                                                               | 55   |

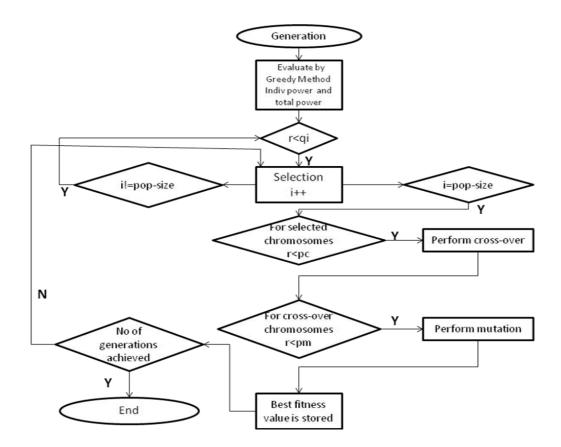

| Fig. 10. Genetic Algorithm Structure.                                                                                                                       | 66   |

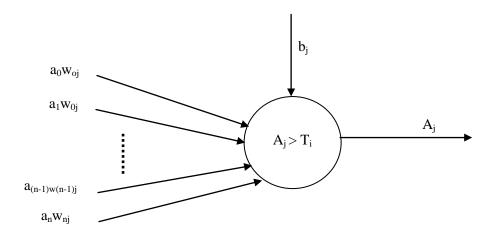

| Fig. 11. Neural Network node illustration. Shown are the input vector A (with elements a0 weight matrix W (with elements w0jwnj); bias value, b; and output |      |

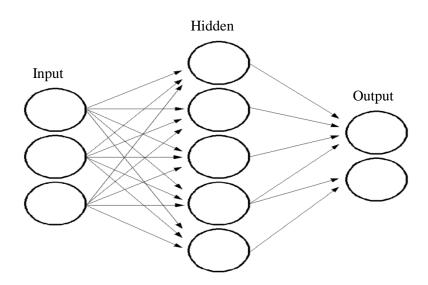

| Fig. 12. Artificial Neural Network                                                                                                                          | 69   |

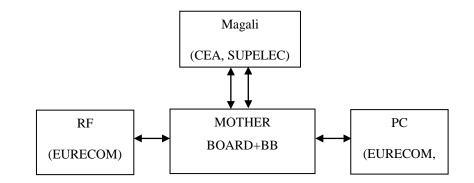

| Fig. 13. Hardware Architecture of IDROMeL [37]                                                                                                              | 71   |

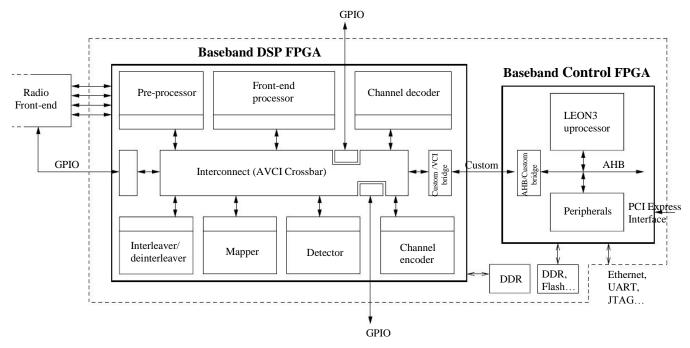

| Fig. 14. Baseband Processor Architecture of IDROMeL (taken from [37])                                                                                       | 71   |

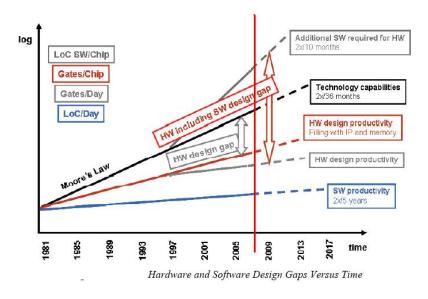

| Fig. 15. ITRS Roadmap                                                                                                                                       | 78   |

| Fig. 16. FPGA board                                                                                                                                         | 80   |

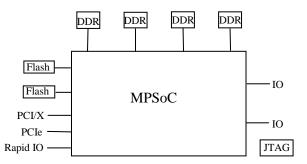

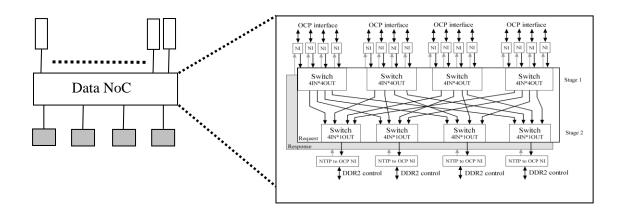

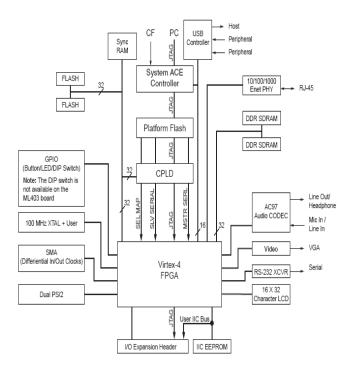

| Fig. 17. MPSoC Target External Connections [61]                                                                                                             | 80   |

| Fig. 18. Block Diagram of designed MPSoC Architecture [61]                                                                                                  | 81   |

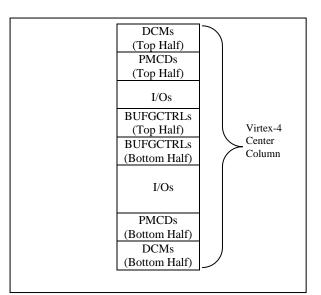

| Fig. 19. Virtex-4 Internal Architecture                                                                                                                     | 81   |

| Fig. 20. Microblaze based Processing Element [61]                                                                                                           | 82   |

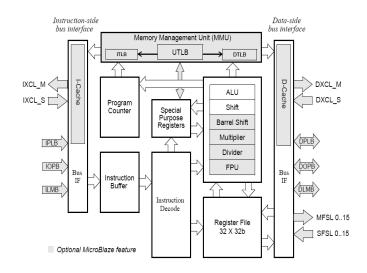

| Fig. 21. Microblaze Core Block Diagram                                                                                                                      | 83   |

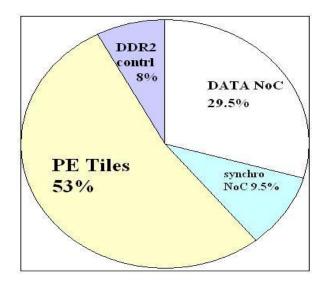

| Fig. 22. Resource use in percentage.[61]                                                                                                                    | 84   |

| Fig. 23. Block Diagram of ML403                                                                                                                             | 88   |

| Fig. 24. Detailed Description of Virtex-4 ML403 Evaluation Platform Components (Front View                                                                  | ) 88 |

| Fig. 25. Detailed Description of Virtex-4 ML403 Evaluation Platform Components (Back View                                                                   | ) 88 |

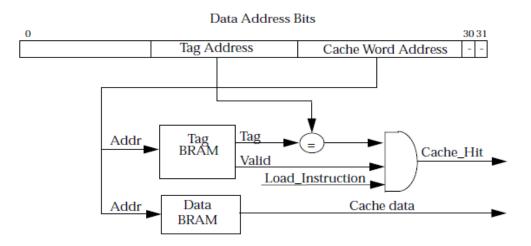

| Fig. 26. Data Cache Organization for Microblaze                                                                                                             | 90   |

| Fig. 27. Block Diagram for Random Data Transceiver                                                                                                          | 92   |

| Fig. 28. Parallelization Strategy for OSSIE Filter Functions                                                                                                | 93   |

| Fig. 29. CalculateRRCFilterCoefficients Parallelized Algorithm Design                                                                                       | 95   |

| Fig. 30. DesignRRCFilter Parallelized Algorithm Design                                                                                                      | 96   |

| Fig. 31. CalculateDerivativeFilterCoefficients Parallelized Algorithm Design                                                                                | 97   |

| Fig. 32. Phase 1 of FFT Algorithm: Iterative Computation for each PE without communication.                                                                 | 99   |

| Fig. 33. Phase 2 of FFT algorithm: Communication between pairs of processors                              | 100 |

|-----------------------------------------------------------------------------------------------------------|-----|

| Fig. 34. Processing done by each PE for Viterbi Decoding Algorithm                                        | 101 |

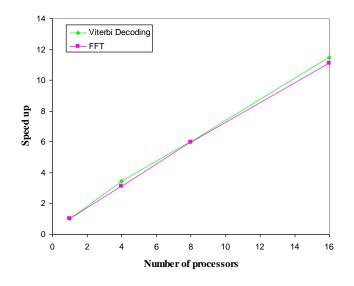

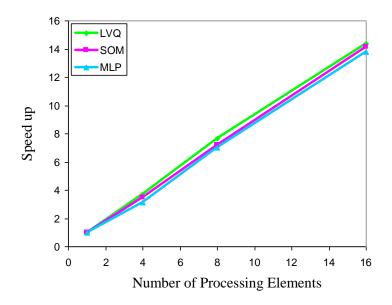

| Fig. 35. Speed-up versus PEs for FFT and Viterbi Decoding                                                 | 103 |

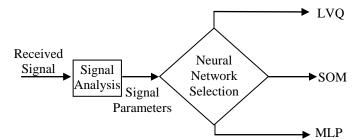

| Fig. 36. Neural Networks Selection based on received signal extracted parameters                          | 114 |

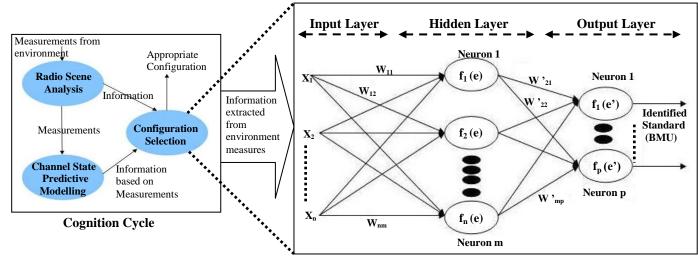

| Fig. 37. SOM and LVQ and MLP based Cognition Cycle Receiver                                               | 117 |

| Fig. 38. SOM Algorithm for BMU (Standard) determination and weight update                                 | 118 |

| Fig. 39. Iterative MLP Algorithm for Standard and transmission power determination and update.            | •   |

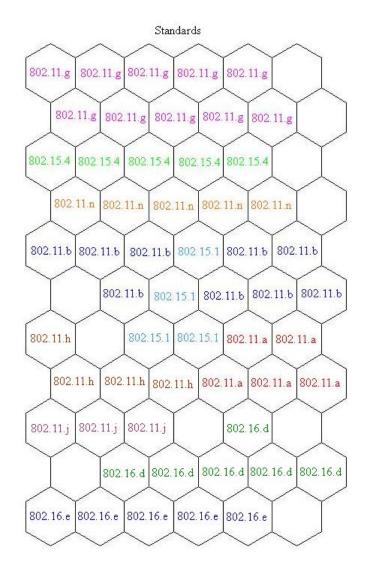

| Fig. 40. Output grid showing different standards forming a cluster                                        | 124 |

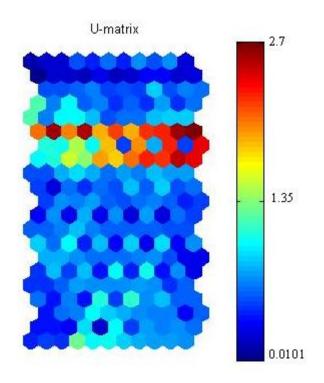

| Fig. 41. U-matrix for normalized parameters for all Standards                                             | 125 |

| Fig. 42. U-matrix row showing equal distance between three map units of a cluster comp 802.11.g Standard. | •   |

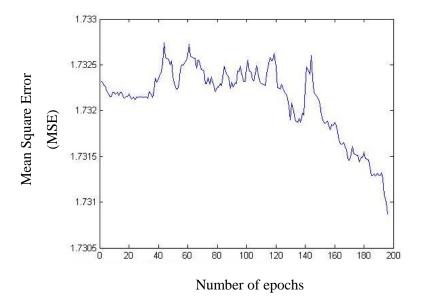

| Fig. 43. MSE after 200 training epochs                                                                    | 126 |

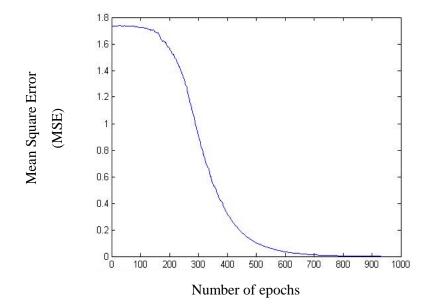

| Fig. 44. MSE after 700 training epochs                                                                    | 126 |

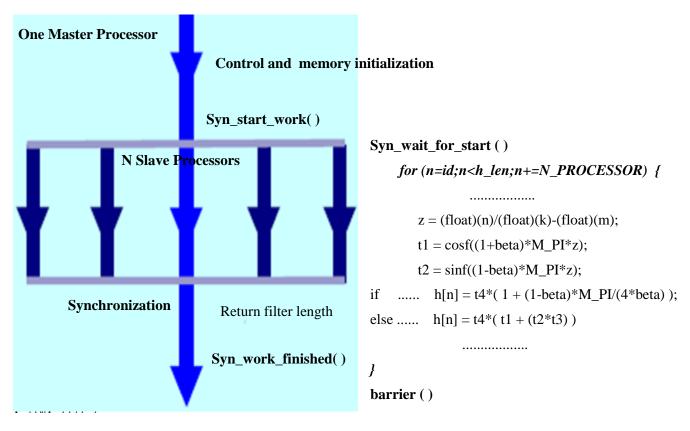

| Fig. 45. LVQ and SOM parallelized Algorithm                                                               | 129 |

| Fig. 46. MLP Parallelized Algorithm                                                                       | 130 |

| Fig. 47. Parallelization illustration with the primitives.                                                | 131 |

| Fig. 48. Speed-up obtained for all three Neural Networks based cognition algorithms                       | 133 |

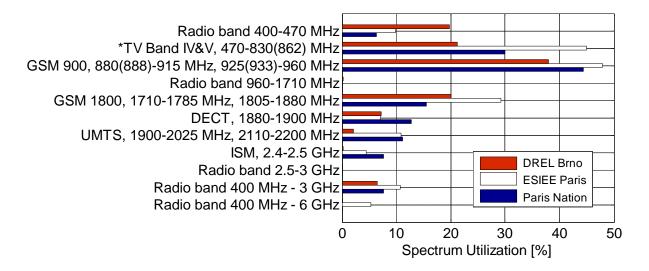

| Fig. 49. Recent Spectrum Utilization in Percentage in Europe (taken from [136])                           | 136 |

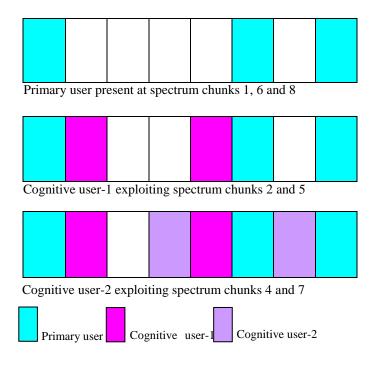

| Fig. 50. Opportunistic Spectrum access by cognitive users.                                                | 137 |

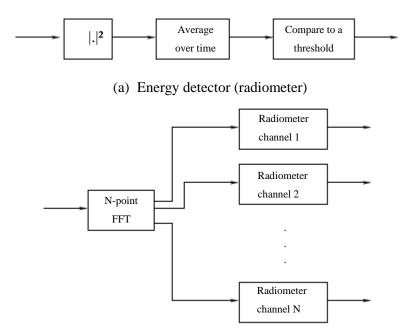

| Fig. 51. Block diagram of (a) the basic energy detector and (b) an energy detector in fadomain.           | · · |

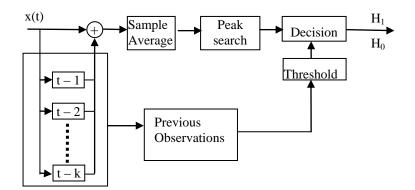

| Fig. 52. Block Diagram of Spectrum Sensing predicate decision.                                            | 145 |

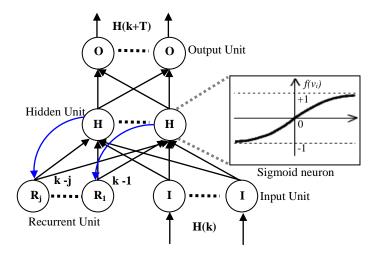

| Fig. 53. Elman Recurrent Neural Network                                                                   | 147 |

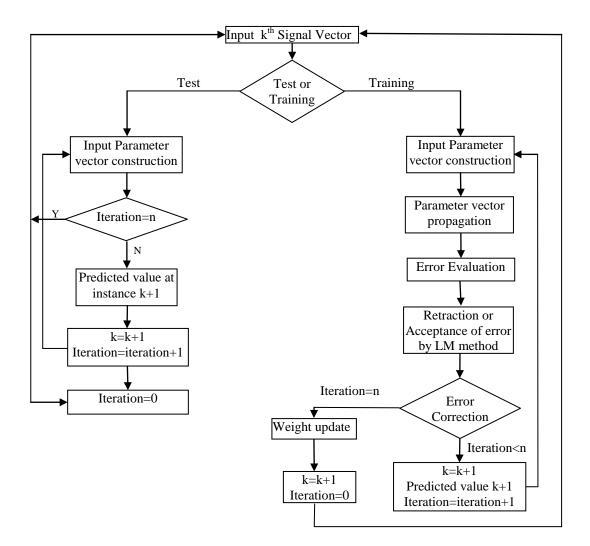

| Fig. 54. Our designed ERNN and LM based Algorithm for Spectrum prediction in form of tin                  |     |

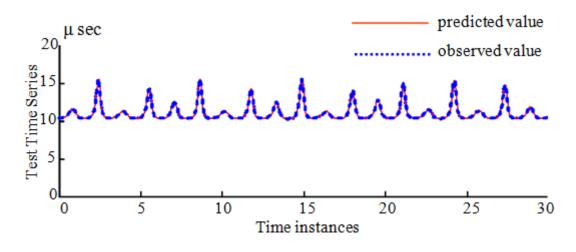

| Fig. 55. Observed and Predicted values of time series over testing samples                                | 152 |

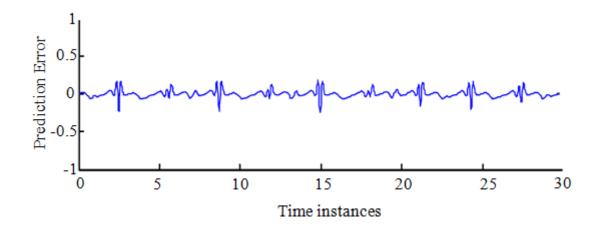

| Fig. 56. Prediction error between predicted and observed time series.                                     | 152 |

# **List of Tables**

| Tab. 1. Radio Computer Framework Components and their functionalities    40            |

|----------------------------------------------------------------------------------------|

| Tab. 2. Important Functions of SigProc namespace    87                                 |

| Tab. 3. Worst case execution time of SigProc Functions    89                           |

| Tab. 4. Filter Functions Performance Comparison for different Cache sizes.       91    |

| Tab. 5. Our Proposed Cache Size for each Filter Function    91                         |

| Tab. 6. Component Processor usage                                                      |

| Tab. 7. Speed up of OSSIE Filter Functions using Multi-processor platform       97     |

| Tab. 8. FFT Speed up for different number of PEs.    102                               |

| Tab. 9. Viterbi decoding Speed up for different number of PEs.    102                  |

| Tab. 10. Standards identified by respective Neural Network Techniques.       115       |

| Tab. 11. Parameters of Standards recognized using LVQ                                  |

| Tab. 12. Parameters of Standards recognised using SOM    116                           |

| Tab. 13. Parameters of Standard recognized using MLP    116                            |

| Tab. 14. Comparison with other NN based CR proposals                                   |

| Tab. 15. Speed-up of ANN Cognitive Algorithms using Multiprocessor platform.       132 |

| Tab. 16. Spectrum Sensing methods and their limitations.    140                        |

| Tab. 17. Algorithm Parameters.    150                                                  |

## **Chapter 1:**

## **Motivation and Context.**

#### 1. Introduction:

Future mobile networks offer new opportunities to access information in an anytime, anywhere paradigm. Next wireless terminals will have to integrate an increasing number of functionalities to allow an increased interactivity with the surrounding environment itself enhanced with the paradigm of "Ambient Intelligence". In this respect, the trends taken by mobile communications towards Software Defined Radio (SDR), Reconfigurable Terminals and Cognitive Radio(CR) create not only new opportunities but also new constraints, in already constraint environment, in terms of platforms optimization answering requirements (criteria) of performance, energy consumption and chip area. The emergence of the concept of Software Defined Radio and Cognitive Radio is very attractive for future mobile communications since it naturally matches reconfigurability of wireless and multimodes of operations. This has a direct influence on the design of new solutions oriented towards FPGA based reconfigurable platforms.

Software Defined Radio and Cognitive Radio Technologies are entering mainstream. This can be witnessed by observing a huge recent interest in Software Radio related wireless communications and different proposals to incorporate cognition in the software radio. A massive amount of literature has been published on the topic. The academia and industry both are eager to contribute to the research policy and regulation issues. Despite being introduced for the first time in 1991 by J.Mitola, this topic still happens to be very fresh and fascinating research interest as there are many technical questions still need to be answered, e.g. how to address the required high performance and high adaptability with respect to ITRS Roadmap Prediction? How to address the real time constraint mode switching from one radio configuration to another? How to configure the Cognitive Radio Transceiver? How to perform Spectrum Sensing based on previous learning experiences?

This thesis answers all these technical challenges and questions associated with this SDR and CR concept. We contribute towards the development of this technology in three fold way:

1. Efficient implementation of SDR based algorithms, comprising a complete SDR waveform, on embedded Network on chip based multiprocessor system on chip, together with appropriate middleware evaluation.

2. Cognition incorporation in our designed Software Defined Radio waveform by Artificial Neural Networks based Multi-standard CR Transceiver design so as to enhance its functionality. This resulted in an Universal Transceiver capable of operating in different Standards.

3. Incorporating radio resource (spectrum) efficiency by predicting the future occupancy status based on previous learnt experiences, using Artificial Neural Networks. This resulted in efficient cognitive user decision to exploit the available spectrum opportunity, thereby optimizing the most valuable resource (Spectrum) usage.

We explain all these points hereafter:

### 2. First Contribution [183, 184, 185]:

Due to the relatively complexity of applications related to software radio and if one wishes to exploit at best the dynamic behavior of those applications in order to optimize their implementations, it is necessary to rely on a rigorous and complete system level design methodology. Multiprocessor System on chip (MPSoC) are prime candidates for the implementation of next generation wireless systems due to their strong computational potential. Although front end analog part issues are essential and are being currently tackled, numerous issues in the digital part are emerging. In particular MPSoC requires efficient QoS based inter-processor interconnections which are implemented with Network on chip (NoC) at our targeted platform. These NoC adapt to workload variations in the operating wireless environments and make the utmost use of available resources. We explore the potentials of reconfigurable NoC technologies through eFPGA for SDR and CR. Hence the first objective of this thesis is to propose new design methodologies and new architectures for Network on chip based multiprocessor SoC which are efficient with regard to the above mentioned criteria for SDR. We started our work by the performance evaluation of the only open source C based SDR Open Source SCA Implementation:: Embedded (OSSIE) developed at Virginia Tech University in the USA. OSSIE implements the radio-communication algorithms under the name space of SigProc (Signal processing Library).We used Xilinx ML-403 platform based on Virtex-4 FPGA and the softcore Microblaze processor for identifying the functions that need to be optimized. We ported the following four classes of algorithms that were part of SigProc namespace:

- 1. Filter Functions.

- 2. Algebraic Functions.

- 3. Modulation Functions.

- 4. Demodulation Functions.

These four classes of algorithms constitute a basic SDR waveform and so by porting all these algorithms on Microblaze softcore processor, we evaluated the performance of SDR waveform components on embedded platform to meet good area performance tradeoffs. As a result of this mapping, the filter functions were identified to be strong candidates for optimization. We proposed the appropriate cache size for each filter function in question. We further went a step ahead by parallelizing these filter functions to address the prediction of International Technology Roadmap for Semiconductors (ITRS) that out to 2017, software design productivity will fall behind hardware design productivity. This prediction has a direct impact on SDR and CR based platforms as major investments has been made to impart intelligent software defined behavior in these agile frequency based operational devices. To address this ITRS prediction with respect to SDR, we ported the identified optimization requiring filter functions onto a sixteen processing element (PE) Network on chip based multi-core single chip platform, that is developed on a Xilinx FPGA Virtex-4 FX based chip. Each processing element happens to be the same Microblaze softcore processor that we chose for ML-403 board. Then we proceeded to include further components in the waveform to change its basic nature into more advanced form by parallelizing the following two functions on the same 16 PE platform:

#### 1. FFT.

#### 2. Viterbi Decoding.

An advanced parallelization strategy was followed for these two waveform components this time. This is because of the inherent intercommunication nature of these two algorithms. Because of this very reason, the speed-up obtained was not linear this time, unlike our filter functions. We proposed enhancement methodologies to exploit our multiprocessor platform leading to further optimized results. So in our first contribution, we have ported and proposed to enhance all the components of a SDR waveform on our NoC based multiprocessor SoC architecture compised of 16 PE, each element being Microblaze.

At the same time, we evaluated the five aspects of omniORB Object Request Broker, namely, Invovation Time, In Sequence, Out Sequence, Objects Registered and Multi-threading over a high speed network of multicore workstations. This contribution resulted in an efficient SDR waveform design on MPSoC to address efficiently, the high performance and high adaptability requirements of SDR.

#### 3. Second Contribution [186, 187]:

We target our efforts toward a Multi-standard Cognitive Radio Transceiver design for our Software Defined Radio waveform. CR systems are based on SDR technology and utilize intelligent software packages that enrich their transceivers with the ability to adjust their operating parameters, observe the results and eventually take actions, that is to say, decide to operate in a specific radio configuration, expecting to move the radio towards some optimized operational state. So, the aim of a CR is to self adapt to changing requirements from user's applications in order to provide QoS and self-management capability. Multimode reconfigurable devices that are able to adapt their behaviour to the environment, configuring themselves in an appropriate fashion are increasingly being adapted within the wireless industry. In this respect, future cognitive radio devices will have the capability to adjust their operating parameters to optimize the radio state after sensing the environment variables and estimating the channel state. This is visualized in cognition cycle. In this respect, we target our efforts in designing efficient algorithms that can address the multimode reconfigurable device requirements. We proposed Unsupervised Neural Networks, Self Organizing Maps (SOM) and Linear Vector Quantization (LVQ) and Supervised Neural Network, Multilayer Perceptron (MLP) to incorporate learning lessons from previous experiences, thereby recognizing a Standard amongst a predefined list of Standards, and in the case of huge data range, the estimated transmission power required, as well. We evaluated the feasibility of SOM, LVQ and MLP algorithms to address our cognitive needs in SDR and we obtained encouraging results and each standard in question was recognized by our proposed Neural Networks based cognition algorithms for CR, thereby enabling the radio to move in the recognized standard mode, and in the case of huge data range, estimating the transmission power required. This leads to optimize radio resource use (spectrum, battery, carrier frequency). The cognitive functionality is spread across the layers of communication architecture, resulting in coordination amongst the layers for an efficient use of available resources. The characteristics, to be identified, to switch the CR Transceiver in the desired Standard mode, pertain to different layers of a communication system, thus we optimize the cognitive transceiver across different layers. We propose to perform the Standard detection by the identification of parameters specific to a particular standard and these parameters pertain to different layers of communication architecture, thus we target at cross-layer optimization of the CR system. After evaluating SOM, LVQ and MLP for cognition incorporation in our radio waveform, we come up with an efficient parallelization strategy for implementation of SOM, LVQ and MLP and then implemented our algorithms using our designed strategy on our target 16 PE NoC based multi-core MPSoC chip, to again address the ITRS Roadmap Prediction. Putting all the discussion of our second contribution, together, in this part we contributed by:

1. SOM, LVQ and MLP algorithms design to enhance our waveform's functionality.

2. Parallelized Implementation of SOM, LVQ and MLP on NoC based multicore, single chip Xilinx Virtex-4 FPGA.

This resulted in an efficient Cognitive Radio Transceiver design that recognized the standard based on parameters received as input to the Neural Network, moving the radio in the recognized standard mode

to make adequate decisions, thereby enhancing the waveform functionality addressed in the first contribution.

### 4. Third Contribution [188, 189]:

Our third contribution targets at making our radio waveform resource efficient. The most important radio resource in today's spectrum constraint environment is Spectrum. WLAN 2.4 and 5 GHz bands are overpopulated as their capacity is small enough for a very high number of interested parties. Paradoxically, with a keen observation at any recent spectrum utilization measurement we will witness a gigantic asymmetry in spectrum usage. That is, even if the popular spectrum bands, like WLAN are highly overcrowded in many geographical areas, majority of spectrum bands, assigned to different systems are practically silent. They are not exploited at the fullest. This Underutilization is notably visible in the licensed bands. This is where the waveform spectrum efficiency comes into play, to overcome this paradox of spectrum allocation. In this contribution, we address this very spectrum scarcity issue, as only a small portion of the allocated spectrum is used everywhere and at all times. We propose an efficient methodology to alleviate this inefficient use of the spectrum. We exploit the cyclostationary feature detection to propose an efficient spectrum management algorithm using Elman Recurrent Neural Network (ERNN). We model the licensed signal Radio Frequency (RF) features as a NARX time series, which is then given as input to ERNN. The interdependence between different variables (RF features of primary user in our case) makes it more difficult to predict the time series with multiple variables. Therefore, majority of the modelling and predicting methods focus on the time series with a single variable. At the same time, single variable time series are known not to contain enough information to predict accurately the future instances. The prediction results are more reliable and accurate when there is adequate available information. Non-linear multivariate time series prediction is based on ample available information. Our motivation to choose NARX model of multivariate time series for Spectrum Evolution prediction comes from the fact that this time series model is known to have more information than its counterpart univariate time series models. It is because of this very reason that it is better to predict the primary user presence or absence using multivariate time series. With the ability to accurately predict any universal non-linear function, ERNN is a far better choice for non-linear modelling and prediction, than other available tools, such as ARMA, ARIMA and Markov Models. Thus, the requirement of avoiding interference to potential primary users in their vicinity is addressed in this contribution, using all this background. We have used the Non-linear Autoregressive Exogenous Time Series Model using ERNN to perform single step ahead prediction using second order cyclostationarity. We predict the presence of primary user based on the previous observations, which are modelled as RF time series.

This resulted in a similar trend between predicted and observed values of primary user Spectrum usage, thereby enabling CR to exploit expected available spectrum opportunities, in near future. This

contribution added Spectrum efficient utilization, in the designed waveform of first and second contribution.

#### 5. Conclusions and Thesis Organization:

In this thesis, we address and propose solutions to the most important issues related to SDR and CR Technology that are thought to be the big bang of today's wireless communication industry. This Chapter described our motivation to pursue this challenging subject and introduced the important notions, together with summarizing our contributions towards the subject.

This doctoral thesis is divided into six more Chapters (Chapter 2 to Chapter 7). The rest of the thesis is organized as follows: Chapter 2 describes in detail the SDR concept and the motivation that leads towards this solution. We define the definitions and terminologies with which we stick throughout the thesis, notably the definition of SDR as defined by Wireless Innovation Forum. The Chapter introduces the functionality of an ideal SDR and the key features: Portability, Reconfigurability, Seamless Mobility and Interoperability, that it should possess. We follow this up with the explanation of the practical version of Software Radio, called Software Defined Radio as it is not possible yet to sample directly from antenna. The key research issues that need to be addressed to make this technology viable together with the architecture evolution are reviewed. The first ever SDR project, in recent times, leading to Software Communication Architecture (SCA) definition is described, together with the Core Framework concept. Finally, we describe two academic SDR examples: SCARI and OSSIE, and one commercial product example: SDR-4000 that successfully employs this technology.

Chapter 3 proceeds to the concept of Cognitive Radio (CR) with its fundamental entities, benefits and implications. We stick with the Wireless Innovation Forum's definition of CR throughout this thesis, so we define this very definition in this chapter. Theoretical research issues that need to realize this technology are divided into five groups and are reviewed in this Chapter. We give an overview of CR architecture evolution in terms of RF front-end design and implementation issues. Different machine learning techniques used for CR engineering are reviewed with a special emphasis on Artificial Neural Networks (ANN). We conclude this Chapter by having an overlook of important European research projects addressing the CR engineering.

In Chapter 4, we describe our designed SDR waveform in detail. We begin with the important SDR Embedded Implementation efforts, then we describe in detail our target MPSoC platform and the Processing Element (PE) used. The OSSIE Signal Processing Library is studied in detail in this Chapter and cache size optimization for the considered Processing Element is addressed. We start by the OSSIE Signal Processing Functions (Filter, Algebraic, Modulation and Demodulation) embedded implementation to identify the Filter functions as parallelization requiring functions. We describe the

parallelization strategy to enhance the OSSIE *SigProc* functions (DesignRRCFilter, CalculateRRCFilterCoefficients and CalculateDerivativeFilterCoefficients) through parallelization on our target MPSoC. We conclude the Chapter 4 by describing the two additional functions (FFT and Viterbi Decoding) parallelization strategy to port them on the same MPSoC. The Speed-up, of all the parallelized functions that constitute a SDR waveform, is analyzed in detail to conclude the suitability of the General purpose MPSoC based solution for SDR.

Chapter 5 describes the Universal Multi-standard CR Transceiver Design for our designed waveform explained in Chapter 4. We describe the architecture of the three Artificial Neural Networks: LVQ, SOM and MLP and then exploit them for the Standard recognition among a predefined list of Standards. We describe in detail our proposed Neural Networks algorithms for Universal Multi-standard Transceiver Design and compare them with the other proposals. Our efforts to design a Multi-standard ANN based CR Transceiver answers the question of rapidly evolving new Telecommunication Standards with each day, thereby forcing us to rethink about the current transceiver architecture. In the last part of this Chapter, we design an efficient parallelization strategy to implement the three proposed Transceiver Algorithms: LVQ, SOM and MLP, on our target MPSoC and finally we conclude the Chapter with Speed-up Evaluation.

Chapter 6 incorporates Radio Resource: Spectrum, efficiency by predicting Spectrum Evolution occupation in time. We begin this Chapter by recent spectrum utilization review in Europe. We give an overview of the existing Spectrum sensing methods, with an emphasis on Cyclostationary feature detection. We follow this up with Non-linear Autoregressive Exogenous Multivariate time series modeling using Neural Networks (Elman Recurrent Neural Network) and representation of the received signal using time series analysis. We explain our ERNN design and Levenberg-Marquardt Learning Algorithm used to predict the spectrum evolution in time. We conclude this Chapter by analyzing the experimental results.

The last Chapter (Chapter 7) summarizes and concludes major achievements of this doctoral thesis. We stress the importance of lateral thinking to gain a greater cross domain interaction as we have done in this thesis. We also present multiple possible future research directions and open problems that still need to be addressed. Towards the end of thesis, we list the publications that we have done and finally, we give the bibliography.

## **Chapter 2:**

### Software Defined Radio- State of the art.

#### **1.** Software Defined Radio-Definition:

We are living in a rapid pace of communication technology, which makes the communication devices out-dated soon after their engineering. To go with this pace, communication systems require transparent insertion of the latest technological communication devices. With the insertion of latest technology in the communication devices, the upgraded modern device should be able to communicate with legacy devices as well. The Software Radio Technology allows one to add new functionality without hardware changes, even during a technological update. The ideal Software Radio, as defined by Wireless Innovation Forum [1] refers to the complete software control of the entire system. This means that analogue conversion should take place only at antenna, ensuring the support for a wide frequency range. These kinds of software radios will be obviously future proof as the whole radio system will be dependent on programmability, leading to the same hardware behaving differently at different instances. Furthermore, in the paradigm of Ambient Intelligence, these days even a simple workstation has the possibility of integrating a 2G/3G card. This trend is further evolving to 4G with higher QoS by means of improved channel equalization techniques, smarter antennas engineering and ever enhancing protection coding methods. The different types of applications and usages demand different standards in wireless communication systems. Although all these systems have almost similar components, the ways these components behave differ greatly from standard to standard. Also, while migrating from one generation to next, wireless network operators face problems as the newer handsets may not be compatible with newer generation network. In this regard, a reconfigurable or reprogrammable radio is required that can show different functionality with the same hardware. As defined above, the future proof Software Radio answers this requirement by sampling the antenna output directly, which is an impossible task as some RF front end, e.g. for amplifying and filtering, cannot be avoided to be performed at Analogue Front End. Nevertheless, this notion is different to the previous and traditional approach when the transceivers were hardware based. In that case, after the device engineering, it was exploitable only for the purpose for which it was designed. However, this approach was not able to answer the ever changing requirements of transceiver. The basic notion

behind Software Defined Radio, which is the realizable version of Software Radio, concept is the exact opposite of this very approach, i.e. as many functional blocks (ideally all: which is the definition of Software Radio) are software based as possible. This way, the functions that were carried out in hardware are performed by software, thus modifiable. Traditional Radios were built only for a particular frequency range, modulation type, and output power, which is in complete contrast to this SDR technology. This task is achieved by updating the software on the transceiver. The term was first coined in 1991 by J.Mitola [2].

The term Software Defined Radio (SDR) is the pragmatic version of the ideal Software Radio defined above. There are many different definitions of SDR, but we will stick to the definition of SDR Forum (Wireless Innovation Forum) [1] formed together with Institute of Electrical and Electronic Engineers (IEEE) P1900.1 group that says,

#### "a radio in which some or all of the physical layer functions are software defined."

The physical layer functions refer to the specialized functional blocks that constitute the very functionality of SDR. This definition supports the notion of replacing as many hardware components as possible from traditional hardware based design to the software based SDR. As pointed out by Mitola,

"This term intends to signal the shift from digital radio to multiband multimode software-defined radios where "80%" of the functionality is provided in software, versus the "80%" hardware of the 1990's. "

The very first definition covered only the range of operating frequencies from 2 MHz to 2 GHz. This first definition was meant for military applications as a single radio was desired to communicate with different radios that exploit different RF bands. With the commercial applications using this notion, this definition has evolved to a great extent with the passage of time. The ideal Software Radio places the A/D and D/A converters at the closest proximity of the antenna. This leads to signal processing functionality such as modulation at transmitter and tuning/detection of receiver signal and demodulation at the receiver being performed by different general purpose microprocessors and DSPs. Unfortunately, despite being the basic functional block of any SDR equipment, the performance advances in ADC and DAC are slower than other SDR functional blocks. This leads to the inability of ADCs and DACs to cope up with the high frequency signals. We have claimed the ADCs and DACs to be the basic functional block as they define the bandwidth and it is a well established fact that higher frequencies cause aliasing, leading to the requirement of anti-aliasing filter before ADC. It is because of this reason that the received signal is usually sampled at much higher sampling rates than required to relax the specifications of the anti-aliasing filter. The second implication of high bandwidth combined with dynamic range is the undesirable increase in power consumption. It has also been reported that the base stations and user terminals ask for more and more performance efficient ADCs. Thus, the Software Radio is declined to Software Defined Radio: the pragmatic form of Software Radio, by the reduction of the bandwidth that has to be digitized by ADC. This is where the idea of Intermediate Frequency (IF) comes into play. This IF does not exist in the ideal Software Radio. However, in SDR, we are obliged to select a limited bandwidth from the full band. This practise leads to practical version of Software Radio: SDR, by bifurcating the whole communication waveform into analogue and digital parts i.e. the software processing is done at IF level. This is visualized in Figure 1. This also helps in overcoming the impossibility of wideband receiving antenna design that receives all multiband modes.

Fig. 1. The practical SDR Block Diagram at receiver side

We can see in Figure 1 that the functionality is divided into AFE and DFE. The AFE is necessary to select a bandwidth and to shift it from RF to an Intermediate stage, IF. The DFE is the real notion where the software part of the radio is implemented, i.e. analogue functionality is replaced by digital functionality. At the receiver side, this functionality comprises of I/Q down conversion, sample rate conversion and channelization, as shown in Figure 1. The channel selection is necessary in SDR as compared to ideal Software Radio because of the bandwidth selection criteria, due to the absence of ADCs and DACs supporting the huge bandwidth covering all the communication services required by the popular Standards. It includes baseband conversion and channel filtering. The most wireless standards cannot be implemented with 100 % software because of the reasons explained. The realization of ADCs with extremely high sample rates, with the ability to process in software the bandwidths of all ranges, immediately after the antenna will be a breakthrough in this technology. Also the absence of dealing with extreme dynamic range, which is the measure of the highest and lowest level signals present simultaneously in the radio, is another ADC/DAC related factor degrading the ideal Software Radio to Software Defined Radio. It is because of this reason that ADC conversion is not practical immediately after the antenna. Also, the signal processing with respect to DFE including channelization cannot be performed at RF level. However, in our opinion it will take several years to realize such ADCs with sufficient dynamic range, quantization and sampling frequency, that could support the bandwidths covering all the services provided by the terminal. We have already stated above that ADC engineering is less accelerated research area with respect to SDR engineering.

Software Engineering for SDR is a challenging task as it encounters the key software design concepts such as portability and reusability of the applications code. This challenge is further enhanced when seen in the framework of embedded systems, where very serious resource constraints are encountered. There has been an exponential growth in the ways and means of communication needs: data, video, voice command and control, emergency communication etc. - In this very paradigm modifying and updating the transceiver in a cost-efficient manner has become extremely important. SDR technology is promised to bring the desired flexibility, cost effectiveness and power to drive the radio engineering technology forward in the most technological efficient way. This technology efficiency refers to facilitating transition from dedicated to general-purpose hardware, thereby substituting hardware with software processing. The notion of SDR is an efficient combination of hardware and software in such a fashion that the physical layer functions are modifiable with the least possible changes in hardware. This task is accomplished by programmable processing technologies. This includes FPGA, DSP, GPP, Programmable SoC or other application specific processing entities. The discussion carried out so far can be summarized in three points: moving A/D as close to antenna as possible, replacing hardware with software processing using FPGAs, for example, and substituting dedicated hardware with flexible and general purpose components.

Another aspect refers to the ever increasing traffic rate but decreasing amounts of Spectrum. The Cognitive Radio notion, based on SDR, addresses this issue. So, another usage of SDR can be seen in the CR engineering. This too requires more sophisticated implementation of signal processing algorithms to be mapped on the radio. The need of deploying multiple standards within a single device can be addressed in the most efficient way by this sophisticated algorithm implementation. In a software radio, multiple waveforms can be implemented in a software, using the same hardware. This means that a single radio is meant to communicate with many others only with the change in software, whereas retaining the same hardware. This way interoperability is achieved within different communication needs defined above (data, video, voice command and control, emergency communication). This leads to the easy adaptation of new technologies at a reasonable cost. In order to engineer such radios, that are able to operate in many domains with the minimum or no change of hardware (ideally), there is a need of a standardized architecture. This architecture should help in achieving interoperability apart from reducing time to market by reducing the development time via component re-usage. The SDR provides a flexible radio architecture that allows changing the radio personality in time. This is referred to as Software Communication Architecture (SCA) [17]. The SCA is one of the key elements in the US military's Joint Tactical Radio System (JTRS), which is a SDR. We define SCA in detail in Section 4 of this Chapter.

SDR has found uses in academia, industry, government and military applications. As we have seen that Software Defined Radio has no single, unified, globally recognized definition, thus its definition constitutes the features and issues. It is only by understanding these issues that we can come up with

an efficient solution that addresses the wide range of applications and standards. The Section 2 of this Chapter provides an overview of all these aspects.

SDR is known to provide many opportunities in multiple domains, e.g. it replaces cellular base stations with Software Defined Multi-protocol base stations leading to the rapid introduction of the new Standards. At some point in time, it is also expected that SDR will provide a cheaper solution than conventional mobile terminals. Furthermore, it also gives an opportunity for anticipated wireless mobile users to personalize their units as Standards are upgraded. The concept of Cognitive Radio is also based on reconfigurability. In order to exploit the spectrum opportunities, CR needs platforms with faster reconfiguration capabilities. Chapter 3 is dedicated to the Cognitive Radio, however we need to make this a point that CR technology is based on SDR as well. In the long run, standardized open architectures are expected to become more popular. There are some disadvantages of SDR as well as in any real world entity. The security challenges are there as reconfigurable devices are more vulnerable to malicious attacks, e.g. during reconfigurability, there should be some mean to avoid the installation of malicious or altered code. The conventional security architectures are rigid enough to address this issue as they are known to be inherently less flexible. Also, the ideal Software Radio is still unrealizable as the non-practical goal of communication at any desired bandwidth, modulation and data rate is not achievable. Therefore, the researchers are working on the ADCs that will be capable of very high sampling rate with operating bandwidth of several GHz, greater quantization bits for dynamic range and low power consumption. When these goals will be achieved, a breakthrough can be expected in this technology. Nevertheless SDR has the potential to enhance the productivity of radio engineering by software.

We have noticed that SDR is a general device that can be reprogrammed to operate in various models, unlike AM or FM radios. The first ever device to demonstrate a completely software programmable radio was SPEAKeasy1[3]. Although it was a 6 feet tall rack of equipment but it led to project SPEAKeasy 2 that was a complete radio packaged in a practical radio size. It was the first SDR to include programmable vocoder and sufficient analog and DSP resources to handle many different kinds of waveform. We will explain more details about the SDR Engineering efforts in Chapter 4.

#### **1.1 Features of SDR:**

The SDR transceiver at both ends (transmitter and receiver) is required to possess some key features so as to enable the SDR to handle all the various broadcast standards – including the future expected standards, in this ever changing and adapting industry. These features are a major motivation within the commercial communications market. We define these key features in this section:

#### **1.1.1. Portability:**

A waveform portability refers to its movement from one platform to another without or minimal change in its components. Waveform applications should be able to rebuilt on another platform without rewriting the whole application. The Software Communication Architecture (SCA) contributes to this very feature. We define it in detail in Section 4 of this Chapter. However, even if a waveform is SCA compliant, it is not a sufficient condition that it will meet all the aspects of portability. The various components of a waveform mapped on FPGAs and DSPs require a transport mechanism. SCA 2.2.2 specifications [17] prescribe adapters between components. These adapters are primary means of communications and are between CORBA and FPGA components. The portability also requires that the component is translated correctly on the new platform. This means that the compatibility issues of language and target processor functionality should be addressed.

#### **1.1.2. Reconfigurability:**

This feature is related to the Portability that we have just defined. However, the only addition is that of dynamic reconfiguration of the waveform. The waveform should be reconfigured dynamically in such a way that the end user should not sense the internal change. However, different processing elements, in particular, different programmable processing technologies possess different features ultimately supporting different functionalities. Another important aspect is the trade-off between reconfigurability and energy efficiency in the embedded paradigm. The more energy efficient waveform component tends to be less reconfigurable and vice-versa. The interfacing of all the waveform components to constitute an application seems like a simple task, however it may lead to less reconfigurable waveform if not properly taken care of. The SDR should be able to process signals of all the Standards of specific application. This will enable the capability to change the functionality of radio during mission development or after the launch of mission.

#### **1.1.3.** Seamless Mobility:

The multiple analog transceivers approach is the equivalent of this feature in traditional radio engineering. Although the cellular services possess the feature of all time connectivity, the seamless mobility has not been realized 100 % till date. As an example, the wireless hotspots for 802.11 are yet not figured out easily. Thus the feature of seamless mobility leading to ubiquitous connectivity still needs further work out. In this regard, we have designed a Transceiver that we will explain in Chapter 5. The multiband solution is a way to achieve this seamless mobility. A multiband solution refers to a transceiver architecture that accommodates multiple bandwidths, signal levels and modulation types. We will explore all these issues in detail later in this thesis. A very simplistic approach to explain this ubiquitous connectivity is to opt one single Standard and attempt global regulation, thus providing an

idealistic vision. However, due to obvious reasons, this over simplistic approach is not technologically possible.

#### **1.1.4.** Interoperability:

The feature of interoperability has always been a challenge in public safety and military communications. It refers to the support of open architecture radio systems, e.g. Vanu Inc [4, 5] has demonstrated a multi-mode multi-band radio operating on a Compaq iPAQ platform. Robust methods for identifying incoming waveforms are the interoperability capabilities that are required for future SDRs. The SDR platform has an analog front end for signal transmission and a processing element to perform the modulation and demodulation functions in the radio. The modulation scheme used is normally known before hand. Interoperability seeks to devise solutions to dynamically identify waveforms by their analog and digital characteristics. The detection would then allow multiple radio platforms to communicate autonomously with each other. Core Framework concept, that we will explore in Section 4 of this Chapter is the way to achieve Interoperability in SDR engineering design.

Thus, SDR is a modern radio communication system with the addressed key-features that lead to software implementation of its components. The key features defined above make this a dominant technology in the long term. SDR has been deemed as the future of telecommunications, as most radio devices are expected to be SDRs in the near future. In this respect, this Section has started the Chapter 2 with a detailed introduction and defining features of SDR which are essential to understand.

#### 2. Issues in SDR:

There are numerous issues and challenges that need to be addressed, so as to make this technology 100 % viable. The fundamental challenge still remains the same as we have discussed in the SDR definition, i.e. processing the waveform applications with multiple components with reasonable computational capacity, in such a way that the need of IF stage should be eliminated, or minimized to a great extent. Also the discussed features in Section 1.1 should be incorporated. Starting from the very first reviews in this topic [6], there have been significant issues that have been bought to notice, such as issues in smart application engineering, computational requirements, analog to digital conversion, efficient and secure way to download software, processing elements choice, certification and standardization issues and smart antenna design. This Section defines all these issues. However, this list is, by no means, an exhaustive detail of all the research issues and challenges that need to be addressed.

#### **2.1 Application Engineering:**

The wavefrom components engineering is a difficult and challenging issue. The difficulty is further added when the SCA compliant application needs to be developed. Learning and comprehending SCA may prove challenging and consume several months. We started our work by Open Source SCA Implementation:: Embedded (OSSIE) [7,8] which we define later in this Chapter. OSSIE is an open source implementation that can be useful for beginners. There are certain aspects that need to be well understood while defining SDR waveform components manually, notably: CORBA, Object Oriented Programming, Embedded Systems constraints. OSSIE reduces the learning curve and hence the application development efforts. The SCA specifications ask the use of CORBA as a middleware platform. CORBA is known to consume a lot of memory and other resources, which is further exacerbated by the embedded resource constraint environment. This calls for the need of another available middleware, given the fact that CORBA is not a popular tool any more due to its tedious learning curve and less throughput, which is already dependent on message size to be transferred. On the other hand, the feature of portability is compromised. There have been some Object Request Brokers (ORBs) developed for FPGAs in recent years [9]. This is a way to achieve portability as the CORBA communication between all the processing elements will be easier. However, still the processing elements will encounter the latency and throughput implications, for which the CORBA is known for. The Data Distribution Service (DDS) is recommended as a substitute middleware to CORBA in the SCA framework. Till date, there has been no replacement of CORBA in the SCA context with another middleware meant to be less complex and better performing. There are also efforts going on to make ORBs faster and less memory hungry. In short, there exist ongoing Middleware activities because of which we can anticipate that soon there will be a clear path for middleware to make application engineering easier.

#### 2.2 Computational Capacity:

A small hand held device is required to be multimode these days. In such multimode terminals, the basic issue is achieving the computational requirements in such a way that meet the power consumption, i.e. the power consumption should be below a certain threshold leading to the acceptable limits of battery discharge. At the same time, the temperature of the multimode handheld device should not be high enough to irritate the end user. SDR application engineering is addressed in the previous sub-section. This application performs signal processing at various stages for transmit and received signal, apart from other application control activities. We can divide the SDR waveform in waveform processing elements and administrative elements. Waveform processing elements have a defined algorithm. This is the reason that we can exploit the inherent parallelism in these components. This is an efficient way to address this issue of computational capacity. We delve into more details

about our efforts, in this regard, in Chapter 4. Administrative portion of the waveform has not that much level of inherent parallelism. The reason is that the administrative components are events driven, i.e. they are dependent on events to execute various administrative and control commands. In general the waveform components can be made to run in parallel. This can be explained by the distributed systems architecture support in SCA. The waveform processing elements require more computational capacity. It is because of this reason that we have addressed the waveform components parallelization strategy in Chapter 4 to address this issue.

#### **2.3** Analog to Digital and Digital to Analog Conversion: