# Ordonnancement temps réel dur multiprocesseur tolérant aux fautes appliqué à la robotique mobile

Mohamed Marouf

#### ▶ To cite this version:

Mohamed Marouf. Ordonnancement temps réel dur multiprocesseur tolérant aux fautes appliqué à la robotique mobile. Autre [cs.OH]. Ecole Nationale Supérieure des Mines de Paris, 2012. Français. NNT: 2012ENMP0017. pastel-00720934

# HAL Id: pastel-00720934 https://pastel.hal.science/pastel-00720934

Submitted on 26 Jul 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

École doctorale n°432 : Sciences des Métiers de l'Ingénieur

#### **Doctorat ParisTech**

## THÈSE

pour obtenir le grade de docteur délivré par

# l'École nationale supérieure des mines de Paris

Spécialité « Informatique temps-réel, robotique et automatique »

présentée et soutenue publiquement par

#### **Mohamed MAROUF**

le 01 juin 2012

Ordonnancement temps réel dur multiprocesseur tolérant aux fautes appliqué à la robotique mobile

Fault-tolerant multiprocessor hard real-time scheduling for mobile robotics

Directeur de thèse : Yves SOREL

Co-encadrement de la thèse : Brigitte D'ANDREA-NOVEL

Jury

Mme. Maryline CHETTO, Professeur, Université de NantesRapporteurM. Pascal RICHARD, Professeur, ENSMARapporteurMme. Brigitte D'ANDREA-NOVEL, Professeur, MINES ParisTechExaminateurM. Fawzi NASHASHIBI, Directeur de recherche, INRIA RocquencourtExaminateurM. Patrick RIVES, Directeur de recherche, INRIA Sophia AntipolisExaminateurM. Yves SOREL, Directeur de recherche, INRIA RocquencourtExaminateur

MINES ParisTech

Centre de robotique (CAOR)

60. boulevard Saint-Michel 75272 Paris cedex 06

T H È S

# Remerciements

Je tiens à remercier en premier lieu mon directeur de thèse Yves Sorel pour son encadrement excellent. Il a toujours été attentif et disponible malgré ses nombreuses charges, et il a su m'apprendre, grâce à ses compétences scientifiques, la rigueur et l'autonomie qui resteront pour moi des moteurs de mon travail de chercheur.

Je tiens aussi à remercier Maryline Chetto et Pascal Richard qui ont eu la lourde tâche d'être rapporteurs de ma thèse et qui m'ont fait des commentaires constructifs ayant permis l'amélioration de mon manuscrit. De même, je remercie Brigitte d'Andréa-Novel, Fawzi Nashashibi et Patrick Rives pour avoir accepté de faire partie de mon jury de thèse.

J'exprime aussi mes vifs remerciements à Michel Parent pour m'avoir accueilli comme stagiaire au sein de son équipe et ensuite m'avoir donné l'opportunité d'effectuer cette thèse. Je remercie également Fawzi Nashashibi qui a toujours été à mon écoute et a veillé sur le bon déroulement de ma thèse. Je remercie aussi Brigitte d'Andréa-Novel pour sa rigueur et ses orientations pertinentes.

Je tiens également à remercier Laurent George avec qui j'ai eu le plaisir de travailler sur certains aspects de ma thèse.

Je remercie aussi tous mes collègues des équipes projets AOSTE et IMARA pour les bons moments passés ensemble à l'INRIA-Rocquencourt. De même, je remercie tous mes amis qui m'ont soutenu tout au long de ma thèse.

À mes parents, à mes frères et sœurs, à mon églantine.

# Table des matières

|   | List | e des fig | gures     |                                                | 9         |

|---|------|-----------|-----------|------------------------------------------------|-----------|

|   | List | e des ta  | bleaux    |                                                | 13        |

|   | Intr |           | n général | e<br>                                          | <b>15</b> |

|   |      |           |           |                                                |           |

|   |      |           |           | la thèse                                       |           |

| Ι | Éta  | at de l'  | art       |                                                | 17        |

| 1 | Ord  | onnanc    | ement de  | s systèmes temps réel embarqués                | 19        |

|   | 1.1  | Systèn    | nes temps | réel embarqués                                 | 19        |

|   |      | 1.1.1     | _         | istiques                                       | 19        |

|   |      | 1.1.2     |           | eture des systèmes embarqués                   |           |

|   |      | 1.1.3     | contrain  | tes des systèmes temps réel embarqués          | 20        |

|   |      |           | 1.1.3.1   | contraintes temporelles                        |           |

|   |      |           | 1.1.3.2   | contraintes matérielles                        | 21        |

|   | 1.2  | Ordon     | nancemen  | t de tâches temps réel                         | 21        |

|   |      | 1.2.1     |           | emps réel                                      |           |

|   |      |           | 1.2.1.1   | Modèles de tâches                              | 22        |

|   |      |           | 1.2.1.2   | contraintes temps réel                         |           |

|   |      | 1.2.2     | Typolog   | ie des algorithmes d'ordonnancement            | 26        |

|   |      | 1.2.3     | Algorith  | mes d'ordonnancement monoprocesseur            | 27        |

|   |      |           | 1.2.3.1   | Préemptifs périodiques, apériodiques et spora- |           |

|   |      |           |           | diques                                         | 27        |

|   |      |           | 1.2.3.2   | Non préemptifs périodiques stricts             | 30        |

|   |      | 1.2.4     | Algorith  | mes d'ordonnancement multiprocesseur           | 31        |

|   |      |           | 1.2.4.1   | Approche globale                               | 32        |

|   |      |           | 1.2.4.2   | Approche partitionnée                          | 33        |

|    |      | 1.2.4.3 Approche semi-partitionnée                         | 33 |

|----|------|------------------------------------------------------------|----|

|    | 1.3  | Graphes d'algorithme et d'architecture                     | 34 |

|    | 1.5  | 1.3.1 Graphe d'algorithme                                  | 34 |

|    |      | 1.3.2 Graphe d'architecture                                | 36 |

|    | 1.4  | Conclusion                                                 | 37 |

|    | 1.4  | Conclusion                                                 | 31 |

| 2  | Tolé | rance aux fautes des systèmes temps réel embarqués         | 39 |

|    | 2.1  | Introduction                                               | 39 |

|    | 2.2  | Terminologies de la tolérance aux fautes                   | 39 |

|    |      | 2.2.1 Faute                                                | 40 |

|    |      | 2.2.2 Erreur                                               | 42 |

|    |      | 2.2.3 Défaillance                                          | 42 |

|    | 2.3  | Tolérance aux fautes                                       | 44 |

|    |      | 2.3.1 Principes de la tolérance aux fautes                 | 44 |

|    |      | 2.3.2 Tolérance aux fautes logicielles et matérielles      | 45 |

|    | 2.4  | Redondances pour la tolérance aux fautes matérielles       | 46 |

|    |      | 2.4.1 Redondance logicielle                                | 46 |

|    |      | 2.4.1.1 Redondance active                                  | 47 |

|    |      | 2.4.1.2 Redondance passive                                 | 48 |

|    |      | 2.4.1.3 Redondance hybride                                 | 50 |

|    |      | 2.4.1.4 Comparaison entre les trois types de redondance    | 51 |

|    |      | 2.4.2 Redondance matérielle                                | 52 |

|    |      | 2.4.2.1 Généralités                                        | 52 |

|    |      | 2.4.2.2 Redondance modulaire triple                        | 52 |

|    |      | 2.4.2.3 Cas général de la redondance modulaire             | 53 |

|    | 2.5  | Conclusion                                                 | 53 |

|    |      |                                                            |    |

| II | O    | rdonnancement temps réel monoprocesseur                    | 55 |

| 3  | Ord  | onnancement temps réel monoprocesseur non préemptif pério- |    |

|    |      | e strict                                                   | 57 |

|    | 3.1  | Introduction                                               | 57 |

|    | 3.2  | Stratégie d'ordonnancement                                 | 58 |

|    | 3.3  | Analyse d'ordonnançabilité de tâches harmoniques           | 59 |

|    |      | 3.3.1 Arbre d'ordonnancement                               | 59 |

|    |      | 3.3.2 Toutes les tâches ont des périodes distinctes        | 62 |

|    |      | 3.3.3 Certaines tâches ont des périodes identiques         | 65 |

|    |      | 3.3.4 Algorithme d'ordonnancement                          | 69 |

|    | 3.4  | Analyse d'ordonnançabilité de tâches non harmoniques       | 71 |

|    |      | 3.4.1 Conditions d'ordonnançabilité pour deux tâches       | 71 |

TABLE DES MATIÈRES 5

|    |       | 3.4.2 Conditions d'ordonnançabilité pour plus de deux tâches .  | 73  |

|----|-------|-----------------------------------------------------------------|-----|

|    |       | 3.4.2.1 Tâche candidate à période multiple du PGCD .            | 77  |

|    |       | 3.4.2.2 Tâche candidate à période non multiple du PGCD          | 81  |

|    |       | 3.4.3 Tri des tâches selon les multiplicités de leurs périodes  | 84  |

|    |       | 3.4.4 Algorithme d'ordonnancement                               | 85  |

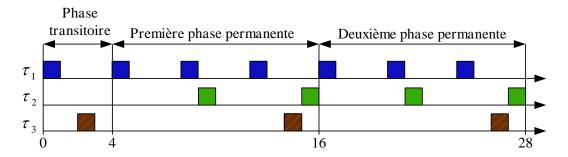

|    | 3.5   | Phase transitoire et phase permanente                           | 88  |

|    | 3.6   | Analyse de performances                                         | 90  |

|    |       | 3.6.1 Algorithme de génération de tâches                        | 90  |

|    |       | 3.6.2 Simulations et discussion des résultats                   | 92  |

|    | 3.7   | Conclusion                                                      | 94  |

| 4  | Ord   | onnancement temps réel monoprocesseur combinant non préemp-     |     |

|    | tif e | t préemptif                                                     | 95  |

|    | 4.1   | Introduction                                                    | 95  |

|    | 4.2   | Combinaison de tâches NPPS et PP                                | 96  |

|    |       | 4.2.1 Stratégie d'ordonnancement                                | 96  |

|    |       | 4.2.2 Analyse d'ordonnançabilité                                | 96  |

|    | 4.3   | Ordonnancement de tâches préemptives périodiques strictes 1     | 100 |

|    |       | 4.3.1 Modèle de tâches                                          | 100 |

|    |       | 4.3.2 Analyse d'ordonnançabilité                                | 101 |

|    | 4.4   | Conclusion                                                      | 105 |

| II | T (   | Ardonnoncoment temps réal multiprocesseur                       | 07  |

| 11 | 1 0   | ordonnancement temps réel multiprocesseur 1                     | U/  |

| 5  |       | onnancement temps réel multiprocesseur non préemptif pério-     |     |

|    | -     |                                                                 | 109 |

|    | 5.1   |                                                                 | 109 |

|    | 5.2   | Analyse d'ordonnançabilité                                      |     |

|    | 5.3   | Déroulement                                                     |     |

|    |       | 5.3.1 Périodicité et transfert de données                       |     |

|    |       | 5.3.2 Algorithme de déroulement                                 |     |

|    | 5.4   | Ordonnancement                                                  |     |

|    |       | 5.4.1 Prise en compte des coûts de communications               |     |

|    |       | 5.4.2 Algorithme d'ordonnancement                               |     |

|    | 5.5   | Conclusion                                                      | 121 |

| 6  |       | onnancement multiprocesseur non préemptif périodique strict to- |     |

|    |       |                                                                 | 123 |

|    | 6.1   |                                                                 | 123 |

|    | 6.2   | Présentation du problème de tolérance aux fautes                | 124 |

|     |            | 6.2.1    | Modèle de fautes                                        | . 124 |

|-----|------------|----------|---------------------------------------------------------|-------|

|     |            | 6.2.2    | Données du problème de tolérance aux fautes             | . 125 |

|     |            | 6.2.3    | Notations et définitions                                |       |

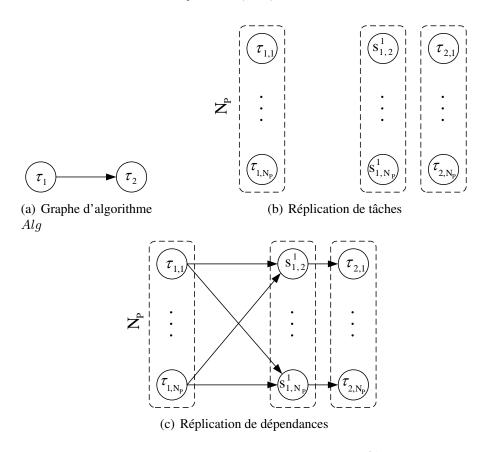

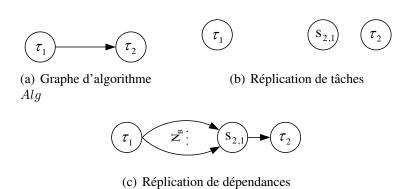

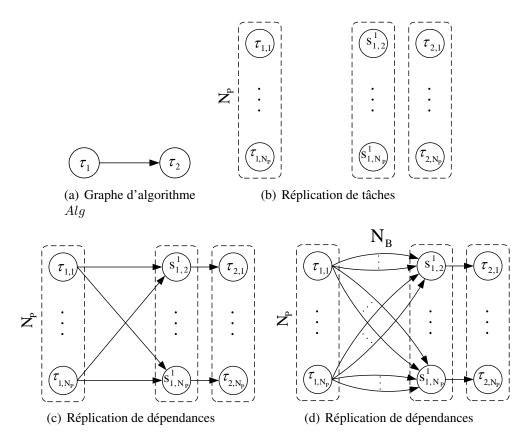

|     | 6.3        | Transf   | Formation de graphe pour la tolérance aux fautes        | . 127 |

|     |            | 6.3.1    | Tolérance aux fautes des processeurs                    | . 127 |

|     |            | 6.3.2    | Tolérance aux fautes des bus de communication           | . 128 |

|     |            | 6.3.3    | Tolérance aux fautes des processeurs et des bus de com- |       |

|     |            |          | munication                                              | . 129 |

|     | 6.4        | Ordon    | nancement tolérant aux fautes                           | . 131 |

|     |            | 6.4.1    | Algorithme d'analyse d'ordonnançabilité                 | . 132 |

|     |            | 6.4.2    | Algorithme de déroulement                               | . 134 |

|     |            | 6.4.3    | Algorithme d'ordonnancement                             | . 134 |

|     | 6.5        | Conclu   | usion                                                   | . 136 |

|     |            |          |                                                         |       |

| IJ  | 7 <b>D</b> | óvolov   | noments legicials at application on CyCah               | 137   |

| 1 ) | , D        | evelop   | ppements logiciels et application au CyCab              | 137   |

| 7   | Dév        | eloppen  | nents du logiciel SynDEx                                | 139   |

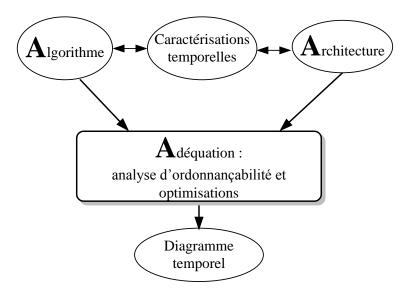

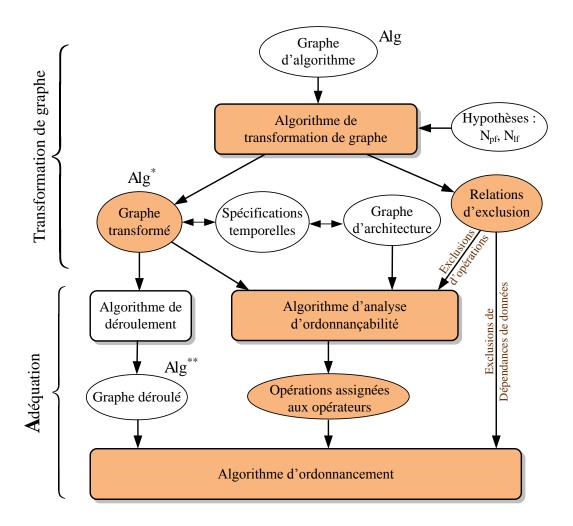

|     | 7.1        | Métho    | odologie AAA et principes de SynDEx                     | . 139 |

|     | 7.2        |          | e d'algorithme et d'architecture                        |       |

|     |            | 7.2.1    | Algorithme                                              | . 141 |

|     |            | 7.2.2    | Architecture                                            | . 143 |

|     |            | 7.2.3    | Caractérisations temporelles                            | . 144 |

|     | 7.3        | Mise à   | à plat                                                  | . 144 |

|     | 7.4        | Adéqu    | nation dans SynDEx V7                                   | . 144 |

|     |            | 7.4.1    | Analyse d'ordonnançabilité                              | . 144 |

|     |            | 7.4.2    |                                                         |       |

|     |            | 7.4.3    | Ordonnancement                                          | . 145 |

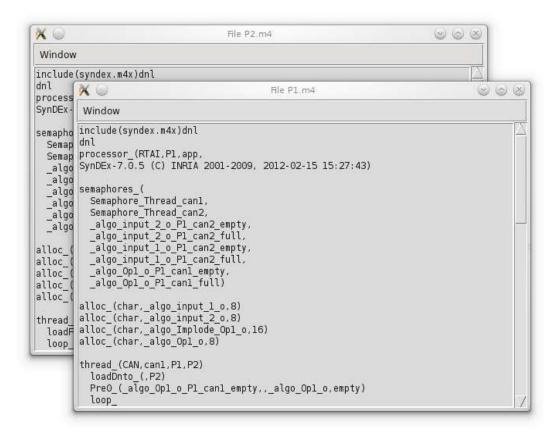

|     | 7.5        | Généra   | ation automatique de code                               |       |

|     |            | 7.5.1    | Génération de macro-code                                |       |

|     |            | 7.5.2    | Génération de code exécutable                           |       |

|     | 7.6        |          | orations apportées à SynDEx                             |       |

|     |            | 7.6.1    | Adéquation                                              |       |

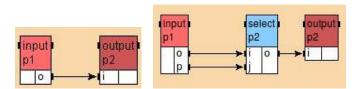

|     |            | 7.6.2    | Extension de SynDEx à la tolérance aux fautes           |       |

|     | 7.7        | Conclu   | usion                                                   | . 151 |

| 8   | Ann        | lication | au suivi automatique de CyCabs tolérant aux fautes      | 153   |

| •   | 8.1        |          | re de la conduite automatique à l'INRIA                 |       |

|     | 8.2        |          | téristiques générales du CyCab                          |       |

|     | 8.3        |          | cations de commande de CyCabs                           |       |

|     |            |          | Application manuelle                                    |       |

TABLE DES MATIÈRES

|   |      | 022     | A1'4'                                                     |

|---|------|---------|-----------------------------------------------------------|

|   | 0.4  | 8.3.2   | 11                                                        |

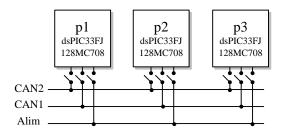

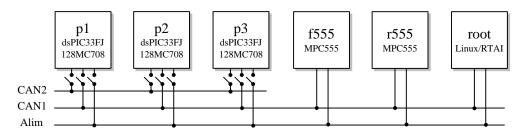

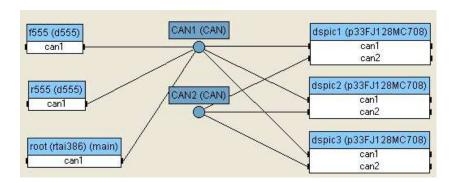

|   | 8.4  |         | ecture à base de dsPIC et de bus CAN                      |

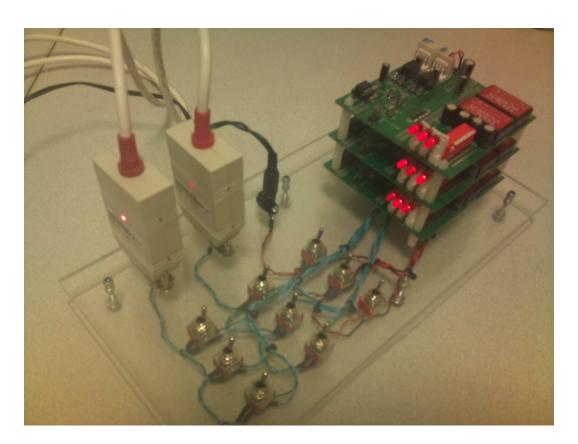

|   |      | 8.4.1   | Banc de test                                              |

|   | 0.5  | 8.4.2   | Cycab tolérant aux fautes                                 |

|   | 8.5  |         | source du dsPIC                                           |

|   | 8.6  |         | nce aux fautes sur le banc de test                        |

|   |      | 8.6.1   | Tolérance aux fautes des bus CAN                          |

|   |      |         | 8.6.1.1 Détection d'erreurs                               |

|   |      | 0.6     | 8.6.1.2 Traitement des erreurs détectées                  |

|   |      | 8.6.2   | Tolérance aux fautes des dsPICs                           |

|   |      |         | 8.6.2.1 Détection d'erreurs                               |

|   |      |         | 8.6.2.2 Traitement des erreurs détectées 168              |

|   | 8.7  |         | nce aux fautes sur le CyCab: application de suivi 168     |

|   |      | 8.7.1   | Communication entre dsPICs et MPC555 170                  |

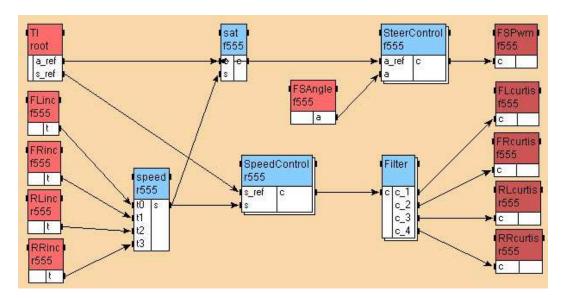

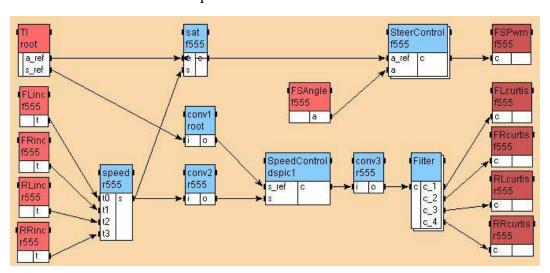

|   |      | 8.7.2   | Application SynDEx de base de suivi automatique de Cy-    |

|   |      |         | Cabs                                                      |

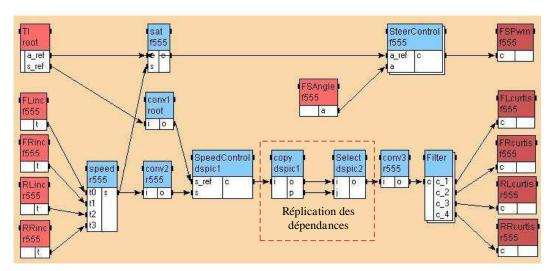

|   |      | 8.7.3   | Tolérance aux fautes des bus CAN 172                      |

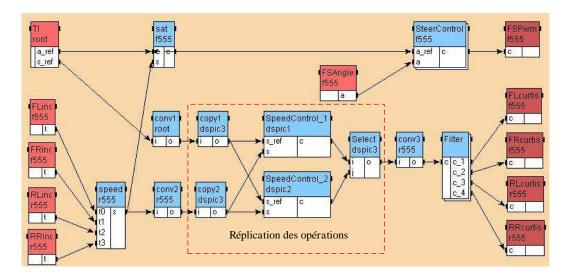

|   |      | 8.7.4   | Tolérance aux fautes des dsPICs                           |

|   | 8.8  | Conclu  | usion                                                     |

|   | Con  | clusion | générale et perspectives 177                              |

|   | Con  |         | usion générale                                            |

|   |      |         | ectives                                                   |

|   |      | 1 crspc | cuves                                                     |

|   |      |         |                                                           |

| V | Ar   | nexes   | 181                                                       |

| ٨ | PC d | mhara   | ué Linux/RTAI, microcontrôleurs MPC555 et dsPIC33 183     |

| А | A.1  | _       | barqué                                                    |

|   |      |         | contrôleur MPC555                                         |

|   |      |         | contrôleur dsPIC33FJ128MC708                              |

|   | 11.5 | WHETOV  |                                                           |

| В | Cod  | e sourc | e des dsPIC pour les communications inter-processeurs 189 |

| C | Prog | gramma  | ation des dsPICs pour la tolérance aux fautes 191         |

|   | C.1  |         | nce aux fautes sur le banc de test                        |

|   |      | C.1.1   | Tolérance aux fautes des bus CAN 191                      |

|   |      | •       | C.1.1.1 Détection d'erreurs                               |

|   |      |         | C.1.1.2 Traitement des erreurs détectées 193              |

|   |      | C.1.2   |                                                           |

|   |      | C.1.2   | C.1.2.1 Détection d'erreurs                               |

|   |      |         |                                                           |

|     |         | C.1.2.2     | Traitement des erreurs détecté | ées |  |  |  | 195 |

|-----|---------|-------------|--------------------------------|-----|--|--|--|-----|

| C.2 | Tolérar | ice aux fau | ıtes sur le CyCab              |     |  |  |  | 196 |

|     | C.2.1   | Commun      | ication entre dsPICs et MPC55  | 55  |  |  |  | 196 |

# Table des figures

| 1.1  | Modèle classique d'une tâche PP $\tau_i(r_i^0, C_i, D_i, T_i)$       |    |

|------|----------------------------------------------------------------------|----|

| 1.2  | Modèle d'une tâche NPPS $\tau_i(C_i, T_i)$                           | 25 |

| 1.3  | Exemple d'un graphe d'algorithme                                     | 35 |

| 1.4  | Exemple d'un graphe d'algorithme infiniment répété                   | 35 |

| 1.5  | Modèles d'architecture                                               | 37 |

| 2.1  | Relation entre faute, erreur et défaillance                          | 40 |

| 2.2  | Couverture entre les hypothèses de défaillance                       | 43 |

| 2.3  | Graphes d'algorithme et d'architecture                               | 46 |

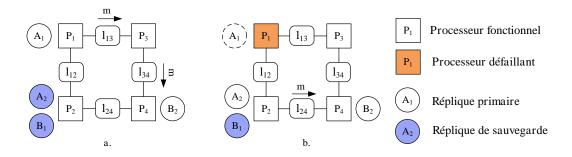

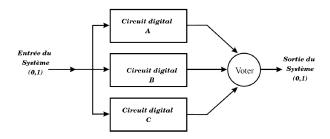

| 2.4  | Tolérance aux fautes des processeurs par redondance active           | 48 |

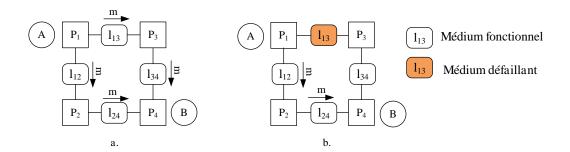

| 2.5  | Tolérance aux fautes des média de communication par redondance       |    |

|      | active                                                               | 48 |

| 2.6  | Tolérance aux fautes des processeurs par redondance passive          | 49 |

| 2.7  | Tolérance aux fautes des média de communication par redondance       |    |

|      | passive                                                              | 50 |

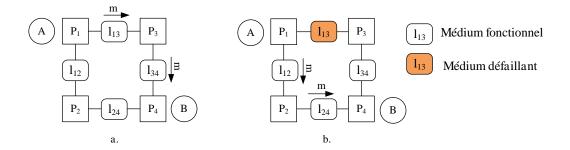

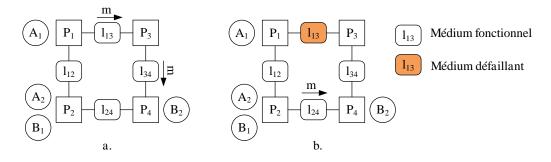

| 2.8  | Tolérance aux fautes des média de communication par redondance       |    |

|      | hybride                                                              | 50 |

| 2.9  | Rodondance modulaire triple                                          | 53 |

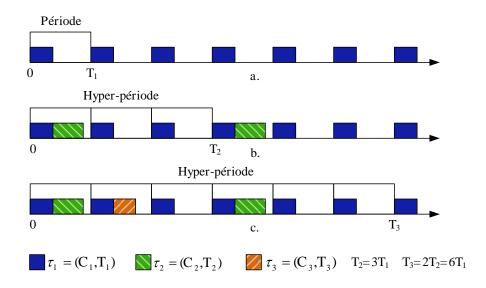

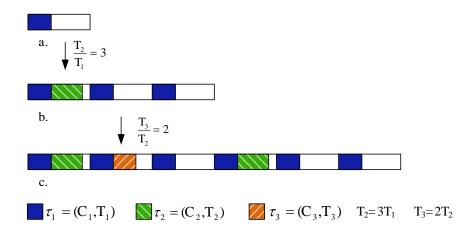

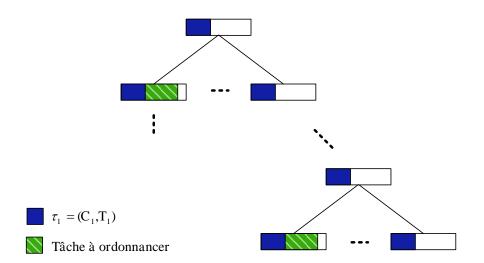

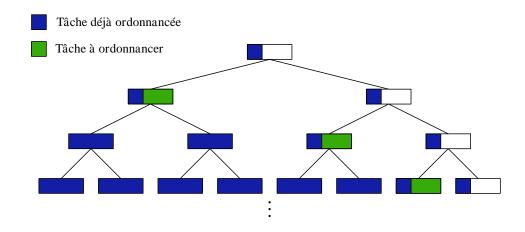

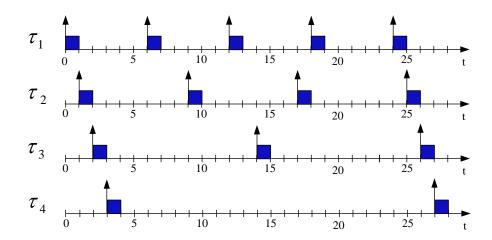

| 3.1  | Ordonnancement de tâches harmoniques                                 | 59 |

| 3.2  | Réduction de l'ordonnancement à l'hyper-période                      | 60 |

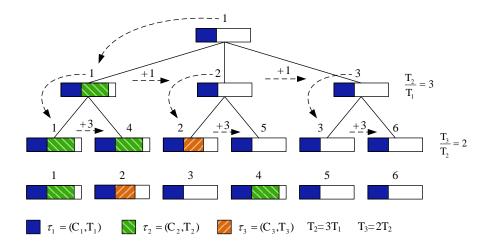

| 3.3  | Arbre d'ordonnancement de tâches harmoniques                         | 61 |

| 3.4  | Arbre d'ordonnancement de tâches harmoniques                         | 63 |

| 3.5  | Arbre d'ordonnancement de tâches harmoniques                         | 65 |

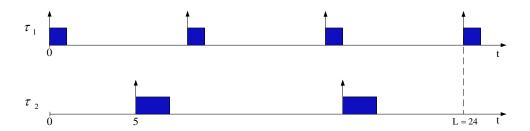

| 3.6  | Ordonnancement de deux tâches                                        | 71 |

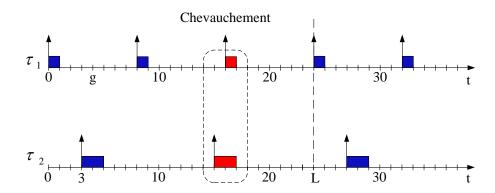

| 3.7  | Chevauchement de deux instances                                      | 73 |

| 3.8  | Diagramme d'ordonnancement de quatre tâches                          | 75 |

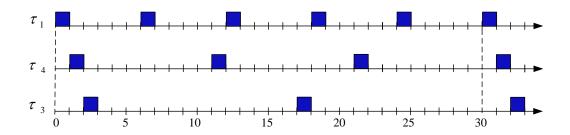

| 3.9  | Ordonnancement des tâches $\tau_1$ , $\tau_2$ et $\tau_3$            | 83 |

| 3.10 | Ordonnancement des tâches $\tau_1$ , $\tau_2$ , $\tau_3$ et $\tau_4$ | 84 |

| 3.11 | Ordonnancement de quatre tâches NPPS                                 | 88 |

| 3.12 | Ordonnancement avec phase transitoire                                | 90 |

TABLE DES FIGURES

|     | Différents ensemble de tâches                                           |

|-----|-------------------------------------------------------------------------|

|     | pour les conditions $CS1$ et $CS2$                                      |

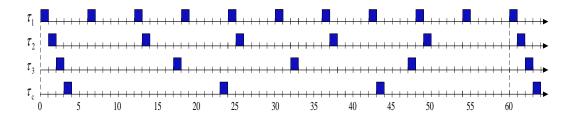

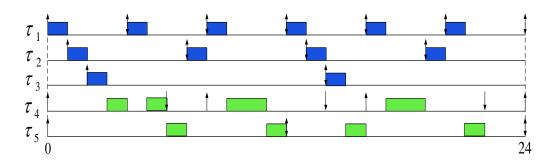

| 4.1 | Diagramme d'ordonnancement de tâches PP et NPPS 100                     |

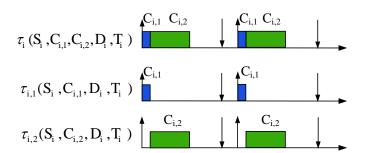

| 4.2 | Décomposition d'une tâche PPS en une tâche NPPS et une tâche PP101      |

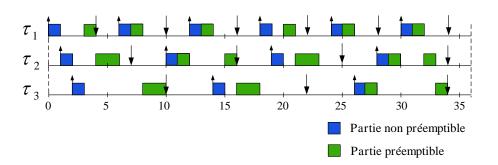

| 4.3 | Diagramme d'ordonnancement de tâches PPS                                |

| 5.1 | Exemple d'un graphe d'algorithme                                        |

| 5.2 | Graphe d'algorithme déroulé                                             |

| 5.3 | Graphe d'algorithme et d'un graphe d'architecture                       |

| 5.4 | Ordonnancement multiprocesseur avec prise en compte du coût             |

|     | de communication                                                        |

| 6.1 | Défaillance complète du bus 1 et partielle du bus 2                     |

| 6.2 | Représentations d'une tâche de sélection $S_{i,j}^k$                    |

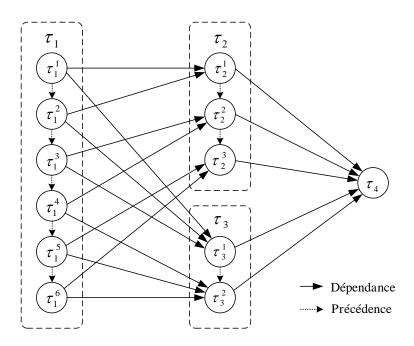

| 6.3 | Transformation de graphe $Alg^*$                                        |

| 6.4 | Transformation de graphe $Alg^*$                                        |

| 6.5 | Transformation de graphe $Alg^*$                                        |

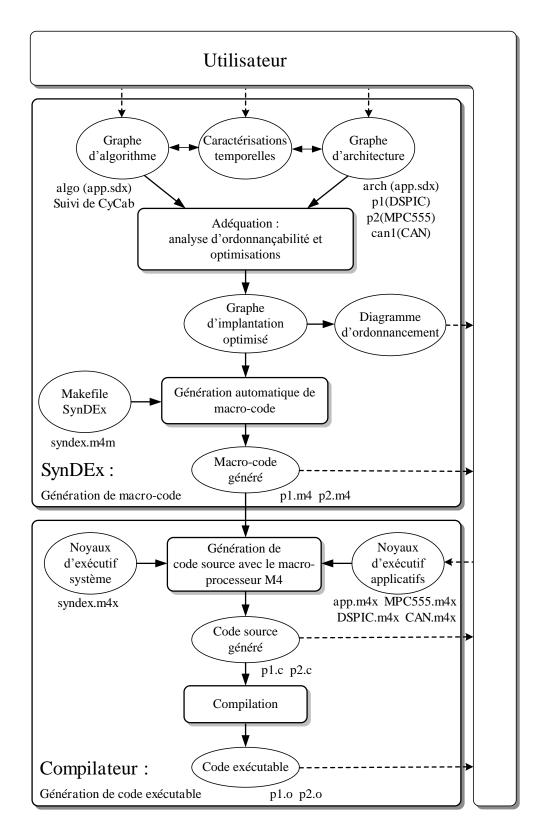

| 7.1 | Méthodologie AAA                                                        |

| 7.2 | Principes de SynDEx                                                     |

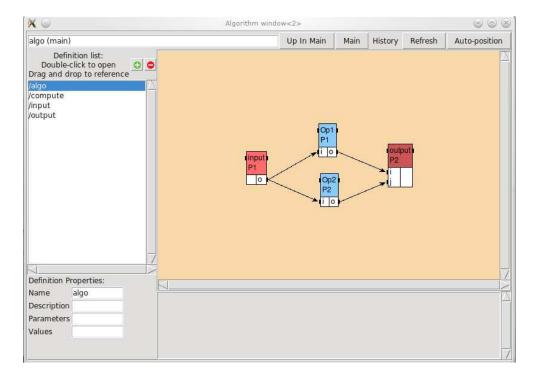

| 7.3 | Graphe d'algorithme dans SynDEx                                         |

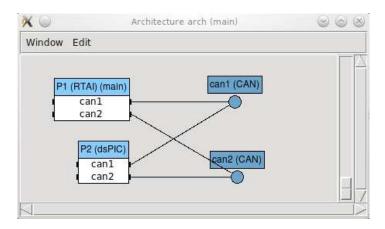

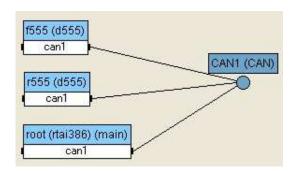

| 7.4 | Graphe d'architecture dans SynDEx                                       |

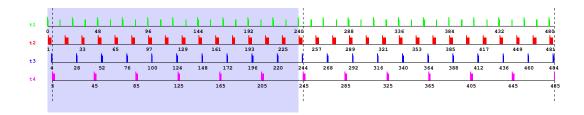

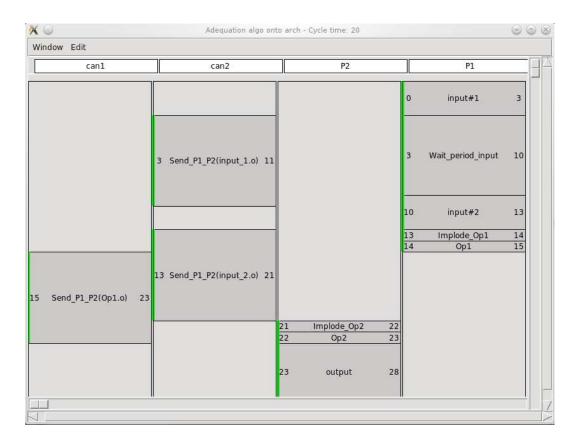

| 7.5 | Graphe temporel d'exécution de l'algorithme                             |

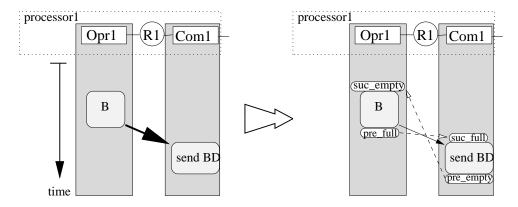

| 7.6 | Synchronisations intra-répétition et inter-répétition pour un envoi     |

|     | de donnée                                                               |

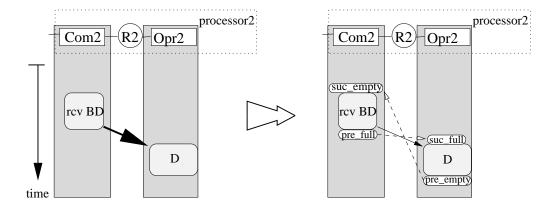

| 7.7 | Synchronisations intra-répétition et inter-répétition pour une ré-      |

|     | ception de donnée                                                       |

| 7.8 | Macro-code généré pour un processeur                                    |

| 7.9 | SynDEx multipériode tolérant aux fautes                                 |

| 8.1 | CyCab                                                                   |

| 8.2 | Architecture matérielle d'un CyCab                                      |

| 8.3 | Graphe d'algorithme de l'application manuelle du CyCab 156              |

| 8.4 | Graphe d'architecture de l'application manuelle du CyCab 158            |

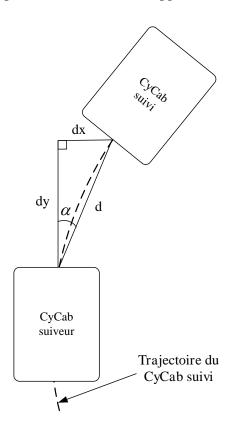

| 8.5 | Distance longitudinale $dy$ , distance latérale $dx$ et angle de dépor- |

| 0 1 | tation $\alpha$                                                         |

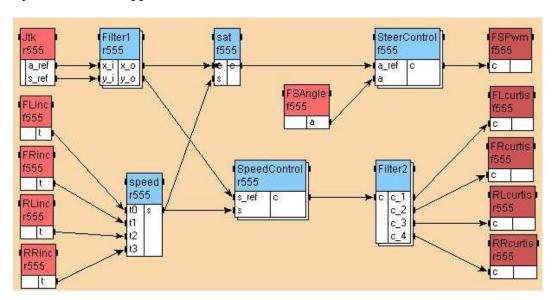

| 8.6 | Graphe d'algorithme de l'application automatique du CyCab 159           |

| 8.7 | Architecture du banc de test                                            |

| 8.8 | Architecture du CyCab tolérant aux fautes                               |

TABLE DES FIGURES 11

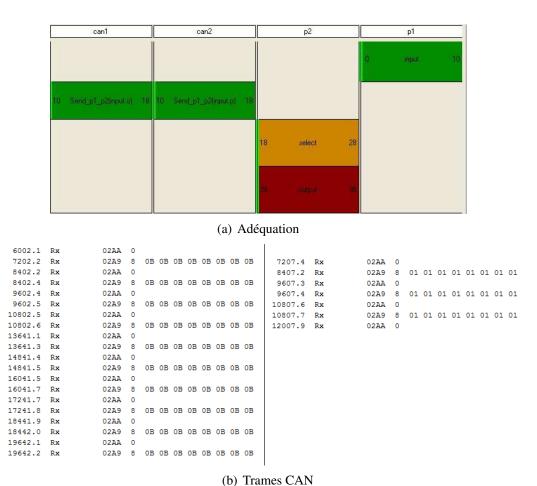

| 8.9  | Graphes d'algorithme initial et transformé et graphe d'architec-  |

|------|-------------------------------------------------------------------|

|      | ture pour la tolérance aux fautes de bus CAN                      |

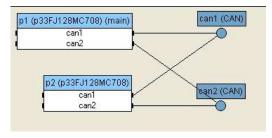

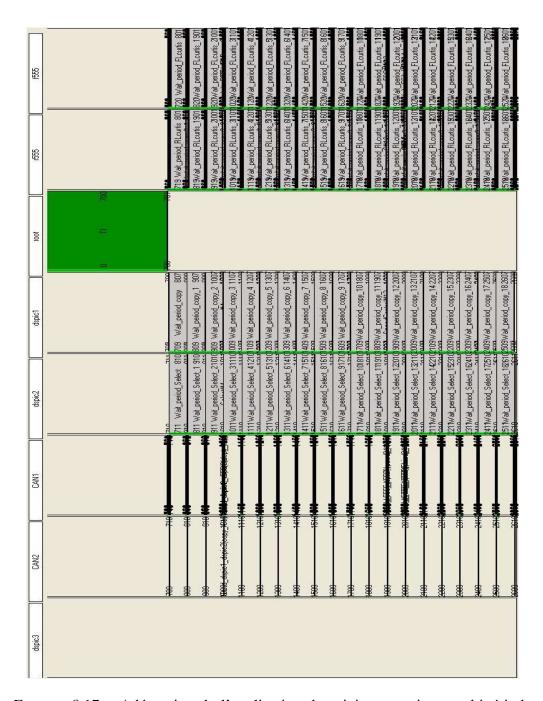

| 8.10 | Adéquation et trames CAN lors d'erreur sur CAN2 166               |

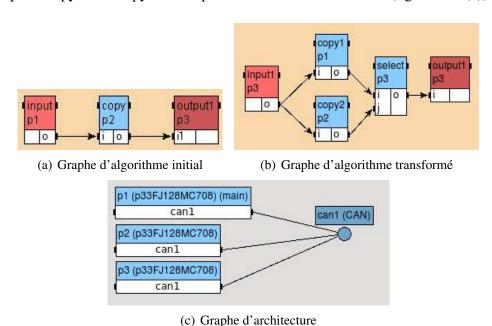

| 8.11 | Graphes d'algorithme initial et transformé et graphe d'architec-  |

|      | ture pour la tolérance aux fautes des dsPICs                      |

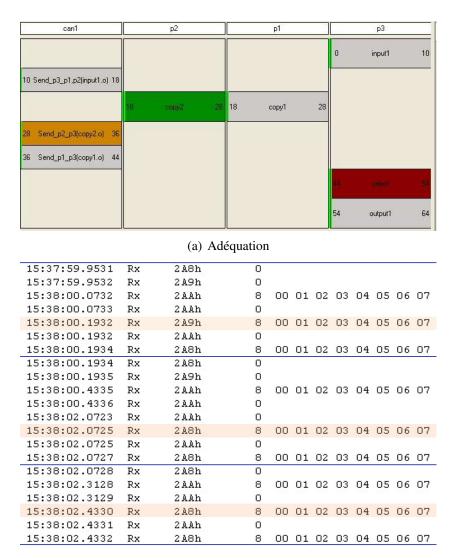

| 8.12 | Adéquation et trames CAN lors d'erreur sur p3 169                 |

| 8.13 | Graphe d'algorithme de l'application de suivi automatique multi-  |

|      | période de base                                                   |

| 8.14 | Graphe d'architecture de l'application de suivi automatique mul-  |

|      | tipériode de base                                                 |

| 8.15 | Graphe d'algorithme de l'application de suivi automatique multi-  |

|      | période tolérante aux fautes de bus CAN                           |

| 8.16 | Graphe d'algorithme de l'application de suivi automatique multi-  |

|      | période tolérante aux fautes de dsPICs                            |

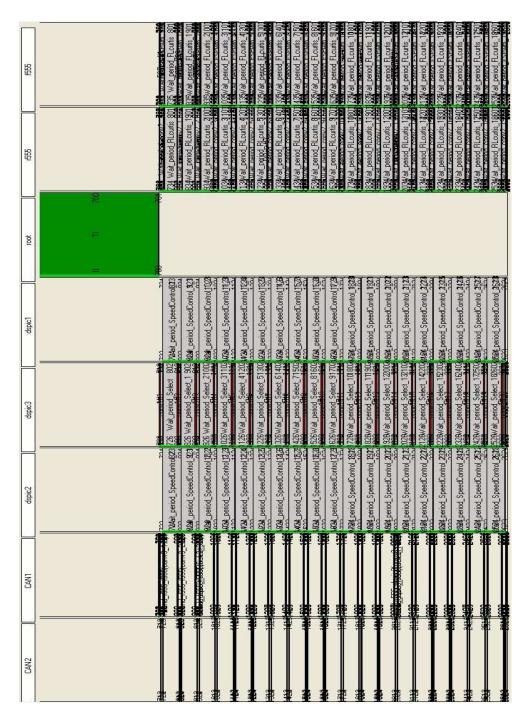

| 8.17 | Adéquation de l'application de suivi automatique multipériode to- |

|      | lérante aux fautes de bus CAN                                     |

| 8.18 | Adéquation de l'application de suivi automatique multipériode to- |

|      | lérante aux fautes de dsPICs                                      |

| A.1  | Carte mère (à gauche) et fille (à droite)                         |

| A.2  | Banc de test à base de trois dsPIC33FJ128MC708 187                |

# Liste des tableaux

| 2.1         | Comparaison entre les trois approches de redondance   |  |  |  |  |  |  |

|-------------|-------------------------------------------------------|--|--|--|--|--|--|

| 4.1         | Calcul des pires temps de réponse $RT_4$ et $RT_5$    |  |  |  |  |  |  |

| 4.2         | Calcul des pires temps de réponse $RT_{1,2}$          |  |  |  |  |  |  |

| 4.3         | Calcul des pires temps de réponse $RT_{2,2}$          |  |  |  |  |  |  |

| 4.4         | Calcul des pires temps de réponse $RT_{3,2}$          |  |  |  |  |  |  |

| <b>A.</b> 1 | Principales caractéristiques du MPC555                |  |  |  |  |  |  |

| A.2         | Principales caractéristiques du dsPIC33FJ128MC708 186 |  |  |  |  |  |  |

# Introduction générale

#### **Contexte**

Les applications de robotique mobile sont de plus en plus complexes car d'une part elles font intervenir des algorithmes de traitement du signal et des images ainsi que des algorithmes de commande tous les deux multipériodes, et d'autre part elles sont soumises à des contraintes temps réel dures. Ces applications doivent, pour des raisons de modularité, de puissance de calcul et de tolérance aux fautes, être implantées sur des architectures distribuées hétérogènes formées de plusieurs processeurs et média de communication, tous les deux éventuellement de type différents. Il existe des solutions théoriques et un outil logiciel SynDEx pour résoudre ce problème de conception et d'implantation dans le cas monopériode sur une architecture distribuée. Cependant le code généré par SynDEx monopériode tolérant aux fautes, n'a jamais été testé sur une véritable architecture distribuée. Par ailleurs cette thèse a été réalisée dans le cadre d'une collaboration entre les équipes-projets AOSTE et IMARA, cette dernière ayant développé une architecture matérielle distribuée à base de microcontrôleurs MPC555 et de bus de communication CAN pour leur véhicule électrique appelé CyCab. Une application de suivi de CyCab a été développée et testée avec une version de SynDEx multipériode non tolérante aux fautes.

# **Objectif**

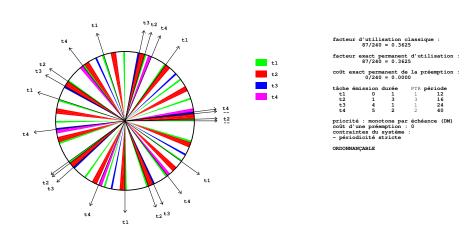

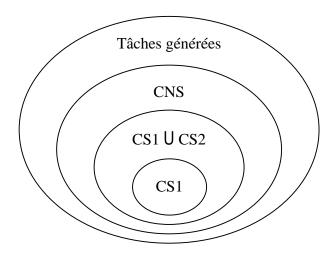

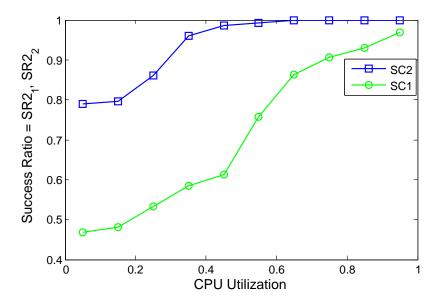

Il existait deux versions de SynDEx : l'une monopériode tolérante aux fautes mais qui n'avait jamais été testée sur une véritable architecture, et l'autre multipériode non tolérante aux fautes qui avait été testée sur le CyCab, nous avons choisi de fonder nos travaux sur la version multipériode non tolérante aux fautes pour la rendre tolérante aux fautes. Cependant SynDEx multipériode ordonnance les tâches non préemptives à périodes strictes selon une condition d'ordonnançabilité très restrictive, i.e. elle donne un faible taux de succès d'ordonnancement. Donc le premier objectif visé a été de proposer des nouvelles conditions d'ordonnançabilité donnant de meilleurs taux de succès. Le deuxième objectif a été d'étudier séparément les tâches harmoniques ayant toutes des périodes multiples les unes

des autres, et les tâches non harmoniques. En effet les tâches harmoniques ont de meilleurs taux de succès d'ordonnancement que les tâches non harmoniques. Le troisième objectif a été de garder certaines tâches non préemptives périodiques strictes et d'y ajouter des tâches préemptives périodiques non strictes afin d'améliorer le taux de succès d'ordonnancement. Le quatrième objectif a été d'étendre les résultats d'ordonnancement pour rendre ces systèmes tolérants aux fautes matérielles des processeurs et des média de communication. L'objectif final consiste à intégrer tous ces travaux dans le logiciel SynDEx et de les tester sur une sur une application de contrôle/commande robotique fonctionnant sur le CyCab.

# Plan général de la thèse

Ce manuscrit est constitué de quatre parties chacune d'elles comportant deux chapitres.

La première partie est consacrée à l'état de l'art. Nous proposons dans le premier chapitre un état de l'art sur l'ordonnancement temps réel embarqué et dans le deuxième chapitre un état de l'art sur la tolérance aux fautes.

La deuxième partie est consacrée à l'ordonnancement temps réel monopériode. Nous proposons dans le troisième chapitre une analyse d'ordonnançabilité de tâches non-préemptives périodiques strictes dans le cas des tâches harmoniques et des tâches non harmoniques. Cette étude est ensuite étendue dans le quatrième chapitre pour prendre en compte des mélanges de tâches non préemptives périodiques strictes et de tâches préemptives périodiques strictes.

La troisième partie est consacrée à l'ordonnancement multiprocesseur. Comme nous utilisons une approche d'ordonnancement partitionnée qui transforme le problème d'ordonnancement multiprocesseur en plusieurs problèmes d'ordonnancement monoprocesseur, nous exploitons, dans le cinquième chapitre les résultats d'ordonnancement monoprocesseur obtenus dans la partie précédentes pour proposer des algorithmes d'ordonnancement multiprocesseurs. Ces résultats sont ensuite étendus dans le septième chapitre pour tolérer les fautes de processeurs et de média de communications.

La dernière partie est consacrée aux développements logiciels et à l'application de suivi automatique de véhicules électriques CyCabs. Nous présentons dans le septième chapitre les améliorations apportées au logiciel SynDEx et dans le huitième chapitre l'applications de suivi automatique de CyCabs tolérante aux fautes.

Il y a aussi trois annexes : la première donne les caractéristiques du CyCab en particulier celles des processeurs et du bus de communication qu'il utilise, la deuxième présente le code source généré par SynDEx pour les microntrôleurs dsPICs, et la dernière donne les programme sources tolérants aux fautes.

Première partie État de l'art

# Chapitre 1

# Ordonnancement des systèmes temps réel embarqués

# 1.1 Systèmes temps réel embarqués

Les applications qui nous intéressent dans cette thèse sont temps réel et aussi embarquées. Pour celà, nous devons prendre en considération les caractéristiques de ces systèmes dans les différents travaux que nous menons.

### 1.1.1 Caractéristiques

Un système embarqué ("embedded system" en anglais) est un système intégré dans un système plus large avec lequel il est interfacé, et pour lequel il réalise des fonctions particulières (contrôle/commande de procédés, surveillance, communication) spécifiant l'application concernée. Beaucoup de systèmes embarqués sont temps réel car d'une part ils doivent interagir infiniment avec leur environnement (le monde physique), et d'autre part ils doivent prendre des décisions et/ou effectuer des calculs en respectant des contraintes temporelles.

## 1.1.2 Architecture des systèmes embarqués

Un système embarqué comporte une partie matérielle formée d'un ensemble d'éléments physiques : processeur(s), mémoire(s) et entrées/sorties, une partie logicielle qui consiste en des programmes, et une source d'énergie. Les systèmes embarqués nécessitent parfois d'utiliser plusieurs processeurs pouvant être de types différents. Un premier classement des architectures pour système embarqué dépend du nombre de processeurs : architecture monoprocesseur ou multiprocesseur. Il existe différents classements pour les architectures multiprocesseurs :

- homogène/hétérogène selon la *nature des processeurs* de l'architecture :

- identiques : les processeurs sont interchangeables et ont la même puissance de calcul;

- uniformes : chaque processeur est caractérisé par sa puissance de calcul avec l'interprétation suivante : lorsqu'un travail s'exécute sur un processeur de puissance de calcul s pendant t unités de temps, il réalise  $s \times t$  unités de travail ;

- indépendants : un taux d'exécution  $r_{i,j}$  est associé à chaque couple travail-processeur  $(J_i, P_j)$ , avec l'interprétation suivante : le travail ; le travail  $J_i$  réalise  $(r_{i,j} \times t)$  unités de travail lorsqu'il s'exécute sur le processeur  $P_j$  pendant t unités de temps. Dès lors la vitesse de progression sur un même processeur varie éventuellement d'un travail à l'autre ;

- homogène/hétérogène selon la nature des communications entre processeurs :

- homogène : les coûts de communication entre chaque paire de processeurs de l'architecture sont toujours les mêmes;

- hétérogène : les coût de communication entre processeurs varient d'une paire de processeurs à une autre ;

- parallèle/distribuée selon le type de mémoire de l'architecture :

- parallèle : les processeurs communiquent par mémoire partagée ;

- distribuée : les processeurs ne partagent pas de mémoire et ont leur propre mémoire qui est ainsi dite distribuée. Ils communiquent par envoi/réception de messages.

#### 1.1.3 contraintes des systèmes temps réel embarqués

Nous distinguons deux types de contraintes : les contraintes temporelles et les contraintes matérielles.

#### 1.1.3.1 contraintes temporelles

Les systèmes temps réel peuvent avoir deux types de contraintes temporelles : contraintes strictes (dures) et contraintes souples. Un système temps réel est dit à contraintes strictes quand une faute temporelle (non respect d'une échéance, arrivée d'un message après les délais, irrégularité d'une période d'échantillonnage, dispersion temporelle trop grande dans un lot de mesures simultanées) peut avoir des conséquences catastrophiques du point de vue humain, économique ou écologique. Un système temps réel est à contraintes souples lorsque le non respect de contraintes temporelles est acceptable. On admet alors de ne pas respecter certain pourcentage d'échéances par exemple. On parle alors de qualité de service (QoS).

Dans les applications de contrôle/commande temps réel critiques, les traitements de capteurs/actionneurs et les traitements de commande de procédés ne doivent pas avoir de gigue sur les entrées issues des capteurs et sur les sorties fournies aux actionneurs. Dans un tel système, une faute temporelle peut avoir des conséquences catastrophiques autant ou plus qu'une faute de calcul.

#### 1.1.3.2 contraintes matérielles

Ces contraintes sont dues aux restrictions de ressources dans les systèmes embarqués. La puissance de calcul et la mémoire de ces systèmes sont limitées. Cela est dû aux limitations de poids, de volume (avions), de consommation d'énergie (véhicules), ou de prix. Parmi ces différentes contraintes, la gestion de la mémoire et la consommations sont les principales contraintes étudiées dans la littérature.

L'accès aux mémoires reste toujours plus lent comparé à la vitesse des processeurs qui ne cesse de croître. Bien que la capacité mémoire dans les systèmes embarqués augmente, elle reste toujours insuffisante pour des applications qui deviennent de plus en plus complexes. Les premières techniques de gestion de la mémoire étaient manuelles comme la réservation de mémoire (instruction "malloc" en langage C) et comme la restitution de mémoire (instruction "free" en langage C). Des techniques automatiques où l'intervention de l'utilisateur est (quasi) nulle ont été introduites plus tard. Ces techniques restent plus complexes à mettre en œuvre.

La complexité des systèmes embarqués ne cesse d'augmenter, ce qui engendre des consommations d'énergie de plus en plus élevées. La consommation d'énergie est un paramètre essentiel dans le développement des applications embarquées. L'utilisation de processeurs puissants cadencés à des fréquences élevées génère des consommations d'énergie élevées [Koc00]. Une technique importante de minimisation de la consommation d'énergie est basée sur la minimisation du "makespan" qui correspond au temps total d'exécution des tâches [LL08], afin d'utiliser des processeurs moins puissants pour avoir les mêmes résultats obtenus avec des processeurs puissants et qui consomment plus d'énergie [Ven06, Par02, Gar05, Koc00].

# 1.2 Ordonnancement de tâches temps réel

Dans la suite on présente les modèles de tâches qui nous intéressent et les contraintes temporelles qu'on peut y appliquer, puis on présente les différents algorithmes monoprocesseurs et multiprocesseurs capables d'ordonnancer ces tâches.

#### 1.2.1 Tâches temps réel

Une tâche temps réel est une séquence d'instructions constituant l'unité de base d'un système temps réel. Les tâches réalisent des entrées/sorties et des calculs permettant de commander des procédés via un ensemble de capteurs et d'actionneurs, éventuellement tout ou rien, par exemple ensemble de tâches réalisant le contrôleur de vitesse d'une voiture ou le pilotage automatique d'un avion. Elles sont soumises à des contraintes temporelles qui doivent être respectées. Par exemple il faut désactiver avant un certain temps le contrôleur de vitesse d'une voiture lorsqu'on actionne les freins.

On suppose que les caractéristiques temporelles sont des entiers non négatifs multiples d'unité de temps en général égale à la période de l'horloge du processeur.

Les tâches *périodiques* se répètent indéfiniment et leurs instances sont séparées par une période constante. Une tâche périodique est activée par le déclenchement d'une interruption produite par un timer externe, à une date appelée date d'activation. Chaque instance s'exécute pendant une durée d'exécution maximale et doit terminer son exécution avant une échéance relative à sa date d'activation. Une tâche périodique est représentée par quatre paramètres : une date d'activation, un temps d'exécution maximum (pire cas), une échéance relative et une période.

Les tâches *apériodiques* doivent s'exécuter au moins une fois et ne se répètent pas nécessairement indéfiniment. Une tâche apériodique est représentée par trois paramètres : une date d'activation, un temps d'exécution maximum et une échéance relative à sa date d'activation. Différents procédés d'ordonnancement de tâches apériodiques d'un système temps réel sont exposés dans [SSL89].

Les tâches *sporadiques* sont un cas particulier de tâches apériodiques. Ce sont des tâches qui se répètent indéfiniment avec une période minimum. En d'autres termes, deux instances peuvent être séparées d'une valeur plus grande que cette période minimum. Une tâche sporadique est représentée par quatre paramètres : une date d'activation, un temps d'exécution maximum, une échéance relative à sa date d'activation et une durée minimum entre deux activations successives de la tâche.

#### 1.2.1.1 Modèles de tâches

Comme par la suite nous nous intéresserons aux systèmes de tâches temps réel périodiques, nous introduisons d'abord le modèle classique habituellement cité dans la littérature et nous introduisons par la suite le modèle de tâches non préemptives périodiques strictes que nous utilisons dans nos travaux.

#### Modèle classique de tâches préemptives périodiques

Un modèle canonique de tâches temps réel préemptives périodiques a été proposé par Liu & Layland [LL73]. Ce modèle regroupe les principaux paramètres temporels qui permettent de caractériser une tâches temps réel et son ordonnancement. Ces paramètres sont scindés en deux groupes : paramètres statiques et paramètres dynamiques.

Afin d'alléger la lecture, les tâches préemptives périodiques (non strictes) sont notées tâches PP dans la suite du manuscrit.

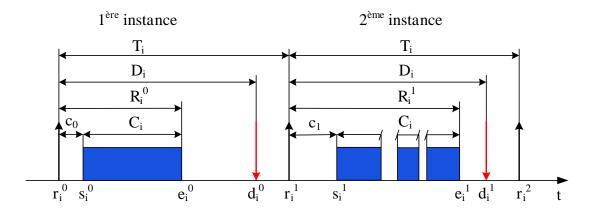

Les paramètres de base d'une tâche  $\tau_i(r_i^0,C_i,D_i,T_i)$  sont :

- $-\ r_i^0\ ({\it first\ release}\ {\it ou\ offset})$  : première date de réveil ou d'activation, qui représente le moment de déclenchement de la première requête d'exécution,

- $-C_i$  (computing time): durée d'exécution maximale d'une tâche, souvent considéré comme le pire temps d'exécution WCET (Worst Case Execution Time), qui est une borne supérieure du temps d'exécution d'une tâche sur un processeur donné,

- D<sub>i</sub> (relative deadline): échéance relative, date au plus tard ou délai critique, ce paramètre représente le délai, relativement à la date d'activation, avant laquelle l'exécution de la tâche doit être terminée,

- $-T_i$  (period): période d'exécution d'une tâche périodique ou écart minimum entre deux activations successives d'une tâche apériodique.

Notez que pour la  $k^{me}$  instance  $\tau_i^k$ , la date d'activation (release time, request time, ready time) est donnée par  $r_i^k = r_i^0 + k \cdot T_i$ .

Lorsque la période d'une tâche est égale à son échéance, on dit que la tâche est à échéance sur requête.

D'autres paramètres sont dérivés des paramètres de base :

- $\begin{array}{l} -\ U_i = \frac{C_i}{T_i}\ (\textit{utilization factor}) : \text{facteur d'utilisation d'une tâche}\ ; \ \text{on a}\ U_i \leq 1, \\ -\ CH_i = \frac{C_i}{D_i}\ (\textit{density}) : \text{densit\'e}\ d'une\ tâche}\ ; \ \text{on a}\ CH_i \leq 1. \end{array}$

Les paramètres dynamiques servent à suivre le comportement de l'exécution d'une tâche:

- $-s_i^k$  (start time) : date de début d'exécution de la  $k^{me}$  instance  $\tau_i^k$ ,  $-e_i^k$  (end time) : date de la fin d'exécution de la  $k^{me}$  instance  $\tau_i^k$ ,  $-d_i^k$  (absolute deadline) : échéance absolue de la  $k^{me}$  instance  $\tau_i^k$  donnée par  $d_i^k = r_i^k + D_i = r_i^0 + k \cdot T_i + D_i,$

- $-R_i^k$  (response time) : temps de réponse de la  $k^{me}$  instance  $\tau_i^k$  donné par  $e_i^k - r_i^k$ . On a  $C_i \leq R_i^k \leq D_i$ ,

- $-L_i$  (laxity) : laxité nominale d'une tâche qui représente le retard maximum pour son début d'exécution  $s_i^k$  lorsque cette tâche est exécutée seule.

La figure 1.1 représente un modèle canonique d'une tâche périodique où l'on peut voir deux instances dont la deuxième est préemptée deux fois.

FIGURE 1.1 – Modèle classique d'une tâche PP  $\tau_i(r_i^0, C_i, D_i, T_i)$

#### Modèle de tâches non préemptives périodiques strictes

Dans les applications de contrôle/commande temps réel critiques, les tâches réalisant les entrées/sorties ne doivent pas avoir de gigue. Donc pour éviter la gigue sur les entrées issues des capteurs les tâches les gérant doivent être périodiques strictes, et pour éviter la gigue sur les sorties fournies aux actionneurs les tâches les gérant doivent être non préemptives.

Le modèle de tâches à non préemptives périodiques strictes est le modèle naturel utilisé pour faire de l'ordonnancement sans préemption qui a existé bien avant celui préemptif dit de Liu & Layland décrit précédemment. Dans ce dernier la différence entre la date d'activation et la date de début d'exécution peut varier alors qu'elle est constante dans le cas de tâches non préemptives périodiques strictes. Ce qui revient à dire qu'il n'y a pas de gigue [CS03]. De plus il a le gros avantage d'être déterministe car il ne dépend pas de *l'approximation du coût de l'OS* définie par Liu & Layland [LL73], nécessaire pour gérer la préemption. Cet avantage est utile dans le cas des applications temps réel critiques citées plus haut.

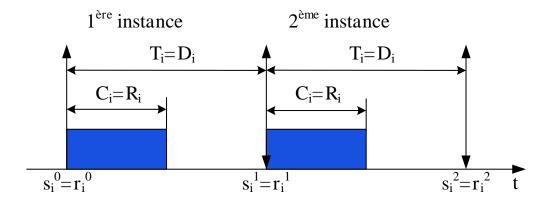

Afin d'alléger la lecture, les tâches non préemptives périodiques strictes sont notées tâches *NPPS* dans la suite du manuscrit.

Ce modèle a les caractéristiques suivantes :

- la différence entre la date d'activation et la date de début d'exécution d'une instance  $\tau_i^k$  est égale à une constante :  $s_i^k r_i^k = d$ ,

- le temps de réponse est constant :  $R_i = C_i + d$ ,

- la différence entre deux dates de début d'exécution successives est égale à la période :  $s_i^{k+1}-s_i^k=T_i$ ,

- l'échéance est égale à la période :  $T_i = D_i$ ,

La figure 1.2 représente un modèle de tâches NPPS dans le cas où d=0. Dans la suite du manuscrit et sans perte de généralité nous ferons cette hypothèse.

FIGURE 1.2 – Modèle d'une tâche NPPS  $\tau_i(C_i, T_i)$

#### 1.2.1.2 contraintes temps réel

Parmi les contraintes temporelles traitées dans cette thèse on retrouve les contraintes suivantes :

#### **Echéance**

La contrainte d'échéance exprime une condition sur la date de fin au plus tard de chacune des tâches du système. On distingue trois types d'échéances :

- 1.  $D_i = T_i$ : ce cas représente les tâches à échéance sur requête, où chaque activation d'une tâche doit être exécutée avant la prochaine requête de la même tâche.

- 2.  $D_i \leq T_i$ : chaque activation d'une tâche doit être exécutée avant une date inférieure ou égale à la prochaine date d'activation de la même tâche.

- 3.  $D_i \leq T_i$  ou  $D_i \geq T_i$ : la date de fin d'exécution d'une tâche peut être inférieure, égale ou supérieure à sa période.

#### Précédence et dépendance

On parle de précédence et de dépendance quand il y a une interaction entre les tâches. Une précédence désigne un ordre partiel d'exécution des tâches [MBFSV07,

Cuc04] sans qu'il y ait transfert de données entre ces tâches. Deux tâches sont dépendantes si une tâche produit des données et l'autre tâche les consomme. La tâche réceptrice, appelée successeur, ne peut s'exécuter avant la réception de données de la tâche émettrice appelée prédécesseur. Une dépendance impose une précédence entre la tâche qui produit une donnée et la tâche qui la consomme. Les tâches sont dites indépendantes lorsqu'elles ne sont définies que par leurs paramètres temporels.

Dans la suite du manuscrit quand on parle d'ordonnancement on sous-entend ordonnancement temps réel.

#### Gigue

L'exécution de requêtes périodiques est parfois soumise à des contraintes de régularité pour le début de leurs exécutions ou pour leurs temps de réponse. La variation entre le début d'exécution de deux instances successives est appelée gigue de début d'exécution (gigue sur les entrées). La variation entre le temps de réponse de deux instances successives est appelée gigue de temps de réponse (gigue sur les sorties).

#### 1.2.2 Typologie des algorithmes d'ordonnancement

Étant donné un algorithme d'ordonnancement, une condition d'ordonnançabilité permet de déterminer s'il existe un ordonnancement qui satisfait toutes les contraintes des tâches. En revanche une condition de faisabilité permet de déterminer s'il existe un ordonnancement qui satisfait toutes les contraintes des tâches. Donc un ensemble de tâches est faisable s'il existe une condition de faisabilité qui est satisfaite par cet ensemble.

Un algorithme d'ordonnancement est dit *hors ligne* s'il construit la séquence d'ordonnancement complète à partir des paramètres temporels de l'ensemble des tâches avant l'exécution de l'application. Cela convient bien aux systèmes de tâches périodiques. Il est dit *en ligne* s'il construit la séquence d'ordonnancement à partir des paramètres temporels de l'ensemble des tâches pendant l'exécution de l'application. Les algorithmes en ligne sont plus robustes vis-à-vis des dépassements des WCETs. Cela convient bien aux systèmes de tâches sporadiques et apériodiques.

Un algorithme d'ordonnancement est dit *optimal* si tout ensemble de tâches faisable, est ordonnançable avec cet algorithme. En d'autres termes un algorithme d'ordonnancement est optimal si lorsqu'un ensemble de tâches est ordonnançable alors l'algorithme optimal conclut qu'il est ordonnançable.

Un algorithme d'ordonnancement est dit *monoprocesseur* s'il n'ordonnance l'ensemble des tâches que sur un seul processeur. Il est dit *multiprocesseur* s'il

ordonnance l'ensemble des tâches sur plusieurs processeurs.

Un algorithme d'ordonnancement est dit *préemptif* s'il exploite la préemption des tâches, i.e. s'il permet qu'une tâche s'exécutant soit interrompue par une autre tâche plus prioritaire. Il est dit *non préemptif* s'il n'utilise pas la préemption des tâches.

#### 1.2.3 Algorithmes d'ordonnancement monoprocesseur

Nous présentons dans cette partie les différents types d'algorithmes d'ordonnancement monoprocesseur que l'on trouve dans la littérature. Nous commençons d'abord par présenter les algorithmes d'ordonnancement pour des tâches PP, puis nous nous focaliserons sur les algorithmes d'ordonnancement des tâches NPPS.

#### 1.2.3.1 Préemptifs périodiques, apériodiques et sporadiques

Dans cette catégorie d'algorithmes d'ordonnancement, nous distinguons les algorithmes à priorité statique (fixe) et ceux à priorité dynamique (variable).

#### Priorité statique (fixe)

Pour ce type d'algorithmes, la priorité d'une tâche est fixée avant son exécution et elle est la même pour toutes ses activations. Les algorithmes RM et DM décrits ci-dessous sont de ce type.

#### **RM** (Rate Monotonic)

L'algorithme à priorité fixe Rate Monotonic a été introduit par liu et layland en 1973 [LL73]. Il s'agit d'un ordonnancement préemptif à priorité statique qui s'applique à un ensemble de tâches périodiques indépendantes, et à échéance sur requête. Les priorités sont inversement proportionnelles aux périodes des tâches, i.e. la tâche la plus prioritaire est celle ayant la plus petite période.

**Propriété 1.1** L'algorithme RM est optimal pour l'ordonnancement de tâches préemptives, périodiques, indépendantes, à premières dates d'activation simultanés et à échéance sur requête.

Remarque 1.1 On appelle souvent scénario synchrone le cas particulier où les première dates d'activation des tâches sont simultanées. Ces tâches sont dites concrètes. Les tâches qui n'ont pas cette particularité sont dites non concrètes.

Pour les tâches apériodiques et sporadiques, l'algorithme RM n'est plus optimal.

La condition suffisante d'ordonnançabilité avec l'algorithme RM pour un système de n tâches est donnée par [LL73] :

$$\sum_{i=1}^{i=n} \frac{C_i}{T_i} \le n(2^{\frac{1}{n}} - 1)$$

Joseph et Pandya ont proposé par la suite une condition de faisabilité nécessaire et suffisante basée sur le calcul du temps de réponse  $RT(\tau_i)$  (Response Time) [Jos85]. Elle montre que si un ensemble de tâches périodiques triées par priorités décroissantes est ordonnancé par RM et dont le temps de réponse  $RT(\tau_i)$  d'une tâche  $\tau_i$  est borné supérieurement par la solution de l'équation

$$RT(\tau_i)^{q+1} = \sum_{i=1}^{i-1} \left\lceil \frac{RT(\tau_i)^q}{T_j} \right\rceil \cdot C_j + C_i$$

alors l'ordonnancement de cet ensemble est faisable si et seulement si :  $\forall i = 1..n, RT(\tau_i) \leq T_i$ . Cette équation peut être résolue récursivement où  $\lceil x \rceil$  est la partie entière supérieure de x.

#### **DM** (Deadline Monotonic)

Cet algorithme a été introduit par Leung et Whitehead en 1982 [LW82]. Contrairement à l'algorithmes RM qui est basé sur les périodes des tâches, DM est basé les échéances relatives des tâches. Les priorités des tâches sont inversement proportionnelles aux échéances relatives des tâches où  $T(\tau_i) \geq D_i \geq C_i$ . La tâche la plus prioritaire est celle ayant la plus petite échéance relative.

**Propriété 1.2** L'algorithme DM est optimal pour l'ordonnancement de tâches préemptives, périodiques, indépendantes, à premières dates d'activation simultanés et à échéances contraintes  $D_i \leq T_i$ .

Pour les tâches apériodiques et sporadiques, l'algorithme DM n'est plus optimal. La condition suffisante d'ordonnançabilité de n tâches périodiques (triées par priorités décroissantes)  $\{\tau_1,...,\tau_i,...,\tau_n\}$  avec DM basée sur la densité est :

$$\sum_{i=1}^{n} \frac{C_i}{D_i} \le n(2^{1/n} - 1)$$

De la même manière que pour RM, il existe une condition nécessaire et suffisante pour l'algorithme DM. Si un ensemble de tâches périodiques triées par priorités décroissantes est ordonnancé par DM et dont le temps de réponse  $RT(\tau_i)$  d'une tâche  $\tau_i$  est borné supérieurement par la solution de

$$RT(\tau_i)^{q+1} = \left(\sum_{i=1}^{i-1} \left\lceil \frac{RT(\tau_i)^q}{T_j} \right\rceil . C_j\right) + C_i$$

alors l'ordonnancement de cet ensemble est faisable si et seulement si :  $\forall i_{(1 \leq i \leq n)} \ RT(\tau_i) \leq D_i$ .

À noter que si toutes les tâches sont à échéance sur requête, RM et DM sont équivalents.

#### Priorité dynamique (variable)

Pour cette catégorie d'algorithmes d'ordonnancement, la priorité d'une tâche est définie pour chaque activation de cette tâche.

#### **EDF** (Earliest Deadline First)

Cet algorithme a été présenté par Jackson en 1955 [Jac55] puis par Liu et Layland en 1973 [LL73]. C'est un ordonnancement qui peut être préemptif ou non préemptif et est à priorité dynamique. Il s'applique à des tâches périodiques indépendantes et à échéance sur requête. Le principe d'allocation de priorités dans cet algorithme est que la tâche dont l'échéance absolue arrive le plus tôt aura la priorité la plus élevée. Les priorités sont réévaluées à chaque fois que l'ordonnanceur doit déterminer la prochaine tâche à exécuter. Par exemple lorsqu'une nouvelle tâche est activée et que son échéance est la plus proche comparée à celles des autres tâches prêtes à être exécutées.

**Propriété 1.3** L'algorithme EDF est optimal pour l'ordonnancement de tâches préemptives et indépendantes [Der74].

La condition nécessaire et suffisante d'ordonnançabilité dans le cas préemptif  $\forall i: D_i = T_i$  (échéance sur requête) est :

$$\sum_{i=1}^{i=n} \frac{C_i}{T_i} \le 1$$

#### **LLF** (Least-Laxity First)

Cet algorithme se base sur la laxité. LLF a été introduit par Mok et Dertouzos [Mok83b, MD78]. À chaque invocation, LLF élit la tâche dont la laxité est la plus faible. L'ouvrage [CDKM00] montre que les conditions d'ordonnançabilité pour l'algorithme LLF sont les mêmes que pour EDF, c'est-à-dire que la condition

nécessaire et suffisante d'ordonnançabilité dans le cas préemptif si  $\forall i: D_i = T_i$  est :

$$\sum_{i=1}^{i=n} \frac{C_i}{T_i} \le 1$$

**Propriété 1.4** L'algorithme LLF est optimal pour l'ordonnancement de tâches préemptives, indépendantes et avec des échéances relatives inférieures ou égales aux périodes [DM89, Mok83a].

L'algorithme LLF présente l'inconvénient, lorsque plusieurs tâches possèdent la même laxité, d'engendrer un grand nombre de préemptions donc de changements de contexte ce qui explique qu'il soit aussi peu utilisé dans le cas monoprocesseur [Bim07].

#### 1.2.3.2 Non préemptifs périodiques stricts

Les problèmes d'ordonnancement non préemptifs ont reçu moins d'attention dans le domaine de l'ordonnancement temps réel. En effet, comme vu précédemment il existe beaucoup de conditions d'ordonnançabilité dans le cas préemptif. Malheureusement elles deviennent, dans le meilleur des cas, des conditions nécessaires (non suffisantes) [GRS96] dans le cas non préemptif.

Les problèmes d'ordonnancement monoprocesseur non préemptifs sont NP-difficiles au sens fort, comme Jeffay, Stanat et Martel l'ont démontré [JSM91]. Baruah a proposé dans [Bar98] un modèle de tâches récurrentes, qui est plus général que le modèle de tâches périodiques et non périodiques. Baruah et Chakraborty ont proposé dans [BC06] une condition d'ordonnançabilité nécessaire et suffisante de ce type de tâches, et ont montré qu'il existe des algorithmes en temps polynomial pour les ordonnancements préemptifs et non préemptifs.

Une analyse d'ordonnançabilité des tâches non préemptives périodiques non strictes a été effectuée par George, Rivierre, and Spuri [GRS96]. Ils ont prouvé dans le scénario synchrone que pour n'importe quel ensemble de tâches non préemptives  $\{\tau_1,...,\tau_i,...,\tau_n\}$  tel que  $\sum_{i=1}^{i=n}\frac{C_i}{T_i}\leq 1$  est ordonnançable en utilisant EDF si et seulement si  $\rho$  est un instant donné dans le scénario synchrone de l'exécution tel que  $\not\exists i:D_i>\rho$  alors :

$$\forall \rho \in \mathbb{S}, \ \rho \ge h(\rho)$$

Avec:

$$-\mathbb{S} = \bigcup_{i=1}^{n} \{kT_i + D_i, k \in \mathbb{N}\} \cap [0, L[,$$

-h la demande processeur qui représente la durée cumulée d'exécution des tâches qui arrivent et ont leurs l'échéances dans l'intervalle [0,t[,

— L la plus longue période d'activité du processeur obtenue dans le scénario synchrone (toutes les tâches démarrent en 0).

La principale différence entre les travaux précédents et ceux que nous proposons dans cette thèse réside dans la définition des périodes qui pour nous sont strictes.

Nous rappelons que dans le cas d'une période stricte la différence entre deux dates d'activation successives est constante et la différence entre deux dates de début d'exécution est aussi constante, et la différence entre une date d'activation et une date de début d'exécution est constante. En revanche dans le modèle classique de tâches la période est telle que la différence entre deux dates d'activation successives est constante, mais celle entre deux dates de début d'exécution peut varier.

Il existe des travaux sur l'ordonnancement monoprocesseur de tâches NPPS. Cucu et al. [CS03] ont étendu les travaux de George et al. [GRS96] dans deux directions : la première lorsque des tâches NPPS ont des précédences, et la deuxième lorsque plusieurs paires de tâches ont des contraintes de latence [CPS07]. Ces multiples contraintes de latence aussi appelées contraintes de bout-en-bout (end-to-end). Les deux types de contraintes peuvent être mélangées. Korst et al. ont proposé dans [KALW91] une condition d'ordonnançabilité nécessaire et suffisante par deux tâches NPPS. Cette condition devient une condition suffisante dans le cas de plus de deux tâches, comme l'avait prouvé Kermia et al. dans [KS08]. Cependant, comme nous l'avons mentionné dans [MS10], cette condition est très restrictive (pessimiste). Eisenbrand et al. ont proposé dans [EHN+10b] un algorithme d'ordonnancement des tâches harmoniques et non harmoniques, sans donner de conditions d'ordonnançabilités.

Il existe des travaux sur l'ordonnancement multiprocesseur de tâches NPPS. Kermia et al. ont donné dans [KS07] des solutions approchées avec des heuristiques pour l'ordonnancement de tâches NPPS pour des architectures multiprocesseurs hétérogènes. Al Sheikh et al. ont donné dans [ASBH10] des solutions exactes avec la programmation linéaire en nombres entiers pour l'ordonnancement multiprocesseur de tâches NPPS pour des plates-formes IMA (Integrated Modular Avionics).

## 1.2.4 Algorithmes d'ordonnancement multiprocesseur

Nous avons à ordonnancer un ensemble  $\Gamma$  de n tâches périodiques (ou sporadiques) sur une architecture multiprocesseur composée de m processeurs. Ce problème a été formulé pour la première fois par Liu en 1969 [Liu69].

On distingue trois approches d'ordonnancement multiprocesseur : globale, partitionné et semi-partitionné.

#### 1.2.4.1 Approche globale

Il s'agit d'appliquer sur l'ensemble des processeurs une stratégie d'ordonnancement globalement. Ceci revient à utiliser un seul ordonnanceur pour l'ensemble des processeurs. Si le nombre de tâches n est supérieur ou égal au nombre de processeurs, les tâches les plus prioritaires sont attribuées aux m processeurs, sinon des processeurs sont laissés oisifs. Dans cette approche, outre la préemption des tâches, la migration de ces dernières est aussi autorisée. Une tâche peut donc commencer son exécution sur un processeur  $P_i$ , puis être préemptée par une tâche plus prioritaire, pour reprendre son exécution sur un autre processeur  $P_j$ , avec  $i \neq j$ . Ce phénomène est appelé la migration de tâche et est une caractéristique des approches globales.

Hong et Leung ont démontré dans [HL92a] qu'il n'existe aucun algorithme d'ordonnancement en-ligne optimal pour des systèmes de tâches avec au moins deux échéances distinctes. Ce résultat n'est plus valable dans le cas où toutes les tâches ont une échéance commune [HL92b].

Phillips, Stein, Torng and Wein [PSTW97] ont étudié la manière dont un algorithme en ligne peut se comporter si l'on augmente la vitesse des processeurs. Ainsi un système de tâches qui est ordonnançable sur m processeurs identiques, est ordonnançable avec EDF sur m processeurs identiques mais ayant une vitesse  $(2-\frac{1}{m})$  fois plus grande que la vitesse initiale.

Contrairement aux algorithmes d'ordonnancement monoprocesseurs, les algorithmes multiprocesseurs présentent des anomalies. En effet certaines modifications des paramètres des tâches qui paraissent intuitivement positives, peuvent rendre non ordonnançables un système de tâches ordonnançables. Par exemple pour un système de tâches ordonnançables, en diminuant le facteur d'utilisation d'une tâche en augmentant sa période ou en diminuant sa durée d'exécution, on s'attendrait à avoir encore un système de tâches ordonnançables alors que parfois ce n'est pas vrai.

Par ailleurs un système de tâches périodiques ordonnançables en monoprocesseur reste ordonnançable si ces tâches sont maintenant sporadiques. Cette propriété n'est pas valable en multiprocesseur.

Parmi les algorithmes d'ordonnancement global, PFAIR est le plus connu. Baruah et al. ont établi dans [BCPV96] les fondements théoriques pour les algorithmes PFAIR et plus particulièrement la notion de "proportionate fairness". Ces algorithmes diffèrent des algorithmes classiques d'ordonnancement dans la mesure où le taux d'exécution d'une tâche est quasi constant. Lorsque l'on considère de grands intervalles de temps, le taux d'exécution d'une tâche sur un intervalle de temps est approximativement égal à son facteur d'utilisation  $U(\tau_i)$ . Cependant, sur de petits intervalles de temps, le taux d'exécution d'une tâche peut varier d'une façon très importante. Dans les algorithmes PFAIR, chaque tâche est exé-

cutée approximativement à un taux constant et ce en divisant la tâche en série de sous-tâches exécutées dans des intervalles identiques appelés fenêtres. Dans le cas particulier des architectures multiprocesseurs homogènes et des tâches périodiques à échéance sur requête, PFAIR est optimal. Il existe trois variantes de PFAIR : PF [BCPV96], PD [BGP95], PD<sup>2</sup> [And00]. La stratégie utilisée par ces algorithmes dans la manière où ils donnent des priorités aux sous-tâches est proche d'EDF.

À noter que certains algorithmes d'ordonnancement monoprocesseur comme EDF peuvent s'appliquer en ordonnancement multiprocesseur global [DP06], mais ils ne sont pas optimaux et peuvent se révéler très inefficaces (cf. effet de Dhall).

Baruah a étudié l'ordonnancement de tâches non préemptives périodiques non strictes et a proposé des conditions d'ordonnançabilité suffisantes avec l'algorithme d'ordonnancement multiprocesseur  $EDF_{np}$  selon l'approche globale [Bar06].

#### 1.2.4.2 Approche partitionnée

Il s'agit d'appliquer sur chaque processeur une stratégie d'ordonnancement qui peut être différente des autres. Cela revient à utiliser un ordonnanceur par processeur. L'ensemble des n tâches est partitionné en m sous-ensembles  $\Gamma_1, \Gamma_2, ..., \Gamma_m$ , avec  $\bigcup \Gamma_i = \Gamma$ , et chaque sous-ensemble  $\Gamma_i$  est ordonnancé sur le processeur  $P_i$ . Dans cette approche, les tâches ne sont pas autorisées à migrer d'un processeur à un autre [DB10].

Le problème qui consiste à trouver un partitionnement optimal, est équivalent à un problème de remplissage de boîtes avec des objets de tailles différentes (bin-packing) [CJG<sup>+</sup>98] en cherchant à placer le plus grand nombre d'objets possibles dans chaque boîte et en cherchant à minimiser le nombre de boîtes. Les tâches correspondent aux objets et les processeurs aux boîtes. Ce problème est NP-difficile au sens fort [GJ90]. Des algorithmes de complexité polynomiale, comme *First Fit*, *Next Fit*, *Best Fit* ou *Worst Fit* sont proposés pour le résoudre de façon approchée [BLOS95, OS95, SVC98]. Ils effectuent à la fois le choix des processeurs et la vérification d'une condition d'ordonnançabilité sur chaque processeur.

À noter que certains algorithmes d'ordonnancement monoprocesseur comme EDF peuvent s'appliquer en ordonnancement multiprocesseur partitionné [LDG01, LGDG00].

#### 1.2.4.3 Approche semi-partitionnée

L'approche semi-partitionnée est dérivée de l'approche partitionnée. Dans cette approche certaines instances d'une tâche peuvent être exécutée sur des processeurs différents, ce qui entraine des migrations moins nombreuses que dans le cas global. Certaines tâches ne sont pas autorisées à migrer.

Andersson et Tovar ont introduit dans [AT06] une approche semi-partitionnée d'ordonnancement de tâches périodiques où certaines instances de tâches peuvent être exécutées sur des processeurs différents avec une utilisation bornée. Ensuite Anderson et al. ont proposé dans [ABB08] une approche où certaines instances de tâches sporadiques peuvent être exécutées sur des processeurs différents. Dans cette approche chaque processeur  $P_i$  exécute au plus les instances de deux tâches, l'une exécutée sur le processeur  $P_i-1$  et l'autre sur le processeur  $P_i+1$ .

Kato et Yamasaki ont introduit plusieurs algorithmes Ehd2-SIP [KY07], EDDP [KY08a, KY08b] tous fondés sur l'algorithme à priorité dynamique EDF. Ils ont aussi proposé un algorithme DM-MP pour des tâches sporadiques fondé sur un algorithme à priorité fixe.

Lakshmanan et al. ont proposé l'algorithme PDMS-HPTS [LRL09] pour des tâches sporadiques fondé sur un algorithme à priorité fixe.

#### 1.3 Graphes d'algorithme et d'architecture

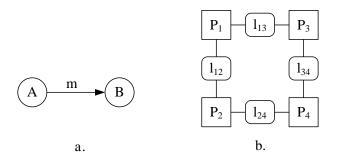

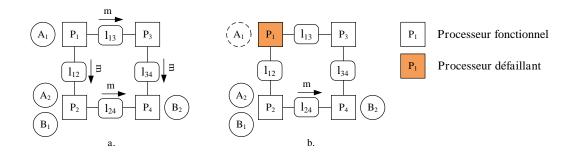

Les systèmes distribués embarqués peuvent être décrits par deux graphes : un graphe d'algorithme représentant les fonctionnalités à implanter ainsi que leurs dépendances sous la forme d'un graphe et un graphe d'architecture matérielle représentant les processeurs inter-connectés qui implantent ces fonctionnalités. On présente donc dans ce qui suit le graphe d'algorithme et le graphe d'architecture matérielle.

#### 1.3.1 Graphe d'algorithme

Dans la mesure où nous visons des systèmes distribués (parallèles, multicœur), nous avons choisi de modéliser l'algorithme par un graphe flot de données répété indéfiniment [GLS99, CKS02] bien adapté à la spécification de parallélisme potentiel pour les applications temps réel réactives. En effet l'algorithme d'un système réactif interagit de manière répétée indéfiniment avec son environnement. Une interaction est composée d'une acquisition, d'un calcul et d'une réaction (commande). Dans un graphe flot de données les sommets représentent les opérations et les arcs représentent les dépendances de données entre opérations.

**Définition 1.1** Une dépendance de données  $(o_i \triangleright o_j)$  représente la relation de précédence et un échange de données entre l'opération  $o_i$  appelée prédécesseur de  $o_j$ , et l'opération  $o_j$  appelée successeur de  $o_i$ . Elle est appelée dépendance de donnée de diffusion si elle possède une seule opération productrice et plusieurs opérations consommatrices, et elle est notée  $(o_i \triangleright ..., o_j, ...)$ .

**Définition 1.2** Une opération est une séquence finie de code.

Les opérations dans un graphe d'algorithme peuvent être des opérations de calcul ou des opérations d'entrée/sortie (opération sans prédécesseur/opération sans successeur) qui peuvent être associées à des capteurs/actionneurs.

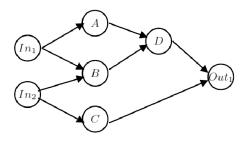

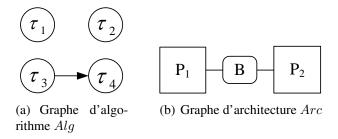

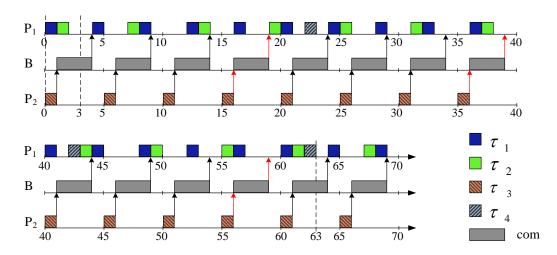

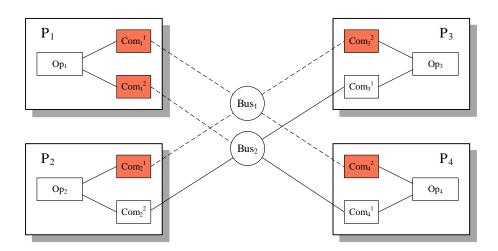

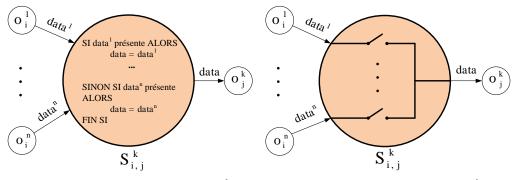

FIGURE 1.3 – Exemple d'un graphe d'algorithme.

La figure 1.3 représente un graphe d'algorithme composé de deux opérations d'entrées  $In_1$  et  $In_2$ , de quatre opérations de calcul A,B,C,D, d'une opération de sortie  $Out_1$ , de six dépendances de données  $(In_2 \triangleright B)$ ,  $(In_2 \triangleright C)$ ,  $(A \triangleright D)$ ,  $(B\triangleright D)$ ,  $(C\triangleright Out_1)$  et  $(D\triangleright Out_1)$ , et d'une dépendance de diffusion  $(In_1\triangleright \{A,B\})$ .

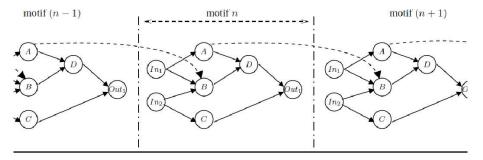

La figure 1.4 montre le graphe flot de données (motif) de la figure 1.3 répété indéfiniment pour lui permettre d'interagir avec l'environnement (procédé) qu'il commande par l'intermédiaire des opérations d'entrée/sortie.

FIGURE 1.4 – Exemple d'un graphe d'algorithme infiniment répété.

**Définition 1.3** Une opération délai se charge de mémoriser la donnée produite par une opération lors de son exécution précédente à la répétition n-1. Cette donnée sera consommée par son successeur à la répétition n. Cette opération est nécessaire pour pouvoir factoriser le graphe flot de données répété indéfiniment afin d'obtenir un graphe factorisé.

**Définition 1.4** Une opération constante conserve sa valeur durant l'exécution du système. Elle est exécutée une fois durant la première répétition et sa durée est considérée nulle.

**Définition 1.5** Un algorithme est modélisé par un graphe flot de données répété indéfiniment factorisé, appelé graphe d'algorithme. Il est représenté par le couple (O, E) où O est l'ensemble des n opérations et E est l'ensemble des m dépendances de données.

#### 1.3.2 Graphe d'architecture

Une architecture distribuée peut être constituée de composants programmables (processeurs) et de composants non programmables (ASIC : Application Specific Integrated Circuit, FPGA : Field Programmable Gate Array), inter-connectés tous ensemble. Un processeur est formé d'une machine séquentielle exécutant des instructions et d'autant de machines séquentielles de communication que de connexions possibles avec d'autres processeurs. Chacune de ces machines séquentielles de communication exécute des communications inter-processeur. Nous faisons l'hypothèse que toutes les machines séquentielles d'un processeur communiquent par une mémoire partagée interne.

Ainsi le graphe d'architecture est constitué de trois types de sommets : processeur, mémoire partagée et multiplexeur-démultiplexeur, et d'arcs qui relient ces trois types de sommets. On ne peut pas connecter deux sommets du même type. Les communications inter-processeur peuvent s'effectuer soit à travers une mémoire partagée à laquelle accèdent les machines séquentielles de communication, soit par passage de messages à travers un multiplexeur-démultiplexeur auquel accèdent les machines séquentielles de communication qui possèdent chacune une partie de la mémoire distribuée [GS03]. Dans le cas de communication par passage de messages (mémoire distribuée) on distingue deux types de multiplexeurs-démultiplexeurs : point-a-point et multipoint (bus).

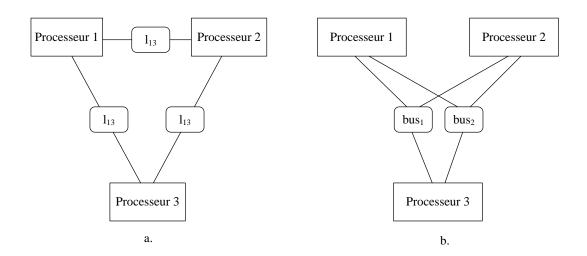

La figure 1.5a (resp. figure 1.5b) représente le graphe d'une architecture pointà-point (resp. à bus).

Remarque 1.2 Sur les graphes d'architecture le sommet de type processeur représente la machine séquentielle exécutant des instructions. Les machines séquentielles exécutant les communications inter-processeurs sont représentées par les points d'accroche des arcs de connexion. Dans le cas d'une communication par passage de message chaque point d'accroche représente une machine séquentielle de communication et une mémoire partagée et dans le cas d'une communication par mémoire partagée chaque point d'accroche représente une machine séquentielle de communication seulement.

Les opérations et les dépendances du graphe d'algorithme devront être distribuées et ordonnancées sur les processeurs et les machines séquentielles de communication de l'architecture matérielle. Pour faire cela les sommets du graphe 1.4 Conclusion 37

FIGURE 1.5 – Modèles d'architecture

d'algorithme doivent être étiquetés par des caractéristiques temporelles indépendantes de l'architecture comme la période, la période minimale, l'échéance, et des caractéristiques temporelles dépendantes de l'architecture comme le WCET, la quantité de mémoire, etc. De la même manière les dépendances de données doivent être étiquetées par des caractéristiques temporelles dépendantes de l'architecture WCCT, quantité de mémoire, etc. Les périodes des communications sont déduites de celles des opérations dépendantes. Quand les sommets et les dépendances sont étiquetés le graphe d'algorithme est un graphe de tâches temps réel.

#### 1.4 Conclusion

Dans ce chapitre nous avons présenté un état de l'art sur les systèmes temps réel embarqués. Nous avons commencé par donner des définitions concernant les architectures des systèmes embarqués ainsi que les contraintes temporelles et matérielles, puis nous avons présenté le graphe de tâches temps réels classique et celui de tâches NPPS. Ensuite nous avons présenté les différentes conditions d'ordonnançabilité et les algorithmes d'ordonnancement associés, monoprocesseur et multiprocesseur. Enfin nous avons présenté le graphe d'algorithme correspondant à la spécification de systèmes de tâches temps réel et le graphe d'architecture distribuée que nous allons utiliser dans la suite.

Dans le chapitre suivant nous présentons un état de l'art sur la tolérance aux fautes dans les systèmes temps réel embarqués.

## Chapitre 2

# Tolérance aux fautes des systèmes temps réel embarqués

#### 2.1 Introduction

Les systèmes réactifs réalisent des traitements complexes critiques et sont soumis à des contraintes strictes en terme de temps et de fiabilité. En effet, au vu des conséquences catastrophiques (perte d'argent, de temps, ou pire de vies humaines) que pourrait entraîner une faute, ces systèmes doivent être extrêmement sûrs. Pour cette raison, ils doivent mettre en oeuvre des mécanismes de tolérance aux fautes comme la redondance matérielle/logicielle [CP99, PIEP09, CSC05, IPEP05].

La majorité des méthodes existant dans la littérature pour la conception des systèmes tolérants aux fautes se concentrent sur les problèmes qui résultent de défaillances de matériel (processeurs et liens de communications). Ils supposent que la programmation (l'ensemble des traitements) est correcte et validée. Ces méthodes sont basées sur la réplication passive [QHPL00, DGLS01] ou active [Lap92] et sont vitales dans la conception de systèmes sûrs de fonctionnement appelés dans la suite *systèmes tolérants aux fautes*. La tolérance aux fautes permet à un système de continuer à délivrer un service conforme à sa spécification en présence de fautes.

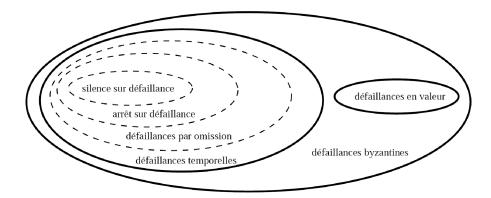

#### 2.2 Terminologies de la tolérance aux fautes