# ASIC Design Methodology for 3D NOC Based Heterogeneous Multi Processor on Chip Abir M'Zah

### ▶ To cite this version:

Abir M'Zah. ASIC Design Methodology for 3D NOC Based Heterogeneous Multi Processor on Chip. Micro and nanotechnologies/Microelectronics. Ecole Polytechnique X, 2012. English. NNT: . pastel-00769455

## HAL Id: pastel-00769455 https://pastel.hal.science/pastel-00769455

Submitted on 1 Jan 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT

En co-tutelle entre

Ecole Doctorale de l'Ecole Polytechnique

Spécialité : Physique Polytechnique

Ecole : ENSTA ParisTech U2IS-Lab

Université Tunis El Manar Spécialité : Génie Electrique

Ecole : ENIT Tunis

Présentée par :

Mme Abir M'zah Ben Nejma

Sujet

# ASIC Design Methodology for 3D NOC Based Heterogeneous Multi Processor on Chip

Soutenue le 14/12/2012 devant les membres du Jury:

M. Bernard COURTOIS, Invité, Directeur de Recherches, CMP Grenoble, France

M. Marc DURANTON, Examinateur, Docteur, CEA LIST Saclay, France

M. Omar HAMMAMI, Directeur, Professeur, ENSTA ParisTech, France

M. Jaouhar MOUINE, Co-directeur, Maître de conférences, ENIT, Tunisie

M. Smail NIAR, Rapporteur, Professeur, Université de Valencienne, France

Mme. Laurence PIERRE, Examinatrice, Professeur, Laboratoire TIMA Grenoble, France

M. Hassan RABAH, Rapporteur, Professeur, Université Henri Poincaré Nancy, France

M. Fréderic ROUSSEAU, Examinateur, Professeur, Laboratoire TIMA Grenoble, France

**3D MPSOC**

## ABSTRACT

ITRS Road Map predicts that the number of cores in the same chip will increase following an exponential curve. Insuring the interconnections between the different cores in the same chip is a real challenge when the number of components is high. The use of the NoC (Network On Chip) is a suitable solution overcoming the limitations of the classical interconnects methodologies. The regular NoC topology is costly in term of area and power consumption that is why designing an optimized architecture is a major problematic in MPSOC design. Moreover, with the semi-conductor CMOS shrinking, the interconnect delay has overcome the gate delay. In fact there is a real need to find other methodologies to continue the evolution of the chip design. 3D IC is one of the promising solutions which can reduce the interconnect delay, minimize the area of the chip and allow the use of mixed technologies. With the shortage of real 3D IC MPSOC implementation, we propose in this thesis to study the 3D design methodologies on ASIC for MPSOC architectures based on 3D NoC. Even though the NoC was proven to be an efficient solution to deal with the interconnect problems between the different cores, only few works have validated the architectures based NoC by a real implementation on FPGA/ASIC. We consider that the validation of 3D NoC by synthesis, place and route workflow is an essential step which guarantees the good functionality of the architecture before moving to 3D technology. That is why we have validated our MPSOC based 16 PEs architecture with a butterfly NoC on different FPGAs platforms. 3D IC design is facing new challenges like TSV assignment, heat dissipation and partitioning problems. That is why, in order to generate an optimized 3D NoC for a specific application and subject to the 3D Tezzaron technology, we propose in this work a new 3D NoC synthesis methodology based on MOEA. A real 3D IC design implementation of our tested and validated 3D MPSOC architecture was performed using the 3D IC Tezzaron technique. Our real case study represents a significant example proving that there is no actual 3D tool taking in consideration all the 3D IC challenges like mapping and partitioning.

Keywords: NOC, MPSOC, 3DIC, EDA tools, Validation/Verification

3

3D MPSOC

## RÉSUMÉ

La feuille de route d'ITRS prévoit que le nombre de processeurs dans la même puce va augmenter suivant une courbe exponentielle. Assurer la connexion entre les différents processeurs dans la même puce constitue un vrai défi quand le nombre des composants est important. L'utilisation d'un réseau sur puce est une solution efficace qui résout les problèmes des moyens classiques de connexion comme le bus et le point à point. Le réseau sur puce régulier coûte cher en termes de surface et d'énergie, c'est pourquoi la conception d'une architecture optimale représente une motivation majeure. En plus, avec la réduction de la taille des transistors, le temps de propagation dans les liens dépasse celui des portes logiques. En effet, il est indispensable de trouver de nouvelles techniques qui permettent de continuer le développement des circuits du semi conducteur. La conception 3D des circuits intégrés est une solution prometteuse qui peut réduire la longueur des liens, la surface de la puce et qui permet d'utiliser des technologies différentes dans la même architecture. Vu le manque d'implémentations réelles des architectures à base de multiprocesseurs avec la technique 3D, nous proposons dans cette thèse d'étudier les méthodologies de conception ASIC des architectures MPSOC à base du NoC 3D. Bien que les réseaux sur puce soient considérés comme une solution efficace pour le problème de connexions entre les processeurs, rares sont les travaux qui valident le NoC par une vraie implémentation sur FPGA/ASIC. Nous considérons que la validation d'un NoC par émulation nous permet de garantir la bonne fonctionnalité de notre architecture lors de l'implémentation en 3D. La technique de conception en 3D IC est confrontée à plusieurs problèmes comme le placement des connexions verticales, la dissipation de chaleur et le problème de partitionnement. Dans ce cadre, nous proposons dans cette thèse une nouvelle méthodologie de synthèse NoC 3D qui se base sur les algorithmes évolutionnaires. Nous avons implémenté une architecture MPSOC avec la technologie 3D de Tezzaron. Notre cas d'étude représente une architecture significative qui tient en considération les contraintes de la technologie 3D de Tezzaron.

Mots clés : NOC, MPSOC, 3DIC, EDA tools, Validation/Verification

4

## REMERCIEMENTS

Je tiens vraiment à remercier mes deux rapporteurs, Prof S. Niar et Prof H.Rabah, d'avoir accepté d'évaluer mon rapport de thèse. Je vous remercie pour le temps précieux que vous m'avez accordé. Vos remarques et votre évaluation ont très bien contribué à l'amélioration de mon manuscrit.

Je tiens à remercier tous les membres de jury d'avoir accepté de faire partie de mon comité de thèse. Je suis honorée par la participation de M.Courtois, M.Duranton, Mme Pierre et M.Rousseau dans l'évaluation de ma thèse.

Je voudrais maintenant remercier la personne que j'ai croisée dans l'accueil de l'ENSTA il y a maintenant trois ans et qui est devenu par un coup de destin inévitable mon directeur de thèse. Prof. Omar, merci de m'avoir appris des leçons pour toute ma vie. Je n'oublierai jamais mes moments de souffrance, de stress, de patience et de succès. Je vous remercie pour votre temps, pour votre énergie incroyable et pour votre confiance en moi. Je n'ai jamais croisé une personne comme vous, quand vous étiez parfois dur avec moi je regardais vos yeux très fatigués et je me disais que vous êtes plus dur avec vous-même et ça me donnait de la force pour continuer. C'était vraiment philosophique de faire une thèse avec vous.

Je tiens aussi à remercier mon co-directeur de thèse Prof. Jaouhar. Grâce à votre formation de base j'ai pu bien avancer dans mes études doctorales. Je vous remercie pour vos qualités humaines invraisemblables et pour votre support moral.

Enfin je me rappelle de tous les visages qui m'ont accompagnée pendant ma thèse. Je voudrais spécialement remercier Xinyu pour son encadrement au début de la thèse.

Khawla mon amie de thèse, je pense que tu étais mon meilleur support quand les choses allaient parfois mal tu étais là pour m'encourager et pour en discuter. Je suis très contente pour toi et pour la petite qui vient.

Thank you for Mohamed Hairol, we started the PHD together and it was a very good experience. I will always like Malaysian people because they are kind and frank like you.

Je remercie tous mes amis de l'ENSTA Isslem, Nessrine, Mazen, Ghassen, Souhir, Gangui d'avoir fait partie de ma vie à l'ENSTA.

## DEDICACES

Je dédie ce travail à mon cher mari Youssef. Je te remercie pour ton support moral merci d'avoir transformé mes larmes en rires. Je te remercie de m'avoir aidé à voir les choses simplement. Je t'ai demandé une fois de me cacher de toute cette vie mais je n'oublierai jamais ce que tu m'as dit : ° tout le monde peut arrêter, c'est très facile, mais seule une personne forte puisse continuer ". J'ai voulu toujours te voir fier de moi et j'espère que nos sacrifices portent bien leurs fruits.

Je dédie ce travail à mes chers parents. Je vous aime fort, vous êtes ma raison d'être et mon grand amour dans cette vie. Je suis désolée maman par ce que je ne t'ai pas accompagné dans ta maladie j'aurais aimé être là pour te donner de ma vie si il le faut. Cher papa, tu étais parmi les gens à qui je pensais dans mes moments difficiles je savais que tu tenais vraiment à ce que je termine mes études alors je t'offre cette thèse comme une vraie reconnaissance pour ton amour pour moi.

Je dédie ce travail à ma chère sœur Imen et sa petite famille, tu me manques beaucoup, à mes deux frères Mokhtar et Aladine, je n'arrive pas à vous oublier je pense à vous chaque jour. Vous êtes mes deux anges diaboliques.

Je tiens à remercier mes beaux parents et toute ma belle famille. Je vous remercie pour votre amour et pour votre support.

Je dédie ce travail à toute ma grande famille.

Je dédie ce travail à ma chère amie Maryouma, tu es le meilleur cadeau que j'ai eu de l'ENSTA merci d'avoir été une sœur pour moi.

Je dédie cette thèse à tous mes amis et spécialement à Hana, l'amie de ma vie.

Enfin, je dédie ce travail à ma belle TUNISIE enfin libre, révolutionnaire et prometteuse !

6

# List of Abbreviations

- MPSOC: Multi Processor System On Chip

- IC : Integrated Circuit

- NOC : Network On Chip

- **GA :** Genetic Algorithm

- MOEA : Multi Objective Evolutionary Algorithm

- LP : Linear Programming

- **TSV :** Through Silicon Via

- EDA : Electronic Design Automation

- IC : Integrated Circuit

- **ILP** : Integer Linear Programming

- MOGA : Multi Objective Genetic Algorithm

- **ID** : Individual

- **FSL** : Fast Simplex Link

- **IP** : Intellectual Property

- **PE** : Processing Element

- **CMP** : Chemical-Mechanical Polishing

- WNS : Worst Negative Slack

- WTW : Wafer To Wafer

- **DTD** : Die To Die

- **DTW** : Die To Wafer

# Table of Contents

| In                         | troduct | ion   |                                                              |

|----------------------------|---------|-------|--------------------------------------------------------------|

| 1                          | MPS     | SOC S | State of The Art                                             |

| 1.1 Trends                 |         |       |                                                              |

| 1.2 MPSOC State of the Art |         |       | SOC State of the Art                                         |

|                            | 1.3     | MPS   | SOC Actual implementation                                    |

|                            | 1.4     | MPS   | SOC Design methodologies                                     |

|                            | 1.5     | Cond  | clusion                                                      |

| 2                          | . 20    | O MPS | SOC Design and implementation                                |

|                            | 2.1     | Theo  | pretical Complexity Problems in 2D Design and implementation |

|                            | 2.2     | Regu  | ular NoC implementation on FPGA: case study Butterfly        |

|                            | 2.2.1   | 1     | Synthesis results                                            |

|                            | 2.2.2   | 2     | Parallel Programming: Filter Harris                          |

|                            | 2.3     | NoC   | Design Space exploration on FPGA                             |

|                            | 2.3.1   | 1     | ModeFRONTIER tool                                            |

|                            | 2.3.2   | 2     | Multi objective Genetic Algorithm NSGA-II Algorithm          |

|                            | 2.3.3   | 3     | ModeFRONTIER project: MOEA on FPGA 46                        |

|                            | 2.3.4   | 4     | Machines Specifications                                      |

|                            | 2.3.5   | 5     | Sequential DSE                                               |

|                            | 2.4     | Para  | Ilel and multi-scale software implementation                 |

|                            | 2.5     | Retu  | rn on experience: Analyses and discussions                   |

|                            | 2.6     | Cond  | clusion                                                      |

| 3                          | 3D S    | Semi  | conductor Technology                                         |

|                            | 3.1     | 3D S  | Semi conductor Technology: Motivation                        |

|                            | 3.2     | 3D S  | Semi conductor Technology: State of the Art                  |

|                            | 3.3     | 3D I  | Design Methodologies                                         |

|                            | 3.3.1   | 1     | Wire Bonded System-in-Package                                |

|                            | 3.3.2   | 2     | Peripheral Vertical Interconnects                            |

|                            | 3.3.3   | 3     | Micro Bumps                                                  |

|                            | 3.3.4   | 4     | Through silicon via (TSV)                                    |

|                            | 3.3.5   | 5     | Contactless                                                  |

|                            | 3.4     | Bene  | efits and challenges in 3D Design                            |

|                            | 3.4.1   | 1     | Benefits of 3D Design                                        |

|   | 3.4. | 2 Challenges of 3D Design                                                        | 81  |

|---|------|----------------------------------------------------------------------------------|-----|

|   | 3.5  | 3D Academic and industrial devices                                               | 84  |

|   | 3.5. | 1 3D Academic                                                                    | 85  |

|   | 3.5. | 2 3D industrial                                                                  | 85  |

|   | 3.6  | Conclusion                                                                       | 85  |

| 4 | NoC  | C Synthesis methodologies                                                        | 88  |

|   | 4.1  | 2D NoC synthesis methodologies                                                   | 88  |

|   | 4.1. | 1 Deterministic methods                                                          | 88  |

|   | 4.1. | 2 Mixed methods                                                                  | 89  |

|   | 4.1. | 3 Heuristic methods                                                              | 89  |

|   | 4.2  | FPGA based NoC synthesis Design Flow                                             | 91  |

|   | 4.3  | Case study and performance evaluation results                                    | 95  |

|   | 4.3. | 1 Introduction to linear programming LP                                          | 95  |

|   | 4.3. | 2 OPL Modelling and CPLEX solver                                                 | 96  |

|   | 4.3. | 3 Our LP Problem Definition                                                      | 96  |

|   | 4.3. | 4 Experimental Results                                                           | 102 |

| 5 | NoC  | C Synthesis Methodology for 3D ASIC Design                                       | 110 |

|   | 5.1  | 3D NoC synthesis state of the Art                                                | 110 |

|   | 5.2  | 3D NoC synthesis design Flow                                                     | 112 |

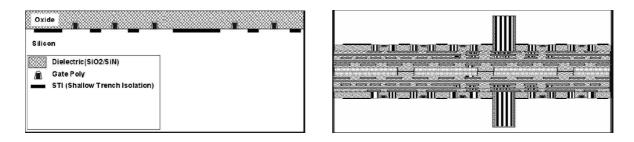

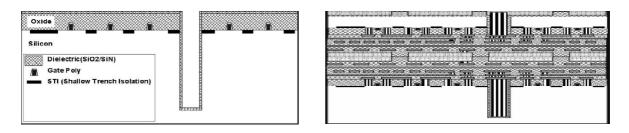

|   | 5.3  | Tezzaron Technology methodology                                                  | 117 |

|   | 5.4  | 3D NoC Synthesis with GA                                                         | 121 |

|   | 5.5  | Performance Evaluation Results                                                   | 127 |

|   | 5.5. | 1 Case Study                                                                     | 127 |

|   | 5.6  | Conclusion                                                                       | 134 |

| 6 | ASI  | IC Design Methodology for 3D NoC based 3D Heterogenous Multiprocessor On Chip    | 136 |

|   | 6.1  | 3D Multiprocessor Architecture Homogenous                                        | 136 |

|   | 6.2  | 3D Heterogeneous Multiprocessor architecture                                     | 141 |

|   | 6.3  | 3 Hardware Accelerator synthesis in 3D Heterogeneous Multiprocessor architecture | 143 |

|   | 6.4  | Conclusion                                                                       | 143 |

| 7 | The  | eoretical Complexity and Parallel EDA for 3D                                     | 146 |

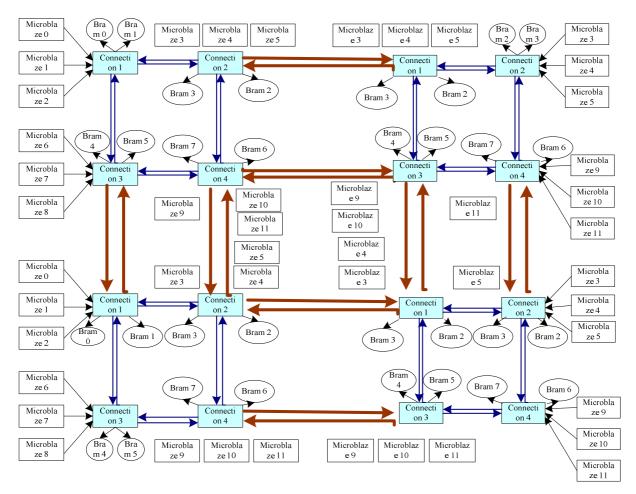

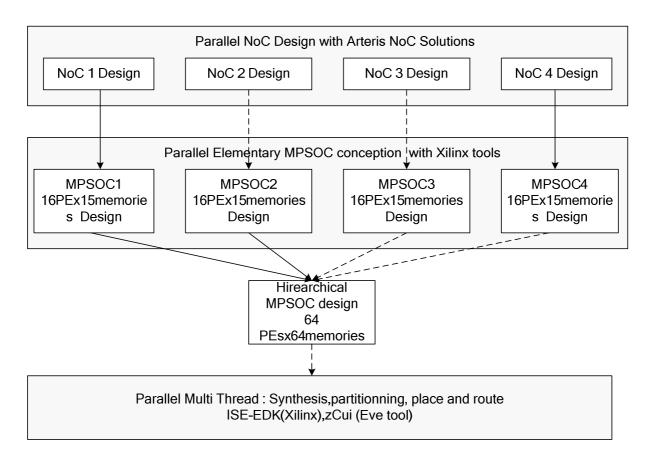

|   | 7.1  | Parallel EDA: Hierarchical MPSOC based 64 PEs on FPGA                            | 146 |

|   | 7.2  | 3D Theoretical Complexity from return of experience                              | 150 |

|   | 7.2. | 1 Core to layer mapping                                                          | 150 |

|   | 7.2. | 2 Floorplanning                                                                  | 150 |

|                      | 7.2.   | .3      | NoC topology                                     | 150 |

|----------------------|--------|---------|--------------------------------------------------|-----|

| 7.2.4                |        | .4      | NoC floorplanning                                | 150 |

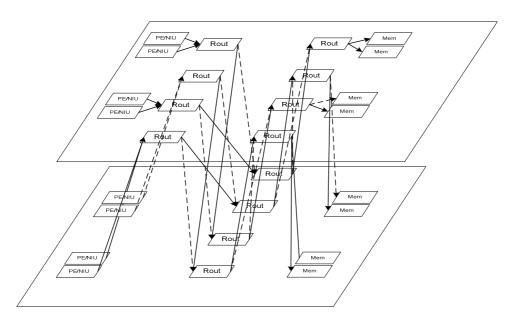

|                      | 7.3    | Para    | allel EDA for 3D IC implementation               | 151 |

|                      | 7.4    | Para    | allel EDA for 3D : Case study                    | 153 |

|                      | 7.5    | Con     | clusion                                          | 155 |

| 8                    | 3IC    | Desig   | gn and Modelling Case of Tezzaron                | 157 |

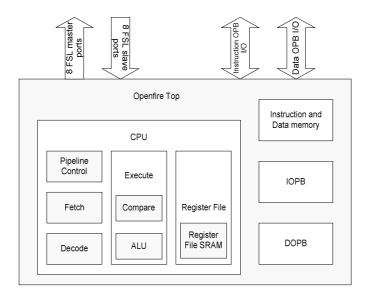

|                      | 8.1    | MPS     | SOC basic components                             | 157 |

|                      | 8.1.   | .1      | Processor                                        | 157 |

|                      | 8.1.   | .2      | Fast Simplex Link (FSL) Bus                      | 157 |

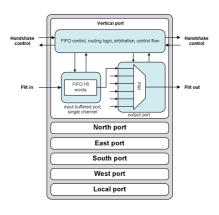

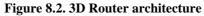

|                      | 8.1.   | .3      | 3D Router                                        | 158 |

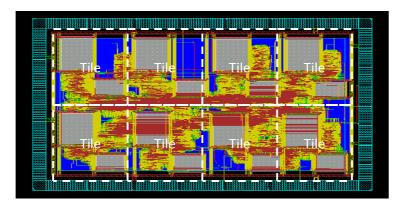

|                      | 8.2    | Arch    | hitecture 1 : MPSOC1 based on mesh topology      | 159 |

|                      | 8.3    | Arch    | hitecture 2 : MPSOC2 based on Butterfly topology |     |

|                      | 8.4    | Imp     | lementation results and discussion               | 162 |

|                      | 8.5    | Con     | nplexity of 3D implementation                    |     |

|                      | 8.6    | 3D I    | IC Fabrication                                   |     |

|                      | 8.7    | Con     | clusion                                          | 169 |

| 9                    | Cor    | nclusio | on                                               | 171 |

|                      | Refere | ences.  |                                                  | 176 |

| List of Publications |        |         | lications                                        | 194 |

# Table of Figures

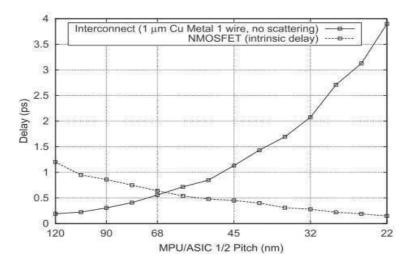

| Figure 0.1. Global and local wire delay evolution [1]                                                        | . 16 |

|--------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1 Design Complexity trend [2]                                                                       | . 21 |

| Figure 1.2. Point to Point Architecture                                                                      | . 22 |

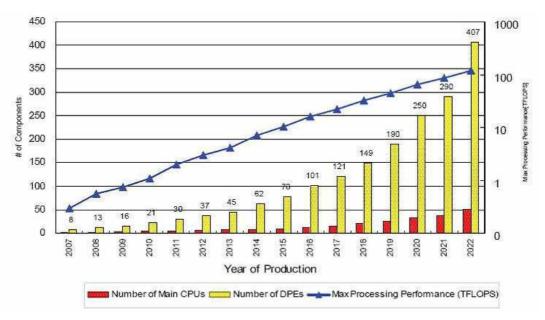

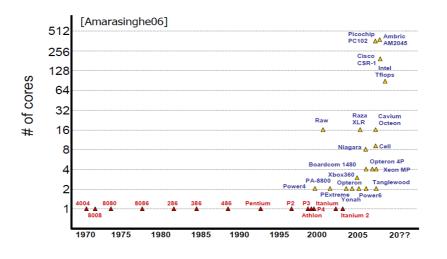

| Figure 1.4. Industrial MPSOC number of cores evolution [4]                                                   | . 23 |

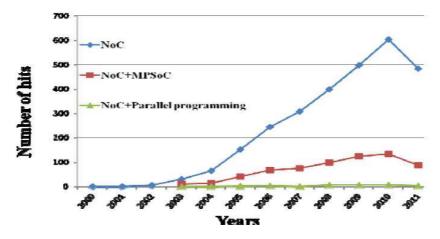

| Figure 1.5. IEEE Xplorer hits for different "network-on-chip" researches [5]                                 | . 24 |

| Figure 1.6. Tile 64 Block Diagram Processor[17]                                                              | . 27 |

| Figure 1.7. SpiNNaker MPSoC block diagram[13]                                                                | . 27 |

| Figure 1.8. SpiNNaker MPSoC plot[13]                                                                         | . 27 |

| Figure 1.9. Kumar et al MPSOC Design flow[18]                                                                | . 28 |

| Figure 1.10. Application Specific MPSOC workflow [22]                                                        |      |

| Figure 1.11. Xpipes Synthesis Flow[23]                                                                       | . 29 |

| Figure 1.12. STARSOC Design flow overview                                                                    | . 30 |

| Figure 1.13. Automatic heterogeneous design flow [25]                                                        | . 31 |

| Figure 1.14. MPSOC Methodology Workflow of SpiNNaker [13]                                                    | . 32 |

| Figure 2.1. MPSOC based Butterfly NoC: 2Ary 4Fly Architecture                                                |      |

| Figure 2.2. Our MPSOC implementation workflow                                                                |      |

| Figure 2.3. Harris Filter Execution Time and speed up                                                        | . 41 |

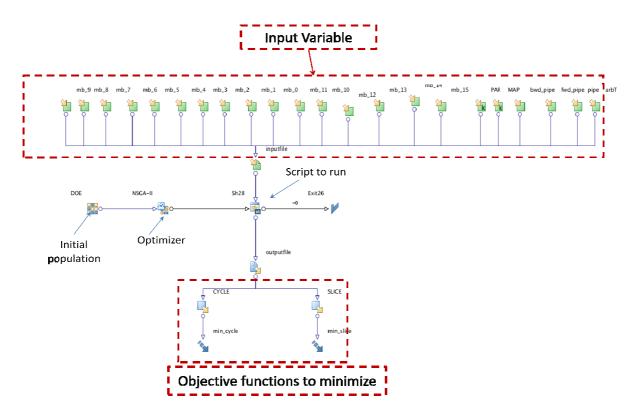

| Figure 2.4. ModeFRONTIER project example                                                                     | . 42 |

| Figure 2.5. ModeFRONTIER initial population                                                                  |      |

| Figure 2.6. NSGA-II algorithm illustration                                                                   |      |

| Figure 2.7. ModeFRONTIER DSE Project                                                                         |      |

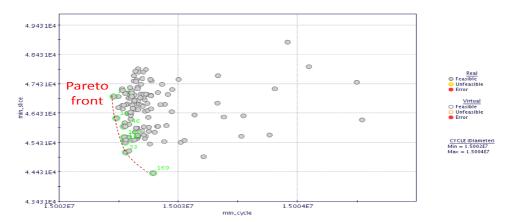

| Figure 2.8. Pareto Front DSE of Harris Filter on MPSOC 16x16                                                 |      |

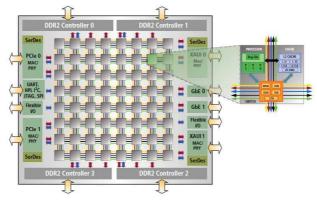

| Figure 2.9. SSM IP Architecture                                                                              |      |

| Figure 2.10. MPSOC7: Execution time variation in function of the population size:                            |      |

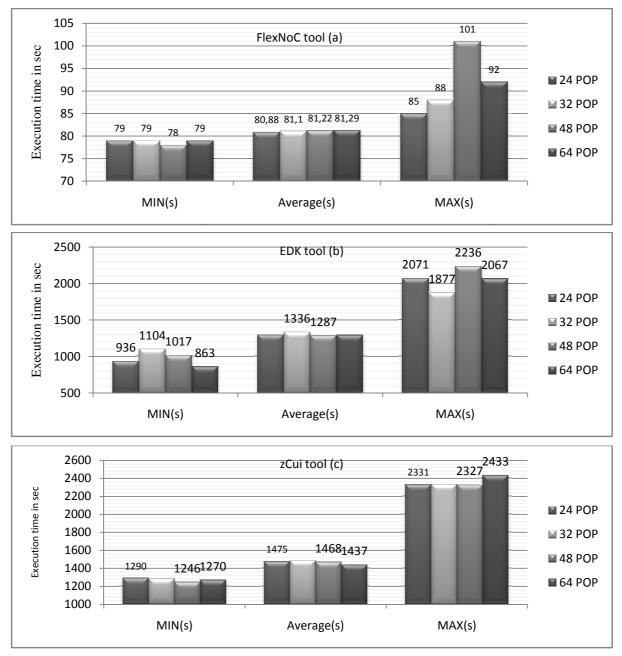

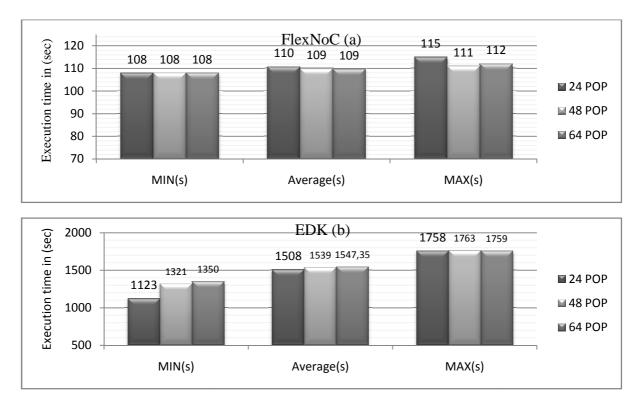

| Figure 2.11. THALES2 : Comparison of FlexNoC (a) EDK (b) execution with different population sizes           |      |

| Figure 2.12. MPSOC4: Comparison of FlexNoC (a), EDK (b), zCui (c) with different population sizes            |      |

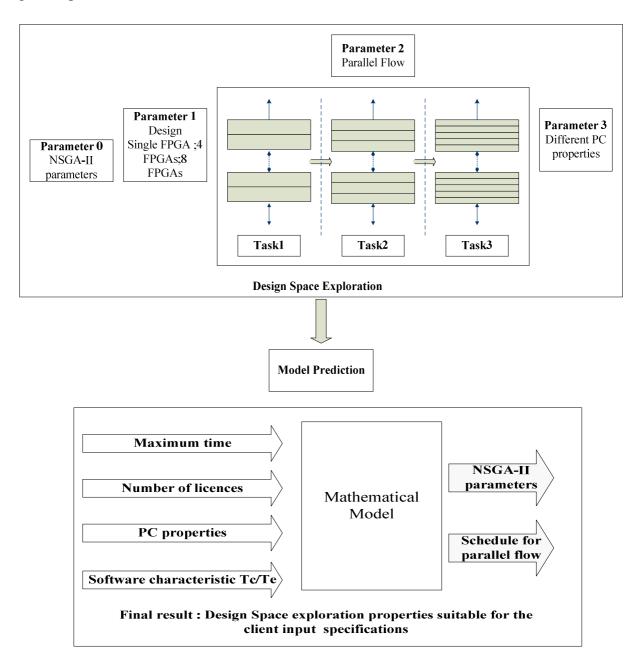

| Figure 2.13. Design Space Exploration for mathematical Model generation                                      |      |

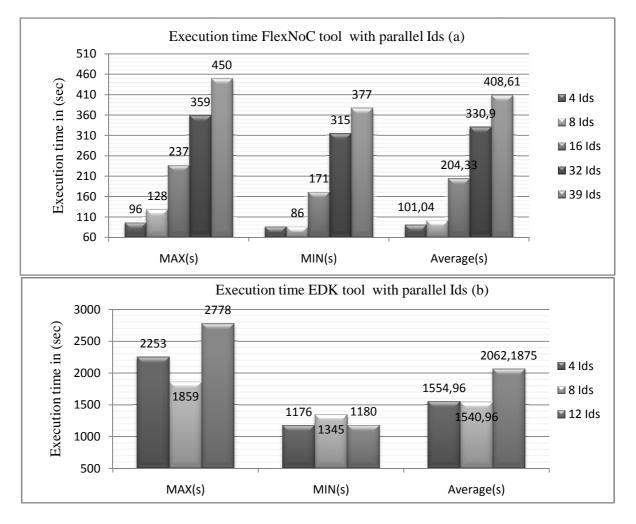

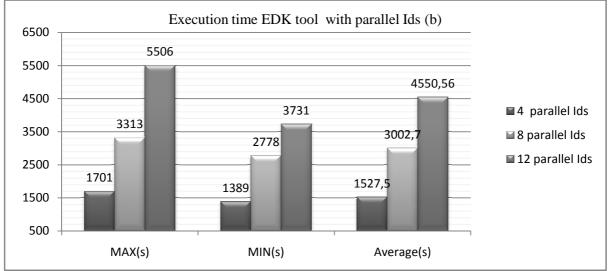

| Figure 2.14. MPSOC7 : Comparison of FlexNoC (a), EDK (b) execution with different numbers parallel Ids       |      |

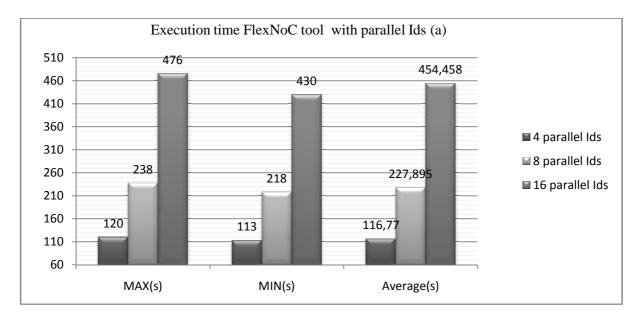

| Figure 2.15. THALES2: Comparison of FlexNoC (a), EDK (b) execution with different numbers parallel Ids.      |      |

| Figure 2.16. SSM IP 48 processors 32 BRAMs                                                                   |      |

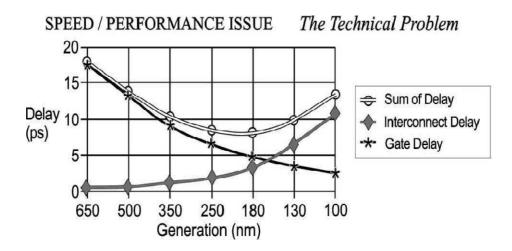

| Figure 3.1. Gate and Interconnect Delay as a function of gate technology [39]                                |      |

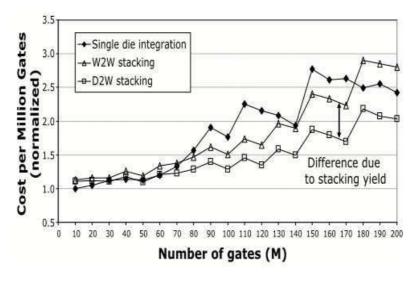

| Figure 3.2. Cost CMOS scaling[40]                                                                            |      |

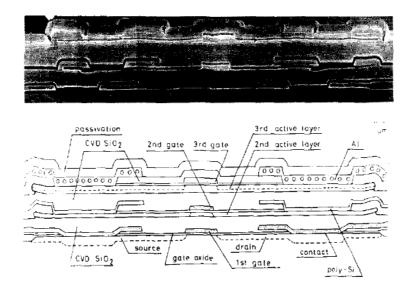

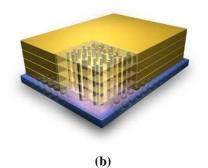

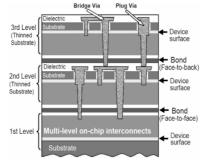

| Figure 3.3. Example of 3D Design [42]                                                                        |      |

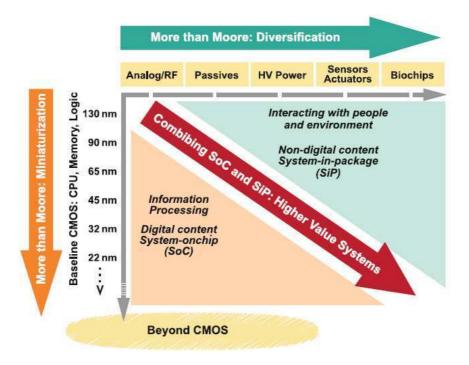

| Figure 3.4. Illustration of the evolution of the semi conductor technology with CMOS scaling with other ways |      |

| development offering new functionalities [2]                                                                 |      |

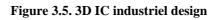

| Figure 3.5. 3D IC industriel design                                                                          |      |

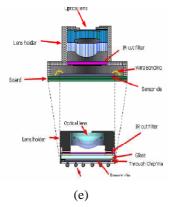

| Figure 3.6. Illustration of vertical interconnect technologies: wire bonded (a); microbump—3D package (b) ar |      |

| face-to-face (c); contactless—capacitive with buried bumps (d) and inductive (e); through via—bulk (f) and   |      |

| silicon on insulator (g) [54]                                                                                | . 68 |

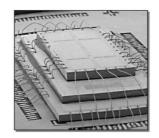

| Figure 3.7. Wire bonding design [55]                                                                         |      |

| Figure 3.8. Wire bonded System-in-Package[57]                                                                |      |

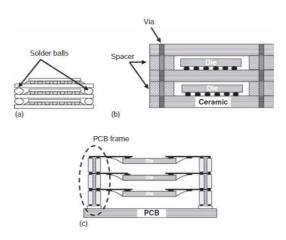

| Figure 3.9. SiP with peripheral connections: (a) solder balls (b) through-hole via and spacers ,             |      |

| Figure 3.10. 3D Chip with Micro Bumps                                                                        |      |

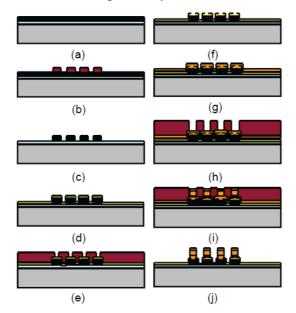

| Figure 3.11. Process flow fabrications of CuSn solder Microbump[60]                                          |      |

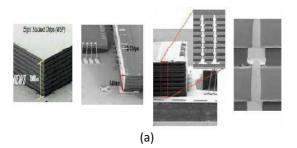

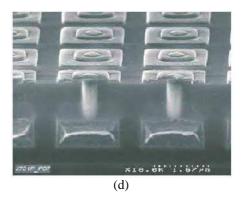

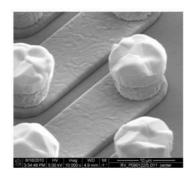

| Figure 3.12. SEM picture a die part of the interwoven daisy chain with 10µm diameter CuSn bumps formed b     |      |

| electrochemical plating. The pitch of the bumps is $20\mu$ m [61]                                            | -    |

| Figure 3.13. Through silicon via (TSV)[62]                                                                   |      |

| Figure 3.14. TSV examples [64]                                                                               |      |

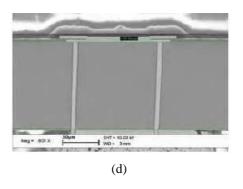

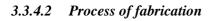

| Figure 3.15. General TSV flow fabrication [65]                                                               |      |

| Figure 3.16. Via first (left), Via last (right) 3D IC methodologies[63]                                      |      |

|                                                                                                              |      |

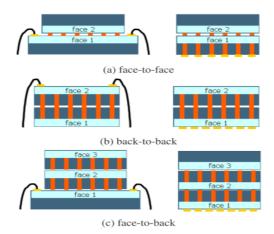

| Figure 3.17. Stacking Methods[66]                                                                          |     |

|------------------------------------------------------------------------------------------------------------|-----|

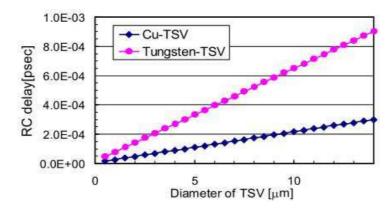

| Figure 3.18. RC delay vsTSV diameter[67]                                                                   | 77  |

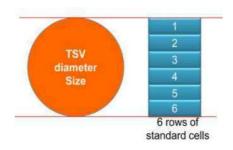

| Figure 3.19. TSV Area estimation[68]                                                                       |     |

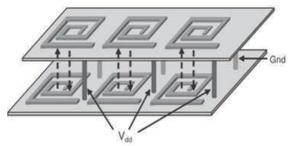

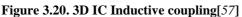

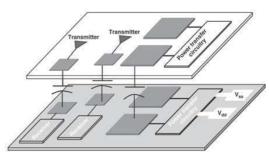

| Figure 3.20. 3D IC Inductive coupling[57] Figure 3.21. 3D IC capacitive coupling[70]                       |     |

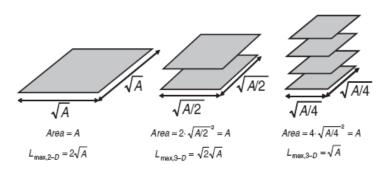

| Figure 3.22. Area reduction with 3D Stacking [71]                                                          | 79  |

| Figure 3.23. Average latency 3D IC and 2D IC [67]                                                          | 80  |

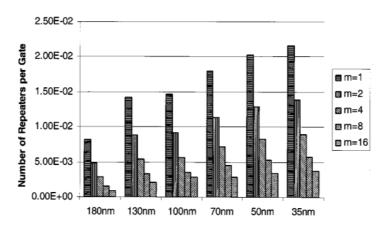

| Figure 3.24. Number of repeaters with different technologies                                               | 80  |

| Figure 3.25. 3D chip with heterogenous technologies [72]                                                   | 81  |

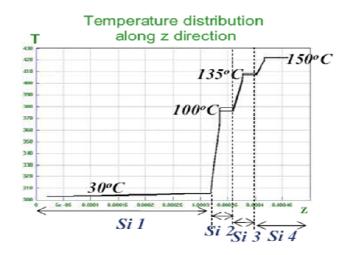

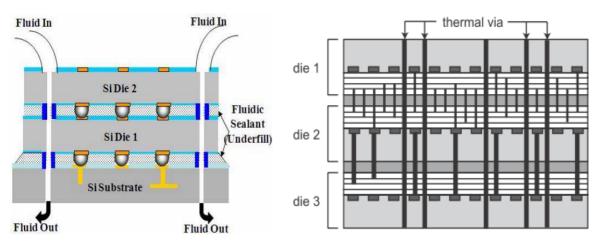

| Figure 3.27. Temperature distribution along the z Axis with different Silicon layers [69]                  | 82  |

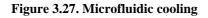

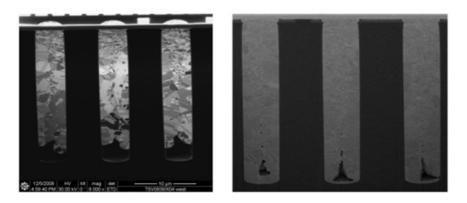

| Figure 3.28. Microfluidic cooling                                                                          | 82  |

| Figure 3.29. Thermal vias for heat dissipation [74]                                                        | 82  |

| Figure 3.30. Examples of TSV defects: insufficiently filled TSV (right), TSV containing Micro voids (left) | 83  |

| Figure 3.31. 3D IC testing model[75]                                                                       | 83  |

| Figure 3.32.Geographic mapping of 3D IC players [76]                                                       | 84  |

| Figure 3.33. 3D TSV applications and players [77]                                                          | 85  |

| Figure 4.1. NoC synthesis on FPGA [87]                                                                     | 91  |

| Figure 4.2. 2D NoC synthesis workflow                                                                      | 92  |

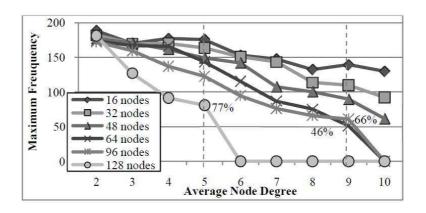

| Figure 4.3. Prediction of the Frequency variation when the number and the average node degree of the       |     |

| benchmark change [88]                                                                                      | 93  |

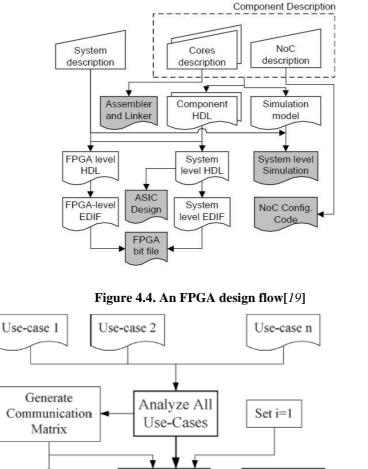

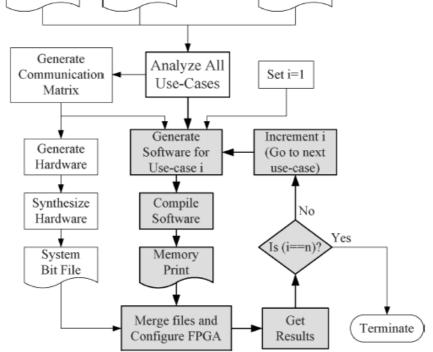

| Figure 4.4. An FPGA design flow[19]                                                                        | 94  |

| Figure 4.5. The overall flow for analyzing multiple use-cases: the software part is performed for each     |     |

| application, the hardware is performed only one time [89]                                                  | 94  |

| Figure 4.6. LP graphical solution                                                                          |     |

| Figure 4.7. 263 enc MP3 Dec : coregraph (left), NoC toplogy (right)                                        | 104 |

| Figure 4.8. MPEG4 Decoder[78]                                                                              |     |

| Figure 4.9. MPEG 4 Decoder NoC topology                                                                    |     |

| Figure 4.10. H264 Decoder                                                                                  |     |

| Figure 4.11. H264 Decoder NoC topology                                                                     |     |

| Figure 4.12. Coregraph partitioning                                                                        |     |

| Figure 5.1. 3D Design flow                                                                                 |     |

| Figure 5.2. Algorithm Steps                                                                                |     |

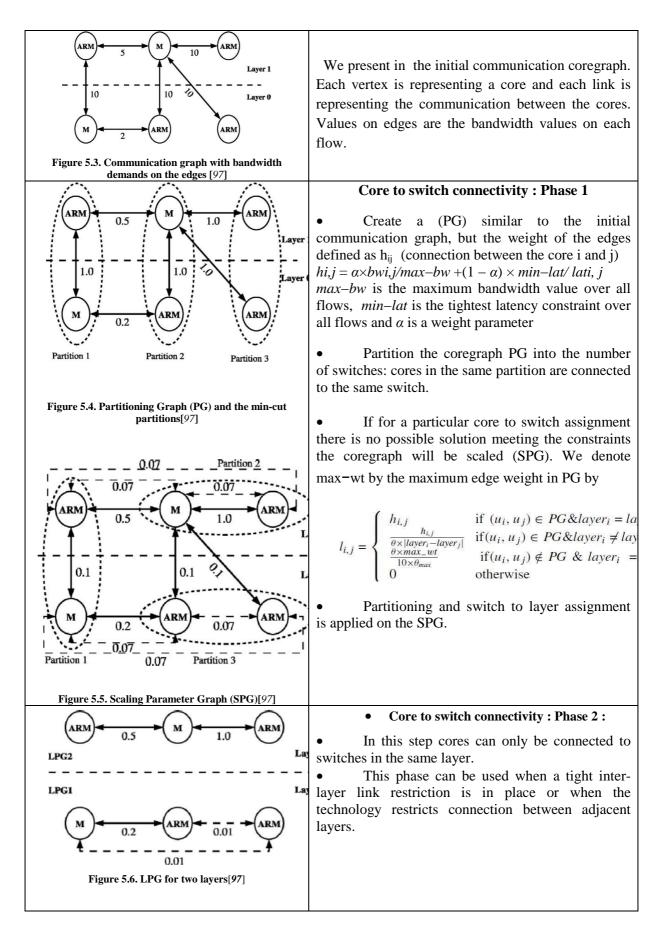

| Figure 5.3. Communication graph with bandwidth demands on the edges [97]                                   |     |

| Figure 5.4. Partitioning Graph (PG) and the min-cut partitions[97]                                         |     |

| Figure 5.5. Scaling Parameter Graph (SPG)[97]                                                              |     |

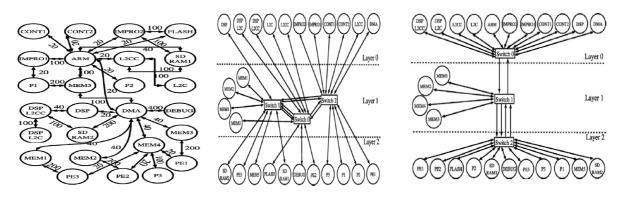

| Figure 5.7. (left) D26_media communication, (middle) NoC architecture phase 1, (right) NoC Architecture pl |     |

| 2 [97]                                                                                                     |     |

| Figure 5.8. 3D NoC synthesis Design flow with GA,                                                          |     |

| Figure 5.9. 3D NoC synthesis Design flow based on floorplanning[92]                                        |     |

| Figure 5.10. 3D NoC synthesis workflow[95]                                                                 |     |

| Figure 5.11. 3D-IC Automatic P&R using DBI and TSV                                                         |     |

| Figure 5.13. Signal to Bumps assignment                                                                    |     |

| Figure 5.12. Create Bumps Array                                                                            |     |

| Figure 5.14. Create pins under Bumps Tezzaron technology                                                   |     |

| Figure 5.15. Our 3D NoC synthesis workflow                                                                 |     |

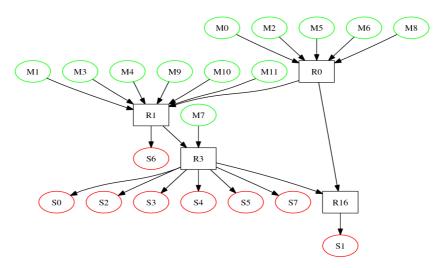

| Figure 5.16. Coregraph 1 : 12 Masters 8 slaves                                                             |     |

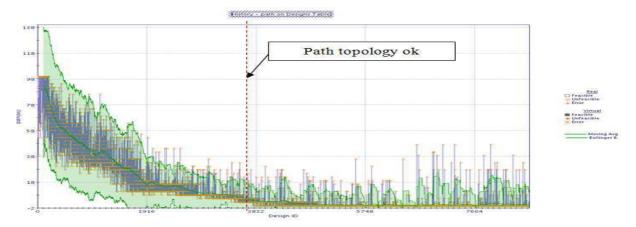

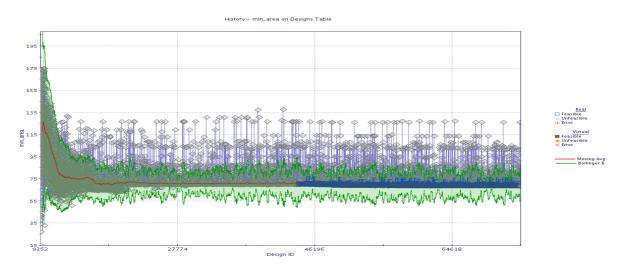

| Figure 5.17. Case 1: Error Path constraint evolution                                                       |     |

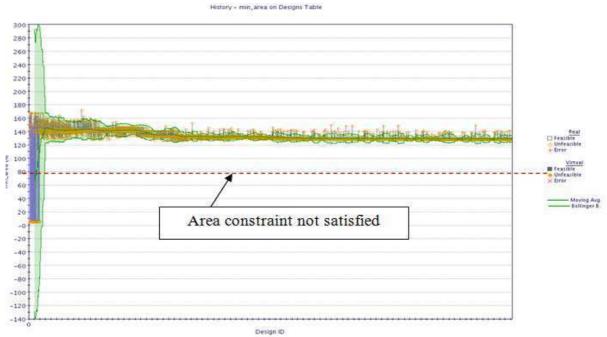

| Figure 5.17. Case 1: Area Constraint evolution                                                             |     |

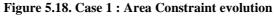

| Figure 5.19. Case 2 Min area constraint evolution                                                          |     |

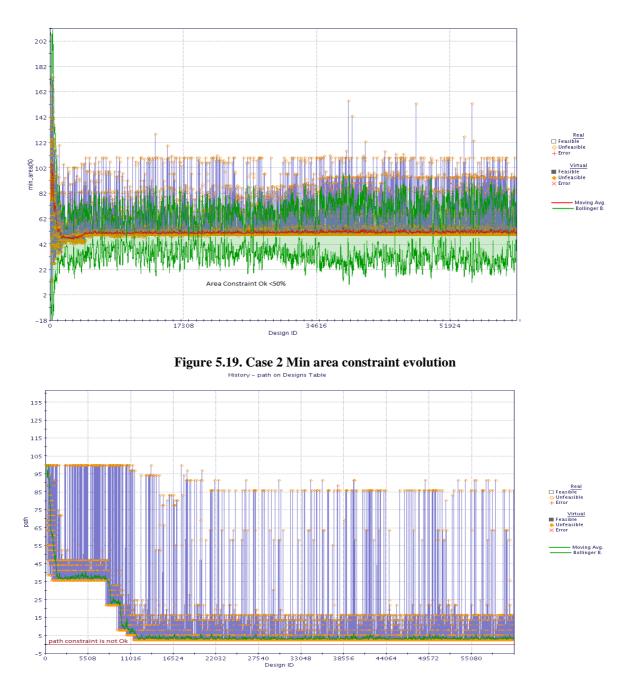

| Figure 5.20. Case 2 Error path constraint Evolution                                                        |     |

|                                                                                                            |     |

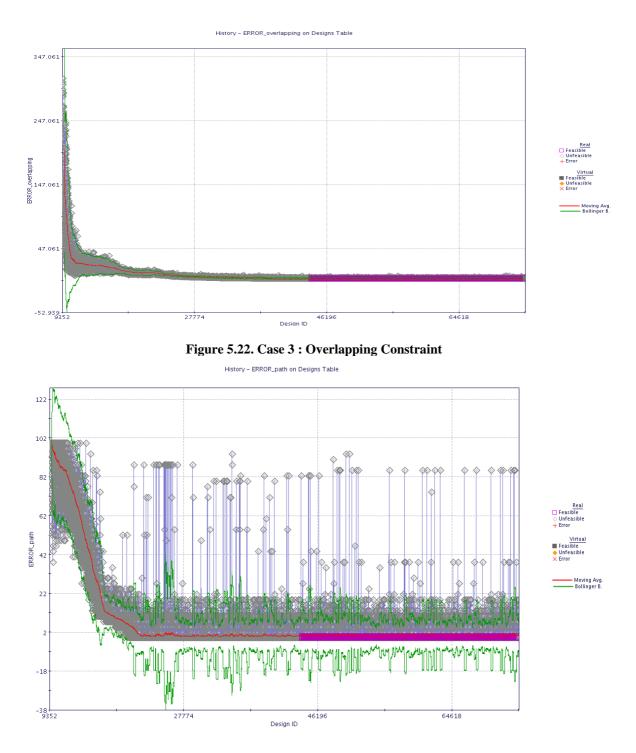

| Figure 5.21. Case 3 : Area constraint evolution                                                            |     |

| Figure 5.22. Case 3 : Overlapping Constraint                                                               |     |

| Figure 5.23. Case 3 : Path constraint                                                                      |     |

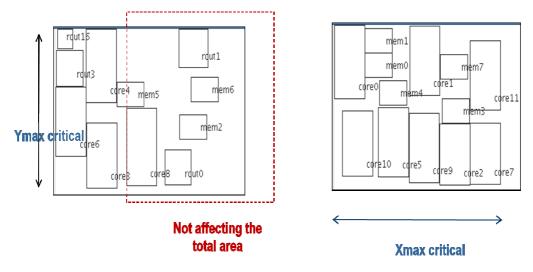

| Figure 5.24. Our 3D NoC synthesis floorplan Solution                                                       | 133 |

| Figure 5.25. The optimized NoC topology                                                                 | 133      |

|---------------------------------------------------------------------------------------------------------|----------|

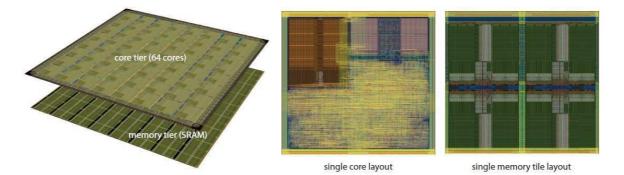

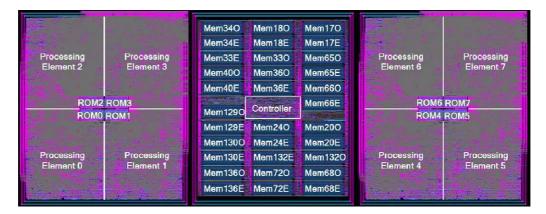

| Figure 6.1. Various layout views of the 3D-MAPS processor[48]                                           | 136      |

| Figure 6.2. The structure of the PE [49]                                                                |          |

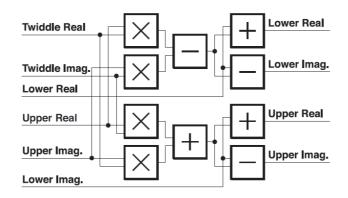

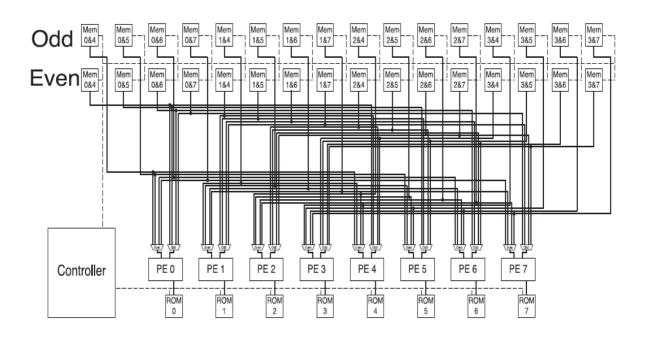

| Figure 6.3. The SAR FFT processor architecture[49]                                                      | 138      |

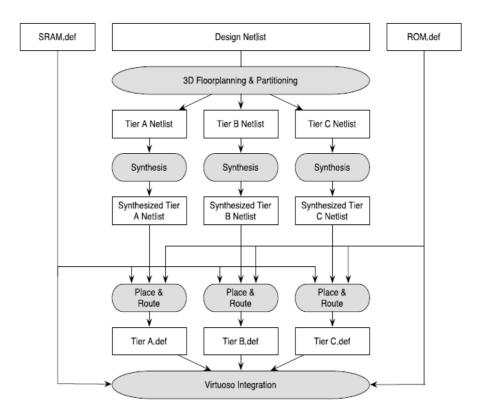

| Figure 6.4. T. Thorolfsson 3D Design flow[49]                                                           | 139      |

| Figure 6.5. The SAR FFT floorplan[49]                                                                   | 139      |

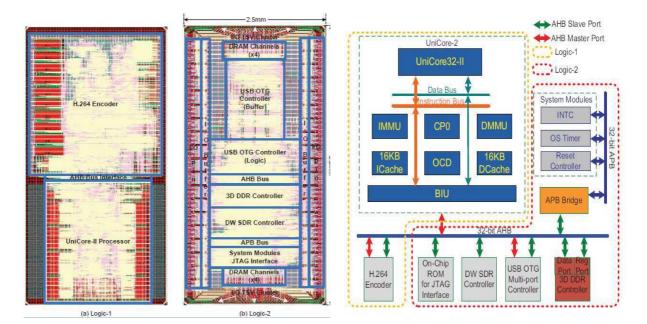

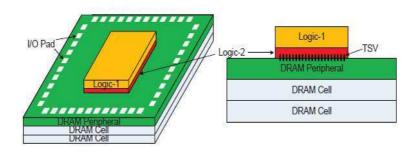

| Figure 6.6.Schematic and layout view of 3D SoC H.264 Application [51]                                   | 140      |

| Figure 6.7. 3D DRAM stacking [51]                                                                       | 140      |

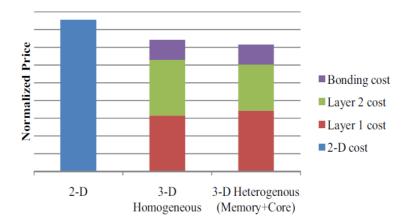

| Figure 6.8. The estimated cost of OpenSPARC : the separate core and memory fabrication reduces the cost | st [101] |

|                                                                                                         | 141      |

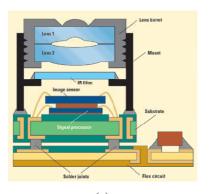

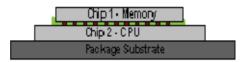

| Figure 6.9. cross section of the final package                                                          | 142      |

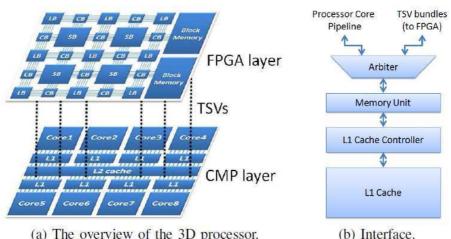

| Figure 6.10. 3D processor architecture CMP-FPGA[103]                                                    | 143      |

| Figure 7.1. MPSOC architecture 64 PEs on Multi-FPGA platform Zebu-UF4                                   | 146      |

| Figure 7.2. Parallel workflow EDA MPSOC implementation on FPGA                                          | 148      |

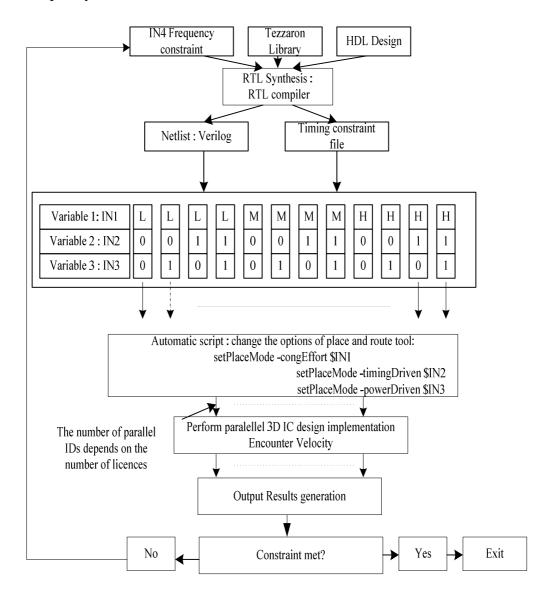

| Figure 7.3. 3D IC parallel and automatic workflow                                                       | 152      |

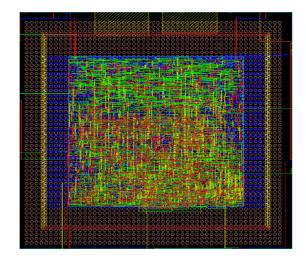

| Figure 7.4. The placed and routed Filter with 3D Tezzaron Technology                                    | 153      |

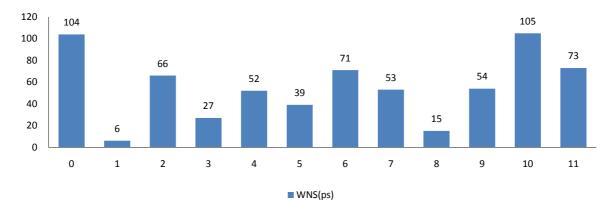

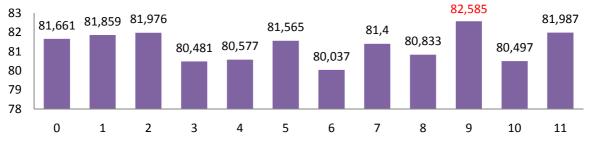

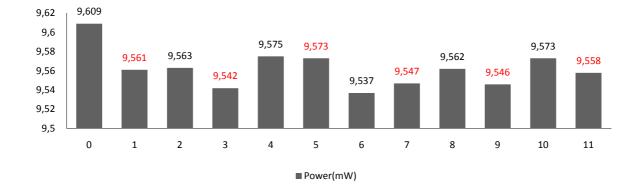

| Figure 7.5 WNS (ps), Density (%) and power (mw) for the different combinations of the DSE (Freq=100     | )MHZ)    |

|                                                                                                         | 154      |

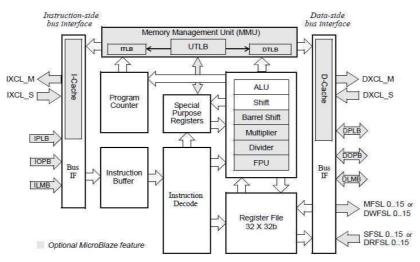

| Figure 8.1. Openfire processor architecture                                                             |          |

| Figure 8.2. 3D Router architecture                                                                      | 159      |

| Figure 8.3. Network interface architecture                                                              | 159      |

| Figure 8.4. Architecture 1: MPSOC based on Mesh topology                                                | 160      |

| Figure 8.5. Tile Block Diagram                                                                          | 160      |

| Figure 8.6. Architecture 2 : MPSOC Based on the butterfly architecture                                  | 161      |

| Figure 8.7 MPSOC1 Mesh: Bottom tier routed layout                                                       |          |

| Figure 8.8. MPSOC2 Butterfly: Bottom Tier routed layout                                                 | 162      |

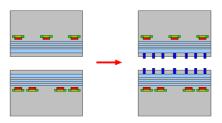

| Figure 8.9. 3D MPSOC partitioning                                                                       | 164      |

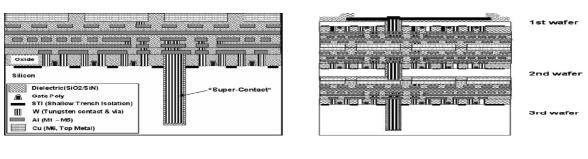

| Figure 8.10. Tezzaron 3D Techniques: Super-Via(left), Super Contact(right)[107]                         | 165      |

| Figure 8.11. Illustration of Tezzaron's Stacking method with the '' Super Contact'' Interconnect[107]   |          |

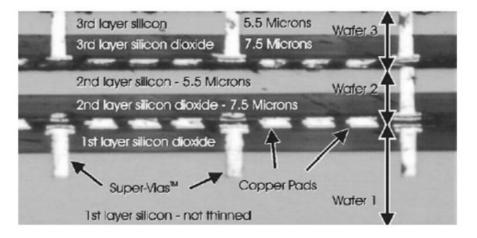

| Figure 8.12. Tezzaron metal bonding[62]                                                                 | 167      |

| Figure 8.13. Deposit D2D Vias[108]                                                                      |          |

| Figure 8.14. CMP step for stack thinning [108]                                                          | 168      |

| Figure 8.15. Etching for power/Gnd TSV [108]                                                            | 168      |

| Figure 8.16.The Heat Sink creation [108]                                                                | 168      |

# List of Table

| Table 1.1. ITRS 3D Interconnect TSV Roadmap                                        | . 22 |

|------------------------------------------------------------------------------------|------|

| Table 1.2. MPSOC state of the Art                                                  | . 24 |

| Table 1.3. MPSOC using busses communication                                        | . 26 |

| Table 1.4. Actual MPSOC implementation                                             | . 26 |

| Table 2.1. Comparison Mesh and Butterfly topology                                  | . 35 |

| Table 2.2 Address of the slaves                                                    | . 36 |

| Table 2.3. Different switch routing tables                                         | . 37 |

| Table 2.4. Resource utilization of Zebu-UF4                                        | . 39 |

| Table 2.5. Microblaze parameters                                                   | . 47 |

| Table 2.6. Switch Options                                                          | . 48 |

| Table 2.7. The properties of the machines                                          | . 49 |

| Table 2.8. ZEBU UF4 Emulator specifications                                        | . 50 |

| Table 2.9. SSM IP 48x32 on Zebu UF4 Resource utilizations                          | . 58 |

| Table 2.10. SSM IP 48x32 Exploration Results                                       | . 59 |

| Table 3.1. 3D MPSOC design implementation [50]                                     |      |

| Table 3.2. High-density through silicon via projections in 2008 ITRS update [63]   | . 72 |

| Table 3.3. TSV process flows [63]                                                  |      |

| Table 3.4. Comparison between bonding methods (KGD: Known Good Die)[60]            | . 75 |

| Table 3.5. Comparison of Via Filling Materials [55]                                | . 76 |

| Table 3.6. Performance and power comparison between different 3D architectures[71] |      |

| Table 3.7. Reduction of integrated yield with stacking using wafer on wafer [70]   | . 83 |

| Table 4.1. Summary of 2D NOC synthesis Methods                                     | . 90 |

| Table 4.2. Semi conductor properties                                               | 103  |

| Table 4.3. Properties and execution time for the different benchmarks              | 104  |

| Table 4.4. Routers Description 263 Enc MP3 Dec                                     | 104  |

| Table 4.5. Routers Description MPEG 4 Decoder                                      | 106  |

| Table 4.6. Router configurations H264 Decoder.                                     |      |

| Table 5.1.3D NoC synthesis methodologies                                           | 111  |

| Table 5.2. ARM used in the Design Kit Tezzaron library                             | 119  |

| Table 5.3. MOEA Project parameters                                                 | 123  |

| Table 5.4. Case study different configurations                                     | 128  |

| Table 6.1. Physical Design Summary [48]                                            | 137  |

| Table 6.2. Architectural Performance Metrics[48]                                   |      |

| Table 7.1. Resources utilization                                                   |      |

| Table 7.2. 64PE MPSOC Used IPs                                                     | 148  |

| Table 7.3. Resource utilization of the MPSOC based 64 PEs NoC[104]                 | 149  |

| Table 7.4. Options of FILTER DSE                                                   |      |

| Table 7.5.Different ID (L: Low, H: High, M: Medium)                                |      |

| Table 8.1. MPSOC Implementation results                                            | 164  |

## Introduction

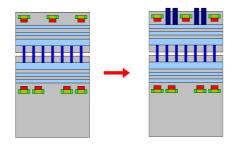

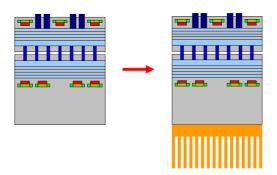

ITRS road map has predicted that the number of cores in the same chip will increase following an exponential curve. This was the major motivation to create new techniques to solve the interconnection problem between high number of cores in the same MPSOC. The use of the Network On Chip represents an efficient solution to deal with classical interconnect methods limitations like the point to point and the shared bus. But with the evolution of the CMOS semi-conductor reaching the Nanometre scales, the interconnect delay is overcoming the gate delay which is illustrated in Figure 0.1. The Interconnect delay is the new performance limitation of the chip. The reduction of the interconnection length is the new challenge in the MPSOC design. 3D IC is emerging as a suitable solution to reduce the global interconnects delay thanks to the use of the vertical links.

Figure 0.1. Global and local wire delay evolution [1]

Even though 3D IC design is not a new methodology, the number of works making real 3D ASIC implementation is too limited. The major problem of the 3D IC design is the shortage of 3D IC dedicated EDA tools. In fact, there is no complete industrial software allowing the implementation of all the steps of 3D workflow.

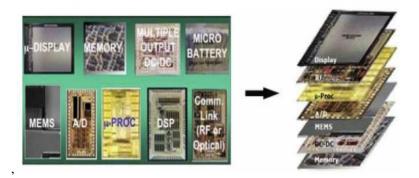

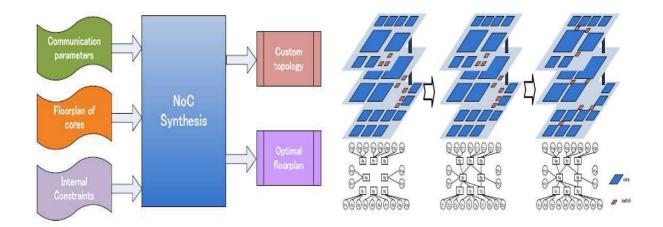

The objective of this work is to evaluate the different MPSOC design methodologies used in 3D IC design. We focus on the implementation of the NoC synthesis with heterogeneous architectures.

We propose in the first part of this work, to explore different MPSOC implementation methodologies. A design space exploration of the different configurations of the hardware architectures will be performed in order to find the optimal one in term of cost and performance. The objective of this work is to validate the used MPSOC architectures before their implementation on 3D IC.

The main objective of this thesis is to propose a new 3D NoC synthesis methodology taking in consideration the 3D IC used technology. A real implementation with 3D ASIC design will be performed in order to show up the advantages of the 3D design compared to the obtained results in 2D.

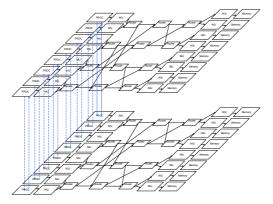

The organization of this report is directly related to the scientific approach and methodology adopted during this PHD studies. In fact, the first step of this work which is the MPSOC state of the art represents an important introduction to the general research field. We can then propose an MPSOC design implementation of an interesting architecture when compared to the actual industrial and research achievements. Chapter two and three are performed in parallel in order to have a good 2D experimental knowledge and a rich 3D theoretical background which are necessary before the NoC synthesis section. As we believe that the 3D NoC synthesis problem has a very high complexity, we propose to start by exploiting our Lab experience in 2D NoC synthesis by proposing a new NoC synthesis model based on the Microelectronics characteristics. After having a first experience in the 2D NoC synthesis we can then move to the 3D NoC synthesis chapter with an efficient strategy. The last three chapters concern the 3D IC MPSOC state of the art, complexity and real implementation.

We present in chapter 1 of this thesis, the state of the art of the existing MPSOC real implementations listed in the literature. We also detail the different design methodologies with real implementations.

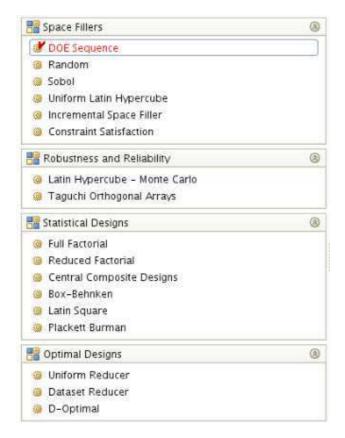

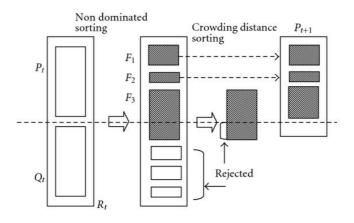

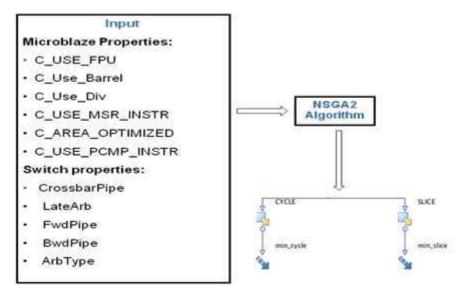

We introduce in chapter 2 the 2D design and implementation of our MPSOC architecture based on software processors and regular NoC. The execution result of a parallel image processing on FPGA will be reported. We will use the GA in order to explore and evaluate the performance of the different industrial tools.

Chapter 3 will be the subject of 3D semi conductor technology state of the art. We will detail the different 3D ASIC design methodologies. We will then discuss the different issues and challenges in 3D design.

17

The NoC synthesis methodologies will be the subject of chapter 4. We will define the exact, the mixed and the heuristic methods already used in literature. Our NoC synthesis 2D solution will be presented as a case study of this chapter.

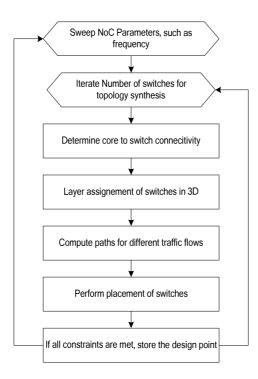

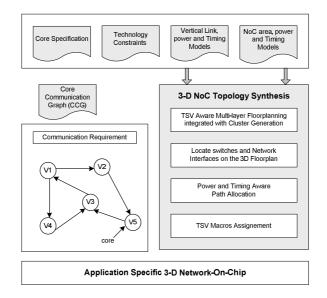

We will introduce in chapter 5 the different properties of the 3D Tezzaron technology. We will also detail the 3D ASIC methodologies presented in the literature. The sate of the art of the 3D NoC synthesis problem will be summarized. We will detail in this chapter our 3D NoC synthesis methodology based on the MOEA.

In chapter 6, we will study different MPSOC architectures based on heterogeneous components. We will then discuss the different methodologies to create MPSOC architectures using 3D Hardware Accelerator.

We will evaluate in chapter 7, the theoretical complexity and the experimental results of our parallel EDA of the 3D NoC synthesis problem. We will perform a design space exploration on the cadence tool to study the effect of the different properties on the synthesis, place and route results.

Chapter 8, will present the 3D ASIC design implementation of our MPSOC using the 3D Tezzaron technology. The results of synthesis, place and route of our 3D architecture will be reported.

The last part of this report will include the conclusion and our future work.

PHD Plan and Scientific Approach Organization

18

# Chapter 1 : MPSOC State of The Art

### 1 MPSOC State of The Art

The use of a single processor is not any more possible in the industrial products like smart phones and medical devices needing high computational time and fast parallel programming. That is why; the use of Multi Processor System On Chip (MPSOC) is emerging. As a real example, we can notice that the MPSOC Cortex-A9 of ARM Company was included in many industrial chips like Nvidia's Tegra 2 and Samsung's Exynos 4210.

#### 1.1 Trends

Figure 1.1 Design Complexity trend [2]

The prevision of the International Technology Roadmap in Semi conductor (ITRS) was considered as a sort of science fiction in the beginning of the last decades but researchers have respected and sometime they have even exceeded this prevision. In fact, the evolution of the number of IPs in the same chip was supposed to double each about 18 months as presented in Figure 1.1. For this, the first alternative was scaling the technology but this methodology has almost reached its limitation face to the physical problems of semi conductor. In Figure 0.1, we can see that the global wire delay is becoming more important than gates delay in Nanometre technologies. The global delay of the NoC is limited in this case not by the gate delay but by the global wires delay. The connectivity becomes a major problem when we increase the number of cores in the same chip. With the high complexity of the multiprocessors system on chip MPSOC, the need for scalable and efficient communication architectures to support inter-core data transfers has become paramount. Network-on-Chip (NoC) fabrics have been shown to provide superior communication

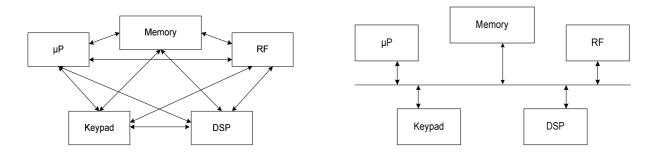

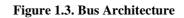

bandwidth, scalability, and modularity compared to traditional bus-based architectures (Figure 1.2 and Figure 1.3).

#### Figure 1.2. Point to Point Architecture

NoCs have gradually gained acceptance as the dominant interconnection paradigm for emerging CMP systems with tens to hundreds of cores. The interconnect challenge is one of the major problems in MPSOC architectures. Once solved with the NoC solution, a new limitation related to the interconnect length is now faced. In fact, the design of future MPSOC architectures especially with Nanometre technologies should minimize the interconnection length in order to increase the performance.

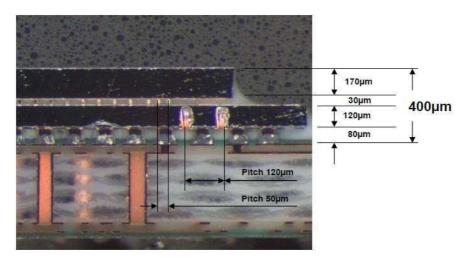

. A new solution is emerging to deal with this limitation which is the 3D ASIC design. In fact, with a 3D MPSOC, the global routing length can be shortening thanks to the use of the vertical connection called TSV. ITRS roadmap presents in the report published in 2011[3], the prediction of the evolution in the world of 3DIC which is presented in Table 1.1. Referring to this table, the reduction of the TSV diameter and pitch will reach 50% between the years 2012-2015. This can be a major reason to increase the use of the 3DIC in the future chips.

| Global Level, WTW, DTW, or DTD 3D stacking | 2009-2012  | 2012-2015  |

|--------------------------------------------|------------|------------|

| Minimum TSV diameter                       | 4-8 µm     | 2-4 µm     |

| Minimum TSV pitch                          | 8-16 µm    | 4-8 µm     |

| Minimum TSV depth                          | 20-50 µm   | 20-50 µm   |

| Maximum TSV aspect ratio                   | 5:1-10-1   | 10:1-20:1  |

| Bonding overlay accuracy                   | 1.0-1.5 µm | 0.5-1.0 µm |

| Minimum contact pitch(thermo compression)  | 10 µm      | 5µm        |

| Minimum contact pitch (solder or SLID)     | 20 µm      | 10µm       |

| Number of tiers                            | 2-3        | 2-4        |

| INTERMEDIATE Level, WTW 3D stacking        | 2009-2012  | 2012-2015  |

| Minimum TSV diameter                       | 1-2 µm     | 0.8-1.5 μm |

| Minimum TSV pitch                          | 2-4 µm     | 1.6-3 µm   |

| Minimum TSV depth                          | 6-10 µm    | 6-10µm     |

| Maximum TSV aspect ratio                   | 5:1-10:1   | 10:1-20:1  |

| Bonding overlay accuracy                   | 1.0-1.5 µm | 0.5-1.0 µm |

| Minimum contact pitch                      | 2-3 µm     | 2-3 µm     |

| Number of tiers                            | 2-3        | 8-16(DRAM) |

| Table 1.1. ITRS | <b>3D Interconnect</b> | TSV | Roadmap |

|-----------------|------------------------|-----|---------|

|-----------------|------------------------|-----|---------|

#### **1.2 MPSOC State of the Art**

The first real MPSOC was created in the beginning of the last decade based on two processors. The communication between cores was ensured in the beginning via the classical communication technologies like shared busses and point to point methodologies. With reference to the Figure 1.4, it is clear that the number of cores is increasing respecting an exponential curve. Until the year 2000, only single processors were available like the well known one which is the Pentium. This domain knew a real revolution in the previous decade with the apparition of different MPSOCs architectures. The evolution of the MPSOC is directly related the evolution of the interconnection methodologies.

Figure 1.4. Industrial MPSOC number of cores evolution [4]

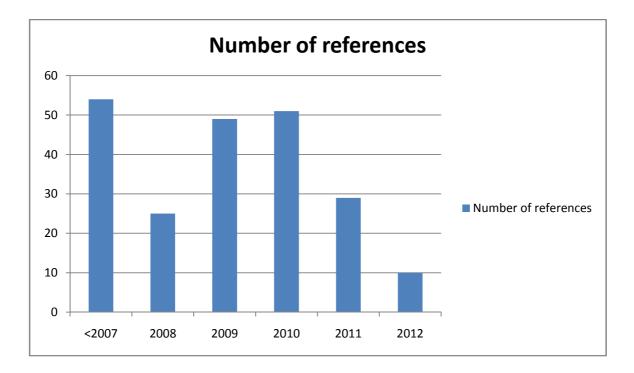

This last decade has known a real explosion in term of research and industrial products in these fields. The evolution of number of hits in the IEEE Xplorer for different NoC searches presented in Figure 1.5 can be a real witness of this trend. We can conclude from this curve that the Hardware field overcomes the Software filed in term of research papers. This can explain the decrease of the NoC and the MPSOC curves by the year of 2010. In fact, there is no meaningful need to increase the number of cores in the same chip if there is no suitable parallel application to use the hardware researches. Moreover, the competition in the MPSOC becomes costly with large Scale designs needing adequate emulation platforms instead of the simulation. Many big companies like INTEL, TILERA, Philips and ST Microelectronics are the leaders in this domain.

Figure 1.5. IEEE Xplorer hits for different "network-on-chip" researches [5]

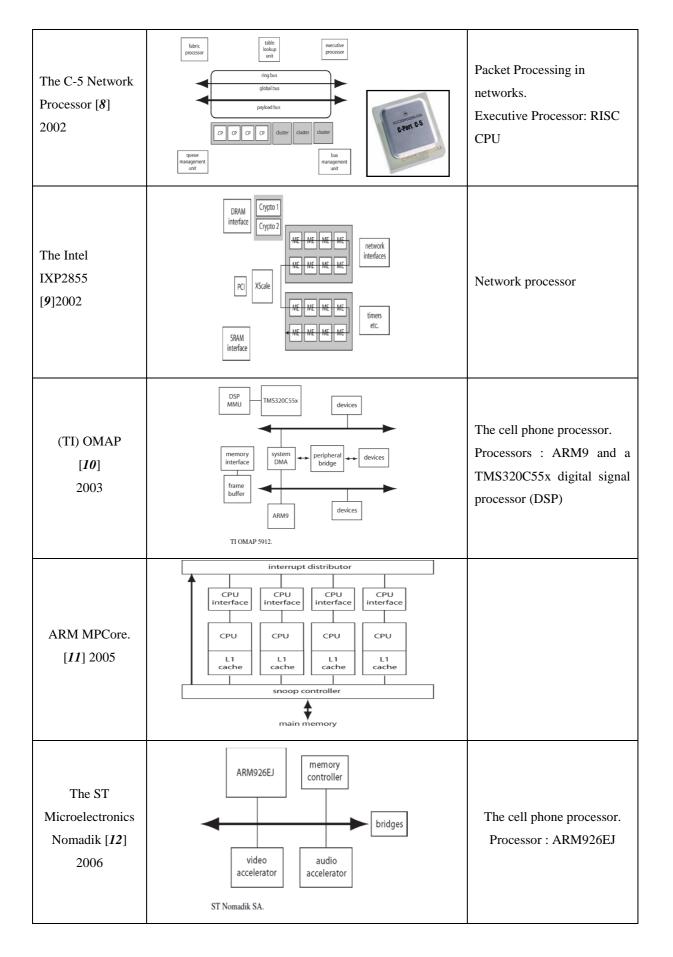

The point-to-point architecture and the bus based communication schemes are considered as the origin of the first MPSOC topologies. We present in Table 1.2 some first industrial chips based on the first MPSOC architectures. Starting from a trivial idea to connect all the cores to each others, the P2P (point to point) method is an easy way to ensure the communication between all the components of a design. This solution can be suitable with few cores and reaches its limitation with larger designs. On the other hand, by using the shared Bus architecture we can connect tens of cores. These two methods suffer from the lack of scalability needed for big applications, but they are still used in the case of few cores in the same chip due to their simplicity in term of design.

| MPSOC                                | Architecture                                                                                                                                                                   | Application                                                                |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Lucent Daytona<br>[ <b>6</b> ]2000   | RISC + SIMD<br>L1 cache<br>L1 cache<br>L1 cache<br>L1 cache<br>RISC + SIMD<br>L1 cache<br>RISC + SIMD<br>RISC + SIMD<br>RISC + SIMD                                            | Daytona was designed for<br>wireless base Stations<br>Processor : SPARC V8 |

| Philips Viper<br>Nexperia[7]<br>2001 | MIPS<br>PR3940<br>C-bridge<br>devices/<br>devices/<br>devices/<br>C-bridge<br>C-bridge<br>C-bridge<br>C-bridge<br>devices/<br>accelerators<br>devices/<br>devices/<br>devices/ | Multimedia processing<br>Processor : MIPS PR3940                           |

Table 1.2. MPSOC state of the Art

| Company          | Name                         | Number of cores | Topology |

|------------------|------------------------------|-----------------|----------|

| INTEL            | Intel IXP2850                | 2               | Busses   |

| Philips [7] 2001 | Philips NexperiaTM PNX-8500. | 2               | Busses   |

| TI 2002 [10]     | TI OMAPTM 5910 2             |                 | Bridge   |

| ST 2003 [12]     | ST NomadikTM                 | 2               | Bridge   |

| Toshiba 2008     | Venezia                      | 8               | Busses   |

| TI 2008          | TMS320VC544                  | 4               | Busses   |

| ARM              | ARM11                        | 4               | Busses   |

#### Table 1.3. MPSOC using busses communication

### 1.3 MPSOC Actual implementation

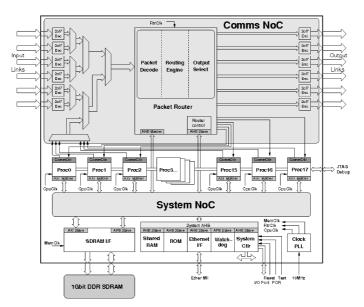

In the actual implementations, the use of the NoC in the MPSOC industry is taking more and more place. With the increasing number of cores, the classical interconnection technologies are not any more sufficient. We present in Table 1.4, a summary of actual MPSOC implementation. We notice that the most popular NoC topology is the Mesh due to its symmetry and to its simple routing algorithm. ARM has produced the Cortex family with the technology 40 nm and below and Tilera has reached the 64 cores with its MPSOC Tile 64 presented in Figure 1.6. We present in Figure 1.7 and Figure 1.8 respectively the architecture and the spot of the chip SpiNNaker including 18 processors.

Table 1.4. Actual MPSOC implementation

|                    | NAME               | Number of cores     | Topology     | Technology        |

|--------------------|--------------------|---------------------|--------------|-------------------|

| 2011[ <b>13</b> ]  | SpiNNaker          | 18                  | Hierarchical | UMC 8-metal layer |

|                    |                    |                     |              | 130nm             |

| 2009 [ <b>14</b> ] | 81.6 GOPS          | 10                  | Mesh         | 180nm             |

| LETI 2009 [15]     | The MAGALI         | 15                  | Mesh         | ST 65nm           |

| ARM 2009[16]       | ARM Cortex-15      | 4 cores per cluster | Mesh         | 40nm & below      |

|                    | Cortex-5, Cortex-8 |                     |              |                   |

| Tilera 2009 [17]   | Tile 64 family     | 64                  | Mesh         | 90nm              |

| MIPS 2009          | MIPS32 1074K       | Dual core           | Bus          |                   |

| MIPS 2009          | MIPS32 1074K       | Dual core           | Bus          |                   |

Figure 1.6. Tile 64 Block Diagram Processor[17]

Figure 1.7. SpiNNaker MPSoC block diagram[13]

Figure 1.8. SpiNNaker MPSoC plot[13]

#### 1.4 MPSOC Design methodologies

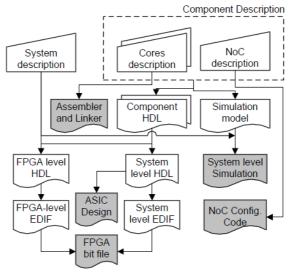

Figure 1.9. Kumar et al MPSOC Design flow[18]

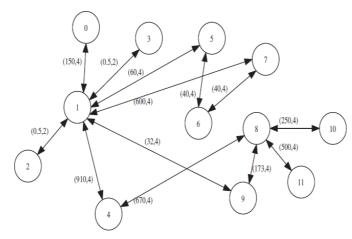

Kumar et al proposed in [19], a full and complete MPSOC design workflow. They proposed to generate a customized NoC and cores in the same workflow design. The Silicon Hive [20] processing core was used. This one is an entire tool chain for rapid design of custom cores. For the NoC generation they proposed to use Æthereal [21] design flow. In Figure 1.9, we present the proposed design flow. The system level description is considered as the input point of the design flow. In fact after the description of the NoC and the cores, the HDL entities are generated together with a simulation model. An .edif file is then generated automatically from Handel-C. These files and with the system level edif file are used during Place and Route (P&R) to obtain the bit file (for FPGA configuration). ASIC design can also be produced from the system-level HDL if desired.

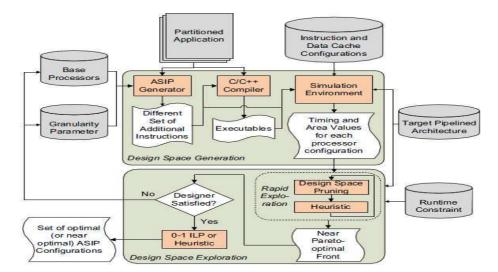

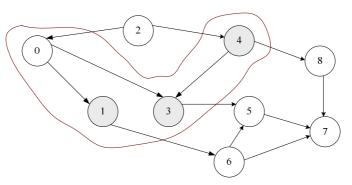

Figure 1.10. Application Specific MPSOC workflow [22]

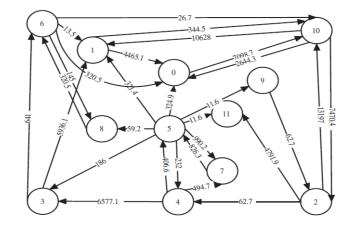

In [22] the proposed design flow aiming to generate an application specific heterogeneous pipelined multiprocessor system, is composed of two separate stages which are: the Design Space Generation and the Design Space Exploration. The designer provides the partitioned application, the pipelined architecture and the runtime constraint as inputs. The different configurations and instructions are determined during the Design Space Generation phase. The user can choose the basic processors as an input to this design flow. In this methodology authors used ASIPs (Application Specific Instruction Set Processors) which is generated using a commercial tool Tensilicia. Thanks to the input parameters, a designer can control the amount of design space to be generated for a particular application. As shown in Figure 1.10, the simulation results are used to record the timing and the area values for all the ASIP configurations which will be used in the exploration phase. In the second phase dedicated to the Design Space exploration, authors proposed to use heuristic approach to run a rapid exploration and to find a near Pareto front. This one will be the new design space to explore in the last step and to find the optimal configuration.

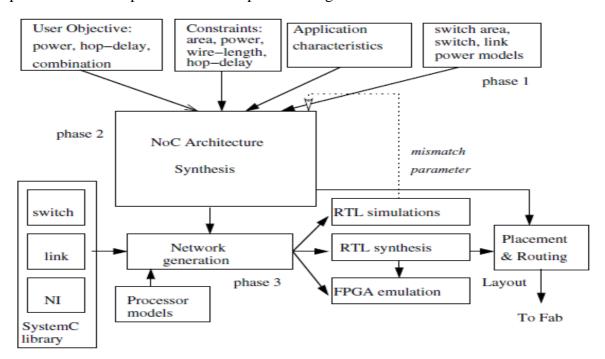

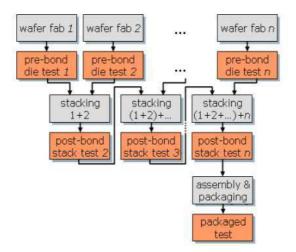

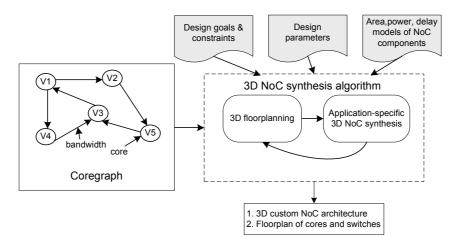

Figure 1.11. Xpipes Synthesis Flow[23]

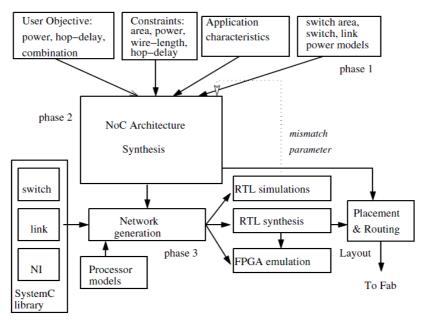

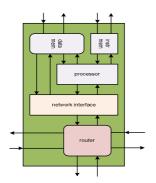

In this paper [23] L. Benini proposed a new MPSOC Design flow based on the NoC architecture synthesis called Xpipes NoC synthesis Design flow. In the first phase, the user specifies the objectives and the constraints that should be satisfied by the designed NoC. The application traffic characteristics, the size of the cores, the area and the power models of the network components are also obtained. In the second phase of the flow, the NoC architecture that optimizes the user objectives and satisfies the design constraints is automatically

synthesized. In the last step, the XpipesLite is used to generate the RTL (SystemC) code of the switches, the network interfaces and the links for the designed topology. The RTL files can be then synthesized and implemented on FPGA. A place and route steps are performed using the industrial tool soc encounter from Cadence. The output of this phase is a total floorplan design specification which can be sent to the fabrication. A real implementation was realized in this work with a design consisting of 30 cores: 10 ARM7 processors with caches, 10 private memories (a separate memory for each processor), 5 custom traffic generators, 5 shared memories and devices to support inter processors communication.

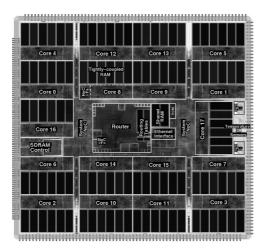

Figure 1.12. STARSOC Design flow overview

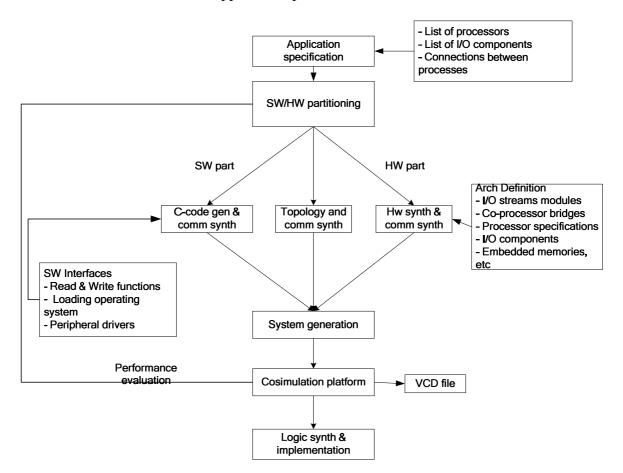

The input of STARSOC [24] design flow is a set of files in C code describing the whole design: the number of processors, their configurations and their interconnections. After the step of the hardware-software partitioning, the hardware part is synthesized into register transfer-level (RTL) architecture, and the software part is distributed on the whole of processors. The software part will be modified to ensure the operation of the hardware call. The RTL code generated by the high-level synthesis and the communication system synthesizer is then downloaded to the FPGA.

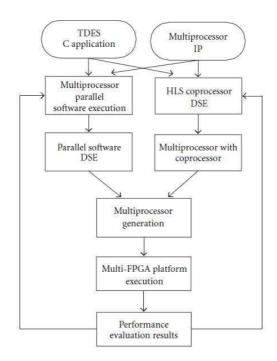

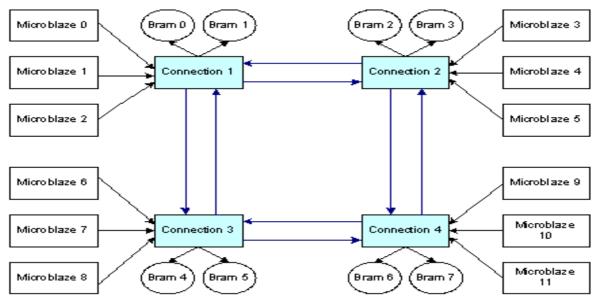

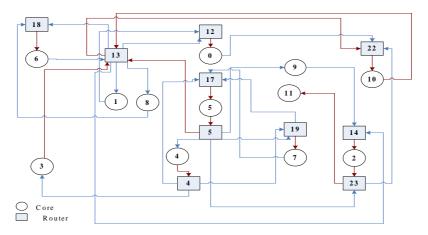

X.Li and O.Hammami presented in their work [25] an automatic Heterogeneous MPSOC design flow on Multi-FPGA. The input of the workflow is an ANSI C code of Triple Data Encryption Standard (TDES) and a small-scale multiprocessor (SSM) IP which will serve as the basic element for the parallelization process. At the first step, software parallelization is explored through direct execution on multi-FPGA platform to find out the best data parallel and the pipelined configuration. While the parallel programming ensures to achieve a maximum design space exploration, the second step is reserved to explore coprocessor – based TDES by incrementally adding TDES C-based synthesis generated coprocessor. The last step compares the two paths and chooses the appropriate one.

Figure 1.13. Automatic heterogeneous design flow [25]

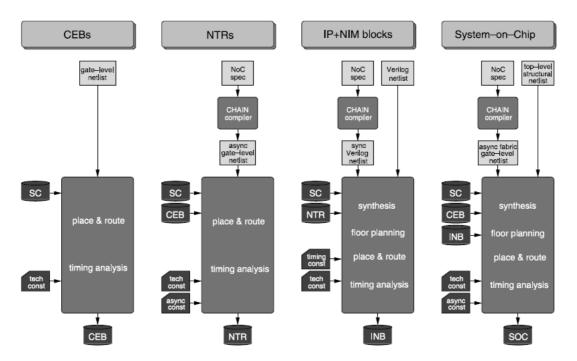

We present in Figure 1.14, the workflow methodology to implement the SpiNNaker MPSOC. Plana et al used a hierarchical place and route method to implement this architecture considered complex. In fact the SpinNNaker includes different IPs devices ARM cores, SDRAM controller, timers, interrupt controller and watchdog as well as the devices developed specifically for SpiNNaker: multicast router, DMA controller and bridge, Ethernet interface, and system controller. In this method the place and route step of the IP blocks was applied separately. This was possible thanks to the fact that the MPSOC has a GALS nature which means that each IP can have its different clock signal.

Figure 1.14. MPSOC Methodology Workflow of SpiNNaker [13]

### 1.5 Conclusion

With reference to the ITRS road map, the number of cores in the same chip will double each about 18 months to reach hundreds of cores by the end of the current decade (see Figure 1.1). Actually, many works have already reached few hundreds of cores in the same chip: for example the number of cores in [26] is equal to 762. With this evolution, classical interconnection methodologies like bus and point to point are not any more possible and other interconnect solutions like the Network On Chip have appeared to deal with those limitations.

We presented in this chapter a brief description of the evolution of the MPSOC during last decades. The evolution of the number of cores is exponential which means that the design complexity is also exponential. We presented the actual MPSOC implementations which have different network On Chip topologies starting from a simple bus connection to a free NoC topology. Designers used different methodologies to implement their own chips; we presented a set of workflows with real implementations.

# Chapter 2 : 2D MPSOC Design and implementation

## 2 . 2D MPSOC Design and implementation

Before moving to 3D IC implementation, we propose in this chapter to test and to verify our MPSOC designs with 2D implementation on FPGA. This approach will guarantee the good functionality of our chip which helps us to solve the MPSOC problems and to only focus on the specific 3D challenges. Thanks to the MPSOC state of the art performed in chapter 1, we choose to study the Butterfly architecture which is an interesting case study for EDA evaluation and of an eventual 3D IC design.

### 2.1 Theoretical Complexity Problems in 2D Design and implementation

To perform an efficient implementation of a 2D Design, we have to deal with the complexity of the workflow steps. We will present the complexity of the basic steps in 2D design implementation on FPGA which are the partitioning, the floorplanning and the place and route.

### The partitioning:

When the Netlist of a component or a design can not fit on a single FPGA the step of partitioning on Multi-FPGA becomes necessary. This operation can be trivial with symmetric and homogenous MPSOC but it becomes a real challenge with asymmetric and heterogeneous architectures. The main goal of this operation is to find a methodology which minimizes the connections between the partitions. In the provided solution, each partition should meet all the design constraints (size, number of external connections...) and get a balanced distribution between the different groups. The problem of VLSI partitioning can be defined by a Hypergraph partitioning. Given a graph G=(V,E), we can model the cells of the Netlist or the components by the set of the vertices V and the nets ( or interconnections) by the set of the edges E. K-way partitions can be defined by the division of the vertices into K groups. This problem is known to be NP-Hard that is why the proposed solutions are based on approximations and heuristic methods [27].

### Placement:

The step of placement on FPGA is the determination of the cell's locations of the Netlist in order to optimize the area and the frequency. Given a Nelist of logic blocks, I/O pads and the set of interconnections between the cells, the output of the placement operation are the coordinates  $(x_{i}, y_{i})$  for each block. This problem is known to be NP Hard which means that no polynomial algorithm is known to propose an exact solution to solve it [**28**].

**3D MPSOC**

#### Routing:

Routing is one of the major steps in 2D FPGA designs as it has an important impact on the performance of the circuit. The success of this operation is affected by the previous step which is the placement. The routing step has been also proved to be NP-hard [29].

The listed steps in the FPGA 2D design are classified in the family of the NP hard problems which means that the optimization in the EDA tools is still possible. In general the common tools used in the synthesis place and route for FPGA like ISE and EDK from Xilinx [*30*], perform each step sequentially which is not an efficient approach as there is a real dependency between the different operations. We propose in this chapter to study the implementation of an MPSOC with 16 masters and 16 slaves based on the Butterfly NoC topology. A real execution on FPGA will be performed.

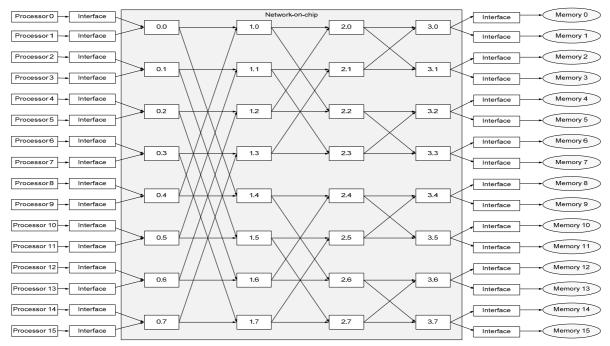

#### 2.2 Regular NoC implementation on FPGA: case study Butterfly

The common NoC topology which is usually used in the literature and in the industrial products is the mesh topology. This one is famous thanks to its symmetric architecture and to the possibility to use a repetitive structure. A NoC with a mesh topology is relatively an easy case study for the EDA tools implementation. In fact, partitioning tools can find a symmetric structure even with a NoC with a very Large Scale MPSOC [26]. In this work [31], authors implemented an MPSOC with 2048 cores. We choose in this chapter, to study the butterfly topology to evaluate the limitation of EDA tools in order to solve the design step problematic. In Table 2.1, we compare the mesh and the butterfly topology. With its asymmetric architecture, the butterfly NoC represents an interesting case study to evaluate the portioning algorithm used in the EDA tools. This NoC is composed of long wires compared to the mesh topology with its equal short links. This characteristic can affect the maximum propagation delay time and the power consumption of the NoC. It can also represent difficulties for the automatic routing algorithms. In the mesh topology, links are bidirectional which is not the case for the butterfly case which needs a request and a response NoC.

| Table 2.1. Comparison Mesh and Butterfly topology |  |

|---------------------------------------------------|--|

|                                                   |  |

| NoC topology | Mesh          | Butterfly      |

|--------------|---------------|----------------|

| Symmetry     | Symmetric     | Asymmetric     |

| Wires        | Short         | Long           |

| Direction    | Bidirectional | unidirectional |

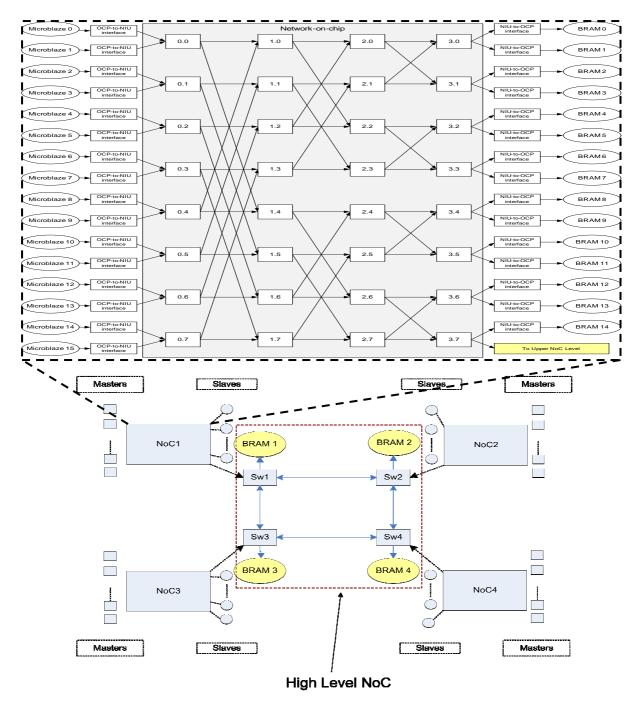

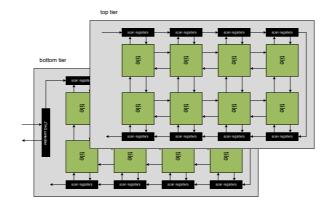

To study in deep the different characteristics of the butterfly architecture, we have designed a NoC with 16 masters and 16 slaves. A such NoC is called 2Ary-4Fly : the term 2Ary refers to the fact that all the used switches have a degree equal to 2, the term 4Fly refers to the number of stages needed which is equal to 4. The NoC's topology is presented in the Figure 2.1; Masters in the left are sharing 16 slave memories presented in the right part of the NoC.

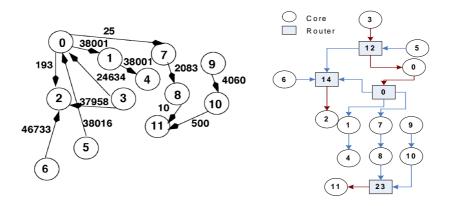

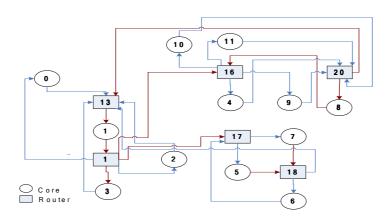

Figure 2.1. MPSOC based Butterfly NoC: 2Ary 4Fly Architecture

The main component of the NoC is the switch, we use the switch library from the company Arteris [32]. This switch presents different options like arbitration, pipelines...In each router we have to modify the routing table according to the physical links and to the position of the switch in the NoC. We can verify from the NoC's architecture that all masters are connected to all the slaves through a single path. According to the routing table and to the message's address, the packets can be routed by the switch. For each switch, we have 2 input ports and 2 output ports. When the switch receives the packets, it can decide thanks to its routing table through which output port to send it. We present the routing tables of each switch in Table 2.2.

| Cores  | Addresses | Cores   | Addresses |

|--------|-----------|---------|-----------|

| Slave0 | 0x0       | Slave8  | 0x800000  |

| Slave1 | 0x100000  | Slave9  | 0x900000  |

| Slave2 | 0x200000  | Slave10 | 0xA00000  |

#### Table 2.2 Address of the slaves

| Slave3 | 0x300000 | Slave11 | 0xB00000 |

|--------|----------|---------|----------|

| Slave4 | 0x400000 | Slave12 | 0xC00000 |

| Slave5 | 0x500000 | Slave13 | 0xD00000 |

| Slave6 | 0x600000 | Slave14 | 0xE00000 |

| Slave7 | 0x700000 | Slave15 | 0xF00000 |

#### Table 2.3. Different switch routing tables

| Switches                                     | TX0                              | TX1                              |

|----------------------------------------------|----------------------------------|----------------------------------|

|                                              | 0x0                              | 0x800000                         |

|                                              | 0x100000                         | 0x900000                         |

|                                              | 0x200000                         | 0x400000                         |

|                                              | 0x300000                         | 0xB00000                         |

| $\{0.0, 0.1, 0.2, 0.3, 0.4, 0.5, 0.6, 0.7\}$ | 0x400000                         |                                  |

|                                              | 0x500000                         | 0xC00000                         |

|                                              | 0x600000                         | 0xD00000                         |

|                                              | 0x700000                         | 0xE00000                         |

|                                              |                                  | 0xF00000                         |

|                                              | 0.0                              | 0x400000                         |

|                                              | 0x0                              | 0x500000                         |

| {1.0,1.1,1.2,1.3}                            | 0x100000                         | 0x600000                         |

|                                              | 0x200000                         | 0x700000                         |

|                                              | 0x300000                         |                                  |

|                                              | 0x800000                         | 0xC00000                         |

|                                              | 0x900000                         | 0xD00000                         |

| {1.4,1.5,1.6,1.7}                            | 0xA00000                         | 0xE00000                         |

|                                              | 0xB00000                         | 0xF00000                         |

|                                              | 0x0                              | 0x200000                         |

| {2,0,2.1}                                    | 0x100000                         | 0x300000                         |

|                                              | 0x400000                         | 0x600000                         |

| {2,2,2.3}                                    | 0x500000                         | 0x700000                         |

|                                              | 0x800000                         | 0xA00000                         |

| {2.4,2.5}                                    | 0x900000                         | 0xB00000                         |

|                                              | 0xC00000                         | 0xE00000                         |

| {2.6,2.7}                                    | 0xD00000                         | 0xF00000                         |

| 3.0                                          | 0x0                              | 0x100000                         |

| 3.1                                          | 0x200000                         | 0x300000                         |

| 3.2                                          | 0x400000                         | 0x500000                         |

|                                              |                                  |                                  |

|                                              |                                  |                                  |

| 3.2       3.3       3.4                      | 0x400000<br>0x600000<br>0x800000 | 0x500000<br>0x700000<br>0x900000 |

| 3.5 | 0xA00000 | 0xB00000 |

|-----|----------|----------|

| 3.6 | 0xC00000 | 0xD00000 |

| 3.7 | 0xE00000 | 0xF00000 |

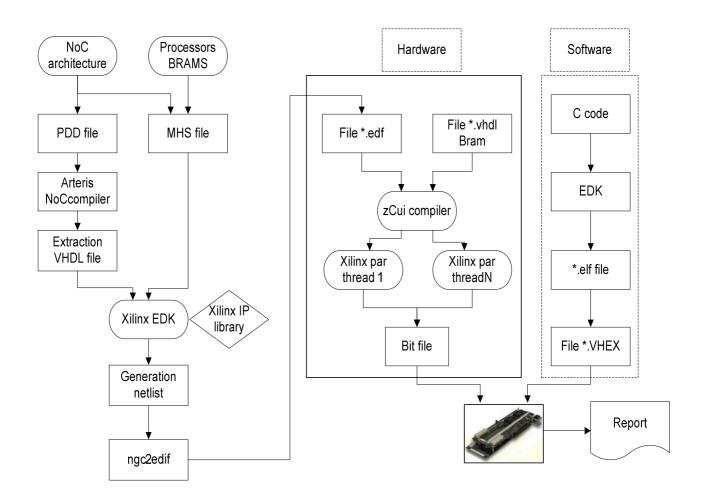

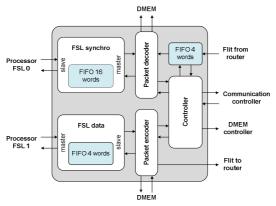

We add our NoC as an IP in the EDK project to connect 16 Microblaze processors which are the masters to sixteen block memories representing the 16 slaves. To evaluate the execution time of the design we add a timer which is connected to an OPB (On-Chip Peripheral Bus). We start by the hardware part of the design. After we generate the Netlist of the project, we use the command *ngc2edif* to transform the Netlist to edif files used by zCui. This one is a compiler tool designed by EVE company [33] to synthesis the DUT (Design Under Test) by calling Xilinx tools. At the end, it generates a bit file and several reports describing the FPGA resources used after the place and route on the board. For each Microblaze, we create a software application in the EDK project. In each application we add a C code and header files to describe the tasks to be performed by the processor. Once we define a software for each processor, EDK calls the C code compiler and generates \*.elf files. We transform these files to \*.vhex files which can be run on the board. At this level we have now hardware and software files ready to be run on the zebu board. We call the command zRun to make the execution on the board. Eve tool offers the possibility to use static and dynamic probes. In our case, we use a static probe to capture the end of the execution time. In fact, the run will stop when the condition of stop which is related to the probe value will be true. Then we can read the execution time needed for the program to be complete. A summary of this workflow is presented in Figure 2.2

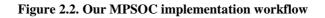

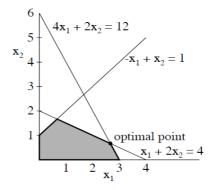

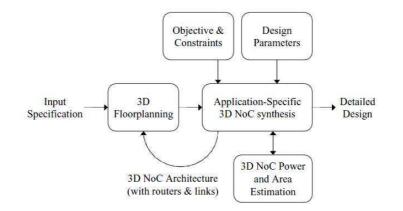

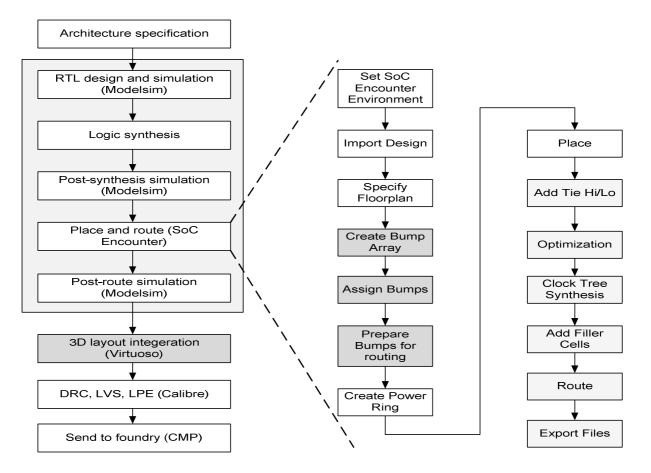

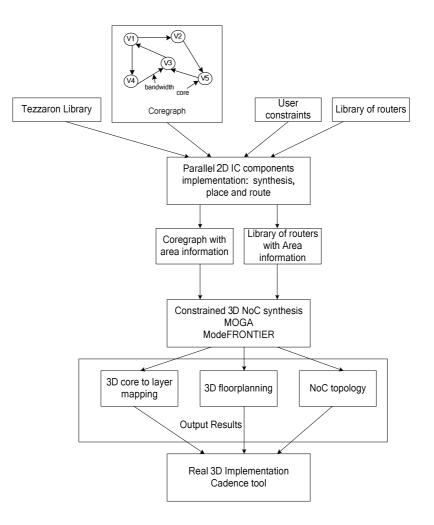

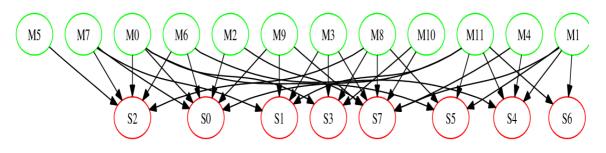

#### 2.2.1 Synthesis results