# Methods and architectures based on modular redundancy for fault-tolerant combinational circuits

Tian Ban

#### ▶ To cite this version:

Tian Ban. Methods and architectures based on modular redundancy for fault-tolerant combinational circuits. Other. Télécom ParisTech, 2012. English. NNT: 2012ENST0038. pastel-00933194

### HAL Id: pastel-00933194 https://pastel.hal.science/pastel-00933194

Submitted on 20 Jan 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Doctorat ParisTech**

### THÈSE

pour obtenir le grade de docteur délivré par

### **TELECOM ParisTech**

Spécialité « Communications et Electronique »

présentée et soutenue publiquement par

#### Tian BAN

le 4 septembre 2012

# Méthodes et Architectures basées sur la Redondance Modulaire pour Circuits Combinatoires Tolérants aux Fautes

Directrice de thèse : Mme. Lirida NAVINER

Jury

M. Patrick Girard, Directeur de Recherche, CNRS, LIRMM

M. Emmanuel Casseau, Professeur, ENSSAT, INRIA/IRISA

M. Habib Mehrez, Professeur, UPMC, LIP6

M. Costin Anghel, Professeur associé, ISEP

Mme. Lirida Naviner, Professeur, Télécom ParisTech

Rapporteur Rapporteur Examinateur Examinateur Directrice de thèse

#### **TELECOM ParisTech**

## **Thèse**

Methods and Architectures based on Modular Redundancy for Fault-Tolerant Combinational Circuits

**Tian BAN**

Directrice de thèse

Pr. Dr. Lirida NAVINER

«To

My Father

Mr. BAN Tong

and

My Mother

Mrs. ZHU Zhaoyun »

## **Acknowledgments**

Tout d'abord, je tiens à remercier ma directrice de thèse, Mme. Lirida Naviner, qui a dirigé mes travaux de recherche avec toujours beaucoup de patience et disponibilité. En particulier, j'ai beaucoup apprécié la liberté qu'elle m'a accordée pour étudier différentes pistes (qu'elles soient incertaines ou de sentiers plus cadrés) toujours en assurant mon encadrement et avec le souci de me faire acquérir une vision globale de mon travail.

Je remercie M. Patrick Girard, M. Emmanuel Casseau, M. Habib Mehrez et M. Costin Anghel pour avoir accepté d' être membres de mon jury de thèse, en accordant leur temps et leur expérience.

Merci également à Dr. Jean-François Naviner, Dr. Hervé Petit et Dr. Philippe Matherat. Vos idées et suggestions ont renforcé le contenu de ce travail. Je voudrais aussi remercier tous les membres de notre équipe de recherche NanoElec (l'équipe "Nouvelles Problématiques de l'Electronique"), pour leur soutien pendant ma thèse.

Merci à ceux qui ont contribué, directement ou indirectement, à la réussite de cette thèse. Mon professeur de Français Langue Etragère, Julie Montagu, qui m'a appris à aimer cette belle langue. Les personnels administratifs de Télécom ParisTech, Florence Besnard, Martha Dwyer, Fabienne Lassausaie et Nazha Essakkaki, qui enlèvent les tracas de différents types de bureaucraties.

Un grand merci aux personnels administratifs du département COMELEC, en particulier Chantal Cadiat, Zouina Sahnoune et Yvonne Bansimba, qui ont fourni diverses aides pour mon travail et ma vie à l'école.

J'ai eu le plaisir de collaborer avec tous mes collègues venus de divers horizons. Etudier, travailler et déjeuner avec vous m'a offert une excellente occasion de mieux connaître différentes cultures et m'a fait voir le monde différemment.

Mes amis chinois dans le monde entier, je vous remercie pour votre disponibilité immédiate chaque fois j'ai eu des difficultés. Des remerciements particuliers à Feng Yan, Jian Wang et Kun Lee, en France, aux Etats-Unis et la Chine, respectivement. Je me permets de vous décrire en ramassant un mot technique dans ma thèse, fiable.

Un grand merci tout particulier à mes parents. Le talent, l'amour et la compréhension dont vous avez fait toujours preuve sont indispensables pour chacune de mes réalisations. La fin de ma scolarité vous semblait parfois lointaine... elle a pris presqu'un quart de siécle, mais voici qu'elle arrive!

Enfin, je tiens à remercier le CSC (China Scholarship Council) et le projet STIC AmSud Nanora-

dio pour leur soutien financier au cours de mon travail de recherche.

At the end of my thesis, I would like to thank my advisor, Mrs. Lirida Naviner, for her excellent guidance, patience and assistance while I pursued this research. In particular, thank you for ensuring that I saw the big picture and allowing me the absolute freedom to study the different tracks, sometimes uncertain paths even occasional stray.

An additional thank you to Mr. Patrick Girard, Mr. Emmanuel Casseau, Mr. Habib Mehrez and Mr. Costin Anghel for serving on my committee. Thank you for your time and experience on this thesis.

The same acknowledgments are due to Dr. Jean-François Naviner, Dr. Hervé Petit and Dr. Philippe Matherat. Your insights and suggestions have strengthened the content of this work. I would like to say thank you to all the former and present members in our research team NanoElec (Team of new issues in electronics), for their support during my thesis.

Thank you for those who contributed, directly or indirectly, to the success of this thesis. To my french teacher, Julie Montagu, who taught me to love this beautiful language. To the administrative staffs of Télécom ParisTech, Florence Besnard, Martha Dwyer, Fabienne Lassausaie and Nazha Essakkaki, who remove the hassles of different kinds of bureaucracies.

To the administrative staffs of COMELEC department, particularly Chantal Cadiat, Zouina Sahnoune and Yvonne Bansimba: thank you for providing miscellaneous assistances as I used and abused during my work and life on campus.

I am very happy to work with my colleagues from various backgrounds. Studying, working, lunch and coffee break with you offers me an excellent opportunity to learn about different cultures and made me see the world differently.

My Chinese friends all around the world, thank you for your immediate availability each time I am in difficulty. Particular thanks to Feng Yan, Jian Wang and Kun Lee, in France, United States and China respectively. Please allow me to describe you by picking up a technical word in my thesis, reliable.

The most special thanks are undoubtedly due to my parents. Talent, love and understanding derived from you enabled each achievement from kindergarten to graduate school. While you may complain sometimes that the end of my schooling seems to be unforeseeable, now it is the end, yet a bit long - nearly a quarter of century.

Lastly, I would like to thank CSC (China Scholarship Council) and STIC AmSud Nanoradio Project for their financial support during my research work.

# **Contents**

| Ac | Acknowledgments               |           |                                              |    |

|----|-------------------------------|-----------|----------------------------------------------|----|

| Sy | Symbols and Abbreviations xix |           |                                              |    |

| Al | ostrac                        | t         |                                              | 1  |

| Fr | ench (                        | Summa     | ry                                           | 3  |

| 1  | Intro                         | oduction  | n                                            | 21 |

|    | 1.1                           | Motiva    | tions                                        | 21 |

|    | 1.2                           | Object    | ives                                         | 22 |

|    | 1.3                           | Organi    | zation of the thesis                         | 23 |

| 2  | Relia                         | ability I | mprovement Techniques                        | 25 |

|    | 2.1                           | Introdu   | nction                                       | 25 |

|    | 2.2                           | Prelim    | inaries of reliability                       | 25 |

|    |                               | 2.2.1     | Defect, fault, error and failure             | 25 |

|    |                               |           | 2.2.1.1 SEUs and SETs under DSM technologies | 27 |

|    |                               |           | 2.2.1.2 Modeling of faults                   | 27 |

|    |                               | 2.2.2     | Measures and metrics related to reliability  | 29 |

|    | 2.3                           | Reliabi   | ility evaluation of logic circuits           | 33 |

|    |                               | 2.3.1     | Analytical-based way                         | 34 |

|    |                               | 2.3.2     | Simulation-based way                         | 35 |

|    |                               | 2.3.3     | Hybrid way                                   | 36 |

|    |                               | 2.3.4     | Comparison of existing techniques            | 36 |

|    |                               | 2.3.5     | Comments on PGM approach                     | 37 |

|    | 2.4                           | Reliabi   | ility Improvement based on redundancy        | 39 |

|    |                               | 2.4.1     | Types of redundancy                          | 39 |

|    |                               | 2.4.2     | Hardware fault tolerance                     | 40 |

|    |                               | 2.4.3     | Reliability of M-of-N systems                | 41 |

X CONTENTS

|   |      | 2.4.3.1 N-tuple Module Redundancy                                      | 41 |

|---|------|------------------------------------------------------------------------|----|

|   |      | 2.4.3.2 TMR reliability with repair                                    | 43 |

|   | 2.5  | Trade-offs between reliability improvement and performance degradation | 45 |

| 3 | Reli | ability Enhancement based on Significance                              | 51 |

|   | 3.1  | Introduction                                                           | 51 |

|   | 3.2  | Identification of critical blocks                                      | 51 |

|   |      | 3.2.1 A simple example                                                 | 52 |

|   |      | 3.2.2 Sensitivity and eligibility concept                              | 53 |

|   |      | 3.2.3 Block grading according to design requirement                    | 54 |

|   | 3.3  | Block Grading                                                          | 55 |

|   |      | 3.3.1 Block grading in cascade structures                              | 55 |

|   |      | 3.3.2 Block grading in general cases                                   | 59 |

|   |      | 3.3.2.1 Experimental metric for sensitivity classification             | 59 |

|   |      | 3.3.2.2 Experimental metric for eligibility classification             | 61 |

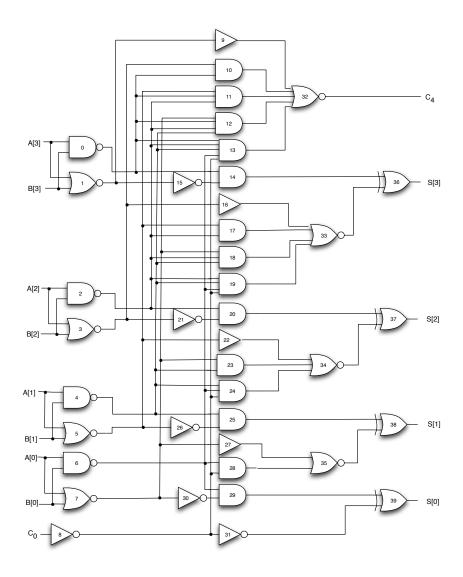

|   |      | 3.3.2.3 Implementation on 74283 fast adder                             | 61 |

|   | 3.4  | Practical Applications of Block Significance                           | 64 |

|   |      | 3.4.1 Using Sensitivity for Monitoring                                 | 64 |

|   |      | 3.4.2 Using Eligibility for Reliability Improvement                    | 64 |

| 4 | Prog | gressive Approach for Modular Redundancy                               | 67 |

|   | 4.1  | Introduction                                                           | 67 |

|   | 4.2  | Progressive modular redundancy approach                                | 68 |

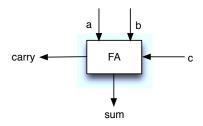

|   |      | 4.2.1 Progressive triple module redundancy: PTMR                       | 69 |

|   |      | 4.2.2 Progressive mixed module redundancy: PMMR                        | 70 |

|   | 4.3  | Validation of progressive redundancy adding: PTMR and PMMR             | 72 |

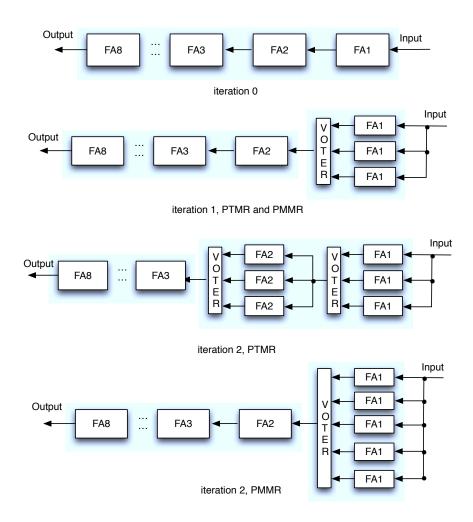

|   |      | 4.3.1 PTMR implementation                                              | 73 |

|   |      | 4.3.2 PMMR implementation                                              | 73 |

|   |      | 4.3.3 Remarks                                                          | 75 |

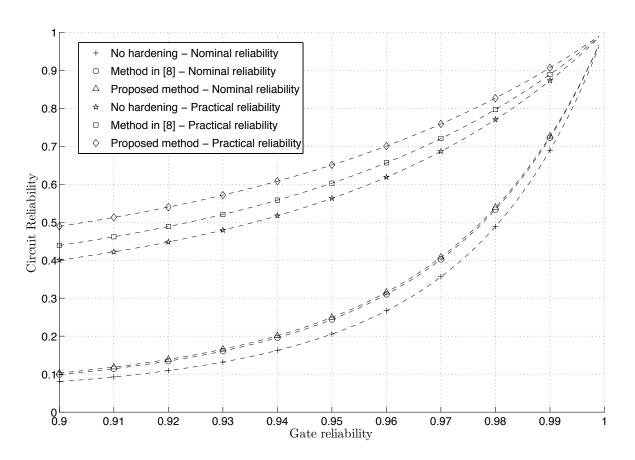

|   |      | 4.3.4 More examples and comparisons                                    | 77 |

|   | 4.4  | Critical errors mitigation in digital IPs                              | 78 |

|   |      | 4.4.1 Cost function and TMR configuration                              | 78 |

|   |      | 4.4.2 Practical metric for reliability evaluation                      | 79 |

|   |      | 4.4.3 Selectively applying TMR based on bit significance               | 80 |

|   |      | 4.4.4 Comparison                                                       | 81 |

|   |      |                                                                        |    |

| 5   | Erro   | or Char | acteristics of Majority Voter                              | 83  |

|-----|--------|---------|------------------------------------------------------------|-----|

|     | 5.1    | Introdu | <u>uction</u>                                              | 83  |

|     | 5.2    | Voters  |                                                            | 83  |

|     |        | 5.2.1   | Introduction of voters                                     | 83  |

|     |        | 5.2.2   | Voting mechanisms for digital circuits                     | 84  |

|     |        | 5.2.3   | Majority voting configurations                             | 84  |

|     |        | 5.2.4   | Single-gate voter structure in Nanoelectronics             | 85  |

|     | 5.3    | Analys  | sis of voter reliability                                   | 86  |

|     |        | 5.3.1   | Motivation                                                 | 86  |

|     |        | 5.3.2   | Preliminaries                                              | 86  |

|     |        |         | 5.3.2.1 Signal probability                                 | 87  |

|     |        |         | 5.3.2.2 Errors in the gate and in the signal               | 87  |

|     |        | 5.3.3   | Minimum functional reliability required for majority voter | 88  |

|     |        | 5.3.4   | Signal probability limitation and upper error bound        | 90  |

|     |        | 5.3.5   | Application                                                | 92  |

|     | 5.4    |         | ble fault-tolerant voter structure in TMR                  | 94  |

|     |        | 5.4.1   | TMR based on imperfect majority voter                      | 94  |

|     |        | 5.4.2   | Alternative majority schemes                               | 95  |

|     |        | 5.4.3   | A novel simple majority voter                              | 96  |

|     |        | 5.4.4   | Analysis and Results                                       | 97  |

| Co  | nclus  | sion    |                                                            | 97  |

| A   | App    | endix   |                                                            | 103 |

|     | A.1    |         | for Inputs Sensitivity Analysis by Boolean Difference      | 103 |

|     |        | A.1.1   | Introduction                                               | 103 |

|     |        | A.1.2   | General usage of the tool                                  | 104 |

|     |        | A.1.3   | Variables                                                  | 104 |

|     |        | A.1.4   | Algorithms                                                 | 104 |

|     |        | A.1.5   | Function descriptions and flow charts                      | 105 |

| Bil | bliogr | aphy    |                                                            | 116 |

xii CONTENTS

# **List of Figures**

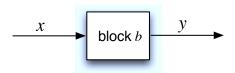

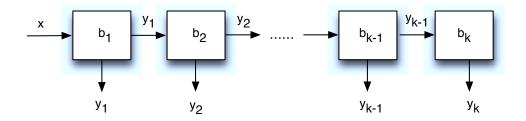

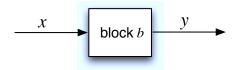

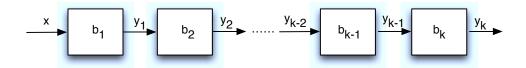

| 1    | Génération des signaux de sortie $y$ du signal d'entrée $x$ traitée par l'opérateur <b>block b</b> . | 5  |

|------|------------------------------------------------------------------------------------------------------|----|

| 2    | Techniques de tolérance aux fautes [1,2])                                                            | 7  |

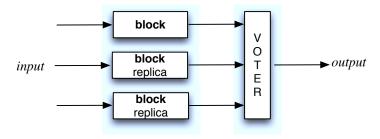

| 3    | Schéma général pour la NMR                                                                           | 8  |

| 4    | Fiabilité pour deux stratégies de mise en oeuvre : module unique (ligne continue) et                 |    |

|      | TMR (ligne pointillée)                                                                               | 8  |

| 5    | Exemple de structure en cascade                                                                      | 10 |

| 6    | Schéma général pour l'injection de fautes et l'analyse des masquage                                  | 10 |

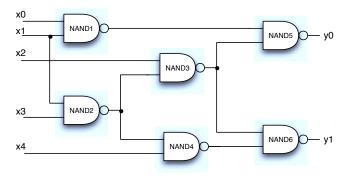

| 7    | Circuit C17                                                                                          | 11 |

| 8    | Workflow pour la méthode proposée                                                                    | 16 |

| 9    | La fiabilité des électeurs requis dans le systéme de NMR                                             | 17 |

| 10   | Schémas classiques pour arbitre dans schéma TMR avec stratégie de vote par majorité.                 | 18 |

| 11   | Structure d'arbitre tolérant aux fautes (NFTVC) [92]                                                 | 19 |

| 12   | Schéma proposé pour l'arbitre tolérant aux fautes                                                    | 19 |

| 13   | Exemple d'utilisation de l'arbitre tolérant aux fautes dans un demi-additionneur                     | 19 |

| 14   | Courbes de fiabilité pour les classiques (ligne continue), NFTC (ligne pointillée) et                |    |

|      | l'électeur proposée (ligne pointillée)                                                               | 20 |

| 2.1  | System States and state transitions in the multi-level model of reliability                          | 26 |

| 2.2  | Mechanism of SEUs in digital IPs                                                                     | 27 |

| 2.3  | Double exponential fault model                                                                       | 28 |

| 2.4  | Series and parallel systems                                                                          | 30 |

| 2.5  | Generation of the output signal $y$ from the input signal $x$ processed by the digital               |    |

|      | block <i>b</i>                                                                                       | 32 |

| 2.6  | A NAND Gate.                                                                                         | 38 |

| 2.7  | An OR Gate.                                                                                          | 38 |

| 2.8  | Fault-tolerant technique and its applicability (adapted from [1,2])                                  | 40 |

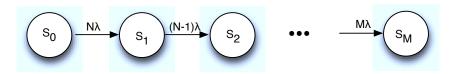

| 2.9  | Markov diagram for M-of-N configuration.                                                             | 41 |

| 2.10 | General scheme for NMR based on majority voter.                                                      | 42 |

xiv LIST OF FIGURES

| 2.11 | Reliability curves for two implementations strategies: unique module (continuous               |

|------|------------------------------------------------------------------------------------------------|

|      | line) and TMR (dashed line)                                                                    |

| 2.12 | A Markov model for a TMR system with repair [3]                                                |

| 2.13 | Example circuit of adding redundant wires [4]                                                  |

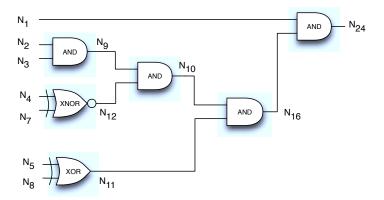

| 2.14 | Combinational circuit and its graphical representation [5]                                     |

| 2.15 | Scheme of selective fault tolerance                                                            |

| 3.1  | Cascade structure                                                                              |

| 3.2  | A kind of cascade structure                                                                    |

| 3.3  | TMR Principle                                                                                  |

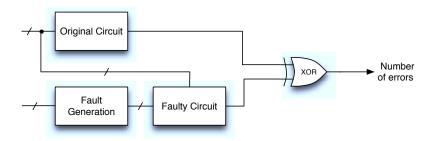

| 3.4  | Fault injection and masks analysis                                                             |

| 3.5  | An illustrated example: Circuit C17                                                            |

| 3.6  | Nonlinear Reliability Growth based on TMR Techinque                                            |

| 3.7  | 74283 gate-level schematic                                                                     |

| 3.8  | Workflow of reliability significance concept applied to monitoring and reliability improvement |

| 4.1  | Workflow for the proposed method                                                               |

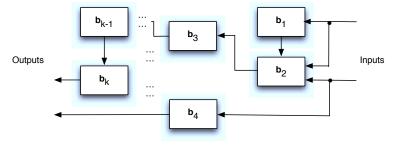

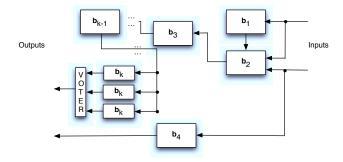

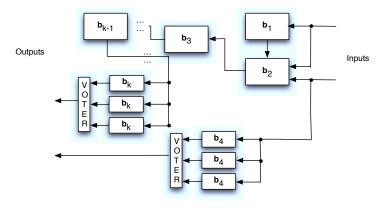

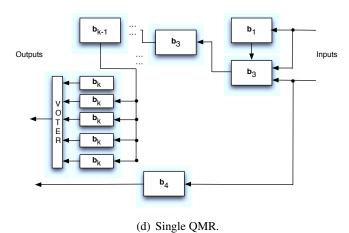

| 4.2  | Different redundancy architectures of generalized circuits                                     |

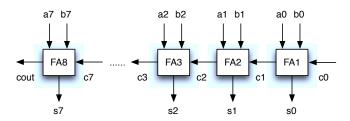

| 4.3  | A 8-bits carry ripple adder                                                                    |

| 4.4  | A full adder block model                                                                       |

| 4.5  | Inputs multiply by PTM of a full adder                                                         |

| 4.6  | Iterations of PMMR implemented on RCA8                                                         |

| 4.7  | Simulation results for the ISCAS 74283                                                         |

| 5.1  | Designs of 2-level majority voter                                                              |

| 5.2  | Scheme of a single gate majority voter                                                         |

| 5.3  | Architecture of a single gate majority voter                                                   |

| 5.4  | Inputs multiply by PTM of a majority voter                                                     |

| 5.5  | Signal and error probability of inputs, error probability of gate and in the outputs 88        |

| 5.6  | Faulty gate model equivalent to Fig. 5.5                                                       |

| 5.7  | Voter reliability required in NMR system                                                       |

| 5.8  | $\varepsilon_{in}$ varies with $\varepsilon$ and $p$                                           |

| 5.9  | $\varepsilon_{in}$ varies with $\varepsilon$ under given $p$                                   |

| 5.10 | An illustrative function module                                                                |

| 5.11 | Reliability curves for TMR with ideal (continuous line) and faulty (dashed line) voter. 94     |

| 5.12 | Conventional schemes for majority voter in TMR                                                 |

| 5.13 | Kshirasgar's scheme for the majority voter (NFTVC)                                             |

| 5.14        | Proposed scheme for the majority voter                                             | 97  |

|-------------|------------------------------------------------------------------------------------|-----|

| 5.15        | Half adder in TMR using proposed voter                                             | 98  |

| 5.16        | Reliability curves for conventional (continuous line), NFTVC (dashed line) and the |     |

|             | proposed voter (dotted line).                                                      | 98  |

|             |                                                                                    |     |

| <b>A</b> .1 | An illustrative function module                                                    | 103 |

| A.2         | Flow chat of main function                                                         | 105 |

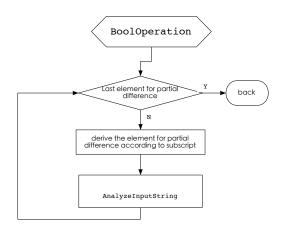

| A.3         | Flow chat of BoolOperation function                                                | 106 |

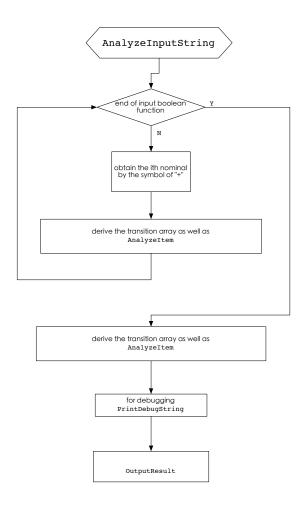

| A.4         | Flow chat of AnalyzeInputString function                                           | 106 |

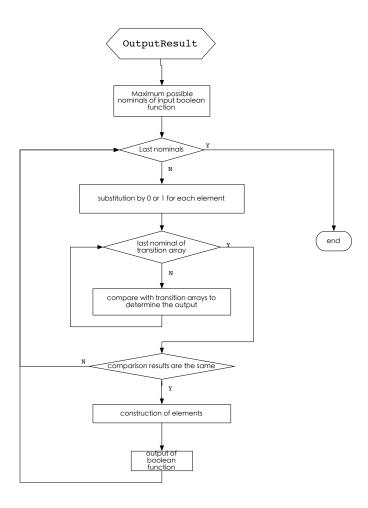

| A.5         | Flow chat of OutputResult function                                                 | 107 |

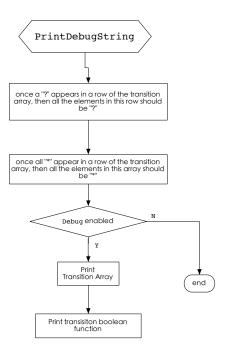

| A.6         | Flow chat of PrintDebugString function                                             | 108 |

# **List of Tables**

| 1   | La comparaison des méthodes représentatives d'évaluation de fiabilité         | 6  |

|-----|-------------------------------------------------------------------------------|----|

| 2   | Classement des sous-blocs du circuit C17 en fonction de la sensibilité        | 11 |

| 3   | Classement des sous-blocs du circuit C17 en fonction de l'éligibilité         | 12 |

| 4   | Exécution de l'algorithme PTMR.                                               | 13 |

| 5   | Résultats de l'application de l'approche <i>PTMR</i> sur le circuit C17       | 13 |

| 6   | Table de vérité pour un arbitre basé sur le vote majoritaire.                 | 14 |

| 7   | Résultats synthétisés dans ASIC (RTL Compiler)                                | 15 |

| 2.1 | Comparison of representative reliability evaluation methods                   | 37 |

| 2.2 | System states of a markov model for a TMR.                                    | 43 |

| 3.1 | Results for $\mathcal C$ with $y=y_8$ and different values of $q_i$           | 58 |

| 3.2 | Results for $C$ with $y = y_8y_7 \cdots y_2y_1$ and $q_i = q, \forall i$      | 58 |

| 3.3 | Results for $C$ with $y = y_8y_7 \cdots y_2y_1$ and different values of $q_i$ | 59 |

| 3.4 | Fault Models                                                                  | 60 |

| 3.5 | Results of sensitivity rank of C17.                                           | 61 |

| 3.6 | Results of eligibility rank of C17                                            | 61 |

| 3.7 | Results for sensitivity factor of 74283 benchmark circuit                     | 62 |

| 4.1 | Algorithm execution for PTMR.                                                 | 70 |

| 4.2 | Algorithm execution for PMMR where $K=8.$                                     | 72 |

| 4.3 | Results of <i>PTMR</i> approach on C17.                                       | 73 |

| 4.4 | Results of <i>PMMR</i> approach on RCA-8                                      | 76 |

| 4.5 | Results and comparisons of Progressive Modular Redundancy                     | 78 |

| 4.6 | Reliability for the output bits of three structures for a 4-bit adder         | 80 |

| 4.7 | Error analysis for the gates of 74283 fast adder                              | 81 |

| 4.8 | Reliability comparison of 74283 fast adder.                                   | 82 |

| 5.1 | Minimum Voter Reliability                                                     | 89 |

| 5.2 | True table for majority voter                                                 | 95 |

| xviii | LIST OF TABL                               | ES |

|-------|--------------------------------------------|----|

| 5.3   | Results synthesized in ASIC (RTL Compiler) | 98 |

# **Symbols and Abbreviations**

A Area (area cost)

C Cost (overall cost)

$arepsilon_i$  Error probability of inputs/outputs

$arepsilon_g$  Gate error probability e(i) Eligibility of block

$p_i$  Error probabilities of inputs/outputs

q Reliability of block

$\mu,\mu(t)$  Repair rate  $\lambda,\lambda(t)$  Failure rate R,R(t) Reliability

ADC Analog to digital converter

ADD Algebraic decision diagram

ASIC Application-specific integrated circuit

BDD Binary decision diagram

BDEC Boolean difference-based error calculator

BN Bayesian network

BSC Binary symmetric channel

CED Concurrent error detection

CMOS Complementary metal oxide semiconductor

DSM Deep submicron

DSP Digital signal processing ECC Error correcting code

EDA Electronic design automation

EDC Error detection code

FET Field-effect transistor

FIFA Fault-injection-fault-analysis

FPGA Field-programmable gate array

HDL Hardware description language

IC Integrated circuits

IP Intellectual property

ISCAS International symposium on circuits and systems

ITM Ideal transfer matrix

ITRS International technology roadmap for semiconductors

LUT Look-up table MC Monte carlo

MOS Metal oxide semiconductor

MOSFET Metal oxide semiconductor FET

MRF Markov random field

MTBF Mean time between failure

MTTF Mean time to failure

MTTR Mean time to repair

NIR N-tuple interwoven redundancy

NMR N-tuple modular redundancy

PBR Probabilistic binomial reliability model

PGM Probabilistic gate model

PLA Programmable logic array

PLD Programmable logic device

PMR Progressive modular redundancy

PMMR Progressive mixed modular redundancy

PTM Probabilistic transfer matrix

PTMR Progressive modular redundancy

QCA Quantum cellular automaton

RE Relative error

RTD Resonant tunneling devices

RTL Register-transfer level

SCM Stochastic computational model

SER Soft error rate

SET Single-electron transistor

SET Single event transient

SEU Single event upset

SFT Selective fault tolerance

SPR Signal probability reliability model

SRAM Static random access memory

TIR Triple interwoven redundancy

TMR Triple modular redundancy

VHDL Very high speed integrated circuit hardware description language

VLSI Very large scale integration

### **Abstract**

Human have to ponder on the reliability of each tool they have created, and cope with the consequences of the failure caused by these tools. Electronic devices are not exceptions. Downscaling of technology brings with the invention of devices into deep submicrion (DSM) CMOS and even non-CMOS nanometer dimensions. While there are a lot of advantages (smaller size, higher speed, lower power consumption as well as better performance in function diversity), downscaling of geometries also has some drawbacks affecting the system reliability.

Under the circumstances of miniaturization, Single-Event Transient (SET) is much easier to produce unexpected values called *soft errors*. Historically, soft errors were often masked before reaching an output or a storage element. However, aforementioned technological trends such as faster clock rates, smaller device sizes, lower supply voltages, and shallower logic depths are drastically reducing SET masking, and thus are reducing reliability of digital IPs dramatically. International Technology Roadmap for Semiconductors (ITRS) depicts that reliability is emerging as a main threat to the future electronic systems and it should be considered as a very important parameter in the phase of predesign.

Under the foreseeable fact that probability of failure is getting higher, reliable digital IPs will be made of unreliable components. As a matter of fact, a 100% reliability of digital IPs is not only very consuming in performances but also might be impractical. Consequently, what we are pursuing is to maintain a high reliability of digital IPs while keeping extra expense accepted. This aim fosters several issues related to fault-tolerant designs in this thesis.

The most common approach for fault tolerance consists of incorporating redundancy, either static or dynamic or hybrid of the both. Aiming at economical design, a lot of work have been studied in recent years to find a good trade-off between high reliability and better performance. In this context, we try to find feasible methods that could build fault-tolerant digital IPs based on smaller redundancy factors.

Inspired by Pareto principle, identifying and classifying critical constituent blocks of digital IPs should be very meaningful. This thesis presents two new classification criteria regarding the significance of a block with respect to the reliability of a circuit. *Sensitivity* gives the criticality of each block for the circuit reliability and *Eligibility* indicates which priority should be given to each block in a process of adding redundancy. How to acquire the ranking depends on the property of the combinational

2 ABSTRACT

circuit (structure, individual reliability, etc.). The proposed two concepts provide key information for the designer who looks for efficient fault-tolerant designs.

The aforementioned block grading based on *Sensitivity* and *Eligibility* brings in a straightforward efficient method to select the best subset: Progressive Module Redundancy (PMR). This method proposes to build a fault-tolerant system step by step, that is in a *progressive* way.

It is obvious that we could have different redundant configurations under the same or similar redundant factor. This progressive module redundancy presents a shortcut by avoiding analyses of all the possible redundant architectures exhaustively. It points out a new direction of economical redundant fault-tolerant designs and it is applicable at all the hierarchical design levels (logic gate, arithmetic and processor).

In this thesis, we mainly take into account the representative technique Triple Module Redundancy (TMR) as the reliability improvement technique. A voter is an necessary element in this kind of fault-tolerant architectures. The importance of reliability in majority voter is due to its application in both conventional fault-tolerant design and novel nanoelectronic systems. The property of a voter is therefore a bottleneck since it directly determines the whole performance of a redundant fault-tolerant digital IP (such as a TMR configuration).

Obviously, the efficacy of TMR is to increase the reliability of digital IP. However, TMR sometimes could result in worse reliability than a simplex function module could. A better understanding of functional and signal reliability characteristics of a 3-input majority voter (majority voting in TMR) is studied. We analyze them by utilizing signal probability and boolean difference. It is well known that the acquisition of output signal probabilities is much easier compared with the obtention of output reliability. The results derived in this thesis proclaim the signal probability requirements for inputs of majority voter, and thereby reveal the conditions that TMR technique requires. This study shows the critical importance of error characteristics of majority voter, as used in fault-tolerant designs.

As the flawlessness of majority voter in TMR is not true, we also proposed a fault-tolerant and simple 2-level majority voter structure for TMR. This alternative architecture for majority voter is useful in TMR schemes. The proposed solution is robust to single fault and exceeds those previous ones in terms of reliability. Furthermore, it saves area, power dissipation and propagation delays.

With novel techniques emerging in the future, new algorithms and architectures for reliable digital IPs could be envisaged. More reliable nanoelectronic systems or quantum computers need researches from multidisciplines, such as physics, mathematical modeling, electronic engineering as well as computer architecture, and maybe even more.

#### Introduction

La réduction des dimensions des dispositifs semi-conducteurs selon la Loi de Moore [6] a apporté beaucoup de bénéfices : les systèmes électroniques sont plus petits, plus rapides, moins consommateurs et plus performants. Néanmoins, des phénomènes associés à cette miniaturisation conduisent à une réduction de la fiabilité des circuits. En particulier, le nombre de Single-Event Transient (SET) augmente, augmentant en même temps la probabilité que les circuits produisent des valeurs erronées appelées *soft errors*. Les derniers rapports annuels de l'International Technology Roadmap for Semiconductors (ITRS) montrent bien que la fiabilité est devenue un paramètre très important pour la conception des systèmes électroniques dans les technologies avancées.

Dans cette thèse, nous nous intéressons à la recherche d'architectures fiables pour les circuits logiques. Par "fiable", nous entendons des architectures permettant le masquage des fautes et les rendant de ce fait "tolérantes" à ces fautes.

Les solutions pour la tolérance aux fautes sont basées sur la redondance, d'où le surcoût qui y est associé. La redondance peut être mise en oeuvre de différentes manières : statique ou dynamique, spatiale ou temporelle. Nous menons cette recherche en essayant de minimiser tant que possible le surcoût matériel engendré par le mécanisme de tolérance aux fautes.

Le travail porte principalement sur les solutions de redondance modulaire, mais certaines études développées sont beaucoup plus générales (cf. chapitre 3).

### **Organisation**

Ce document est structuré de la manière suivante :

- Le chapitre 1 donne le cadre général de cette thèse. Nous y trouvons notamment la motivation pour ce travail et le rappel de ses objectifs, à savoir, développer de nouvelles méthodes et de nouvelles architectures pour circuits logiques tolérants aux fautes.

- Le chapitre 2 présente une introduction générale au problème de l'amélioration de la fiabilité des circuits logiques. Nous y trouverons notamment les définitions et métriques de la fiabilité, la motivation pour améliorer la fiabilité ainsi que des méthodes d'estimation de la fiabilité.

Le chapitre 3 est dédié à l'étude de l'importance qu'un sous-bloc du circuit peut avoir vis-àvis de la fiabilité du circuit global. Cette étude nous conduit à proposer deux métriques : la sensibilité et l'éligibilité. Ces métriques d'importance de chaque sous-bloc permet de mettre en oeuvre un classement des sous-blocs. Ce classement est la clé de l'efficacité d'une stratégie de durcissement sélectif.

- Le chapitre 4 décrit l'approche d'amélioration de fiabilité proposée dans cette thèse. Afin de maximiser le gain en fiabilité tout en minimisant les surcoûts liés au durcissement, nous proposons un ajout de redondance progressif. L'algorithme d'insertion de redondance ainsi que des études de cas sont décrits en détails dans ce chapitre.

- Le chapitre 5 porte sur la fiabilité de l'arbitre dans un schéma TMR. Nous utilisons les différences booléennes pour analyser le comportement d'un arbitre sujet aux fautes et l'impact que ces fautes peuvent avoir sur l'efficacité de la solution TMR. Les études permettent d'établir les conditions nécessaires à imposer sur la fiabilité de l'arbitre pour que la solution TMR soit source d'amélioration de la fiabilité. Nous présentons également une architecture nouvelle et tolérance aux fautes pour la mise en oeuvre d'une stratégie de vote par majorité.

#### Analyse de la fiabilité

#### Introduction

La définition classique de la fiabilité, notée R(t) est la probabilité (en fonction du temps t) que le système fonctionne conformément à ses spécifications pendant une période spécifiée  $[t_0,t]$ . Elle est déterminée par un paramétre important appelé  $taux\ de\ défaillance$  d'un composant (transistor, porte, bloc, module, etc.), généralement noté  $\lambda$ .

La relation entre la fiabilité R(t), taux de défaillance  $\lambda$  et temps t peut être exprimée par :

$$R(t) = e^{-\lambda t}. (1)$$

Plusieurs métriques peuvent être utilisées pour qualifier la fiabilité des circuits combinatoires.

Métrique 1 : Probabilité de fonctionnement

On définit la fiabilité d'un composant (transistor, bloc, module, système, etc) comme étant la probabilité que le composant réalise la fonction souhaitée. La probabilité de fonctionnement est également connue comme *fiabilité fonctionnelle* [7, 8].

$$Prob_{comp} = Prob(working) = 1 - Prob(failing)$$

(2)

Métrique 2 : Probabilité de sortie exacte

On définit la fiabilité d'un circuit par la probabilité que la sortie du circuit soit un bit-vecteur contenant seulement des 0's et 1's corrects. Cette métrique est également connue sous le nom

de fiabilité du signal [7, 12].

Dans cette thèse, nous considérons la métrique "fiabilité du signal" et nous nous appuyons sur les méthodes d'analyses décrites en [12].

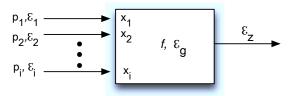

Supposons qu'un signal binaire x peut véhiculer des informations éventuellement incorrectes. Cela est équivalent à supposer que ce signal peut prendre quatre valeurs logiques différentes : zéro  $\operatorname{correct}(0_c)$ , un  $\operatorname{correct}(1_c)$ , zéro  $\operatorname{incorrect}(0_i)$ , et un  $\operatorname{incorrect}(1_i)$ . Les probabilités d'occurrence de chacune de ces quatre valeurs peuvent être représentées dans une matrice probabilité du signal [?] :

$$\begin{bmatrix} P(x=0_c) & P(x=1_i) \\ P(x=0_i) & P(x=1_c) \end{bmatrix} = \begin{bmatrix} x_0 & x_1 \\ x_2 & x_3 \end{bmatrix}$$

(3)

La fiabilité du signal pour x, noté  $R_x$ , vient directement de l'expression (4), où P(.) est la fonction de probabilité :

$$R_x = P(x = 0_c) + P(x = 1_c) = x_0 + x_3 \tag{4}$$

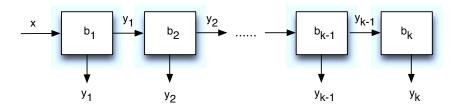

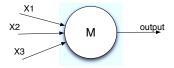

Considérons maintenant un bloc numérique effectuant un traitement sur un signal d'entrée x afin de produire un signal de sortie y (cf. Figure 2.5).

FIGURE 1 – Génération des signaux de sortie y du signal d'entrée x traitée par l'opérateur block b.

Supposons que p est la probabilité de défaillance de cet opérateur et que q=(1-p) est la probabilité qu'il fonctionne correctement. La fiabilité du signal de sortie y peut être facilement obtenue comme suit :

$$R_{y} = (x_0 + x_3).q + (x_1 + x_2).p (5)$$

L'équation (2.12) montre que lorsque le signal d'entrée est fiable  $(x_1 + x_2 = 0)$ , la fiabilité du signal de sortie est donnée par q, ce qui représente la probabilité de succès du bloc numérique. Ceci signifie que, dans le cas d'entrées exemptes de fautes, la fiabilité du signal de sortie est donnée par la fiabilité intrinsèque de l'opérateur de calcul qui produit ce signal.

#### L'évaluation de la fiabilité des circuits logiques

Pour les circuits numériques, l'évaluation de la fiabilité est le processus de l'analyse de l'effet et de la propagation des erreurs sur les blocs de base du circuit.

Il existe différentes méthodes d'analyse de la fiabilité reportées dans la littérature [10–17]. Le Tableau 1 présente une synthèse comparative des propriétés de ces techniques en termes de vitesse, précision, besoins en mémoire et l'adaptabilité à des circuits de grande taille (scalability).

| Méthodes   | Vitesse | Précision  | Mémoire    | Scalability |

|------------|---------|------------|------------|-------------|

| PTM        | _       | précise    | trés haute | non         |

| BN         | moyenne | précise    | haute      | non         |

| PGM        | moyenne | haute      | basse      | non         |

| $SPR_{MP}$ | basse   | précise    | basse      | non         |

| PBR        | basse   | précise    | basse      | non         |

| SCM        | moyenen | adaptative | basse      | oui         |

| BDEC       | moyenne | haute      | basse      | oui         |

TABLE 1 – La comparaison des méthodes représentatives d'évaluation de fiabilité.

#### Amélioration de la fiabilité

#### La tolérance aux fautes basée sur la redondance

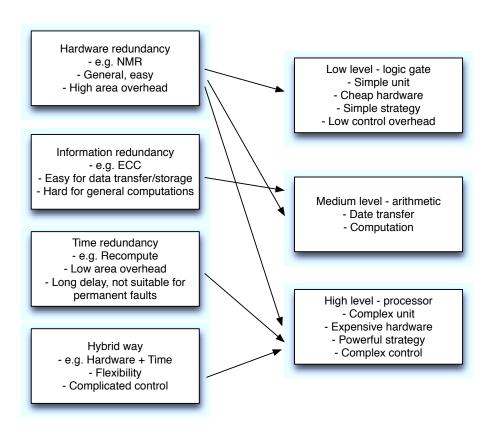

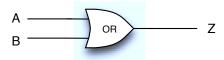

Il existe plusieurs formes de redondance en vue de la tolérance aux fautes [18–20]. La figure 2 montre une synthèse des principales formes de redondance et leur applicabilité aux différents niveaux d'abstraction et granularité de la représentation du système.

Dans ce travail, nous nous intéressons particulièrement à la redondance matérielle mise en oeuvre par réplication de N modules. Cette redondance est connue sous le nom de "redondance modulaire" ou NMR (N Modular Redundancy).

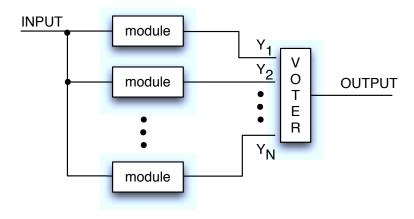

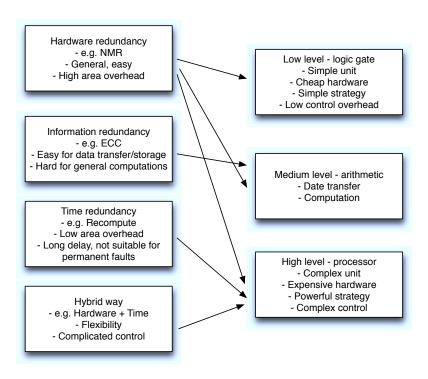

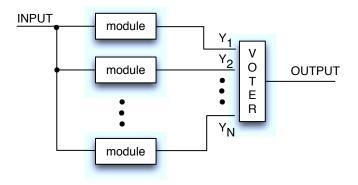

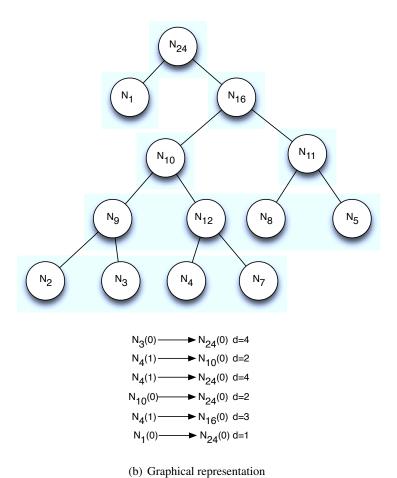

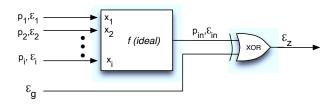

Dans un schéma NMR, il existe N+1 éléments : N répliques du module et un arbitre ( le **VOTER**) qui détermine la valeur de la sortie en fonction de chacune des N sorties produites par les différents modules.

La figure 3 présente un schéma général NMR. Le vote par majorité est l'une des stratégies les plus courantes pour le **VOTER**. Avec l'algorithme de la vote par majorité, N est un nombre impair et la sortie choisie est celle produite par plus de la moitié des répliques, c'est-à-dire, au moins  $\frac{N+1}{2}$  modules.

Sous l'hypothèse d'un arbitre idéal (c'est-à-dire, exempt de fautes), la fiabilité d'un système NMR peut être donnée par l'expression (6), où  $q_M$  est la fiabilité de chaque module et  $\binom{N}{i} = \frac{N!}{i!(N-i)!}$ .

$$R_{NMR-IV} = \sum_{i=\lceil N/2 \rceil}^{N} {\binom{N}{i}} q_M^i (1 - q_M)^{N-i}$$

(6)

FIGURE 2 – Techniques de tolérance aux fautes [1,2]).

FIGURE 3 – Schéma général pour la NMR.

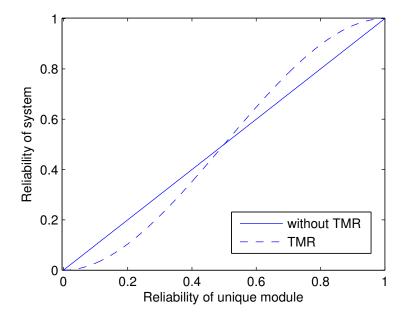

Dans le cas particulier de la redondance modulaire triple (TMR), la fiabilité est donnée par l'expression (7).

$$R_{TMR-IV} = \left(3q_M^2 - 2q_M^3\right) \tag{7}$$

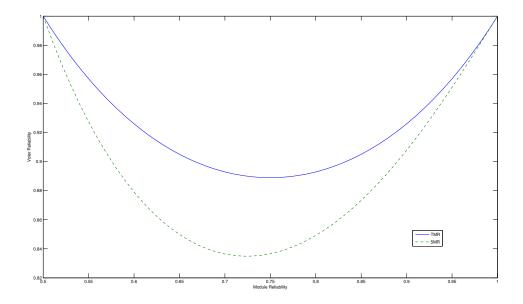

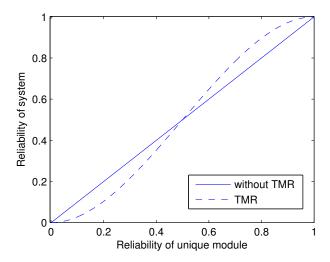

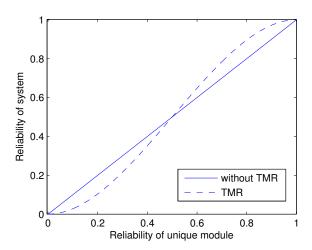

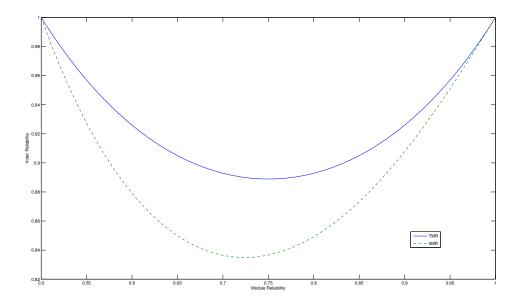

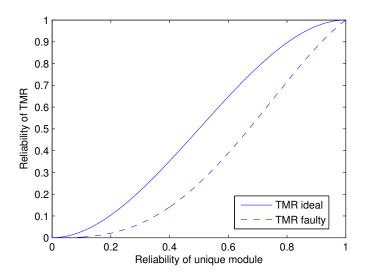

La figure 4 montre le comportement de la fiabilité d'un système sans redondance et avec TMR conformément à l'expression (7).

FIGURE 4 – Fiabilité pour deux stratégies de mise en oeuvre : module unique (ligne continue) et TMR (ligne pointillée).

#### **Durcissement sélectif**

Dans un circuit numériques constitué de différents sous-blocs numériques, la fiabilité est fonction des fiabilités intrinsèques de chacun des blocs individuels ainsi que de la manière selon laquelle ces sous-blocs sont interconnectés. Il est important de savoir quel rôle chacun des sous-blocs joue dans le circuit vis-à-vis de la fiabilité. Cette information est essentielle pour la mise en oeuvre d'une stratégie de durcissement sélectif. Dans ce sens, nous définissons les concepts de "sensibilité" et 'éligibilité".

#### Sensibilité et éligibilité

Considérons un circuit  $\mathcal{C}$  avec fiabilité R et constitué de K blocs indépendants  $b_i$ . Soit  $B = \{b_1, b_2, \dots, b_K\}$  l'ensemble de tous les blocs K dans  $\mathcal{C}$  et  $Q = \{q_1, q_2, \dots, q_K\}$  l'ensemble de leurs fiabilités respectives  $(q_i$  est la fiabilité de  $b_i$ ).

Nous définissons la **sensibilité** de la fiabilité du circuit C par rapport au bloc  $b_i$  dans l'expression (8). Cela correspond à la dérivée partielle de la fonction R par rapport à la variable  $q_i$ .

$$s(b_i) = \left| \frac{\partial R}{\partial q_i} \right| \tag{8}$$

Notons  $\Theta = \{\theta_1, \theta_2, \cdots, \theta_K\}$  l'ensemble des blocs classés en fonction des valeurs de sensibilité de telle sorte que  $\theta_1$  (resp.  $\theta_K$ ) est le bloc dont la sensibilité est maximale (resp. minimale).

Nous définissons l'éligibilité d'un bloc  $b_i$ , notée  $e(b_i)$ , comme l'indicateur de l'impact positif qu'a l'amélioration de la fiabilité de ce bloc sur la fiabilité globale du circuit. Notons  $\Delta_i = |R_i^* - R|$  le changement de la fiabilité du circuit qui résulte de l'amélioration de la fiabilité  $q_i$ .

Les valeurs d'éligibilité de deux blocs  $b_i$ ,  $b_j$  sont alors définies de telle sorte qu'elles respectent  $R_i^* > R_j^* \Rightarrow e(b_i) > e(b_j)$ . Les valeurs  $e(b_i)$  sont des entiers [1, K], où 1 et K représentent, respectivement, les blocs les moins et les plus éligibles.

#### Structures en cascade

Nous considérons d'abord les blocs  $b_i \in B$  tels que définis précédemment. Supposons que ces blocs sont assemblés en une structure en cascade de telle sorte que l'entrée du bloc  $b_i$  est donnée par la sortie du bloc  $b_{i-1}$  (cf. Figure 5).

Nous pouvons voir que la contribution de la fiabilité individuelle  $q_i$  à la fiabilité globale R dépend de la position du bloc  $b_i$  dans la structure. La sensibilité  $s(b_i)$  dépend aussi de la position du bloc i comme suit :

FIGURE 5 – Exemple de structure en cascade.

$$\left| \frac{\partial R}{\partial q_i} \right| = (K - i + 1)q_i^{K-i} \prod_{i=1}^K \prod_{j=1, j \neq i}^i q_j$$

$$= \frac{K - i + 1}{q_i} R \tag{9}$$

$$s(b_i) > s(b_j) \Leftrightarrow \frac{K - i + 1}{K - j + 1} > \frac{q_i}{q_j}$$

$$(10)$$

#### Structures génériques

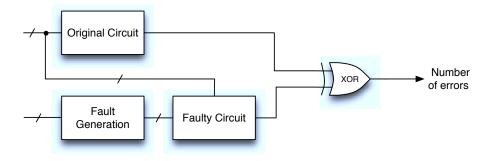

Dans le cas de structures génériques, l'expression de la fiabilité du circuit n'est pas évidente. Ainsi, nous avons déterminé la sensibilité et l'éligibilité à partir de simulations.

Une plate-forme de simulation est utilisée pour injecter des fautes [13, 80]. La figure 6 illustre le processus d'injection de fautes et d'analyse. Les résultats produits par le circuit de référence (exempt de fautes) et le circuit dans lequel les fautes ont été injectées sont comparés. Si ces résultats sont différents, il est conclu que les effets de la faute ont été propagés vers les sorties. Sinon, il est conclu que la faute a été masquée.

FIGURE 6 – Schéma général pour l'injection de fautes et l'analyse des masquage.

Chaque bloc  $b_i$  contribue à un certain nombre de masquages de fautes, noté  $m_i$ . Le nombre total de masquages m est la somme des  $m_i$ ,  $m = \sum_{i=1}^K m_i$ . Chaque  $m_i$  est obtenu en calculant le nombre de masquages après l'injection d'une faute simple sur le bloc correspondant  $b_i$ . En d'autres termes, en considérant que tous les autres blocs  $b_j$   $(1 \le j \le K, j \ne i)$  fonctionnent correctement. De cette façon, chaque  $m_i$  est directement lié à la sensibilité du bloc  $b_i$ . Le classement des blocs en fonction de leurs sensibilités est défini à partir de la relation :

$$s(b_i) > s(b_j) \Leftrightarrow m_i < m_j \tag{11}$$

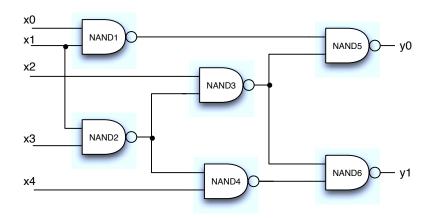

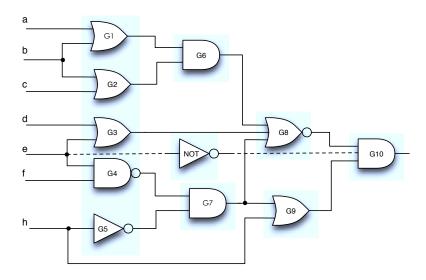

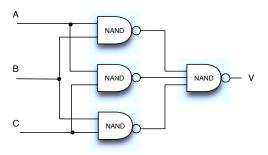

La figure 7 présente un exemple de circuit benchmark (le circuit C17, de la collection ISCAS-85 [77]). Chaque porte NAND est considérée comme un bloc. Il y a 32 combinaisons logiques possibles pour les entrées et deux configurations considérées pour chaque bloc (sans faute et avec faute). Parmi les 192 configurations qui en découlent, les résultats de  $m_i$  sont donnés dans le Tableau 2. Notez que  $m_i = m_i = 0$ , ce qui signifie que ces deux blocs ne peuvent pas masquer les défauts. En effet, leurs sorties sont également sorties primaires du circuit et nous considérons que seule faute.

FIGURE 7 – Circuit C17.

TABLE 2 – Classement des sous-blocs du circuit C17 en fonction de la sensibilité.

| b(i)     | $m_i$ |

|----------|-------|

| $NAND_1$ | 12    |

| $NAND_2$ | 8     |

| $NAND_3$ | 2     |

| $NAND_4$ | 12    |

| $NAND_5$ | 0     |

| $NAND_6$ | 0     |

Considérons le même circuit de C17 pour illustrer le classement de blocs en fonction de leurs éli-

gibilités. Sans perte de généralité, supposons que chaque porte NAND est censée avoir  $q_i=q=0.99$  (99%). De même, considérons que l'amélioration de la fiabilité est mise en oeuvre par la technique TMR (Triple Modular Redundancy). Le résultat de l'application de TMR sur chaque porte NAND est présenté dans le Tableau 3.

| b(i)     | $R_i^+$ | e(i) |

|----------|---------|------|

| $NAND_1$ | 95.765% | 2    |

| $NAND_2$ | 95.882% | 3    |

| $NAND_3$ | 96.056% | 4    |

| $NAND_4$ | 95.763% | 1    |

| $NAND_5$ | 96.117% | 6    |

| $NAND_6$ | 96.114% | 5    |

TABLE 3 – Classement des sous-blocs du circuit C17 en fonction de l'éligibilité.

#### Approche progressive pour la redondance modulaire

#### Principe général

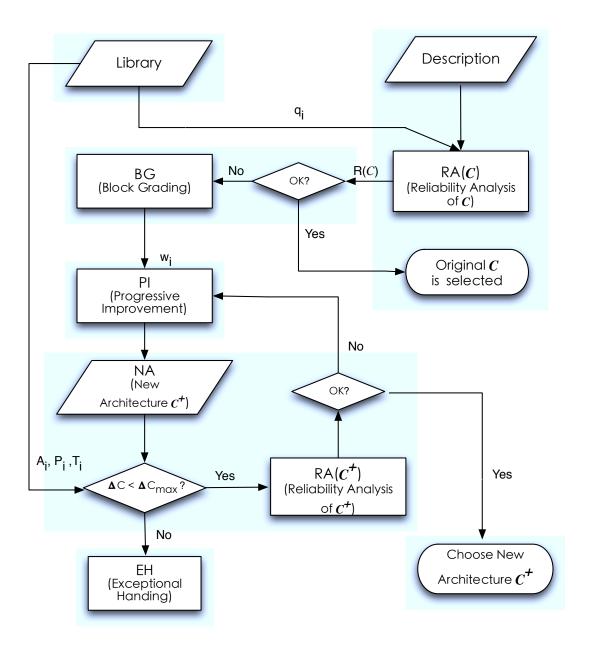

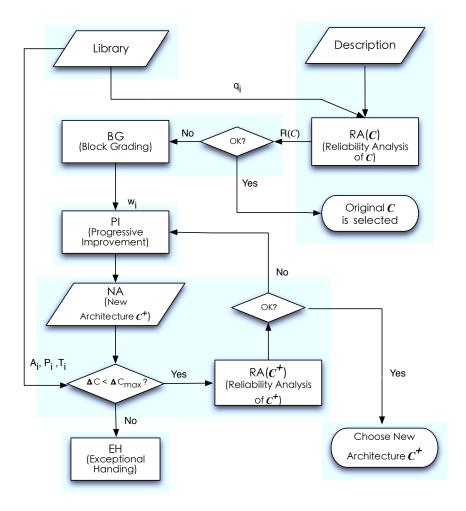

Nous avons proposé une méthode de durcissement progressif basée sur le classement des blocs dans le circuit. Cette méthode, nommée  $Progressive\ Modular\ Redundancy(PMR)$ , a pour objectif de trouver un compromis entre l'amélioration de la fiabilité  $\Delta R$  et le surcoût matériel  $\Delta C$  engendré par cette amélioration de la fiabilité. Selon les contraintes de la conception, l'analyse du problème se traduit par :

- déterminer l'architecture de moindre coût qui peut satisfaire une contrainte de fiabilité. Cela signifie réduire  $\Delta C$ , tout en respectant  $R \geq R_{min}$ .

- déterminer l'architecture de meilleure fiabilité ne dépassant pas un surcoût matériel donné. Cela signifie maximiser  $\Delta R$ , tout en respectant  $\Delta C \leq \Delta C_{max}$ .

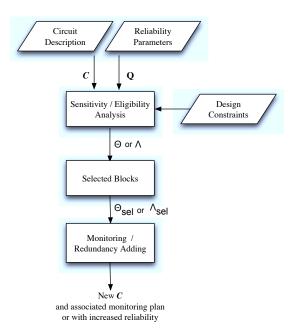

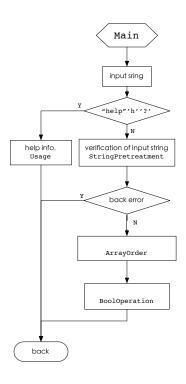

Quel que soit le cas considéré ci-dessus, nous proposons d'agir progressivement sur les blocs, en commençant par l'amélioration de la fiabilité d'un seul bloc, puis deux blocs, et ainsi de suite jusqu'à couvrir tous les blocs ou atteindre le coût maximal autorisé. La méthode proposée est décrite dans la Figure 8.

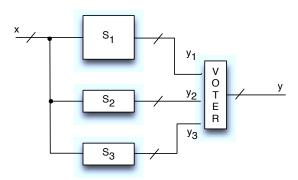

Le Tableau 4 montre comment de nouvelles architectures sont produites selon cette méthode progressive. Le circuit est censé avoir K blocs. La redondance est effectuée en ajoutant une redondance modulaire triple (TMR ou 3MR), ce que nous nommons  $Progressive\ TMR$  (PTMR).

Dans ce tableau, les blocs sont classés en fonction de leur poids  $(w_i)$  et m désigne les étapes d'exécution de la méthode. Les valeurs dans les cellules représentent les degrés de redondance (1 = pas de redondance, 3 = triple redondance modulaire). L'architecture du circuit correspondant à l'étape

m est obtenue en utilisant TMR sur les blocs de m pour lesquels  $w_i \in [K-m+1,K]$ .

|                 | $ $ $w_i$ |     |     |   |       |   |   |   |

|-----------------|-----------|-----|-----|---|-------|---|---|---|

| $\underline{m}$ | K         | K-1 | K-2 |   | K-m   |   | 2 | 1 |

| 0               | 1         | 1   | 1   | 1 | 1     | 1 | 1 | 1 |

| 1               | 3         | 1   | 1   | 1 | 1     | 1 | 1 | 1 |

| 2               | 3         | 3   | 1   | 1 | 1     | 1 | 1 | 1 |

| 3               | 3         | 3   | 3   | 1 | 1     | 1 | 1 | 1 |

| 4               | 3         | 3   | 3   | 3 | 1     | 1 | 1 | 1 |

|                 |           |     |     |   | • • • |   |   |   |

| $\overline{K}$  | 3         | 3   | 3   | 3 | 3     | 3 | 3 | 3 |

TABLE 4 – Exécution de l'algorithme PTMR.

L'application de l'approche PTMR au circuit de la Figure 7 produit le Tableau 3. Chaque porte NAND est censée avoir fiabilité  $q_i=q=0.99$  (99%) et coût  $S_{NAND}$ . Les contraintes de conception considérées sont : fiabilité minimale requise  $R_{req}=0.97$  (97%) et surcoût en surface maximal accepté  $4\times S_{NAND}$ . Bien que le nombre total d'architectures générant la même surface soit  $C_6^2=15$ , cette méthode permet d'identifier le meilleure d'entre elles sans avoir à toutes les tester.

TABLE 5 – Résultats de l'application de l'approche *PTMR* sur le circuit C17.

| Steps (m) | Architecture | Reliability | Area Cost           |

|-----------|--------------|-------------|---------------------|

| 0         | 1-1-1-1-1    | 95.20%      | $6S_{NAND}$         |

| 1         | 3-1-1-1-1    | 96.12%      | $8S_{NAND} + S_V$   |

| 2         | 3-3-1-1-1    | 97.05%      | $10S_{NAND} + 2S_V$ |

#### Fiabilité de l'arbitre dans un schéma TMR

Dans les schémas TMR, l'arbitre est souvent supposé parfait, c'est-à-dire, exempt de fautes. Or, la prise en compte de la fiabilité réelle de ce composant est essentielle pour déterminer l'efficacité de cette approche. Dans le cas de vote par majorité, si nous considérons que l'arbitre a une fiabilité  $R_v$ , l'équation (7) est modifiée pour donner :

$$R_{NMR-FV} = R_v \cdot \sum_{i=\lceil N/2 \rceil}^{N} {\binom{N}{i}} q_M^i \left(1 - q_M\right)^{N-i}$$

(12)

Avec un arbitre imparfait, la condition pour que le système TMR apporte un gain en fiabilité se traduit par :

$$R_{NMR-FV} > q_M \quad or \quad \frac{R_{NMR-FV}}{q_M} > 1$$

(13)

Ainsi, la fiabilité minimale pour l'arbitre est :

$$R_{V_{min}} = \frac{1}{\sum_{i=\lceil N/2 \rceil}^{N} \binom{N}{i} q_M^{i-1} (1 - q_M)^{N-i}}$$

(14)

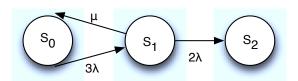

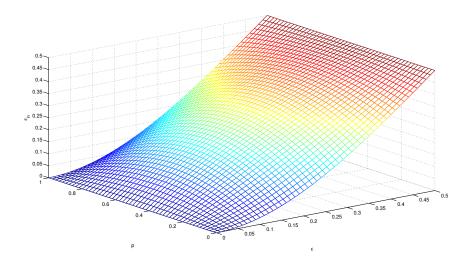

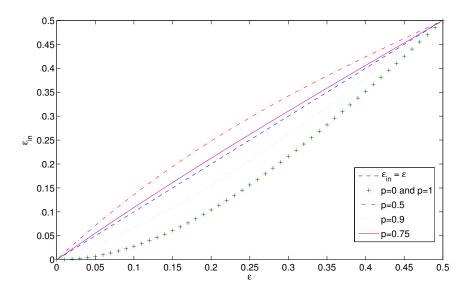

La figure 9 montre l'exigence de fiabilité minimum pour un arbitre dans un schéma de redondance modulaire d'ordre 3 (TMR) et 5 (5MR).

#### Arbitre tolérant aux fautes

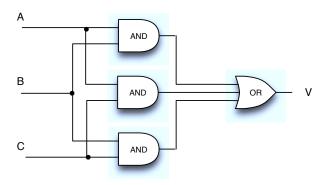

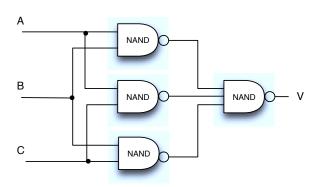

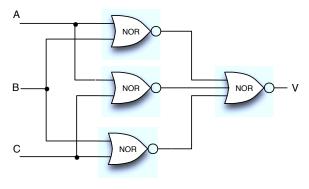

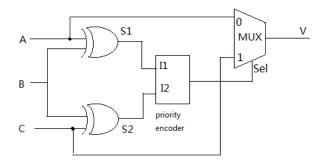

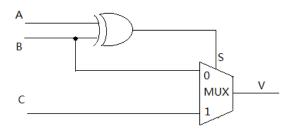

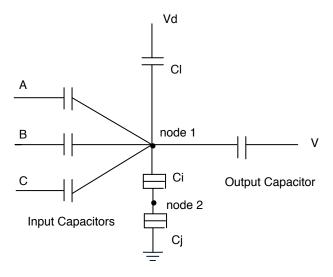

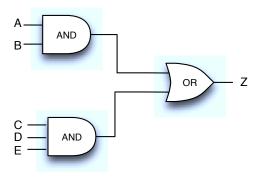

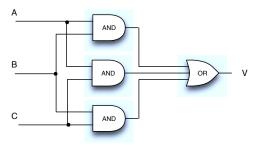

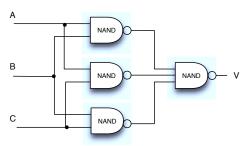

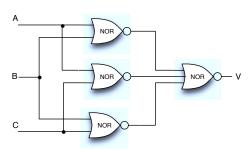

Toutes les combinaisons possibles d'entrées dans un arbitre basé sur le vote majoritaire sont présentées dans le Tableau 6. L'expression booléenne correspondante est donnée dans (15). La forme simplifiée de cette équation, donnée dans l'équation 16, permet d'obtenir différentes structures de mise en oeuvre, comme nous pouvons voir dans les Figures 10(a) et 10(b).

TABLE 6 – Table de vérité pour un arbitre basé sur le vote majoritaire.

| A | В | С | V |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

$$V = ABC + AB\overline{C} + \overline{A}BC + A\overline{B}C \tag{15}$$

$$= AB + BC + AC \tag{16}$$

Considérons la structure d'arbitre AND-OR dans la Figure 10(a). Nous pouvons constater qu'une faute dans une porte AND ou OR peut générer une valeur erronée dans la sortie de cet arbitre. Par exemple, si A = B = C = 0 et une faute simple a lieu dans S1, la sortie sera V = 1, alors que la valeur attendue est V = 0. Par conséquent, cette structure n'est pas tolérante aux fautes.

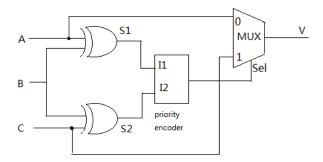

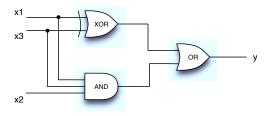

Dans [92], Kshirsagar a proposé une structure d'arbitre tolérante aux fautes (NTFVC) (cf. Figure 11).

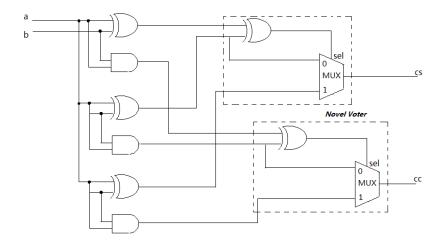

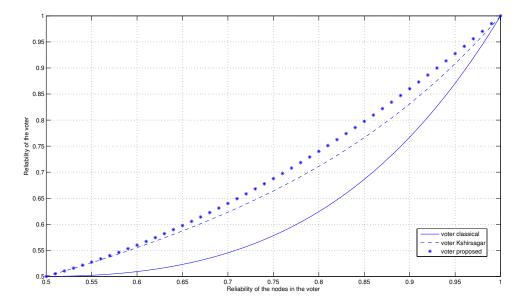

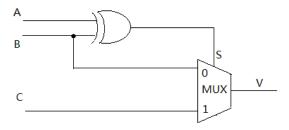

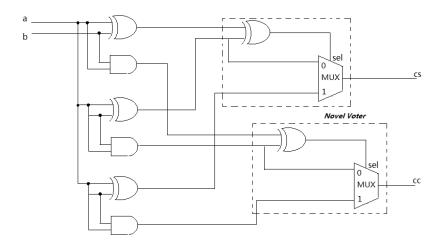

Nous proposons une structure nouvelle pour arbitre dans schéma TMR avec stratégie de vote par majorité capable de tolérer des fautes (cf. Figure 12) et plus compacte que celle de Kshirsagar. Les

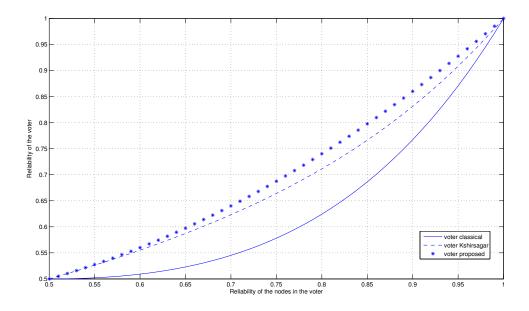

résultats d'analyse de fiabilité obtenus avec l'algorithme SPR [12,46] sont présentés dans la Figure 14. L'arbitre proposé a été utilisé dans plusieurs circuits (cf. exemple de half-adder dans la Figure 13). Les résultats des comparaisons par rapport à des paramétres différents en fonction de différents électeurs de la technique TMR sont présentés dans le Tableau 7.

TABLE 7 – Résultats synthétisés dans ASIC (RTL Compiler).

| Comparison    | Classic | NFTVC | Proposed |

|---------------|---------|-------|----------|

| Instances     | 25      | 31    | 25       |

| Area          | 31      | 40    | 32       |

| Power $\mu w$ | 2.35    | 3.75  | 2.85     |

FIGURE 8 – Workflow pour la méthode proposée.

FIGURE 9 – La fiabilité des électeurs requis dans le systéme de NMR.

(a) L'électeur construit par AND/OR.

(b) L'électeur construit par NAND.

(c) L'électeur construit par NOR.

FIGURE 10 – Schémas classiques pour arbitre dans schéma TMR avec stratégie de vote par majorité.

FIGURE 11 – Structure d'arbitre tolérant aux fautes (NFTVC) [92].

FIGURE 12 – Schéma proposé pour l'arbitre tolérant aux fautes.

FIGURE 13 – Exemple d'utilisation de l'arbitre tolérant aux fautes dans un demi-additionneur.

FIGURE 14 – Courbes de fiabilité pour les classiques (ligne continue), NFTC (ligne pointillée) et l'électeur proposée (ligne pointillée).

# **Chapter 1**

# Introduction

#### 1.1 Motivations

Intellectual property (IPs) in semiconductors refers to pre-designed function modules which are used in Application- Specific Integrated Circuit (ASIC), Field-Programmable Gate Array (FPGA) or Programmable Logic Device (PLD), etc. In accordance with Moore's Law, the number of transistors per chip should double every 18 to 24 months. The smaller dimensions enabled the development of faster, more compact, and more powerful electronic devices [21]. However, the complexity to design and to produce such devices has also grown over the years, emerging as a drawback to maintain their current evolution rate. The operation frequency is expected to increase up to 12 GHz, and a single chip will contain over 12 billion transistors in 2020 according to ITRS [22]. Therefore, transistors are now implemented into the nanoscale and known as nano electronic devices.

As a result of scaling, the amount of defects as well as the number of transient errors in electronic circuits are expected to increase, and it becomes a major concern in Deep-SubMicron technologies (DSM). Some of these are manufacturing imprecision, improved susceptibility to environmental factors and physical parameters variability [23]. This caused two significant challenges. The first is related to the yield that can be achieved during the manufacturing process of digital IPs, known as design-for-yield which is an entire research field. The second challenge is that although digital IPs have been proved to work correctly, they must continue to operate reliably even they are increasingly sensitive to various kinds of perturbations, which are known as SEUs (Single-event Upsets). Reduction in the reliability of digital IPs is one of the main threats in semiconductors industry [24], which leads to paradigm shift toward design-for-reliability [25]. Since reliability is a crucial feature of designs, new techniques of reliability improvement need to be developed to overcome the expected unreliability of IPs implemented on such new DSM technologies.

SEUs in digital IPs have been ignored for a long time because SETs (Single-event transient, also known as soft errors [21,26]) had only minor influence in earlier  $0.35\mu m$  and larger technologies [27]. On the other hand, there are three intrinsic properties of logic circuit itself: First, *logical masking*.

22 1. Introduction

A glitch might not propagate to a memory cell because of a gate on the path not being sensitized to facilitate glitch propagation. Second, *electrical masking*. A generated glitch may get attenuated because of the delays of the gates on the path to the output [28]. Third, *latching-window masking*. A glitch that reaches the primary output might not still cause an error because of the latch not being open.

However, in Deep SubMicron (DSM) technologies, due to the decreasing number of gates in a pipeline stage, logical masking as well as electrical masking have been decreasing for new technology generations. Electrical masking has also been decreasing due to the reduction in node capacitances and supply voltages every generation. Furthermore, increasing clock frequencies have reduced the time window in which latches are not accepting data, thereby also reduced latch-widow masking. As above statement, the soft error rate (SER) in digital IPs raised 9 orders of magnitude from 1992 to 2011, when it is equal to the SER of unprotected memory elements [29]. Needless to say, under the DSM technologies, soft errors in digital IPs are not optimistic and are becoming dominant in the overall soft error rate.

There are various fault-tolerant techniques to increase the robustness of the circuits, which are mostly based on the concept of redundancy [9, 30–32]. These techniques have been applied at different levels of granularity, such as gate level, logic block level, logic function level, unit level, etc. Moreover, these techniques were historically targeted to mission critical systems, for example, in medical, spatial and military applications. With the expected reduction in the reliability of electronic devices, they have been considered in many general applications, such as consumer electronics.

The usage of aforementioned fault-tolerant techniques can help to enhance reliability of circuits, but they normally result in great area, time or power overheads. Moreover, too much redundancy may reduce the yield since a larger-area circuit is expected to have a larger number of defects. *Pareto principle* [33] states that, for many events, roughly 80% of the effects come from 20% of the causes. Consequently, successful designs must have the optimal amount of redundancy to be added. In order to develop this optimal redundancy configuration, we try to implement a partial redundancy where the most eligible parts of the circuits are protected, meanwhile the best improvement in reliability can be achieved.

## 1.2 Objectives

The objective of this thesis is to develop new methods and architectures for logic function IPs bringing with optimized trade-offs which can improve reliability and give consideration to classical performance parameters (power consumption, area and time) simultaneously. Consequently, the question we try to answer in this thesis is how to make a judicious redundancy configuration that could result in optimal reliability improvements. It includes research on finding most suitable extent and location of implementing the hardware redundancy under a given design criteria.

This dissertation mainly addresses the following issues.

- As it is possible to build systems with unreliable components, how to fabricate more reliable systems with the probabilistic nature of the component's individual reliability?

- Propose and verify new fault-tolerant architectures that enable improvement in reliability, with respect to those existing ones.

- As a realistic fault model is relevant to further evaluation of reliability, fault models and reliability evaluation methods need to be analyzed and compared.

- Since the common approach for constructing fault-tolerant architectures consists of incorporating redundancy, the feasibility of designing reliable architectures by using economical/small redundancy factors is worthy to be discussed.

- The importance of reliability in majority voter is due to its application in fault-tolerant design.

Error characteristics of majority voter are discussed to reveal the conditions that Triple Module

Redundancy (TMR) technique requires.

### 1.3 Organization of the thesis

The dissertation is organized as follows:

- Chapter 2 introduces the basic concepts related to reliability improvement in logic circuits: definition and metrics of reliability, motivations for enhancing reliability, ways and methods of evaluating reliability, etc. A brief review of fault-tolerant techniques is presented, including types of redundancy and general methods of fault-tolerant system design. Reliability improvement of digital IPs by hardware redundancy is mainly discussed, concerning module redundancy (especially TMR), trade-offs between reliability requirements and performance degradation etc. As TMR becomes a favorable solution because of its straightforward implementation and also reliability gains, state of the art in alleviating the performance degradation of TMR designs are addressed, including Selective TMR, Partitioning TMR, Non-uniform TMR, Automatic-insertion of TMR, Selective fault tolerance, etc.

- Chapter 3 is about two proposed concepts that describe the significance of the constituent blocks of digital IPs: sensitivity and eligibility. This inherent significance can identify the most critical/eligible blocks of digital IPs according to different design criteria. Afterwards, reliability analysis and improvement based on these two concepts are discussed. The concepts are firstly implemented on the cascade structure mathematically and then on generalized circuit structures by simulations. Applications based on these concepts are also presented.

- Chapter 4 presents reliability improvement by redundancy management. In order to maximize the reliability while minimizing redundancy adding, the progressive manner of redundancy addition (Progressive Modular Redundancy, PMR) is proposed. The algorithm, workflow and methodology are presented in details. Furthermore, considering that not all bits of information

24 1. Introduction

have the same degree of importance, a more aggressive way of fault-tolerance is proposed in some practical applications with related to the bit significance. Finally, results obtained from the proposed method are compared with the state-of-the-art techniques.

- Chapter 5 analyzes the error characteristics of majority voter. The importance of reliability in majority voter is due to its application in both conventional fault-tolerant design and novel nanoelectronic systems. A better understanding of signal probability, functional/signal reliability and error bound of majority voter is discussed here. These parameters are analyzed by boolean difference. The equations derived here present the characteristics of error propagations in majority voter, and reveal the conditions that TMR technique requires. The results show the critical importance of error characteristics of majority voter, as used in fault-tolerant designs. Finally, a simple fault-tolerant voter structure is also proposed which avoids voter introducing new locations wherein faults may occur.

- Chapter 6 presents concluding remarks, reviews of this dissertation and further perspectives are also discussed.

# **Chapter 2**

# **Reliability Improvement Techniques**

#### 2.1 Introduction

Reliability is actually as important as other factors such as power consumption, area overhead and speed in nanometer electronic designs. The ITRS explicitly calls for a fresh look on nano-architecture with emphasis on fault and defect tolerance [34]. With technology scaling and complexity of the designs increasing, digital IPs become more fault-prone and there is a serious menace to the continuous development of the integrated circuits industry. These problems have motivated a lot of researches on reliability improvement. However, cost penalty concomitant with the reliability improvement makes the task not an easy work.

This chapter presents general concepts related to reliability and its enhancement in digital IPs and the scope of the work is also defined. Preliminaries and prevalent models for reliability evaluation are introduced. Most recent progresses about reliability evaluation methods are reviewed. Comparison and comments about them are also presented. An overview of redundancy-based fault-tolerant schemes regarding to nano-electronic technologies is presented as well as a detailed discussion and comparison concerning the methodologies for reliability improvement designs.

## 2.2 Preliminaries of reliability

#### 2.2.1 Defect, fault, error and failure

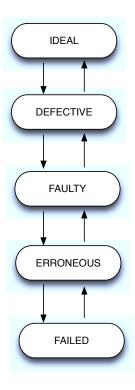

An electronic system can be in one of the five states as shown in Figure 2.1: Ideal, Defective, Faulty, Erroneous, or Failed [35]. These states are explained as below:

- Defect: A defect is any imperfection on the wafer.

- Fault: A fault is an erroneous state of the system, either hardware of software.

- Error: An error is the manifestation of a fault.

- Failure: A failure causes the system performance deviate from its specified performance.

Some distinctions between these definitions are as follows:

- Defects and Faults: A defect is any imperfection on the wafer, but only those defects that actually affect the circuit operation are called faults.

- Faults and Errors: If a fault is actually exercised, it may contaminate the data flowing within the system, causing errors, but not necessarily.

- Errors and Failures: Errors may or may not cause the affected circuits to failures. It doesn't necessarily have a catastrophe: when an error is encountered during the operation of a system, it will cause a failure.

Figure 2.1: System States and state transitions in the multi-level model of reliability.

The circuit systems move from one state to another as a result of deviations and remedies. Deviations are the events that take the system to a less desirable state, while remedies are measures that enable a system to make the transition to a higher state. In addition, faults are usually characterized based on its duration. That is, a fault is said to be *permanent* if it continues to exist until it can be repaired. An *intermittent fault* is one that happens and ends at a frequency that can be characterized. A *transient fault*, which is mainly focused on in this thesis, is the fault that occurs and disappears at an unknown frequency. It is caused by alpha or neutron particles, electrostatic discharge, thermal noise, crosstalk, quantum mechanical effects, etc.

#### 2.2.1.1 SEUs and SETs under DSM technologies

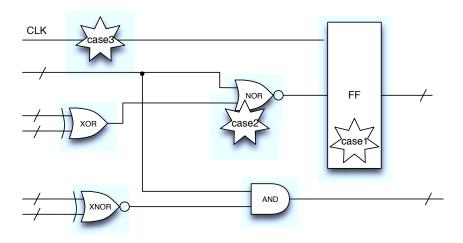

The transient faults we are interested in this thesis are single event upsets (SEUs), in which radiated particles cause the state of a storage element changed. They can occur in storage elements of digital IPs like latches, flip-flops as well as memory cells (SRAM, DRAM). SEUs may happen in three ways, as shown in Figure 2.2.

- Case 1: A particle attacks an internal node of a latch or flip-flop directly. In this case, it may

produce an inversion of the element state.

- Case 2: A particle hits the combinational parts of a digital circuit, for example a logic gate. In this case, the particle strike causes a glitch (glitches) in the output voltage of a logic gate, which is called single event transients (SETs). SETs may propagate through the combinational part to a latch or a flip-flop, thus turn into a SEU.

- Case 3: A particle attacks the control signal such as clock signal. This will result in early or late edge in the clock signal and data will not be latched correctly.

Figure 2.2: Mechanism of SEUs in digital IPs.

As technology size shrinks, digital IPs are becoming more susceptible to SEUs and SETs. SEUs and SETs therefore become the major reliability concerns in deep submicron technologies. Since SETs depend on the propagation time and also combinational logic, the probability to latch a SET can only be evaluated very late in the design process. However, it is necessary to know the potential impact of SEUs and SETs at earlier stage in design flow. Consequently, it requires a model to make it possible to analyze the faults.

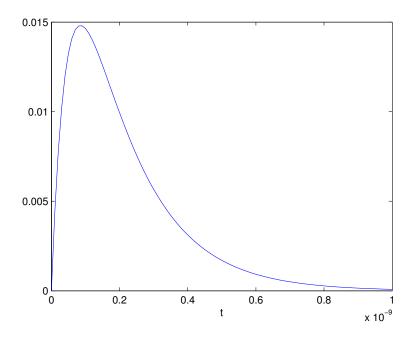

#### 2.2.1.2 Modeling of faults

To deal with faults, a model is needed to simulate their effects. A fault model is a logical abstraction that describes the functional effect of the physical defect. Fault modeling can be made at

different levels, from the lowest physical geometrical level and then gate level and to the highest which is the functional level. The lower the fault models are, the more accuracy could be obtained while the computation is more complex. For example, Figure 2.3 shows the double exponential model for current pulses in analog domain which is proposed in [36]. Although this fault model remains at low level, it can be used to implement fault injections on target nodes in the high-level description of analog blocks. In order to simplify the simulations and reduce the fault injection experiment duration, a more practical model is then proposed in [37] with more parameters that derived from the classical double exponential model.

Figure 2.3: Double exponential fault model.

Fault injection techniques can be classified into three main categories [38].

- physical fault injection: it introduces faults directly to the hardware of the target system by distributing the working environment of hardware. Like electromagnetic interferences, heavy ion radiation, etc. It is most close to the real fault environment but the device for injection is expensive. And it also needs long design cycles.

- software fault injection: it refers to changing the memory and registers to emulate the consequences of hardware faults. The flaw is that injection locations are limited and time resolution is poor.

- simulated fault injection: It imitates the faults of the system based on the use of hardware description languages. It is favorable because it can provide check results at an early time in the design process and simulations could be implemented on RTL as well as gate level.

Simulation-based fault injection is widely adopted for its flexibility, visibility and nonintrusive-

ness. In digital domains, the consequences of SEUs and SETs could be modeled by one of more bit-flip(s) at the functional level. As stated above, it is realized by modifying the initial description of circuits, i.e., HDL codes. To make these modifications, there are two approaches named *saboteurs* and *mutants* respectively. The first is to add blocks (the saboteurs) between the existing blocks. Such modifications are easy both in concept and implementation and are adopted by a lot of applications. In this thesis, we will use this fault model for injecting faults to digital IPs and then analyze the circuit reliability.

If we need to inject higher-level errors that are behavioral errors, we need to modify signals within the initial blocks, for example, values of memorized signals or variables. In such cases, the modified description of the block is called *mutant*. The injections of faults in the high-level is more difficult but more powerful. Examples of sabotaged and mutated VHDL codes could be found in [39] and [40]. A complete framework for Verilog-based fault injection and evaluation is presented in [38]. A novel simulation fault injection method for the dependability analysis of complex SoCs using 32-nm technology is proposed in [41] (named SyFI, which augmented the SystemC simulator kernel so that fault injection experiments can be performed conveniently). It is applied at the system description level, as opposed to the lower, flattened RT level, in order to reduce simulation time and storage space.

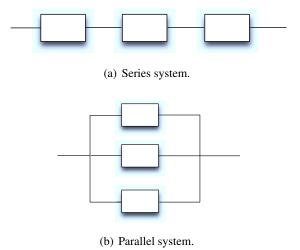

#### 2.2.2 Measures and metrics related to reliability

A reliability measure is a mathematical representation of the circuit reliability characteristics. The conventional definition of reliability, denoted by R(t), is the probability (as a function of the time t) that the system will execute its specified function continuously in a given time interval  $[t_0, t]$ . It is determined by an important parameter called the *failure rate* of a component (transistor, gate, block, module, etc.). Failure rate (usually denoted by  $\lambda$ ), is the rate at which an individual component suffers faults. This parameter depends on the current age of the component, any physical shocks it suffers and the technology. As we stated in the first chapter, combinational circuits have logical, electrical and temporal masking properties. Therefore, *failure rate* in combinational circuits is also dependent on its capacity to mask these faults. This ability reduces the probability of propagation and further storage of the faults in the sequential elements of the circuit, characterizing a failure.

The relationship between reliability R(t) and time t that has been widely accepted is the exponential function, i.e.,

$$R(t) = e^{-\lambda t}. (2.1)$$