## Automatic Resource-Constrained Static Task Parallelization: A Generic Approach

Dounia Khaldi

### ▶ To cite this version:

Dounia Khaldi. Automatic Resource-Constrained Static Task Parallelization : A Generic Approach. Other [cs.OH]. Ecole Nationale Supérieure des Mines de Paris, 2013. English. NNT: 2013ENMP0031. pastel-00935483

### HAL Id: pastel-00935483 https://pastel.hal.science/pastel-00935483v1

Submitted on 23 Jan 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

École doctorale n°432 : Sciences des Métiers de l'Ingénieur

### Doctorat ParisTech

### THÈSE

pour obtenir le grade de docteur délivré par

## l'École nationale supérieure des mines de Paris

Spécialité « Informatique temps-réel, robotique et automatique »

présentée et soutenue publiquement par

### Dounia KHALDI

le 27 novembre 2013

# Parallélisation automatique et statique de tâches sous contraintes de ressources

une approche générique –

Automatic Resource-Constrained Static Task Parallelization

– A Generic Approach –

Directeur de thèse : François IRIGOIN Encadrement de la thèse : Corinne ANCOURT

Jury

Corinne ANCOURT, Chargée de recherche, CRI, MINES ParisTech Cédric BASTOUL, Professeur, Université de Strasbourg Henri-Pierre CHARLES, Ingénieur chercheur en informatique, CEA François IRIGOIN, Directeur de recherche, CRI, MINES ParisTech Paul H J KELLY, Professeur, SPO, Imperial College London Examinateur

Président & Examinateur

Rapporteur

Directeur de thèse

Rapporteur

H È S E

A la mémoire de ma nièce Nada Khaldi

## Remerciements

Soyons reconnaissants aux personnes qui nous donnent du bonheur ; elles sont les charmants jardiniers par qui nos âmes sont fleuries. Marcel Proust

La réalisation d'une thèse est naturellement un travail personnel, mais en aucun cas un travail solitaire. Je tiens à remercier tout d'abord mon directeur de thèse, François Irigoin, et mon encadrante, Corinne Ancourt, pour m'avoir fait confiance malgré les connaissances plutôt légères que j'avais, en octobre 2010, sur les systèmes de parallélisation automatique. J'adresse également, et tout particulièrement, mes vifs remerciements et témoigne toute ma reconnaissance à Pierre Jouvelot pour l'expérience enrichissante et pleine d'intérêt qu'il m'a fait vivre durant ces trois années au sein du CRI.

Je remercie également tous ceux sans lesquels cette thèse ne serait pas ce qu'elle est, aussi bien par les discussions que j'ai eu la chance d'avoir avec eux, leurs suggestions ou leurs contributions. Je pense ici en particulier à Cédric Bastoul, qui de plus m'a fait l'honneur de présider le jury de cette thèse, et Paul Kelly et Henri-Pierre Charles, qui ont accepté d'être les rapporteurs de cette thèse, et je les en remercie, de même que pour leur participation au jury. Ils ont également contribué par leurs nombreuses remarques et suggestions à améliorer la qualité de ce mémoire, et je leur en suis très reconnaissante.

Je passe ensuite une dédicace spéciale à toutes les personnes que j'ai eu le plaisir de côtoyer au CRI, à savoir Jacqueline Altimira, Amira Mensi, Mehdi Amini, Vivien Maisonneuve, Olivier Hermant, Claude Tadonki, Antoniu Pop, Nelson Lossing, Pierre Guillou, Pierre Beauguitte, Benoît Pin, Laurent Daverio et, en particulier, Claire Médrala, avec qui j'ai partagé le même bureau. Je tiens aussi à remercier François Willot, pour son aide pour les expérimentations sur une machine à mémoire distribuée.

Je tiens aussi à remercier Sarah, Ghania et Halim, Razika et Rochdi pour leurs esprits taquins, ainsi que Khaled, Soumia, Molka, Naira, Nilsa, Arnaud et Karter pour leurs nombreux coups de main, leur sens pratique, leur efficacité et leur sourire. J'adresse enfin une pensée particulière à mes parents.

## Abstract

This thesis intends to show how to efficiently exploit the parallelism present in applications in order to enjoy the performance benefits that multiprocessors can provide, using a new automatic task parallelization methodology for compilers. The key characteristics we focus on are resource constraints and static scheduling. This methodology includes the techniques required to decompose applications into tasks and generate equivalent parallel code, using a generic approach that targets both different parallel languages and architectures. We apply this methodology in the existing tool PIPS, a comprehensive source-to-source compilation platform.

This thesis mainly focuses on three issues. First, since extracting task parallelism from sequential codes is a scheduling problem, we design and implement an efficient, automatic scheduling algorithm called BDSC for parallelism detection; the result is a scheduled SDG, a new task graph data structure. In a second step, we design a new generic parallel intermediate representation extension called SPIRE, in which parallelized code may be expressed. Finally, we wrap up our goal of automatic parallelization in a new BDSC- and SPIRE-based parallel code generator, which is integrated within the PIPS compiler framework. It targets both shared and distributed memory systems using automatically generated OpenMP and MPI code.

## Résumé

Le but de cette thèse est d'exploiter efficacement le parallélisme présent dans les applications informatiques séquentielles afin de bénéficier des performances fournies par les multiprocesseurs, en utilisant une nouvelle méthodologie pour la parallélisation automatique des tâches au sein des compilateurs. Les caractéristiques clés de notre approche sont la prise en compte des contraintes de ressources et le caractère statique de l'ordonnancement des tâches. Notre méthodologie contient les techniques nécessaires pour la décomposition des applications en tâches et la génération de code parallèle équivalent, en utilisant une approche générique qui vise différents langages et architectures parallèles. Nous implémentons cette méthodologie dans le compilateur source-à-source PIPS. Cette thèse répond principalement à trois questions. Primo, comme l'extraction du parallélisme de tâches des codes séquentiels est un problème d'ordonnancement, nous concevons et implémentons un algorithme d'ordonnancement efficace, que nous nommons BDSC, pour la détection du parallélisme ; le résultat est un SDG ordonnancé, qui est une nouvelle structure de données de graphe de tâches. Secondo, nous proposons une nouvelle extension générique des représentations intermédiaires séquentielles en des représentations intermédiaires parallèles que nous nommons SPIRE, pour la représentation des codes parallèles. Enfin, nous développons, en utilisant BDSC et SPIRE, un générateur de code que nous intégrons dans PIPS. Ce générateur de code cible les systèmes à mémoire partagée et à mémoire distribuée via des codes OpenMP et MPI générés automatiquement.

# Contents

| Re           | emer                  | ciements                                                    | iv  |

|--------------|-----------------------|-------------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra                 | ıct                                                         | vi  |

| Re           | ésum                  | ıé                                                          | vii |

| In           | $\operatorname{trod}$ | $uction\ (en\ français)$                                    | 8   |

| 1            | Intr                  | roduction                                                   | 10  |

|              | 1.1                   | Context                                                     | 10  |

|              | 1.2                   | Motivation                                                  | 11  |

|              | 1.3                   | Contributions                                               | 13  |

|              | 1.4                   | Thesis Outline                                              | 14  |

| 2            | Per                   | spectives: Bridging Parallel Architectures and Software     | ;   |

|              | Par                   | allelism                                                    | 18  |

|              | 2.1                   | Parallel Architectures                                      | 19  |

|              |                       | 2.1.1 Multiprocessors                                       | 20  |

|              |                       | 2.1.2 Memory Models                                         | 22  |

|              | 2.2                   | Parallelism Paradigms                                       | 23  |

|              | 2.3                   | Mapping Paradigms to Architectures                          | 25  |

|              | 2.4                   | Program Dependence Graph (PDG)                              | 26  |

|              |                       | 2.4.1 Control Dependence Graph (CDG)                        | 26  |

|              |                       | 2.4.2 Data Dependence Graph (DDG)                           | 27  |

|              | 2.5                   | List Scheduling                                             | 28  |

|              |                       | 2.5.1 Background                                            | 28  |

|              |                       | 2.5.2 Algorithm                                             | 29  |

|              | 2.6                   | PIPS: Automatic Parallelizer and Code Transformation Frame- |     |

|              |                       | work                                                        | 32  |

|              |                       | 2.6.1 Transformer Analysis                                  | 33  |

|              |                       | 2.6.2 Precondition Analysis                                 | 33  |

|              |                       | 2.6.3 Array Region Analysis                                 | 34  |

|              |                       | 2.6.4 "Complexity" Analysis                                 | 36  |

|              |                       | 2.6.5 PIPS (Sequential) IR                                  | 37  |

|              | 2.7                   | Conclusion                                                  | 38  |

| 3            | Con                   | ncepts in Task Parallel Programming Languages               | 40  |

|              | 3.1                   | Introduction                                                | 41  |

|              | 3.2                   | Mandelbrot Set Computation                                  | 42  |

|              | 3.3                   | Task Parallelism Issues                                     | 44  |

| CONTERNICO | •  |

|------------|----|

| CONTENTS   | X1 |

|            |    |

|                  | 3.3.1 Task Creation                                     | . 44            |

|------------------|---------------------------------------------------------|-----------------|

|                  | 3.3.2 Synchronization                                   | . 44            |

|                  | 3.3.3 Atomicity                                         | . 45            |

| 3.               | 4 Parallel Programming Languages                        | . 45            |

|                  | 3.4.1 Cilk                                              | . 45            |

|                  | 3.4.2 Chapel                                            | . 47            |

|                  | 3.4.3 X10 and Habanero-Java                             | . 48            |

|                  | 3.4.4 OpenMP                                            | . 50            |

|                  | 3.4.5 MPI                                               | . 52            |

|                  | 3.4.6 OpenCL                                            |                 |

| 3.               | 1                                                       |                 |

| 3.               | 6 Conclusion                                            | . 59            |

| 4 S              | PIRE: A Generic Sequential to Parallel Intermediate Rep | <b>)-</b>       |

| re               | sentation Extension Methodology                         | <b>62</b>       |

| 4.               |                                                         |                 |

| 4.               | , 1                                                     |                 |

|                  | 4.2.1 Design Approach                                   |                 |

|                  | 4.2.2 Execution                                         |                 |

|                  | 4.2.3 Synchronization                                   |                 |

|                  | 4.2.4 Data Distribution                                 |                 |

| 4.               | P                                                       |                 |

|                  | 4.3.1 Sequential Core Language                          | . 76            |

|                  | 4.3.2 SPIRE as a Language Transformer                   | . 77            |

|                  | 4.3.3 Rewriting Rules                                   | . 80            |

| 4.               | 4 Validation: SPIRE Application to LLVM IR              | . 82            |

| 4.               | 5 Related Work: Parallel Intermediate Representations   | . 85            |

| 4.               | 6 Conclusion                                            | . 87            |

|                  | DSC: A Memory-Constrained, Number of Processor-Bou      | $\mathbf{nded}$ |

| $\mathbf{E}_{i}$ | xtension of DSC                                         | 90              |

| 5.               |                                                         |                 |

| 5.               | 0 0                                                     |                 |

|                  | 5.2.1 The DSC Algorithm                                 |                 |

|                  | 5.2.2 Dominant Sequence Length Reduction Warranty       |                 |

| 5.               |                                                         |                 |

|                  | 5.3.1 DSC Weaknesses                                    |                 |

|                  | 5.3.2 Resource Modeling                                 |                 |

|                  | 5.3.3 Resource Constraint Warranty                      |                 |

|                  | 5.3.4 Efficient Task-to-Cluster Mapping                 |                 |

|                  | 5.3.5 The BDSC Algorithm                                |                 |

| 5.               | 4 Related Work: Scheduling Algorithms                   | . 103           |

|                  | 5.4.1 Bounded Number of Clusters                        | . 103           |

|                  | 5.4.2 Cluster Regrouping on Physical Processors         | . 105           |

xii *CONTENTS*

|   | 5.5  | Conclusion                                                 | 6  |

|---|------|------------------------------------------------------------|----|

| 6 | BD   | SC-Based Hierarchical Task Parallelization 10              | 8  |

|   | 6.1  | Introduction                                               | 9  |

|   | 6.2  | Hierarchical Sequence Dependence DAG Mapping 11            | 0  |

|   |      | 6.2.1 Sequence Dependence DAG (SDG)                        | 0  |

|   |      | 6.2.2 Hierarchical SDG Mapping                             | 5  |

|   | 6.3  | Sequential Cost Models Generation                          | 7  |

|   |      | 6.3.1 From Convex Polyhedra to Ehrhart Polynomials 11      | 7  |

|   |      | 6.3.2 From Polynomials to Values                           | 1  |

|   | 6.4  | Reachability Analysis: The Path Transformer                | 4  |

|   |      | 6.4.1 Path Definition                                      | 4  |

|   |      | 6.4.2 Path Transformer Algorithm                           | 5  |

|   |      | 6.4.3 Operations on Regions using Path Transformers 13     | 2  |

|   | 6.5  | BDSC-Based Hierarchical Scheduling (HBDSC)                 | 4  |

|   |      | 6.5.1 Closure of SDGs                                      | 4  |

|   |      | 6.5.2 Recursive Top-Down Scheduling                        | 5  |

|   |      | 6.5.3 Iterative Scheduling for Resource Optimization 13    | 9  |

|   |      | 6.5.4 Complexity of HBDSC Algorithm                        | 0  |

|   |      | 6.5.5 Parallel Cost Models                                 | 2  |

|   | 6.6  | Related Work: Task Parallelization Tools                   | 4  |

|   | 6.7  | Conclusion                                                 | :6 |

| 7 | SPI  | RE-Based Parallel Code Transformations and Genera-         |    |

|   | tion |                                                            | 8  |

|   | 7.1  | Introduction                                               | 9  |

|   | 7.2  | Parallel Unstructured to Structured Transformation 15      | 0  |

|   |      | 7.2.1 Structuring Parallelism                              |    |

|   |      | 7.2.2 Hierarchical Parallelism                             | 5  |

|   | 7.3  | From Shared Memory to Distributed Memory Transformation 15 | 7  |

|   |      | 7.3.1 Related Work: Communications Generation 15           |    |

|   |      | 7.3.2 Difficulties                                         | 9  |

|   |      | 7.3.3 Equilevel and Hierarchical Communications 16         |    |

|   |      | 7.3.4 Equilevel Communications Insertion Algorithm 16      | 5  |

|   |      | 7.3.5 Hierarchical Communications Insertion Algorithm 16   |    |

|   |      | 7.3.6 Communications Insertion Main Algorithm 16           | 9  |

|   |      | 7.3.7 Conclusion and Future Work                           | 1  |

|   | 7.4  | Parallel Code Generation                                   | 5  |

|   |      | 7.4.1 Mapping Approach                                     | 5  |

|   |      | 7.4.2 OpenMP Generation                                    |    |

|   |      | 7.4.3 SPMDization: MPI Generation                          | 8  |

|   | 7.5  | Conclusion                                                 | 0  |

|          | •••  |

|----------|------|

| CONTENTS | XIII |

|          |      |

| 8  | $\mathbf{E}\mathbf{x}\mathbf{p}$ | erime   | ental Evaluation with PIPS                          | 1   | <b>82</b> |

|----|----------------------------------|---------|-----------------------------------------------------|-----|-----------|

|    | 8.1                              | Introd  | duction                                             |     | 183       |

|    | 8.2                              | Imple   | mentation of HBDSC- and SPIRE-Based Parallelization |     |           |

|    |                                  | Proce   | sses in PIPS                                        |     | 184       |

|    |                                  | 8.2.1   | Preliminary Passes                                  |     | 184       |

|    |                                  | 8.2.2   | Task Parallelization Passes                         |     | 187       |

|    |                                  | 8.2.3   | OpenMP Related Passes                               |     | 189       |

|    |                                  | 8.2.4   | MPI Related Passes: SPMDization                     |     | 190       |

|    | 8.3                              | Exper   | rimental Setting                                    |     | 191       |

|    |                                  | 8.3.1   | Benchmarks: ABF, Harris, Equake, IS and FFT         |     |           |

|    |                                  | 8.3.2   | Experimental Platforms: Austin and Cmmcluster       |     | 193       |

|    |                                  | 8.3.3   | Effective Cost Model Parameters                     |     |           |

|    | 8.4                              | Proto   | col                                                 |     | 194       |

|    | 8.5                              | BDSC    | C vs. DSC                                           |     | 195       |

|    |                                  | 8.5.1   | Experiments on Shared Memory Systems                |     | 195       |

|    |                                  | 8.5.2   | Experiments on Distributed Memory Systems           |     |           |

|    | 8.6                              | Sched   | uling Robustness                                    |     |           |

|    | 8.7                              | Faust   | Parallel Scheduling vs. BDSC                        |     | 201       |

|    |                                  | 8.7.1   | OpenMP Version in Faust                             |     |           |

|    |                                  | 8.7.2   | _                                                   |     |           |

|    |                                  | 8.7.3   | Experimental Comparison                             |     |           |

|    | 8.8                              | Concl   | usion                                               | . : | 203       |

| 9  | Cor                              | ıclusio | on                                                  | 2   | 206       |

|    | 9.1                              | Contr   | ributions                                           | . : | 206       |

|    | 9.2                              | Futur   | e Work                                              | . : | 209       |

| Co | onclu                            | ısion ( | (en français)                                       | 2   | 217       |

# List of Tables

| $\frac{2.1}{2.2}$ | Multicores proliferation                                                                                    | 21  |

|-------------------|-------------------------------------------------------------------------------------------------------------|-----|

|                   | complexity analysis                                                                                         | 37  |

| 3.1               | Summary of parallel languages constructs                                                                    | 59  |

| 4.1               | Mapping of SPIRE to parallel languages constructs (terms in parentheses are not currently handled by SPIRE) | 67  |

| 6.1               | Execution and communication time estimations for Harris us-                                                 |     |

|                   | ing PIPS default cost model ( $N$ and $M$ variables represent the input image size)                         | 121 |

| 6.2               | Comparison summary between different parallelization tools .                                                | 146 |

| 8.1               | CPI for the Austin and Cmmcluster machines, plus the trans-                                                 |     |

| 0.0               | fer cost of one byte $\beta$ on the Cmmcluster machine (in #cycles)                                         | 194 |

| 8.2               | Run-time sensitivity of BDSC with respect to static cost es-                                                | 201 |

|                   | timation (in ms for Harris and ABF; in s for equake and IS).                                                | 201 |

# List of Figures

| 1    | Une implementation séquentielle en C de la fonction main de l'algorithme de Harris | 4  |

|------|------------------------------------------------------------------------------------|----|

| 2    | Le graphe de flôts de données de l'algorithme de Harris $$                         | 4  |

| 3    | Organisation de la thèse : le bleu indique les contributions de                    |    |

|      | la thèse ; une ellipse, un processus; et un rectangle, résultats .                 | 8  |

| 1.1  | Sequential C implementation of the main function of Harris .                       | 12 |

| 1.2  | Harris algorithm data flow graph                                                   | 12 |

| 1.3  | Thesis outline: blue indicates thesis contributions; an ellipse,                   |    |

|      | a process; and a rectangle, results                                                | 16 |

| 2.1  | A typical multiprocessor architectural model $\dots$                               | 20 |

| 2.2  | Memory models                                                                      | 22 |

| 2.3  | Rewriting of data parallelism using the task parallelism model                     | 24 |

| 2.4  | Construction of the control dependence graph                                       | 27 |

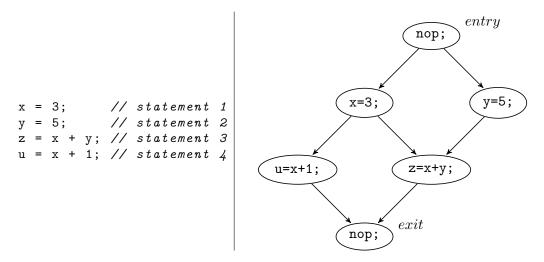

| 2.5  | Example of a C code and its data dependence graph                                  | 28 |

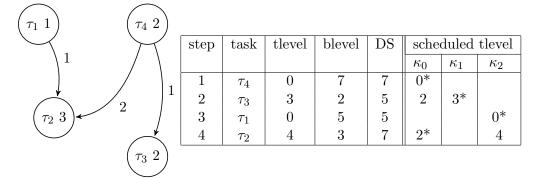

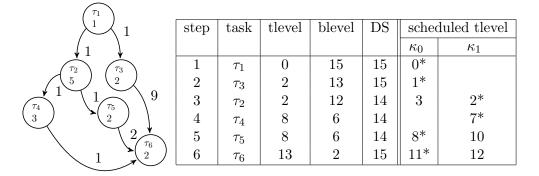

| 2.6  | A Directed Acyclic Graph (left) and its associated data (right)                    | 30 |

| 2.7  | Example of transformer analysis                                                    | 34 |

| 2.8  | Example of precondition analysis                                                   | 34 |

| 2.9  | Example of array region analysis                                                   | 35 |

| 2.10 | Simplified Newgen definitions of the PIPS IR                                       | 37 |

| 3.1  | Result of the Mandelbrot set                                                       | 43 |

| 3.2  | Sequential C implementation of the Mandelbrot set                                  | 43 |

| 3.3  | Cilk implementation of the Mandelbrot set (P is the number                         |    |

|      | of processors)                                                                     | 46 |

| 3.4  | Chapel implementation of the Mandelbrot set                                        | 47 |

| 3.5  | X10 implementation of the Mandelbrot set                                           | 49 |

| 3.6  | A clock in X10 (left) and a phaser in Habanero-Java (right) .                      | 50 |

| 3.7  | C OpenMP implementation of the Mandelbrot set                                      | 51 |

| 3.8  | MPI implementation of the Mandelbrot set (P is the number                          |    |

|      | of processors)                                                                     | 53 |

| 3.9  | OpenCL implementation of the Mandelbrot set                                        | 55 |

| 3.10 | A hide-and-seek game (X10, HJ, Cilk)                                               | 57 |

|      | Example of an atomic directive in OpenMP                                           | 58 |

| 3.12 | Data race on ptr with Habanero-Java                                                | 58 |

| 4.1  | OpenCL example illustrating a parallel loop                                        | 68 |

| 4.2  | ${\tt forall}$ in Chapel, and its SPIRE core language representation               | 68 |

| 4.3  | A C code, and its unstructured parallel control flow graph                         |    |

|      | representation                                                                     | 69 |

| 4.4  | parallel sections in OpenMP, and its SPIRE core language representation                                                                | 69    |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.5  | OpenCL example illustrating spawn and barrier statements .                                                                             | 71    |

| 4.6  | Cilk and OpenMP examples illustrating an atomically-synchroniz                                                                         |       |

| 1.0  | statement                                                                                                                              | 71    |

| 4.7  | X10 example illustrating a future task and its synchronization                                                                         | 72    |

| 4.8  | A phaser in Habanero-Java, and its SPIRE core language                                                                                 |       |

|      | representation                                                                                                                         | 73    |

| 4.9  | Example of Pipeline Parallelism with phasers                                                                                           | 73    |

| 4.10 | MPI example illustrating a communication, and its SPIRE                                                                                |       |

|      | core language representation                                                                                                           | 75    |

| 4.11 | SPIRE core language representation of a non-blocking send $$ .                                                                         | 75    |

| 4.12 | SPIRE core language representation of a non-blocking receive                                                                           | 75    |

| 4.13 | SPIRE core language representation of a broadcast                                                                                      | 75    |

| 4.14 | Stmt and SPIRE(Stmt) syntaxes                                                                                                          | 76    |

| 4.15 | Stmt sequential transition rules                                                                                                       | 77    |

| 4.16 | SPIRE(Stmt) synchronized transition rules                                                                                              | 80    |

| 4.17 | if statement rewriting using while loops                                                                                               | 82    |

| 4.18 | Simplified Newgen definitions of the LLVM IR                                                                                           | 83    |

| 4.19 | A loop in C and its LLVM intermediate representation                                                                                   | 84    |

| 4.20 | SPIRE (LLVM IR)                                                                                                                        | 84    |

| 4.21 | An example of a spawned outlined sequence                                                                                              | 85    |

| 5.1  | A Directed Acyclic Graph (left) and its scheduling (right); starred top levels (*) correspond to the selected clusters                 | 94    |

| 5.2  | Result of DSC on the graph in Figure 5.1 without (left) and                                                                            | 0 1   |

| ·-   | with (right) DSRW                                                                                                                      | 95    |

| 5.3  | A DAG amenable to cluster minimization (left) and its BDSC                                                                             |       |

|      |                                                                                                                                        | 100   |

| 5.4  | DSC (left) and BDSC (right) cluster allocation                                                                                         | 100   |

| 6.1  | Abstract syntax trees Statement syntax                                                                                                 | 110   |

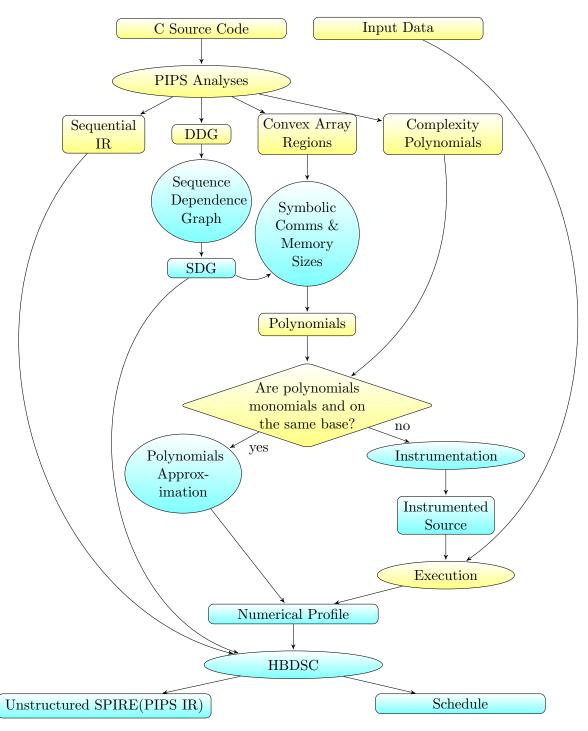

| 6.2  | Parallelization process: blue indicates thesis contributions; an                                                                       |       |

|      | ellipse, a process; and a rectangle, results                                                                                           | 111   |

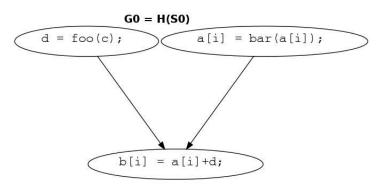

| 6.3  | Example of a C code (left) and the DDG $D$ of its internal $S$ sequence (right)                                                        | 114   |

| 6.4  | SDGs of $S$ (top) and $S0$ (bottom) computed from the DDG (see the right of Figure 6.3); $S$ and $S0$ are specified in the left        | . 1 - |

|      | of Figure 6.3                                                                                                                          | 115   |

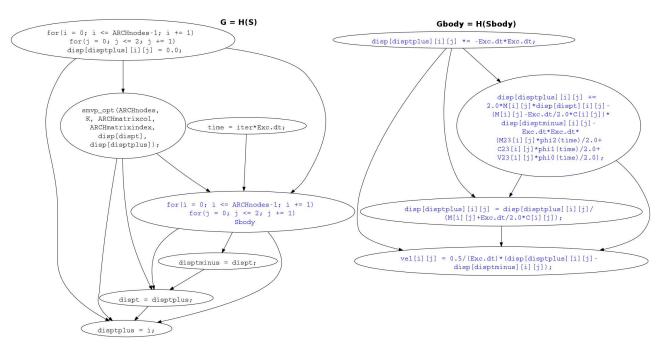

| 6.5  | SDG $G$ , for a part of equake $S$ given in Figure 6.7; $Gbody$ is the SDG of the body $Sbody$ (logically included into $G$ via $H$ ). | 117   |

| 6.6  | Example of the execution time estimation for the function Multiply of the code Harris; each comment provides the                                                                                                                                               |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | complexity estimation of the statement below ( $N$ and $M$ are assumed to be global variables)                                                                                                                                                                 | 120 |

| 6.7  | Instrumented part of equake $(Sbody)$ is the inner loop sequence                                                                                                                                                                                               |     |

| 6.8  | Numerical results of the instrumented part of equake (instrume                                                                                                                                                                                                 |     |

| 0.0  | ted_equake.in)                                                                                                                                                                                                                                                 | 123 |

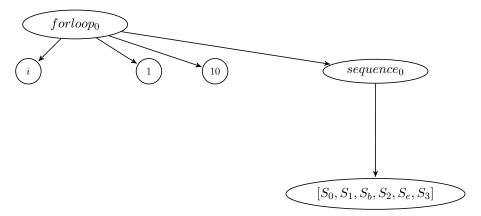

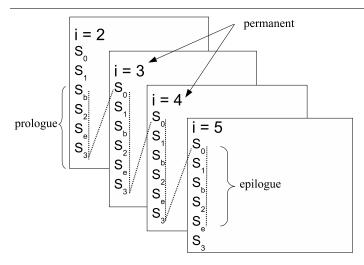

| 6.9  | An example of a subtree of root $forloop_0$                                                                                                                                                                                                                    | 125 |

| 6.10 | An example of a path execution trace from $S_b$ to $S_e$ in the                                                                                                                                                                                                |     |

|      | subtree $forloop_0$                                                                                                                                                                                                                                            | 126 |

| 6.11 | An example of a C code and the path transformer of the sequence between $S_b$ and $S_e$ ; $M$ is $\bot$ , since there are no loops in the code                                                                                                                 | 129 |

| 6.12 | An example of a C code and the path transformer of the sequence of calls and test between $S_b$ and $S_e$ ; $M$ is $\bot$ , since                                                                                                                              | 120 |

|      | there are no loops in the code                                                                                                                                                                                                                                 | 130 |

| 6.13 | An example of a C code and the path transformer between $S_b$ and $S_e$                                                                                                                                                                                        | 133 |

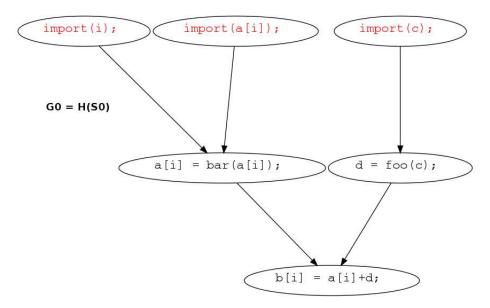

| 6.14 | Closure of the SDG $G0$ of the C code $S0$ in Figure 6.3, with additional import entry vertices                                                                                                                                                                | 136 |

| 6.15 | topsort(G) for the hierarchical scheduling of sequences                                                                                                                                                                                                        |     |

|      | Scheduled SDG for Harris, using $P=3$ cores; the scheduling                                                                                                                                                                                                    |     |

|      | information via $\mathtt{cluster}(\tau)$ is also printed inside each vertex of the SDG                                                                                                                                                                         | 139 |

| 6.17 | After the first application of BDSC on $S = \text{sequence}(S_0; S_1)$ , failing with "Not enough memory"                                                                                                                                                      | 141 |

| 6.18 | Hierarchically (via $H$ ) Scheduled SDGs with memory resource minimization after the second application of BDSC (which succeeds) on $sequence(S_0;S_1)$ ( $\kappa_i = cluster(\sigma(S_i))$ ). To keep the picture readable, only communication edges are fig- |     |

|      | ured in these SDGs                                                                                                                                                                                                                                             | 142 |

| 7.1  | Parallel code transformations and generation: blue indicates this chapter contributions; an ellipse, a process; and a rect-                                                                                                                                    |     |

|      | angle, results                                                                                                                                                                                                                                                 | 151 |

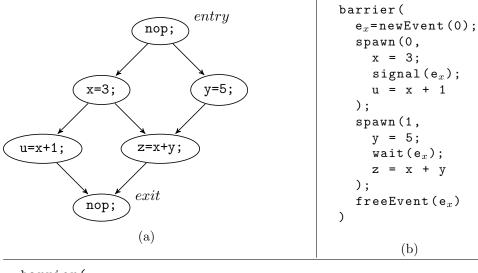

| 7.2  | Unstructured parallel control flow graph (a) and event (b) and structured representations (c)                                                                                                                                                                  | 152 |

| 7.3  | A part of Harris, and one possible SPIRE core language representation                                                                                                                                                                                          | 156 |

| 7.4  | SPIRE representation of a part of Harris, non optimized (left) and optimized (right)                                                                                                                                                                           |     |

| 7.5  | A simple C code (hierarchical), and its SPIRE representation                                                                                                                                                                                                   |     |

|      |                                                                                                                                                                                                                                                                |     |

| 7.6  | An example of a shared memory C code and its SPIRE code efficient communication primitive-based distributed memory         |

|------|----------------------------------------------------------------------------------------------------------------------------|

|      | equivalent                                                                                                                 |

| 7.7  | Two examples of C code with non-uniform dependences 160                                                                    |

| 7.8  | An example of a C code and its read and write array regions                                                                |

| •••  | analysis for two communications from $S_0$ to $S_1$ and to $S_2$ 161                                                       |

| 7.9  | An example of a C code and its in and out array regions                                                                    |

|      | analysis for two communications from $S_0$ to $S_1$ and to $S_2$ 162                                                       |

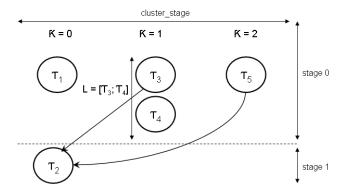

| 7.10 |                                                                                                                            |

| 1.10 | of hierarchy in a parallel code; the levels are specified with                                                             |

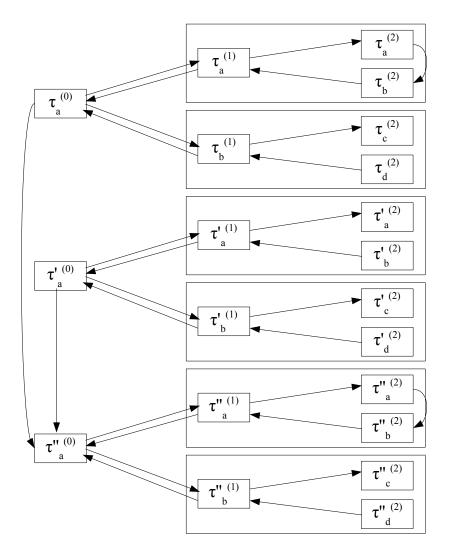

|      | the superscripts on $\tau$ 's                                                                                              |

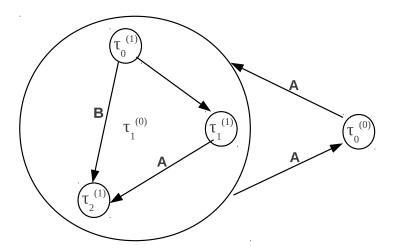

| 7 11 | Equilevel and hierarchical communications                                                                                  |

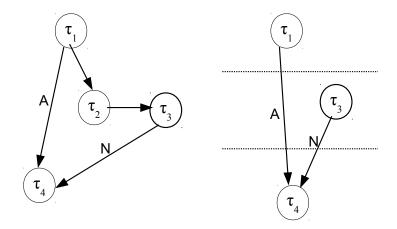

|      | A part of an SDG and the topological sort order of predeces-                                                               |

| 1.12 | sors of $\tau_4$                                                                                                           |

| 7 13 | Communications generation from a region using region_to_coms                                                               |

| 1.10 | function                                                                                                                   |

| 7 14 | Equilevel and hierarchical communications generation and                                                                   |

| 1.14 | SPIRE distributed memory representation of a C code 172                                                                    |

| 7 15 |                                                                                                                            |

| 1.15 | Graph illustration of communications made in the C code of Figure 7.14; equilevel in green arcs, hierarchical in black 173 |

| 7 16 | Equilevel and hierarchical communications generation after                                                                 |

| 1.10 | •                                                                                                                          |

|      | optimizations: the current cluster executes the last nested                                                                |

|      | spawn (left) and barriers with one spawn statement are re-                                                                 |

| 7 17 | moved (right)                                                                                                              |

| 1.11 |                                                                                                                            |

| 7 10 | task generated code                                                                                                        |

| 1.10 | SPIRE representation of a C code, and its OpenMP hierar-                                                                   |

| 7 10 | chical task generated code                                                                                                 |

| 7.19 | SPIRE representation of a part of Harris, and its MPI gener-                                                               |

|      | ated code                                                                                                                  |

| 8.1  | Parallelization process: blue indicates thesis contributions; an                                                           |

| 0.1  | ellipse, a pass or a set of passes; and a rectangle, results 185                                                           |

| 8.2  | Executable (harris.tpips) for harris.c                                                                                     |

| 8.3  | A model of an MPI generated code                                                                                           |

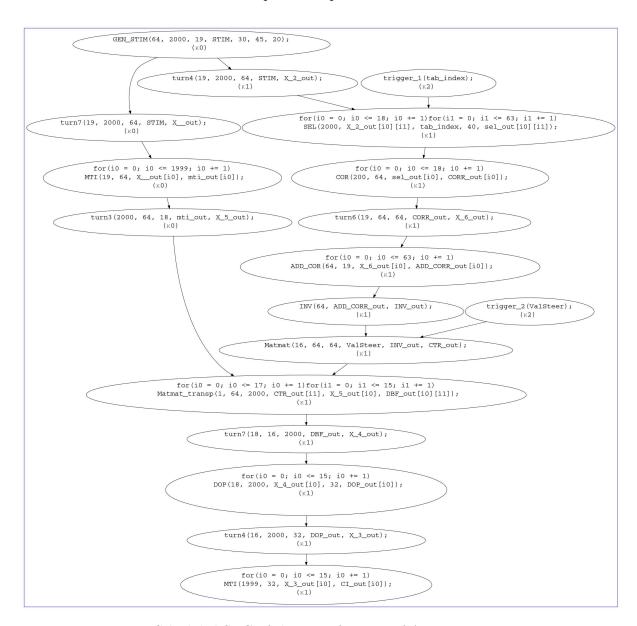

| 8.4  | Scheduled SDG of the main function of ABF 192                                                                              |

| 8.5  | Steps for the rewriting of data parallelism to task parallelism                                                            |

| 0.0  | using the tiling and unrolling transformations 196                                                                         |

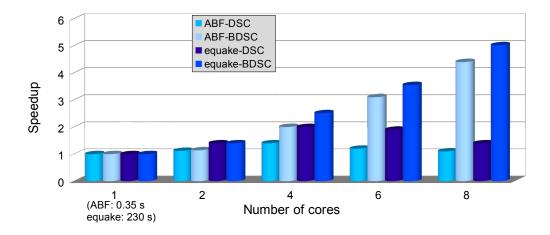

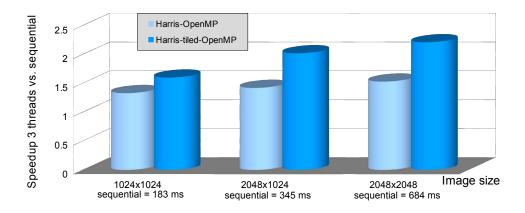

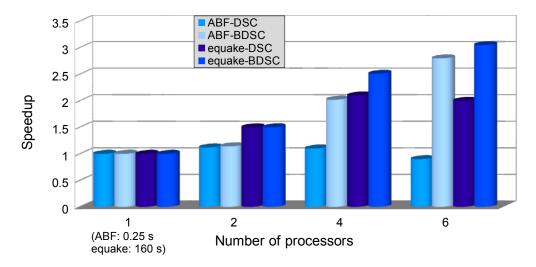

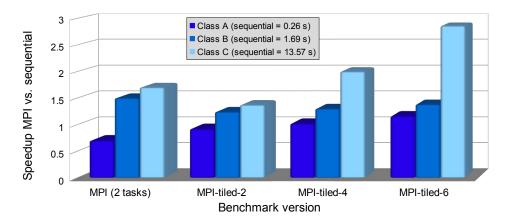

| 8.6  | ABF and equake speedups with OpenMP 196                                                                                    |

| 8.7  | Speedups with OpenMP: impact of tiling (P=3) 197                                                                           |

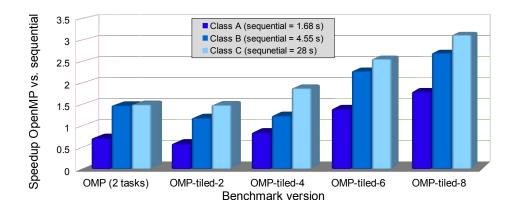

| 8.8  | Speedups with OpenMP for different class sizes (IS) 198                                                                    |

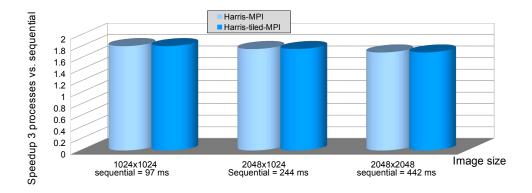

| 8.9  | ABF and equake speedups with MPI 199                                                                                       |

| 8.10 | Speedups with MPI: impact of tiling (P=3) 199                                                                              |

|      | Speedups with MPI for different class sizes (IS) 200                                                                       |

| U.T. | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~                                                                                      |

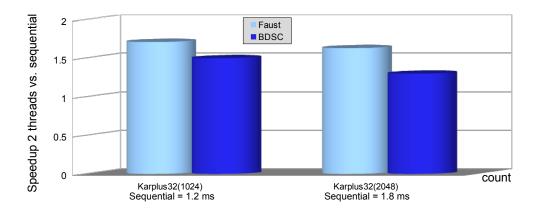

| 8.12 | Run-time | comparison | (BDSC vs. | Faust for | Karplus3  | (2) |  |  | 203 |

|------|----------|------------|-----------|-----------|-----------|-----|--|--|-----|

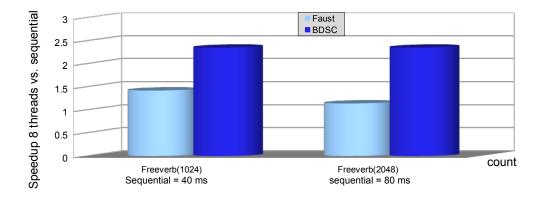

| 8.13 | Run-time | comparison | (BDSC vs. | Faust for | Freeverb) | ) . |  |  | 203 |

## Introduction (en français)

I live and don't know how long, I'll die and don't know when, I am going and don't know where, I wonder that I am happy. Martinus Von Biberach

#### Contexte

La loi de Moore [83] postule que, tout au long de l'histoire du matériel informatique, le nombre de transistors utilisés dans les circuits intégrés va doubler tous les deux ans environ. Cette croissance s'accompagnait, jusqu'à très récemment encore, de vitesses d'horloge toujours plus élevées, afin de d'améliorer encore plus les performances des processeurs (ou cœurs). Le passage de la fabrication de microprocesseurs uniques à la conception de machines parallèles est en partie dû à la croissance de la consommation exagérée d'énergie liée à cette augmentation de fréquence. Le nombre de transistors continue toutefois à augmenter afin d'intégrer plus de cœurs et assurer un passage à l'échelle proportionnel de performance pour des applications scientifiques toujours plus sophistiquées.

En dépit de la validité de la loi de Moore jusqu'à maintenant, la performance des cœurs a ainsi cessé d'augmenter après 2003. Du coup, la scalabilité des applications, qui correspond à l'idée que les performances sont accrues lorsque des ressources supplémentaires sont allouées à la résolution d'un problème, n'est plus garantie. Pour comprendre ce problème, il est nécessaire de jeter un coup d'œil à la loi dite d'Amdahl [16]. Selon cette loi, l'accélération d'un programme à l'aide de plusieurs processeurs est limitée par le temps nécessaire à l'exécution de sa partie séquentielle ; en plus du nombre de processeurs, l'algorithme lui-même limite également cette accélération.

Afin de profiter des performances que les multiprocesseurs peuvent fournir, il faut bien évidemment toujours arriver à exploiter efficacement le parallélisme présent dans les applications. C'est une tâche difficile pour les programmeurs, surtout si ce programmeur est un physicien, un mathématicien ou un informaticien pour qui la compréhension de l'application est difficile car elle n'est pas la sienne. Bien sûr, nous pourrions dire au programmeur : "penses parallèle"! Mais les êtres humains ont tendance à penser, pour l'essentiel, de manière séquentielle. Par conséquent, détecter le parallélisme présent dans un code séquentiel et, automatiquement ou non, écrire un code parallèle efficace équivalent a été, et restera sans doute pendant un certain temps encore, un problème majeur.

Pour d'évidentes raisons économiques, une application parallèle, exprimée dans un modèle de programmation parallèle, doit être non seulement efficace mais également aussi portable que possible, c'est-à-dire être telle qu'il

ne faille pas avoir à réécrire ce code parallèle pour utiliser une autre machine que celle prévue initialement. Pourtant, la prolifération actuelle de modèles de programmation parallèle distincts fait que le choix d'un modèle général n'est, manifestement, pas évident, à moins de disposer d'un langage parallèle à la fois efficace et capable d'être compilé pour tous les types d'architectures actuelles et futures, ce qui n'est pas encore le cas. Par conséquent, cette écriture de code parallèle doit être fondée sur une approche générique, c'est à dire susceptible d'être facilement adaptée à un groupe de langages aussi large que possible, afin d'offrir une meilleure chance de portabilité.

### Motivation

Pour que la programmation pour multiprocesseurs conduise à de bonnes performances sans aller jusqu'à avoir à penser "parallèle", une plate-forme logicielle de parallélisation automatique visant à exploiter efficacement les cœurs est nécessaire. Si divers modes de parallélisme existent, la prolifération de processeurs multi-cœurs offrant des pipelines courts et des fréquences d'horloge relativement basses et la pression que le simple modèle de parallélisme de données impose à la bande passante de la mémoire ont fait de telle sorte que la prise en compte du parallélisme à gros grain apparait comme inévitable pour améliorer les performances.

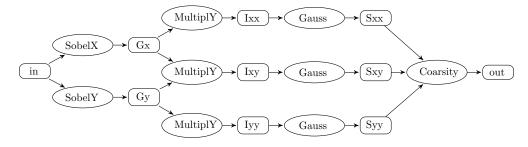

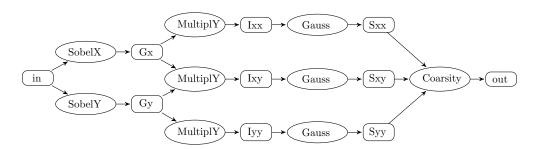

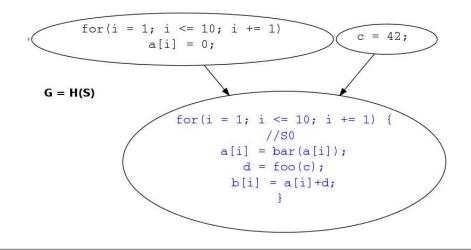

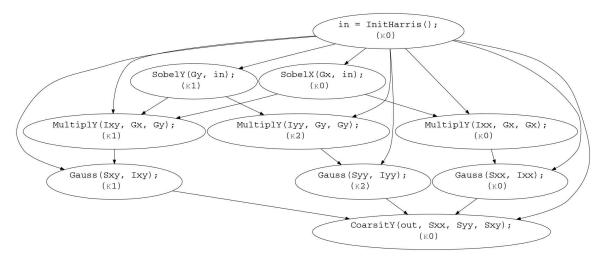

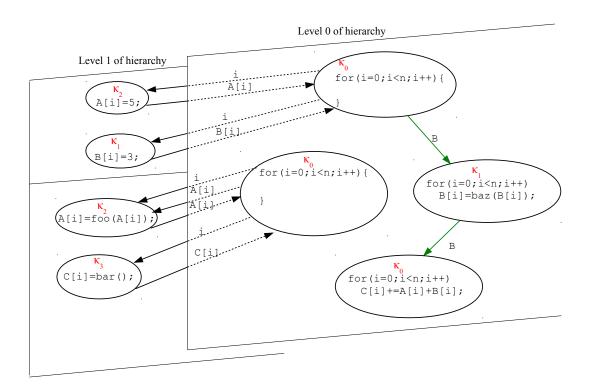

La première étape d'un processus de parallélisation nous semble donc être d'exposer la concurrence de tâche présente dans les programmes, en décomposant les applications en groupes pipelinés d'instructions, puisque les algorithmes peuvent souvent être décrits comme de tels ensembles de tâches. Pour illustrer l'importance de la parallélisation au niveau tâche, nous donnons ici un exemple simple : l'algorithme de recherche de coins dans une image proposé par Harris [96]: il est fondé sur de l'autocorrélation pixel par pixel, en utilisant une chaîne de fonctions, à savoir Sobel, Multiplication, Gauss, et Coarsity. La figure 1 illustre ce processus. Plusieurs chercheurs ont déjà parallélisé et adapté cet algorithme sur des architectures parallèles telles que le processeur CELL [95].

La figure 2 montre une instance de partitionnement possible, réalisée à la main, de l'algorithme de Harris (voir aussi [95]). L'algorithme de Harris peut ainsi être décomposé en une succession de deux à trois tâches simultanées (ellipses sur la figure), en faisant par ailleurs abstraction du parallélisme de données potentiellement présent. L'automatisation de cette approche intuitive, et donc l'extraction automatique de tâches et la parallélisation d'applications de ce type, est la motivation qui sous-tend cette thèse.

Cependant, la détection du parallélisme de tâches et la génération de code efficace s'appuient sur des analyses complexes de dépendances de données, de communication, de synchronisation, etc. Ces différentes analyses peuvent, de facto, être dès maintenant fournies en grande partie par des

```

void main(int argc, char *argv[]){

float (*Gx)[N*M], (*Gy)[N*M], (*Ixx)[N*M],

(*Iyy)[N*M], (*Ixy)[N*M], (*Sxx)[N*M],

(*Sxy)[N*M], (*Syy)[N*M], (*in)[N*M];

in = InitHarris();

/* Now we run the Harris procedure */

//Sobel

SobelX(Gx, in);

SobelY(Gy, in);

//Multiply

MultiplY(Ixx, Gx, Gx);

MultiplY(Iyy, Gy, Gy);

MultiplY(Ixy, Gx, Gy);

//Gauss

Gauss(Sxx, Ixx);

Gauss(Syy, Iyy);

Gauss(Sxy, Ixy);

//Coarsity

CoarsitY(out, Sxx, Syy, Sxy);

return;

```

Figure 1: Une implementation séquentielle en C de la fonction main de l'algorithme de Harris

plateformes logicielles de compilation. Ainsi, la délégation au logiciel du "penser parallèle", construite sur la mobilisation d'analyses automatiques déjà existantes de dépendances de données, parait viable, et peut permettre d'espérer voir gérées tout à la fois la granularité présente dans les codes séquentiels et les contraintes de ressources telles que la taille de la mémoire ou le nombre de processeurs, contraintes qui ont un impact certain sur ce processus de parallélisation.

Figure 2: Le graphe de flôts de données de l'algorithme de Harris

La parallélisation automatique de tâches a été étudiée depuis presque un demi-siècle. Le problème de l'extraction d'un parallélisme optimal avec des

communications optimales est, dans toute sa généralité, un problème NPcomplet [47]. Plusieurs travaux ont tenté d'automatiser la parallélisation de programmes en utilisant différents niveaux de granularité. Métis [62] et d'autres outils de partitionnement de graphe visent à attribuer la même quantité de travail aux processeurs, avec de petites quantités de communication entre ces processeurs, mais la structure du graphe ne fait pas de distinction entre les boucles, les appels de fonction, etc. Les étapes cruciales de construction de graphe et de génération de code parallèle sont absents. Sarkar [98] met en œuvre une méthode de compilation pour le problème de partitionnement pour multiprocesseurs. Un programme est divisé en tâches parallèles au moment de la compilation, puis celles-ci sont fusionnées jusqu'à ce qu'une partition avec le plus petit temps d'exécution parallèle, en présence des surcouts (ordonnancement et communication), soit trouvée. Malheureusement, cet algorithme ne prend pas en compte les contraintes de ressources, qui sont des facteurs importants pour cibler des architectures réelles. Tous ces outils de parallélisation sont dédiés à un modèle de programmation particulier: il y a manifestement un manque d'abstraction générique du parallélisme (exécution parallèle, synchronisation et distribution de données). Ils ne répondent donc pas à la question de la portabilité.

Dans cette thèse, nous développons une méthodologie de parallélisation de tâches automatique pour les compilateurs : les caractéristiques principales sur lesquelles nous nous concentrons sont les contraintes de ressources et l'ordonnancement statique. Elle comprend les techniques nécessaires pour décomposer les applications en tâches et générer le code parallèle équivalent, en utilisant une approche générique qui cible différents langages parallèles et donc différentes architectures. Nous appliquons cette méthodologie à l'outil existant PIPS [59], une plate-forme de compilation source-à-source.

### Contributions

Notre objectif est de développer un nouvel outil et des algorithmes pour la parallélisation automatique de tâches ; nous souhaitons qu'ils prennent en compte certaines contraintes de ressources et également être utiles en général pour les langages parallèles existants. Ainsi, les principales contributions de cette thèse sont les suivantes :

- 1. un nouvel algorithme hiérarchique d'ordonnancement (HBDSC) qui utilise :

- une nouvelle structure de données pour représenter les programmes parallèles partitionnés sous forme d'un graphe acyclique que nous nommons SDG,

- une extension, appelée "DSC borné" (BDSC), de l'algorithme d'ordonnancement DSC [111] capable de gérer simultanément

- deux contraintes de ressources, à savoir une taille mémoire bornée par processeur et un nombre borné de processeurs, qui sont des paramètres clés lors de l'ordonnancement des tâches sur les multiprocesseurs réels,

- un nouveau modèle de coût fondé sur l'estimation de la complexité en temps d'exécution, la définition d'approximations polyédriques convexes de la taille des tableaux de données et l'instrumentation de code pour l'étiquetage des sommets et les arêtes du SDG;

- 2. une nouvelle approche pour l'adaptation des plates-formes de parallélisation automatique aux langages parallèles via :

- SPIRE, une nouvelle méthodologie d'extension au parallélisme des représentations intermédiaires (RI) utilisées dans les compilateurs, pour la conception des RIs parallèles,

- le déploiement de SPIRE pour la parallélisation automatique au niveau tâche de programmes parallèles dans le compilateur PIPS [59];

- 3. une implémentation dans le compilateur source-à-source PIPS de :

- la parallélisation fondée sur HBDSC des programmes encodés dans la RI parallèle de PIPS dérivée de SPIRE,

- la génération de code parallèle fondée sur SPIRE pour deux langages parallèles : OpenMP [4] et MPI [3] ;

- 4. des mesures de performance de notre approche de parallélisation, sur la base de :

- cinq programmes significatifs, ciblant à la fois les architectures à mémoire partagée et distribuée : deux benchmarks de traitement d'image et de signal, Harris [54] et ABF [52], le benchmark equake [22] de SPEC2001, le benchmark IS [87] extrait de NAS et un code de FFT [8],

- leurs translations automatiques en deux langages parallèles : OpenMP [4] et MPI [3],

- et, enfin, une étude comparative entre notre implémentation de parallélisme de tâche dans PIPS et celle du langage de traitement de signal audio Faust [88], en utilisant deux programmes de Faust : Karplus32 et Freeverb. Nous choisissons Faust puisqu'il s'agit d'un compilateur open-source qui génère également des tâches parallèles automatiquement en OpenMP.

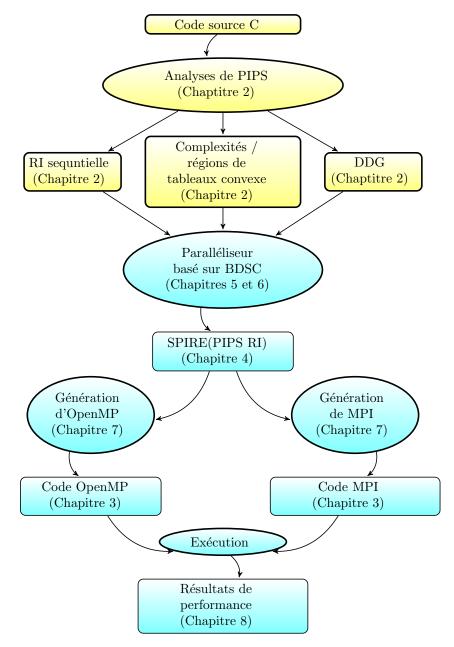

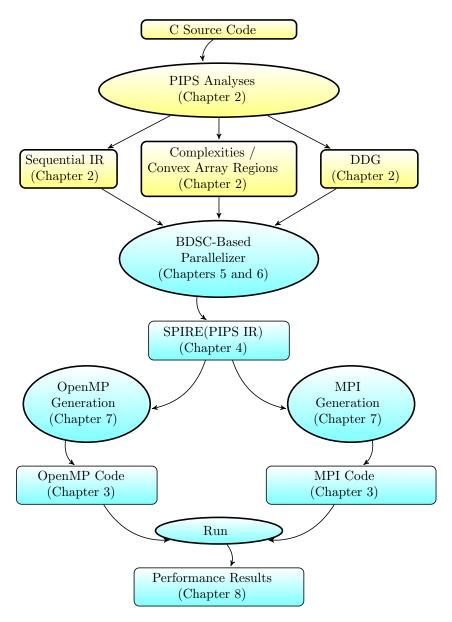

### Organisation

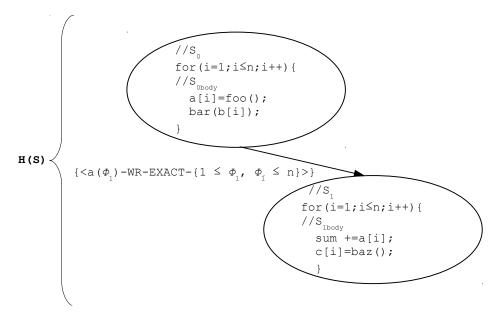

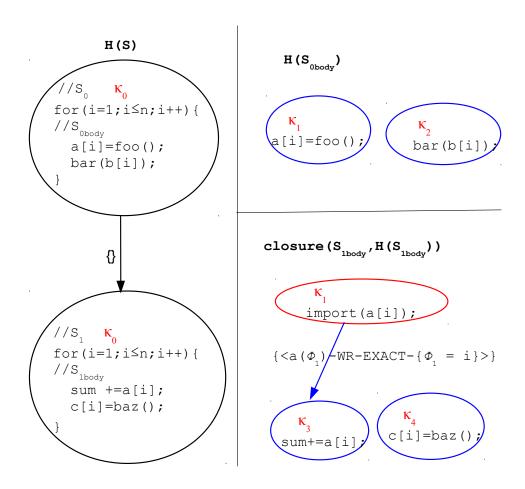

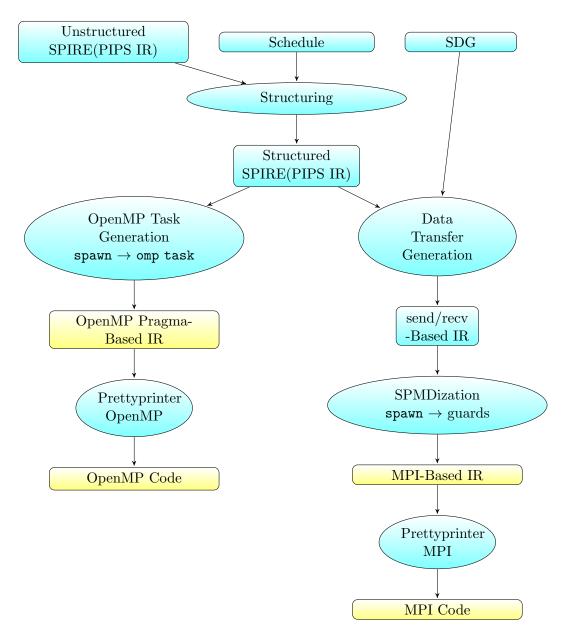

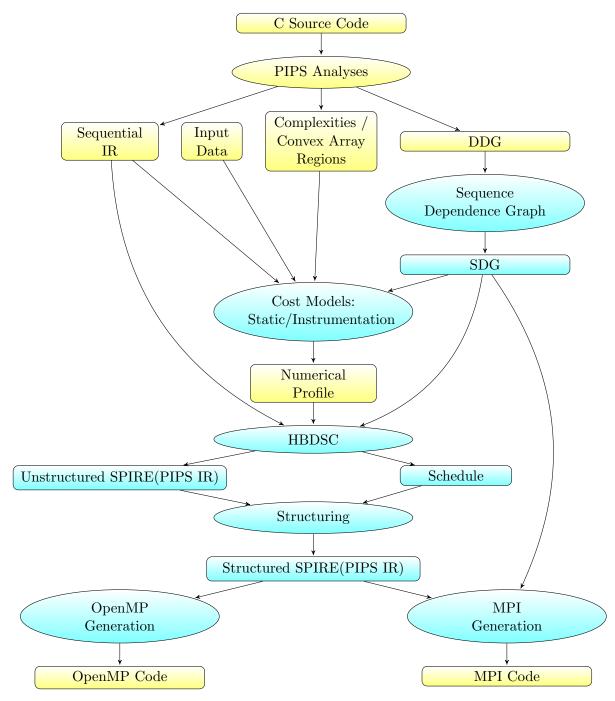

Cette thèse est organisée en neuf chapitres. La figure 3 montre comment ces chapitres peuvent être interprétés dans le contexte d'une chaîne de parallélisation.

Le chapitre 2 fournit un bref historique des concepts d'architectures, de parallélisme, des langages et des compilateurs utilisés dans les chapitres suivants.

Le chapitre 3 examine sept langages de programmation parallèles actuels et efficaces afin de déterminer et de classifier leurs constructions parallèles. Cela permet de définir un noyau de langage parallèle qui joue le rôle d'une représentation intermédiaire parallèle générique lors de la parallélisation de programmes séquentiels.

Cette proposition, appelée la méthodologie SPIRE, est développée dans le chapitre 4. SPIRE exploite les infrastructures de compilation existantes pour représenter les constructions à la fois de contrôle et de données présentes dans les langages parallèles tout en préservant autant que possible les analyses existantes pour les codes séquentiels. Pour valider cette approche dans la pratique, nous utilisons PIPS, une plate-forme de compilation source-à-source, comme un cas d'utilisation pour mettre à jour sa représentation intermédiaire séquentielle en une RI parallèle.

Puisque le but principal de cette thèse est la parallélisation automatique de tâches, l'extraction du parallélisme de tâche des codes séquentiels est une étape clé dans ce processus, que nous considérons comme un problème d'ordonnancement. Le chapitre 5 introduit ainsi une nouvelle heuristique automatique et efficace d'ordonnancement appelée BDSC pour les programmes parallèles en présence de contraintes de ressources sur le nombre de processeurs et la taille de leur mémoire locale.

Le processus de parallélisation que nous introduisons dans cette thèse utilise BDSC pour trouver un bon ordonnancement des tâches d'un programme sur les machines cibles et SPIRE pour générer le code source parallèle. Le chapitre 6 couple BDSC avec des modèles de coûts sophistiqués pour donner un nouvel algorithme de parallélisation.

Le chapitre 7 décrit comment nous pouvons générer des codes parallèles équivalents dans les deux langages cibles OpenMP et MPI, sélectionnés lors de l'étude comparative présentée dans le chapitre 3. Grâce à SPIRE, nous montrons comment la génération de code s'avère efficace tout en restant relativement simple.

Pour vérifier l'efficacité et la robustesse de notre travail, des résultats expérimentaux sont présentés dans le chapitre 8. Ils suggèrent que la parallélisation fondée sur SPIRE et BDSC, tout en gérant efficacement des ressources, conduit à des accélérations de parallélisation importantes sur les deux systèmes à mémoire partagée et distribuée. Nous comparons également notre implémentation de la génération de omp task dans PIPS avec la

génération de omp sections dans le compilateur Faust. Nous concluons dans le chapitre 9.

Figure 3: Organisation de la thèse : le bleu indique les contributions de la thèse ; une ellipse, un processus; et un rectangle, résultats

## Introduction

I live and don't know how long, I'll die and don't know when, I am going and don't know where, I wonder that I am happy. Martinus Von Biberach

### 1.1 Context

Moore's law [83] states that, over the history of computing hardware, the number of transistors on integrated circuits doubles approximately every two years. Recently, the shift from fabricating microprocessors to parallel machines designs was partly because of the growth in power consumption due to high clock speeds, required to improve performance in single processor (or core) chips. The transistor count is still increasing in order to integrate more cores and ensure proportional performance scaling.

In spite of the validity of Moore's law till now, the performance of cores stopped increasing after 2003. Thus, the scalability of applications, which calls for increased performance when resources are added, is not guaranteed. To understand this issue, it is necessary to take a look at Amdahl's law [16]. This law states that the speedup of a program using multiple processors is bounded by the time needed for its sequential part; in addition to the number of processors, the algorithm also limits the speedup.

In order to enjoy the performance benefits that multiprocessors can provide, one should exploit efficiently the parallelism present in applications. This is a tricky task for programmers, especially if this programmer is a physicist or a mathematician or is a computer scientist for whom understanding the application is difficult since it is not his. Of course, we could say to the programmer: "think parallel"! But humans tend to think sequentially. Therefore, one past problem is and will be for some time to detect parallelism in a sequential code and, automatically or not, write its equivalent efficient parallel code.

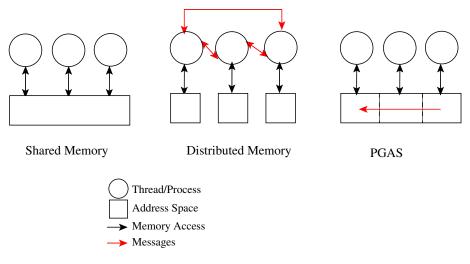

A parallel application, expressed in a parallel programming model, should be as portable as possible, i.e. one should not have to rewrite parallel code when targeting an other machine. Yet, the proliferation of parallel programming models makes the choice of one general model not obvious, unless there is a parallel language that is efficient and able to be compiled to all types of current and future architectures, which is not yet the case. Therefore, this writing of a parallel code needs to be based on a generic approach, i.e. how well a range of different languages can be handled, in order to offer some chance of portability.

### 1.2 Motivation

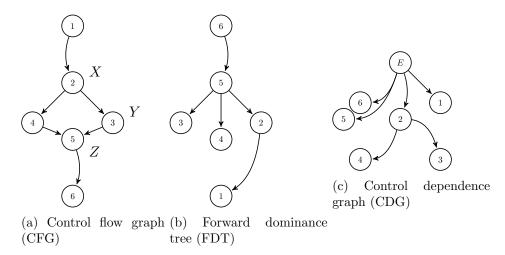

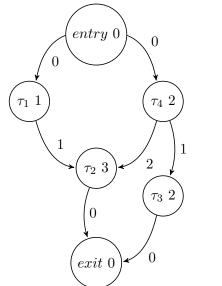

In order to achieve good performance when programming for multiprocessors and go beyond having to "think parallel", a platform for automatic parallelization is required to exploit cores efficiently. Also, the proliferation of multi-core processors with shorter pipelines and lower clock rates and the pressure that the simpler data parallelism model imposes on their memory bandwidth have made coarse grained parallelism inevitable for improving performance.

The first step in a parallelization process is to expose concurrency by decomposing applications into pipelined tasks, since an algorithm is often described as a collection of tasks. To illustrate the importance of task parallelism, we give a simple example: the Harris algorithm [96] which is based on pixelwise autocorrelation, using a chain of functions, namely Sobel, Multiplication, Gauss, and Coarsity. Figure 1.1 shows this process. Several works already parallelized and mapped this algorithm on parallel architectures such as the CELL processor [95].

Figure 1.2 shows a possible instance of a manual partitioning of Harris (see also [95]). The Harris algorithm can be decomposed into a succession of two to three concurrent tasks (ellipses in the figure), assuming no exploitation of data parallelism. Automating this intuitive approach and thus the automatic task extraction and parallelization of such applications is our motivation in this thesis.

However, detecting task parallelism and generating efficient code rest on complex analyses of data dependences, communication, synchronization, etc. These different analyses can be provided by compilation frameworks. Thus, delegating the issue of "parallel thinking" to software is appealing, because it can be built upon existing sophisticated analyses of data dependences, and can handle the granularity present in sequential codes and the resource constraints such as memory size or the number of CPUs that also impact this process.

Automatic task parallelization has been studied around for almost half a century. The problem of extracting an optimal parallelism with optimal communications is NP-complete [47]. Several works have tried to automate the parallelization of programs using different granularities. Metis [62] and other graph partitioning tools aim at assigning the same amount of processor work with small quantities of interprocessor communication, but the structure of the graph does not differentiate between loops, function calls, etc. The crucial steps of graph construction and parallel code generation are missing. Sarkar [98] implements a compile-time method for the partitioning problem for multiprocessors. A program is partitioned into parallel tasks at compile time and then these are merged until a partition with the smallest parallel execution time in the presence of overhead (scheduling and communication overhead) is found. Unfortunately, this algorithm does not

```

void main(int argc, char *argv[]){

float (*Gx)[N*M], (*Gy)[N*M], (*Ixx)[N*M],

(*Iyy)[N*M], (*Ixy)[N*M], (*Sxx)[N*M],

(*Sxy)[N*M], (*Syy)[N*M], (*in)[N*M];

in = InitHarris();

/* Now we run the Harris procedure */

//Sobel

SobelX(Gx, in);

SobelY(Gy, in);

//Multiply

MultiplY(Ixx, Gx, Gx);

MultiplY(Iyy, Gy, Gy);

MultiplY(Ixy, Gx, Gy);

//Gauss

Gauss(Sxx, Ixx);

Gauss(Syy, Iyy);

Gauss(Sxy, Ixy);

//Coarsity

CoarsitY(out, Sxx, Syy, Sxy);

return;

```

Figure 1.1: Sequential C implementation of the main function of Harris

Figure 1.2: Harris algorithm data flow graph

address resource constraints which are important factors for targeting real architectures.

All parallelization tools are dedicated to a particular programming model: there is a lack of a generic abstraction of parallelism (multithreading, synchronization and data distribution). They thus do not usually address the issue of portability.

In this thesis, we develop an automatic task parallelization methodology for compilers: the key characteristics we focus on are resource constraints and static scheduling. It includes the techniques required to decompose applications into tasks and generate equivalent parallel code, using a generic approach that targets different parallel languages and thus different architectures. We apply this methodology in the existing tool PIPS [59], a comprehensive source-to-source compilation platform.

#### 1.3 Contributions

Our goal is to develop a new tool and algorithms for automatic task parallelization that take into account resource constraints and which can also be of general use for existing parallel languages. For this purpose, the main contributions of this thesis are:

- 1. a new BDSC-based hierarchical scheduling algorithm (HBDSC) that uses:

- a new data structure, called the Sequence Data Dependence Graph (SDG), to represent partitioned parallel programs,

- "Bounded DSC" (BDSC), an extension of the DSC [111] scheduling algorithm that simultaneously handles two resource constraints, namely a bounded amount of memory per processor and a bounded number of processors, which are key parameters when scheduling tasks on actual multiprocessors,

- a new cost model based on execution time complexity estimation, convex polyhedral approximations of data array sizes and code instrumentation for the labeling of SDG vertices and edges;

- 2. a new approach for the adaptation of automatic parallelization platforms to parallel languages via:

- SPIRE, a new, simple, parallel intermediate representation (IR) extension methodology for designing the parallel IRs used in compilation frameworks,

- the deployment of SPIRE for automatic task-level parallelization of explicitly parallel programs on the PIPS [59] compilation framework;

- 3. an implementation in the PIPS source-to-source compilation framework of:

- BDSC-based parallelization for programs encoded using SPIREbased PIPS IR,

- SPIRE-based parallel code generation into two parallel languages: OpenMP [4] and MPI [3];

- 4. performance measurements for our parallelization approach, based on:

- five significant programs, targeting both shared and distributed memory architectures: the image and signal processing benchmarks, actually sample constituent algorithms hopefully representative of classes of applications, Harris [54] and ABF [52], the SPEC2001 benchmark equake [22], the NAS parallel benchmark IS [87] and an FFT code [8],

- their automatic translations into two parallel languages: OpenM-P [4] and MPI [3],

- and finally, a comparative study between our task parallelization implementation in PIPS and that of the audio signal processing language Faust [88], using two Faust applications: Karplus32 and Freeverb. We choose Faust since it is an open-source compiler and it also generates automatically parallel tasks in OpenMP.

### 1.4 Thesis Outline

This thesis is organized in nine chapters. Figure 1.3 shows how these chapters can be put into the context of a parallelization chain.

Chapter 2 provides a short background to the concepts of architectures, parallelism, languages and compilers used in the next chapters.

Chapter 3 surveys seven current and efficient parallel programming languages in order to determine and classify their parallel constructs. This helps us to define a core parallel language that plays the role of a generic parallel intermediate representation when parallelizing sequential programs.

Our proposal called the SPIRE methodology (Sequential to Parallel Intermediate Representation Extension) is developed in Chapter 4. SPIRE leverages existing infrastructures to address both control and data parallel languages while preserving as much as possible existing analyses for sequential codes. To validate this approach in practice, we use PIPS, a comprehensive source-to-source compilation platform, as a use case to upgrade its sequential intermediate representation to a parallel one.

Since the main goal of this thesis is automatic task parallelization, extracting task parallelism from sequential codes is a key issue in this process, which we view as a scheduling problem. Chapter 5 introduces a new efficient automatic scheduling heuristic called BDSC (Bounded Dominant Sequence Clustering) for parallel programs in the presence of resource constraints on the number of processors and their local memory size.

The parallelization process we introduce in this thesis uses BDSC to find a good scheduling of program tasks on target machines and SPIRE to generate parallel source code. Chapter 6 equips BDSC with a sophisticated cost model to yield a new parallelization algorithm.

Chapter 7 describes how we can generate equivalent parallel codes in two target languages, OpenMP and MPI, selected from the survey presented in

15

Chapter 3. Thanks to SPIRE, we show how code generation is simple and efficient.

To verify the efficiency and robustness of our work, experimental results are presented in Chapter 8. They suggest that BDSC- and SPIRE-based parallelization focused on efficient resource management leads to significant parallelization speedups on both shared and distributed memory systems. We also compare our implementation of the generation of omp task in PIPS with the generation of omp sections in Faust.

We conclude in Chapter 9.

Figure 1.3: Thesis outline: blue indicates thesis contributions; an ellipse, a process; and a rectangle, results

# Perspectives: Bridging Parallel Architectures and Software Parallelism

You talk when you cease to be at peace with your thoughts. Kahlil Gibran

"Anyone can build a fast CPU. The trick is to build a fast system." Attributed to Seymour Cray, this quote is even more pertinent when looking at multiprocessor systems that contain several fast processing units; parallel system architectures introduce subtle system features to achieve good performance. Real world applications, which operate on large amounts of data, must be able to deal with constraints such as memory requirements, code size and processor features. These constraints must also be addressed by parallelizing compilers that are related to such applications, from the domains of scientific, signal and image processing, and translate sequential codes into efficient parallel ones. The multiplication of hardware intricacies increases the importance of software in order to achieve adequate performance.

This thesis was carried out under this perspective. Our goal is to develop a prototype for automatic task parallelization that generates a parallel version of an input sequential code using an algorithm of scheduling. We also address code generation and parallel intermediate representation issues. More generally, we study how parallelism can be detected, represented and finally generated.

"Anyone can build a fast CPU. The trick is to build a fast system." Attribuée à Seymour Cray, cette citation¹ est d'autant plus pertinente quand on considère les systèmes multiprocesseurs qui contiennent plusieurs unités de traitement rapide; les architectures parallèles présentent des caractéristiques subtiles qu'il convient de bien gérer pour obtenir de bonnes performances. Les applications du monde réel, qui nécessitent de grandes quantités de données, doivent en plus être en mesure de faire face à des contraintes telles que les besoins en mémoire, la taille du code et les fonctionnalités du processeur. Ces contraintes doivent également être prises en compte par

<sup>&</sup>lt;sup>1</sup>Tout un chacun peut construire un CPU rapide. Le plus difficile est de construire un système rapide.

les compilateurs de parallélisation, qui, surtout dans les domaines des applications scientifiques et de traitement du signal et d'image, s'efforcent de traduire des codes séquentiels en des codes parallèles efficaces. L'accroissement de la complexité des matériels augmente l'importance du logiciel chargé de les gérer, et ce afin d'obtenir une performance adéquate.

Cette thèse a été réalisée dans la perspective que nous venons d'esquisser. Notre objectif est de développer un prototype logiciel de parallélisation automatique de tâches qui génère une version parallèle d'un code séquentiel d'entrée en utilisant un algorithme d'ordonnancement. Nous abordons également la génération de code parallèle, en particulier les problèmes de représentation intermédiaire parallèle. Plus généralement, nous étudions comment le parallélisme peut être détecté, représenté et finalement généré.

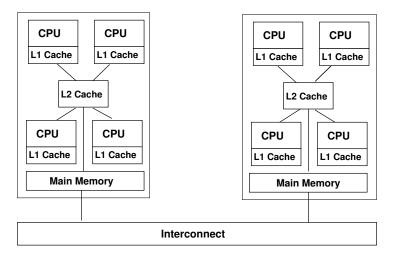

## 2.1 Parallel Architectures

Up to 2003, the performance of machines has been improved by increasing clock frequencies. Yet, relying on single-thread performance has been increasingly disappointing due to access latency to main memory. Moreover, other aspects of performance have been of importance lately, such as power consumption, energy dissipation, and number of cores. For these reasons, the development of parallel processors, with a large number of cores that run at slower frequencies to reduce energy consumption, is adopted and has had a significant impact on performance.