### Robust design of deep-submicron digital circuits

Gutemberg Goncalves dos Santos Junior Gonçalves dos Santos Junior

### ▶ To cite this version:

Gutemberg Goncalves dos Santos Junior Gonçalves dos Santos Junior. Robust design of deepsubmicron digital circuits. Other. Télécom ParisTech, 2012. English. NNT: 2012ENST0039 . pastel-00998731

### HAL Id: pastel-00998731 https://pastel.hal.science/pastel-00998731

Submitted on 2 Jun 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

EDITE - ED 130

### **Doctorat ParisTech**

### THÈSE

pour obtenir le grade de docteur délivré par

### **TELECOM ParisTech**

Spécialité « Communications et Electronique »

présentée et soutenue publiquement par

### **Gutemberg GONÇALVES DOS SANTOS JÚNIOR**

le 6 septembre 2012

# Conception Robuste de Circuits Numériques à Technologie Nanométrique

Directeurs de thèse : Mme. Lirida NAVINER

M. Jean-François NAVINER

#### Jury

M. Raoul Velazco, Directeur de recherche, CNRS-TIMA

M. Luis Entrena, Professeur, Université Carlos III Madrid

M. Habib Mehrez, Professeur, UPMC, LIP6

M. Gilles Deleuze, Chercheur senior, EDF R&D

Examinateur

Mme. Lirida Naviner, Professeur, Télécom Paristech

Directrice de Thèse

M. Jean-François Naviner, Maître de conférences, HDR, Télécom Paristech

### **TELECOM ParisTech**

École de l'Institut Télécom - membre de ParisTech

Directeur de Thèse

# Thèse

Robust Design of Deep-Submicron Digital Circuits

Gutemberg GONÇALVES DOS SANTOS JÚNIOR

Directeurs de thèse Pr. Dr. Lirida NAVINER

Dr. Jean-François NAVINER

"Education is the most powerful weapon which you can use to change the world."

Nelson Mandela

"Il n'y a aucune connaissance de la terre qui ne commence par l'imagination. Lorsqu'elle disparaît, lorsque se brise la création par l'imaginaire, la curiosité s'évanouit avec elle et le savoir s'épuise."

Francesco Alberoni

# Acknowledgement

Working on a Ph.D has been an extraordinary experience. It would not have been possible to succeed without the support of many people who gave of their time tirelessly and patiently in order to make the difficult moments less unbearable.

First and foremost I offer my sincerest gratitude to my supervisors, Dr Lirida Naviner and Dr Jean-François Naviner, without whose sincerity, knowledge, encouragement and assistance this study would not have been successful. I'm deeply thankful for the excellent atmosphere you created for doing research, where everybody could contribute and learn from each other. Besides, you acted not only as a supervisor, but more importantly as a real friend, and I appreciate that from my heart.

I would like to express my deepest gratitude to EDF R&D for the financial support and the opportunity to carry out my research studies. I would like to extend my greetings to Bastien Cousin, Laurent Cretinon, Gilles Deleuze, Anne-Lise Didierjean, Laurent Doireau, Sandrine Legruel, and Philippe Mathevon, whose advice, support and patience were fundamental during my studies.

I would like to thank Dr Luis Entrena and Dr Raoul Velazco for agreeing to be the reviewers of this dissertation. Your knowledge and remarks were vital for the improvement of the current work.

Many thanks to all my friends for sharing their enthusiasm for and comments on my work. I would like to thank Alban Gruget, Arthur Liraneto, Arwa Ben Dhia, Bruno Lyra, Chadi Jabbour, Cibele Trinca, Daniel Caon, Davi Bibiano, Dimitri Edouard, Eduardo Ferraz, Elaine Crespo, Eric Bouton, Fabrice Linot, Farhan Mirani, Florent Lozac'h, Hasham Khushk, Joana Silveira, Julie Gaudin, Maí Correia, Márcia Costa e Silva, Mariem Slimani, Pietro Maris, Sami Mekki, Samuel Pagliarini, Sereuja Zier, Shivam Bhasin, Tian Ban, Yang Liu, and all the other students in Télécom Paristech and friends I made in Paris for the great moments we spent together. Just remembering the happy hours in the "butte-aux-cailles", the picnics in the parks and on the banks of the Seine, the travels, the dinners in Maisel, and all the parties we went make me laugh and feel good. I'm truly grateful to all of you guys, you are fantastic people, and I hope to see you all again very soon.

I would like to thank as well Chantal Cadiat, Florence Besnard, Zouina Sahnoune and

all the employees of Télécom Paristech who welcomed me and made my stay so memorable. You helped me so much with my problems, bureaucracy and so many other things that I can't really imagine finishing this thesis without your help.

I'm especially thankful to my family for their unflagging love, and for always supporting me during difficult times, listening to my worries and complaints.

## Abstract

The design of circuits to operate at critical environments, such as those used in control-command systems at nuclear power plants, is becoming a great challenge with the technology scaling. These circuits have to pass through a number of tests and analysis procedures in order to be qualified to operate. In case of nuclear power plants, safety is considered as a very high priority constraint, and circuits designed to operate under such critical environment must be in accordance with several technical standards such as the IEC 62566, the IEC 60987, and the IEC 61513. In such standards, reliability is treated as a main consideration, and methods to analyze and improve the circuit reliability are highly required.

The present dissertation introduces some methods to analyze and to improve the reliability of circuits in order to facilitate their qualification according to the aforementioned technical standards. Concerning reliability analysis, we first present a fault-injection based tool used to assess the reliability of digital circuits. Next, we introduce a method to evaluate the reliability of circuits taking into account the ability of a given application to tolerate errors. Concerning reliability improvement techniques, first two different strategies to selectively harden a circuit are proposed. The first one is based on the assumption that some output bits of a circuit may be more important for a given application than the others. Then, the proposed technique drives the reliability improvement effort to those bits. The other technique uses a cost function in order to automatically select the best candidates to be hardened. Finally, a method to automatically partition a TMR design based on a given reliability requirement is introduced.

# French Summary

### Introduction

Depuis l'avènement de la micro-électronique, ce domaine n'a pas cessé de prendre de l'ampleur. Les technologies de fabrication ont vécu une évolution exponentielle comme prévu par la Loi de Moore [1,2]. Comme résultat, les dispositifs électroniques deviennent de plus en plus petits, plus performants et moins chers.

Afin de continuer l'évolution de la micro-électronique même après l'arrivée des dimensions submicroniques, les chercheurs doivent surpasser des défis comme la considération des phénomènes physiques qui auparavant étaient négligeables et maintenant sont prépondérants, comme les forces de Casimir et de Van Der Waals [3]. De plus, les systèmes d'interconnections sont devenus très complexes avec l'arrivée du schéma de connexion 3-D [4]. En fait, l'augmentation de la quantité de composants dans la même puce et l'augmentation de la complexité des interconnections font croître la probabilité de défaillance des composants. En même temps, l'augmentation des fréquences d'opération augmente la probabilité des erreurs de synchronisation [5]. En conséquence, une réduction du rendement de fabrication aussi bien que de la fiabilité des circuits intégrés est attendue [6–10].

Avec l'augmentation de la probabilité de fautes dans les circuits numériques, les systèmes développés pour les environnements critiques comme les centrales nucléaires, les avions et les applications spatiales doivent être certifiés selon des normes industrielles. Cette thèse est un résultat d'une coopération CIFRE entre l'entreprise Électricité de France (EDF) R&D et Télécom Paristech. EDF est l'un des plus gros producteurs d'énergie au monde et possède de nombreuses centrales nucléaires. Les systèmes de contrôle-commande utilisé dans les centrales sont basés sur des dispositifs électroniques, qui doivent être certifiés selon des normes industrielles comme la CEI 62566 [11], la CEI 60987 [12] et la CEI 61513 [13] à cause de la criticité de l'environnement nucléaire. En particulier, l'utilisation des dispositifs programmables comme les FPGAs peut être considérée comme un défi du fait que la fonctionnalité du dispositif est définie par le concepteur seulement après sa conception physique. Le travail présenté dans ce mémoire porte sur la conception de nouvelles méthodes d'analyse de la fiabilité aussi bien que des méthodes d'amélioration de la

fiabilité d'un circuit numérique.

### La fiabilité dans les circuits numériques

Un circuit électronique peut être vu comme l'assemblage d'un certain nombre de composants électroniques de telle façon qu'il produit une fonctionnalité souhaité. Cette fonctionnalité peut être garantie si on considère que les composants sont exempts de fautes. Malheureusement les dispositifs électroniques sont susceptibles de défaillances occasionnées par des mécanismes naturels comme les impuretés dans les matériaux et les variations de paramètres, entre autres. Pour être précis, il y a une certaine probabilité qu'un circuit numérique va fournir la fonctionnalité souhaitée pendant un période de temps. Cette probabilité est connue comme fiabilité et peut être définie comme suit : la fiabilité est l'aptitude d'un dispositif à accomplir une fonction requise dans des conditions données pour une période de temps donnée [14].

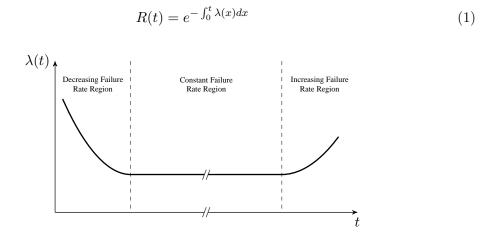

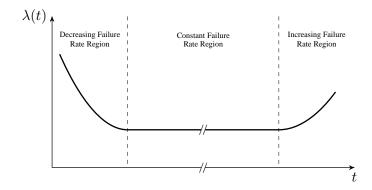

La fiabilité d'un circuit électronique peut être calculée selon (1). Son comportement par rapport au temps peut être divisé en 3 phases (voir FIGURE 1) :

- 1. Taux de défaillance décroissant  $\rightarrow$  Cette phase de vie est aussi appelée période de jeunesse.

- 2. Taux de défaillance sensiblement constant  $\to$  C'est aussi appelé période de vie utile du dispositif.

- 3. Taux de défaillance croissant  $\rightarrow$  Correspond à la période de vieillissement du circuit

Figure 1 – Courbe en baignoire

Parmi les types de fautes qui peuvent occasionner une défaillance du système électronique, les fautes transitoires sont particulièrement une menace à cause de leur comportement aléatoire et leur grande probabilité d'occurrence. Les fautes transitoires peuvent être occasionnées par différents phénomènes physiques comme par exemple les particules alpha, les rayons cosmiques et les interférences électromagnétiques. De plus, la susceptibilité des circuits électroniques à ces types de phénomènes augmente avec la réduction de la taille des composants. Pour faire face à ces erreurs, les concepteurs peuvent utiliser des méthodes de durcissement d'un circuit intégré. Cela représente toujours un surcoût en surface, en consommation ou en vitesse. Ainsi, les méthodes d'analyse de la fiabilité d'un circuit intégré deviennent de plus en plus importantes avec l'évolution de la technologie. C'est grâce à ce type d'analyse que les concepteurs peuvent identifier les zones de défaillance potentielles, la nécessité d'ajout de redondance, la nécessité d'un système de sauvegarde, etc. De plus, les méthodes d'analyse de la fiabilité peuvent être utilisées comme un outil pour mesurer la performance de différentes stratégies de durcissement d'un circuit intégré.

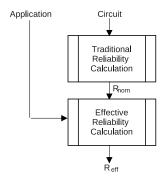

Plusieurs méthodes d'analyse de la fiabilité d'un circuit ont été reportées dans la littérature. C'est bien connu qu'une analyse optimale doit prendre en considération autant d'information que possible du circuit lui-même aussi bien que de l'application cible. En dépit de cela, la plupart de méthodes d'analyse de fiabilité considère quelques simplifications dans les modèles mathématiques comme la considération de fautes simples, de signaux non corrélés, etc. En outre, peu de travaux sur l'analyse de la fiabilité ont été effectués tenant en compte l'importance des résultats du circuit pour l'application cible. En fait, beaucoup d'applications présentent la capacité de tolérer un certain nombre et certains types d'erreurs. En considérant cette information, un concepteur peut mieux contrôler l'ajout de redondance afin d'éviter un surcoût trop élevé. La première contribution de ce travail est une technique nommée « effective reliability » qui prend en considération la tolérance aux erreurs d'une application pour évaluer la fiabilité du circuit.

### Effective Reliability

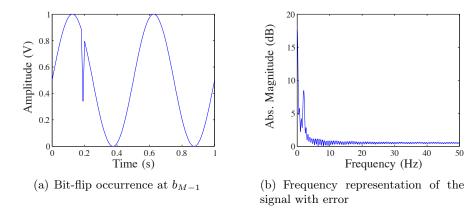

L'augmentation considérable du nombre d'erreurs attendue dans les circuits avec l'évolution de la technologie a inspiré les discussions sur la tolérance aux erreurs depuis la sortie du « 2001 International Technology Roadmap for Semiconductors (ITRS) ». Le concept de tolérance aux erreurs a été introduit comme un paradigme orienté à l'application pour faire face aux variations du processus, aux défauts et au bruit [7]. L'idée principale est de que certaines applications présentent la capacité de tolérer un certain nombre et certains types d'erreurs à condition qu'ils soient limités à un certain niveau de sévérité défini par l'application. En effet, plusieurs applications multimédia présentent cette caractéristique grâce au fonctionnement des sens humains comme la vue, l'audition et l'odorat, qui ne peuvent pas s'apercevoir de la présence de certains types d'erreurs. Ce mémoire se réfère à ce type de phénomène comme les masquages des erreurs par l'application et introduit la

classification d'erreurs suivante :

- Erreurs critiques → Ce sont les erreurs qui peuvent occasionner un grand impact dans les résultats produits par un circuit;

- Erreurs non-critiques → Ce sont les erreurs qui sont masquées par l'application.

Cette classification des erreurs prend en considération l'usage des résultats produits par un circuit. Par conséquence, un facteur très important qui affecte ce type de classification est l'approche de codification utilisée pour représenter l'information dans la sortie du circuit. En fait, l'impact d'une inversion d'un bit de sortie du circuit dépend directement de son poids, c'est-à-dire de sa signifiance relative par rapport au mot de sortie. En dépit de cela, le concept traditionnel de fiabilité d'un circuit (appelé fiabilité nominale dans ce mémoire) est basée sur le paradigme de passer ou échouer, c'est-à-dire il ne prend pas en considération l'importance d'un bit de sortie comme décrit en (2).

$$R_{nom} = \prod_{i=0}^{M-1} q_i \tag{2}$$

Pour faire face à ces problèmes, nous proposons le concept de « effective reliability » comme décrit par (3) et (4). Dans ce cas, le terme  $R_{ack}$  représente la probabilité qu'une erreur soit masquée par l'application cible. Cela veut dire que le terme  $R_{ack}$  prend en considération les erreurs qui sont classées comme non-critiques alors que le terme  $R_{\overline{ack}}$  considère les erreurs critiques. La classification d'une erreur en critique ou non-critique prend en compte des métriques de qualité qui sont considérées pertinentes par rapport à l'application cible. Ce mémoire introduit aussi deux métriques de qualité différentes basées d'importance d'un bit (voir (5) et (6)) et d'erreur relative (voir (7) et (8)).

$$R_{eff} = R_{nom} + R_{ack} \tag{3}$$

$$R_{eff} = 1 - R_{\overline{ack}} \tag{4}$$

$$R_{eff} = \prod_{i=0}^{M-1} q_i + \sum_{k=1}^{T+1} \sum_{r=1}^{C_k^{T+1}} \gamma_{k,r}$$

(5)

$$R_{eff} = 1 - \sum_{k=1}^{T+1} \sum_{r=C_k^{T+1}+1}^{C_k^M} \gamma_{k,r} - \sum_{k=T+2}^{M} \sum_{r=1}^{C_k^M} \gamma_{k,r}$$

(6)

| Sortie | Fiabilité $(q_i)$ |

|--------|-------------------|

| $b_0$  | 99.80%            |

| $b_1$  | 99.48%            |

| $b_2$  | 99.31%            |

| $b_3$  | 99.24%            |

| $b_4$  | 99.20%            |

| $b_5$  | 99.18%            |

| $b_6$  | 99.17%            |

$b_7$   $b_8$  (retenue)

Table 1 – Valeurs de la fiabilité de chaque bit de sortie de l'APPR8

$$R_{eff} = \prod_{i=0}^{M-1} q_i + \sum_{a=0}^{2^{H}-1} p(a) \sum_{k=1}^{k_{max}} \sum_{r=1}^{C_k^M} \gamma_{k,r} \cdot u \left(\delta_{max} - \delta(k, r, a)\right)$$

(7)

99.16%

99.36%

$$R_{eff} = 1 - \sum_{a=0}^{2^{H}-1} p(a) \sum_{k=1}^{k_{max}} \sum_{r=1}^{C_{k}^{M}} \gamma_{k,r} \cdot u \left(\delta(k, r, a) - \delta_{max}\right)$$

(8)

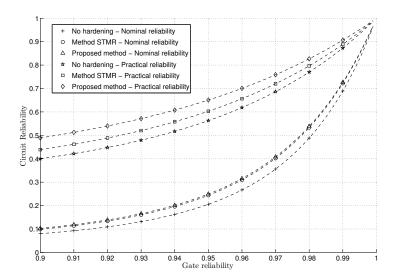

### Résultats

Prenons comme exemple un additionneur parallèle à propagation retenue de 8 bit (APPR8), construit à partir de 8 additionneurs de 1 bit en chaîne, dans lequel la probabilité de défaillance de chaque porte logique est égale à 99.9%. Supposons que la contrainte de fiabilité minimale de l'APPR8 soit  $R_{min} = 95\%$  et que l'application cible présente la capacité de tolérer des erreurs aussi grandes que 2% du résultat correct ( $\delta_{max} = 2\%$ ).

La fiabilité de chaque bit de sortie du APPR8 a été évaluée en utilisant la méthode SPR-MP [15], et les résultats sont illustrés dans le Tableau 1. La concept de fiabilité nominale peut donc être calculée selon (9). En analysant le résultat pour la fiabilité nominale un concepteur ira conclure que l'APPR8 ne respecte pas la contrainte de fiabilité minimale et que le circuit a besoin d'être durci. En considérant la méthode TMR (*Triple Modular Redundancy*) pour réaliser cette procédure, l'architecture durcie avec moins de surface mais qui encore respecte la contrainte de fiabilité minimale cause un surcoût en surface de 75%.

$$R = \prod_{i=0}^{8} q_i = 94.06\% \tag{9}$$

Rappelons que l'application cible présente la capacité de tolérer des erreurs s'ils ne dépassent pas la contrainte d'erreur relative  $\delta_{max} = 2\%$ . Prenons donc le concept de « effective reliability » pour analyser la fiabilité du circuit. Dans ce cas, la fiabilité du circuit

Table 2 – Valeurs de R<sub>eff</sub> pour différentes tolérances aux erreurs (APPR8)

| Erreur Relative $(\delta_{max})$ | Fiabilité |

|----------------------------------|-----------|

| 0.5%                             | 94.23%    |

| 1.0%                             | 94.64%    |

| 1.5%                             | 94.96%    |

| 2.0%                             | 95.22%    |

| 2.5%                             | 95.44%    |

| 3.0%                             | 95.62%    |

| 3.5%                             | 95.77%    |

| 4.0%                             | 95.92%    |

| 4.5%                             | 96.05%    |

| 5.0%                             | 96.16%    |

dépend de la capacité de l'application cible de tolérer des erreurs (voir Tableau 2). C'est bien noté qu'en considérant une capacité de tolérance d'erreurs  $\delta_{max} = 2\%$  la fiabilité du circuit pour cette application est égale à 95.22%, c'est-à-dire la contrainte de fiabilité minimale est déjà respectée et en fait il n'y a pas besoin d'ajout de redondance.

Le concept de « effective reliability » est très intéressant pour les applications dans lesquelles un certain nombre d'erreurs peut être toléré. Par contre, dans les applications appelées critiques comme les centrales nucléaires, les avions et les satellites, l'occurrence d'une seule erreur peut causer des conséquences sévères. En fait, les circuits développés pour ces environnements ont besoin d'une couverture de test qui s'approche de 100%. Pour faire face à ces problèmes, la deuxième contribution de ce travail est un outil basée sur Verilog appelé FIFA (Fault-Injection-Fault-Analysis) développé pour accélérer les tests exhaustifs dans les circuits intégrés.

### L'outil FIFA

C'est déjà bien connu que l'injection de fautes est une approche intéressant pour analyser le fonctionnement des circuits intégrés en présence de fautes. L'idée principale est d'injecter des fautes dans le circuit de forme aléatoire ou contrôlée et analyser si la faute est propagée jusqu'à la sortie. Comme les circuits intégrés deviennent de plus en plus complexes avec l'évolution de la technologie, le temps nécessaire pour atteindre un niveau élevé de couverture de test est très important, voire prohibitif. Cela devient un problème pour les applications qui ont besoin de tel niveau de couverture, et de ce fait le développement des nouvelles méthodes que puissent accélérer la procédure d'injection de fautes devient nécessaire. La deuxième contribution de ce travail est un outil appelé FIFA (Fault-Injection-Faut-Analysis) qui a été développé comme un « hardware IP » pour accélérer l'analyse de fiabilité basée sur l'injection de fautes. Cet outil est adapté à différents modèles de fautes

et à des fautes multiples.

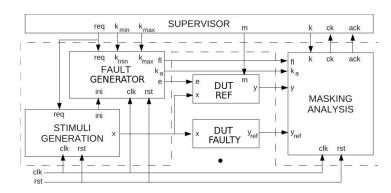

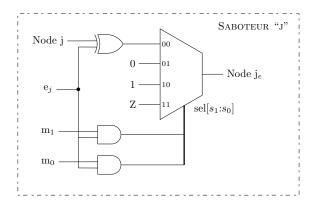

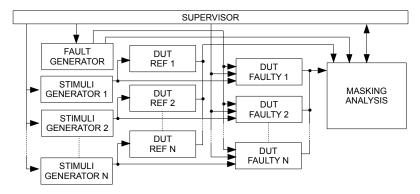

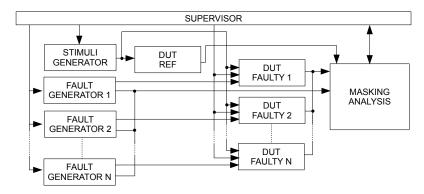

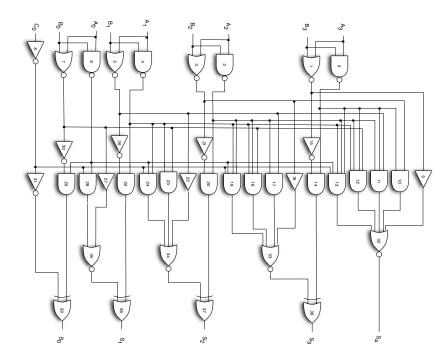

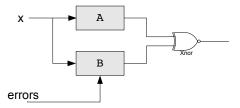

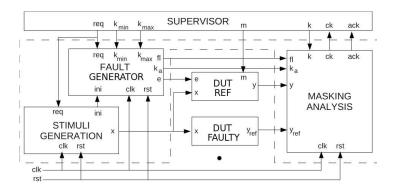

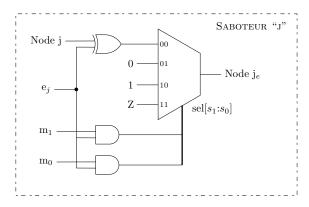

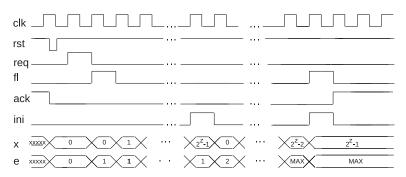

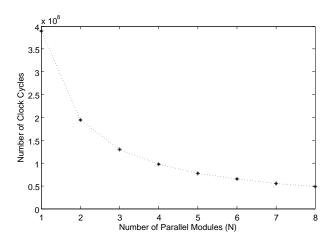

L'architecture de mise en œuvre de l'outil FIFA est illustrée dans la FIGURE 2. Nous pouvons noter qu'il y a deux versions du dispositif sous test (DUT). Le module «DUT REF» correspond à une version idéale du dispositif sous test, tandis que le module appelé «DUT FAULTY» est une copie du «DUT REF» dans laquelle des saboteurs ont été ajoutés . Un saboteur est un dispositif électronique capable de changer la valeur logique d'un nœud du circuit. Le saboteur qui a été développé pour l'outil FIFA supporte quatre types de fautes différentes : les inversions de bit, les collages à zéro, les collages à un, et les hautes impédances. Son schéma est illustré dans la FIGURE 3.

Figure 2 – Schéma général de l'outil proposé

FIGURE 3 – Schéma général d'un saboteur

L'évaluation de la fiabilité d'un circuit à partir des résultats fournis par l'outil FIFA est basée sur la méthode PBR [16]. Le module «FAULT GENERATOR» a été développé pour générer des erreurs en ordre croissante de multiplicité, de sorte que le concepteur peut limiter le nombre de tests à effectuer s'il connaît le nombre maximal de fautes simultanées.

Afin d'analyser la performance et la quantité de ressources utilisées par l'outil FIFA, nous l'avons comparé avec une plateforme reportée dans la littérature nommée FuSE [17].

Table 3 – Plate-forme Fuse vs. outil FIFA

|                    | Fuse [17]           | FIFA                  |

|--------------------|---------------------|-----------------------|

| ALUTs              | 2157                | 817                   |

| Registres          | 694                 | 467                   |

| Fréquence maximale | $75.1 \mathrm{MHz}$ | $109.87 \mathrm{MHz}$ |

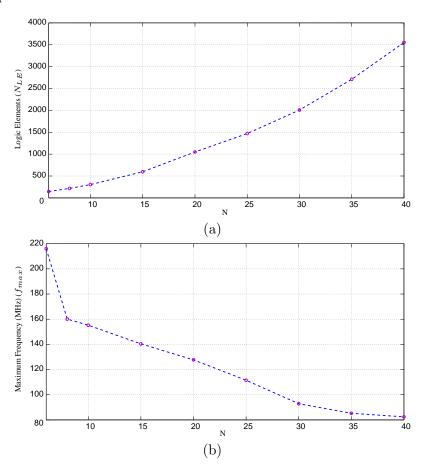

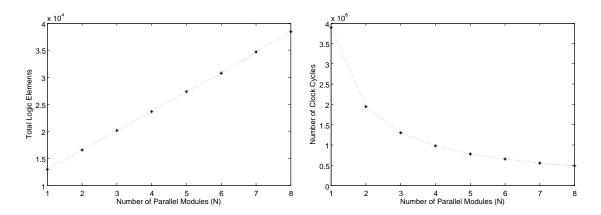

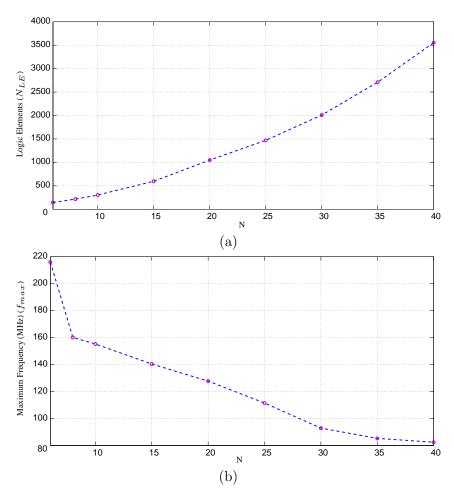

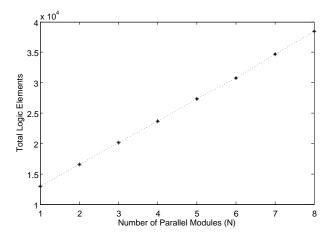

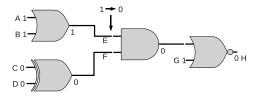

L'implémentation a été faite dans un STRATIX II EP2s180F1508C3 et il a été considéré un circuit avec N=10 saboteurs et P=Z=32 entrées et sorties. Les résultats de comparaison peuvent être analysés dans le Tableau 3. Les résultats de synthèse de l'outil FIFA sont présentés dans la FIGURE 4.

FIGURE 4 – Résultats de la synthèse de l'outil (jusqu'à N erreurs simultanées) : (a) nombre d'éléments logiques nécessaires dans le FPGA (b) fréquence maximale d'injection de fautes

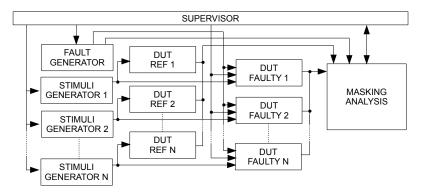

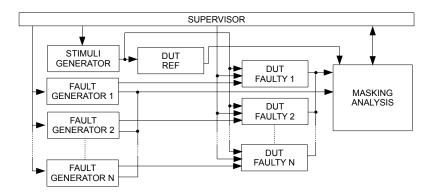

Magré la bonne performance de l'outil FIFA, l'analyse de la fiabilité de circuits complexes reste très coûteuse en temps. Pour surmonter ce problème, nous proposons d'utiliser la technique de parallélisme. La FIGURE 5 illustre une architecture parallèle très simple pour l'outil FIFA. Le problème avec cette approche est la grande surface additionnelle qui

Figure 5 – Une simple architecture parallèle pour la FIFA

FIGURE 6 – L'architecture en parallèle proposée pour la FIFA

devient nécessaire à cause de la réplication des modules «STIMULI GENERATOR», «DUT FAULTY» et «DUT REF». En fait, les modules «DUT REF» et «DUT FAULTY» répliqués requièrent une surface qui peut être significative par rapport à celles des autres modules. Une architecture qui évite la réplication de «DUT REF» est illustrée dans la FIGURE 6. Dans ce cas il est nécessaire de répliquer seulement les modules «DUT FAULTY» et «FAULT GENERATOR».

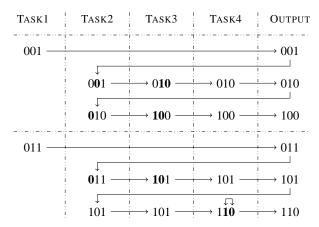

Afin d'implémenter correctement l'architecture illustrée dans la Figure 6, il faut bien distribuer la génération de vecteurs de fautes entre les N modules «FAULT GENERATOR». C'est important de remarquer que la génération de fautes est faite en ordre croissante concernant le nombre de fautes simultanées. En conséquence, il faut développer un algorithme pour calculer les vecteurs de fautes qui iront initialiser chaque module «FAULT GENERATOR». Cet algorithme a été developpé en utilisant quelques régularités numériques comme décrit dans le Chapitre 2. Les résultats, présentés dans la Figure 7, prouvent la bonne distribution de la génération de vecteurs de fautes.

Jusqu'à ce point il a été introduit deux méthodes pour analyser la fiabilité d'un circuit numérique. Cette analyse est généralement utilisée pour certifier le fonctionnement correct du circuit pendant sa période de vie utile. Si sa fiabilité ne respecte pas la contrainte de fiabilité minimale, les concepteurs peuvent réaliser le durcissement du circuit. Générale-

FIGURE 7 – Performance de l'architecture en parallèle proposée pour la FIFA

ment, la protection partiale d'un circuit contre défaillances est suffisante pour la plupart des applications. Ainsi, le développement des nouvelles méthodes basée sur une procédure de durcissement sélectif devient nécessaire. La troisième contribution de ce travail concerne le développement de deux techniques pour identifier les portes logiques les plus critiques et ainsi permettre de réaliser le durcissement sélectif d'un circuit.

#### Durcissement Sélectif

Les techniques de durcissement sélectif d'un circuit offrent un bon compromis entre l'augmentation de sa fiabilité et le surcoût correspondant. Ces techniques consistent fondamentalement de deux étapes : les portes ou blocs logiques sont analysés et ordonnés selon leur susceptibilité aux fautes et la probabilité que ces fautes produisent une défaillance du système ; ensuite, les portes ou blocs logiques les plus critiques sont protégés en utilisant une technique de durcissement choisie par le concepteur. La difficulté de mise en œuvre du durcissement sélectif réside dans l'identification des portes ou blocs logiques les plus critiques pour une application. La première technique proposée dans ce travail considère l'utilisation des résultats produits par un circuit comme le facteur déterminant de la criticité d'un bloc logique.

### Évitement des erreurs critiques dans les circuits intégrés

Un problème présent dans la plupart des méthodes de durcissement sélectif est négliger le profil d'utilisation des résultats d'un circuit par l'application cible. En fait, le concept de fiabilité nominale ne prend pas en compte la quantité d'information que chaque bit de sortie contient pour évaluer la fiabilité d'un circuit. Ce fait peut être illustré en considérant 3 architectures d'un circuit additionneur de 4 bits. La fiabilité de chaque bit de sortie  $(\mathbf{y} = b_3b_2b_1b_0)$  de ces 3 architectures est donnée dans le Tableau 4. La fiabilité nominale

| Table $4-1$ | Fiabilité pour | les bits de | e sortie de 3 | architectures | différentes o | d'un additionneur |

|-------------|----------------|-------------|---------------|---------------|---------------|-------------------|

| de 4-bit    |                |             |               |               |               |                   |

| Architecture | $b_3$ | $b_2$ | $b_1$ | $b_0$ | $R_{nominal}$ | $R_{practical}$ |

|--------------|-------|-------|-------|-------|---------------|-----------------|

| 1            | 99%   | 99%   | 99%   | 95%   | 92.18%        | 97.63%          |

| 2            | 95%   | 99%   | 99%   | 99%   | 92.18%        | 94.17%          |

| 3            | 98%   | 99%   | 99%   | 95%   | 91.25%        | 96.64%          |

peut être calculée selon (10), et les résultats correspondants sont aussi disponibles dans le Tableau 4. Concernant les valeurs pour la fiabilité nominale de ces architectures, un concepteur conclura que les architectures 1 et 2 sont également fiables. Cependant, en analysant la fiabilité de chaque bit de sortie pour ces architectures, il est évident que l'architecture 1 fournit des résultats plus en conformité avec l'application que l'architecture 2.

$$R_{nominal} = \prod_{i=0}^{M-1} R_i \tag{10}$$

Pour faire face à ce problème, ce travail propose le concept de fiabilité pratique. Basée sur le fait que chaque bit de sortie d'un circuit peut avoir une importance différente pour une certaine application, la fiabilité pratique utilise un facteur  $k_i$  pour déterminer la sévérité d'une erreur dans un bit de sortie spécifique (voir (11)). Par exemple, dans le cas d'utilisation d'une codification binaire, la valeur de  $k_i$  est calculée selon (12). Ce concept corrige le problème décrit par l'exemple du additionneur 4 bits comme illustré dans le Tableau 4

$$R_{practical} = \prod_{i=0}^{M-1} R_i^{k_i} \tag{11}$$

$$k_i = \frac{1}{2^{(M-1)-i}} \tag{12}$$

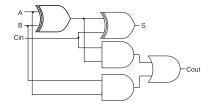

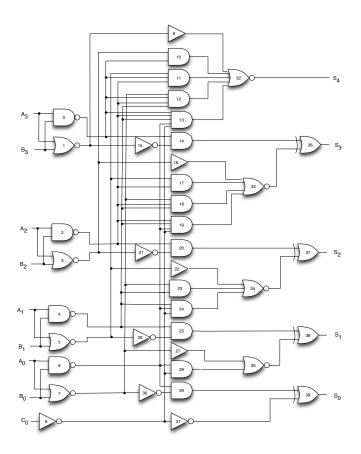

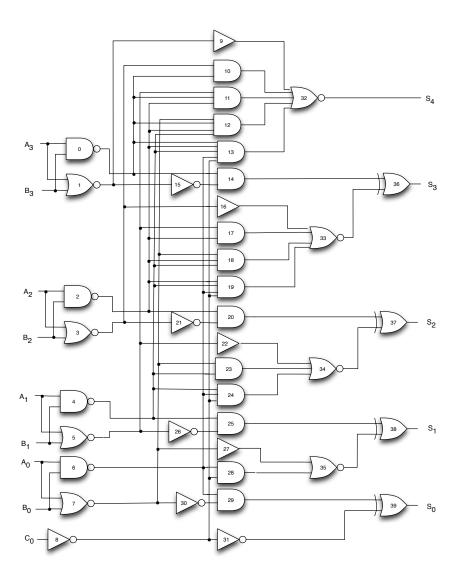

L'utilisation de la fiabilité pratique dans le processus de durcissement sélectif d'un circuit est illustrée avec l'additionneur de 4-bit de la FIGURE 8. Dans ce cas, la première étape consiste à identifier les portes logiques les plus critiques selon le modèle de fiabilité pratique. Les résultats sont présentés dans le Tableau 5. La méthode [18] a été aussi implémentée et les résultats ont été comparés avec la méthode proposée en considérant la même contrainte de surface (voir Tableau 6).

Les résultats présents dans le Tableau 6 prouvent l'efficacité de la méthode proposée. En fait, il peut être noté que le gain en fiabilité est plus marqué pour les bits les plus significatifs du circuit (les plus critiques). En conséquence, le circuit durcit par la méthode proposée exhibe la plus grande fiabilité pratique.

Figure 8 – Schéma en portes logiques du circuit 74283

#### L'utilisation d'une fonction de coût pour déterminer les portes critiques

La méthode décrite dans les paragraphes précédents ne s'applique pas à toutes les applications. En fait, plusieurs applications ne présentent pas une différence d'importance entre les bits de sortie du circuit. Pour ces applications, ce travail propose aussi une méthode basée sur des fonctions de coût pour automatiser le processus d'identification des portes logiques critiques. Cette méthode utilise le modèle SPR pour évaluer la fiabilité d'un circuit et déterminer les blocs logiques offrant la meilleure relation entre gain en fiabilité et coût.

Prenons un circuit composé de K portes logiques  $[g_i \cdots g_k]$  pour lesquelles les fiabilités sont représentées par  $[q_i \cdots q_k]$  et la fiabilité total du circuit par R. Donc, en considérant un gain en fiabilité dans la porte logique  $g_i$ , la fiabilité total du circuit devient  $R_i^*$ . Dans ce cas, deux portes logiques  $g_i$  et  $g_j$  peuvent contribuer différemment pour la fiabilité totale du circuit  $(R_i^* \text{ et } R_j^*)$ . Il faut définir donc un paramètre pour qu'une fonction de coût puisse être utilisée. Dans ce travail, nous proposons un paramètre appelé « hardware affinity »  $(Cha_i)$  qui peut être lié à n'importe quelle contrainte du circuit. Par exemple, le Tableau 7 utilise la surface des portes logiques obtenue par une synthèse basée sur la bibliothèque de Synopsis [19]. Il faut noter que le durcissement des portes logiques avec une valeur de  $Cha_i$  plus grande sera prioritaire. Une fonction de coût  $C_i$  peut donc être exprimée comme

Table 5 – Classification pour les portes logiques du circuit 74283

| $g_i$ | $S_0$ | $S_{0_w}$ | $S_1$ | $S_{1_w}$ | $S_2$ | $S_{2_w}$ | $S_3$ | $S_{3_w}$ | $S_4$ | $S_{4_w}$ | $\sum e_w$ | CritFac |

|-------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|-------|-----------|------------|---------|

| 0     | 0     | 0         | 0     | 0         | 0     | 0         | 384   | 3072      | 192   | 3072      | 6144       | 36      |

| 1     | 0     | 0         | 0     | 0         | 0     | 0         | 384   | 3072      | 320   | 5120      | 8192       | 38      |

| 2     | 0     | 0         | 0     | 0         | 384   | 1536      | 192   | 1536      | 96    | 1536      | 4608       | 33      |

| 3     | 0     | 0         | 0     | 0         | 384   | 1536      | 320   | 2560      | 160   | 2560      | 6656       | 37      |

| 4     | 0     | 0         | 384   | 768       | 192   | 768       | 96    | 768       | 48    | 768       | 3072       | 25      |

| 5     | 0     | 0         | 384   | 768       | 320   | 1280      | 160   | 1280      | 80    | 1280      | 4608       | 32      |

| 6     | 384   | 384       | 192   | 384       | 96    | 384       | 48    | 384       | 24    | 384       | 1920       | 14      |

| 7     | 384   | 384       | 320   | 640       | 160   | 640       | 80    | 640       | 40    | 640       | 2944       | 23      |

| 8     | 512   | 512       | 256   | 512       | 128   | 512       | 64    | 512       | 32    | 512       | 2560       | 22      |

| 9     | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 320   | 5120      | 5120       | 35      |

| 10    | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 288   | 4608      | 4608       | 34      |

| 11    | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 272   | 4352      | 4352       | 31      |

| 12    | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 264   | 4224      | 4224       | 29      |

| 13    | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 272   | 4352      | 4352       | 31      |

| 14    | 0     | 0         | 0     | 0         | 0     | 0         | 512   | 4096      | 0     | 0         | 4096       | 27      |

| 15    | 0     | 0         | 0     | 0         | 0     | 0         | 384   | 3072      | 0     | 0         | 3072       | 24      |

| 16    | 0     | 0         | 0     | 0         | 0     | 0         | 320   | 2560      | 0     | 0         | 2560       | 21      |

| 17    | 0     | 0         | 0     | 0         | 0     | 0         | 288   | 2304      | 0     | 0         | 2304       | 20      |

| 18    | 0     | 0         | 0     | 0         | 0     | 0         | 272   | 2176      | 0     | 0         | 2176       | 18      |

| 19    | 0     | 0         | 0     | 0         | 0     | 0         | 288   | 2304      | 0     | 0         | 2304       | 20      |

| 20    | 0     | 0         | 0     | 0         | 512   | 2048      | 0     | 0         | 0     | 0         | 2048       | 17      |

| 21    | 0     | 0         | 0     | 0         | 384   | 1536      | 0     | 0         | 0     | 0         | 1536       | 13      |

| 22    | 0     | 0         | 0     | 0         | 320   | 1280      | 0     | 0         | 0     | 0         | 1280       | 12      |

| 23    | 0     | 0         | 0     | 0         | 288   | 1152      | 0     | 0         | 0     | 0         | 1152       | 10      |

| 24    | 0     | 0         | 0     | 0         | 320   | 1280      | 0     | 0         | 0     | 0         | 1280       | 12      |

| 25    | 0     | 0         | 512   | 1024      | 0     | 0         | 0     | 0         | 0     | 0         | 1024       | 7       |

| 26    | 0     | 0         | 384   | 768       | 0     | 0         | 0     | 0         | 0     | 0         | 768        | 6       |

| 27    | 0     | 0         | 320   | 640       | 0     | 0         | 0     | 0         | 0     | 0         | 640        | 4       |

| 28    | 0     | 0         | 384   | 768       | 0     | 0         | 0     | 0         | 0     | 0         | 768        | 6       |

| 29    | 512   | 512       | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 512        | 2       |

| 30    | 384   | 384       | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 384        | 0       |

| 31    | 512   | 512       | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 512        | 1       |

| 32    | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 512   | 8192      | 8192       | 39      |

| 33    | 0     | 0         | 0     | 0         | 0     | 0         | 512   | 4096      | 0     | 0         | 4096       | 27      |

| 34    | 0     | 0         | 0     | 0         | 512   | 2048      | 0     | 0         | 0     | 0         | 2048       | 15      |

| 35    | 0     | 0         | 512   | 1024      | 0     | 0         | 0     | 0         | 0     | 0         | 1024       | 8       |

| 36    | 0     | 0         | 0     | 0         | 0     | 0         | 512   | 4096      | 0     | 0         | 4096       | 28      |

| 37    | 0     | 0         | 0     | 0         | 512   | 2048      | 0     | 0         | 0     | 0         | 2048       | 16      |

| 38    | 0     | 0         | 512   | 1024      | 0     | 0         | 0     | 0         | 0     | 0         | 1024       | 9       |

| 39    | 512   | 512       | 0     | 0         | 0     | 0         | 0     | 0         | 0     | 0         | 512        | 3       |

| Fiabilité        | Sans durcissement | Méthode en [18] | Méthode proposée |

|------------------|-------------------|-----------------|------------------|

| $S_0$            | 94.07%            | 94.97%          | 94.07%           |

| $\overline{S_1}$ | 92.39%            | 93.26%          | 92.39%           |

| $S_2$            | 91.80%            | 92.65%          | 92.43%           |

| $\overline{S_3}$ | 91.33%            | 92.17%          | 93.07%           |

| $\overline{S_4}$ | 94.60%            | 95.51%          | 97.15%           |

68.93%

87.29%

Table 6 – Analyse de fiabilité du circuit 74283

en (13).

$R_{nominal}$

$R_{practical}$

Table 7 – Paramètre  $Cha_i$  pour quelques cellules logiques

72.24%

88.89%

| Cellule | Surface $(\mu m^2)$ | $Cha_i$ |

|---------|---------------------|---------|

| INVX0   | 5.5296              | 1       |

| NAND2X0 | 5.5296              | 1       |

| NOR2X0  | 5.5296              | 1       |

| AND2X1  | 7.3728              | 0.75    |

| OR4X1   | 10.1376             | 0.55    |

| XOR3X1  | 22.1184             | 0.25    |

|         |                     |         |

$$Rg_i = R_i^* - R$$

$$C_i = Rg_i/Cha_i$$

(13)

72.63%

90.65%

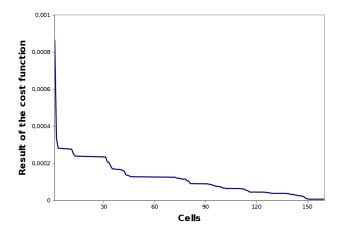

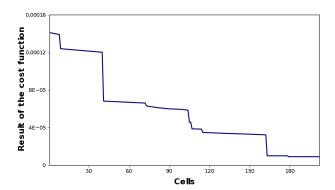

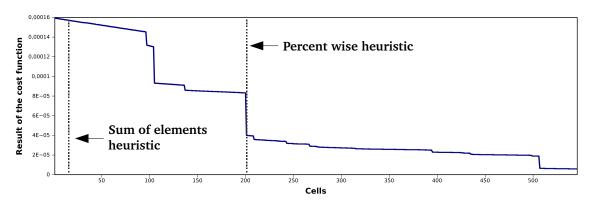

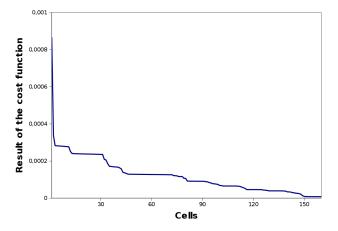

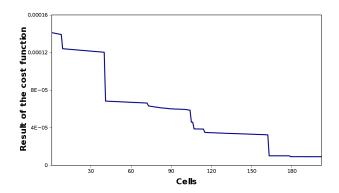

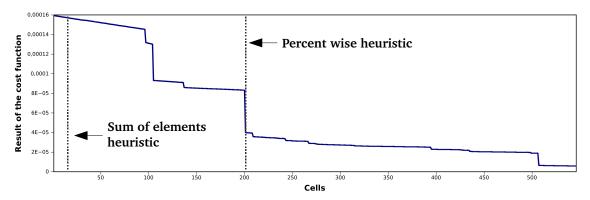

La méthode proposée évalue la fiabilité du circuit et identifie les portes logiques qui seront durcies jusqu'à ce qu'un niveau minimal de fiabilité 'T' soit atteint. En utilisant cette méthodologie pour les circuits du benchmark ISCAS [20], deux profils pour la fonction de coût ont été obtenus (voir FIGURE 9 et 10). Le premier présente une décroissance très marquée juste après le début de la courbe, et le deuxième présente la formation des plateaux jusqu'à la fin de l'évaluation.

A partir de ce constat, ce travail propose aussi deux heuristiques pour trouver un point d'arrêt pour la méthode. Le premier est appelé l'heuristique de la somme des éléments et est calculé selon (14). Dans ce cas,  $C_0$  représente la valeur de la fonction de coût du meilleur candidat pour le durcissement, et K est une contrainte empirique choisie par le concepteur. Le deuxième s'appelle l'heuristique basée sur le pourcentage et utilise un point

Figure 9 – Profil de la fonction de coût pour le circuit c432

FIGURE 10 – Profil de la fonction de coût pour le circuit c499

d'arrêt pour l'algorithme égal à X% du valeur de  $C_0$ . L'utilisation des deux heuristiques peut être analysée dans la FIGURE 11.

$$\sum_{i=2}^{j} C_i \leq K \times C_0 \tag{14}$$

Les deux heuristiques ont été utilisées pour réaliser le durcissement de plusieurs circuits du benchmark ISCAS. Les résultats de cette utilisation sont indiqués dans les Tableaux 8 et 9.

Le durcissement sélectif peut offrir un bon compromis entre le gain en fiabilité du système et l'ajout de redondance nécessaire. Cela est une caractéristique fondamentale pour la plupart des circuits. Cependant, il y a des applications qui requièrent un niveau de fiabilité très élevé. Pour ces applications un durcissement sélectif peut ne pas être suffisant et l'utilisation de méthodes offrant un niveau de protection plus haut est intéressante, même au pris d'un surcoût significatif de surface. La quatrième contribution de ce travail

Table 8 – Résultats pour l'heuristique de la somme des éléments, K=10

| Circuit | Nombre de portes | Surface original $(\mu m^2)$ | Portes<br>durcit | Surface durcit $(\mu m^2)$ | Surcoût<br>en surface |

|---------|------------------|------------------------------|------------------|----------------------------|-----------------------|

| c17     | 6                | 33.1776                      | 6                | 99.5328                    | 200%                  |

| 74283   | 40               | 306.5096                     | 20               | 547.9688                   | 78.7%                 |

| c432    | 160              | 1134.4672                    | 33               | 1541.4208                  | 35.8%                 |

| c499    | 202              | 2155.1680                    | 12               | 2414.1504                  | 12.0%                 |

| c1355   | 546              | 3194.7328                    | 11               | 3316.3840                  | 3.8%                  |

| c1908   | 880              | 5273.7488                    | 13               | 5417.5184                  | 2.7%                  |

| c2670   | 1269             | 8018.0632                    | 19               | 8233.7176                  | 2.6%                  |

| c3540   | 1669             | 10855.1824                   | 25               | 11177.7424                 | 2.9%                  |

| c5315   | 2307             | 15293.5992                   | 20               | 15518.4696                 | 1.4%                  |

Table 9 – Résultats pour l'heuristique basée sur la pourcentage, X=50%

| Circuit | Nombre de portes | Surface original $(\mu m^2)$ | Portes<br>durcit | Suface durcit $(\mu m^2)$ | Surcoût<br>en surface |

|---------|------------------|------------------------------|------------------|---------------------------|-----------------------|

| c17     | 6                | 33.1776                      | 5                | 88.4736                   | 166.6%                |

| 74283   | 40               | 306.5096                     | 9                | 406.0424                  | 32.5%                 |

| c432    | 160              | 1134.4672                    | 2                | 1187.5264                 | 4.6%                  |

| c499    | 202              | 2155.1680                    | 41               | 2854.6752                 | 32.4%                 |

| c1355   | 546              | 3194.7328                    | 201              | 5647.1232                 | 76.7%                 |

| c1908   | 880              | 5273.7488                    | 119              | 6611.912                  | 25.3%                 |

| c2670   | 1269             | 8018.0632                    | 10               | 8128.6552                 | 1.4%                  |

| c3540   | 1669             | 10855.1824                   | 8                | 10963.9312                | 1.2%                  |

| c5315   | 2307             | 15293.5992                   | 15               | 15459.4872                | 1.1%                  |

Figure 11 – L'utilisation des deux heuristiques dans le circuit c1355

est une méthode pour optimiser la procédure de partitionnement d'un circuit TMR de telle façon que un niveau de fiabilité très élevé soit assuré.

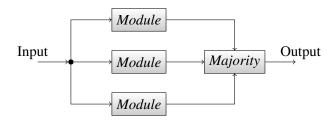

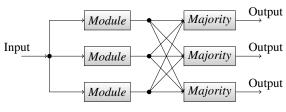

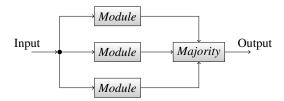

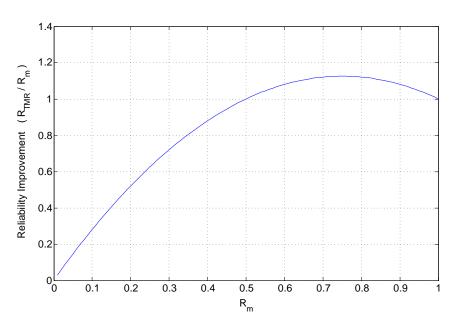

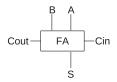

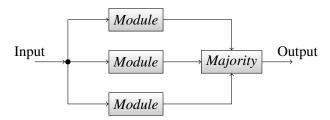

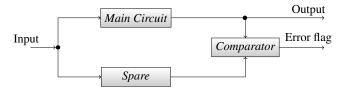

### Optimisation du placement des arbitres dans un circuit TMR

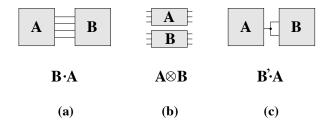

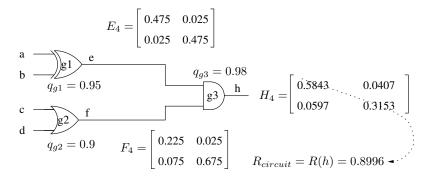

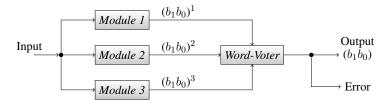

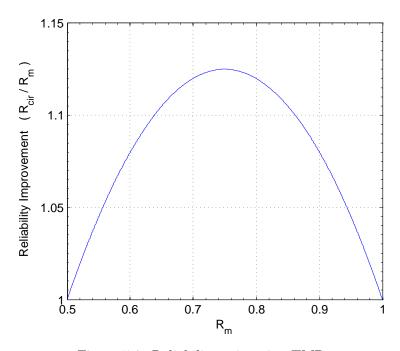

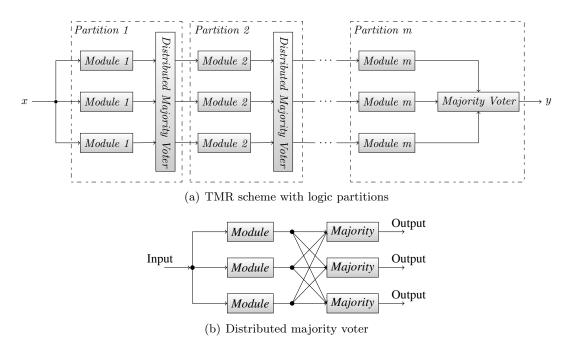

La méthode TMR est souvent utilisée pour réaliser le durcissement d'un circuit intégré. L'idée générale est très simple : trois répliques du circuit fournissent les résultats pour un arbitre qui juge quel est la sortie exacte en utilisant normalement le critère de majorité (voir FIGURE 12). Dans ce cas, même avec la présence d'une erreur dans la sortie d'un module, l'arbitre peut fournir la sortie exacte. Donc, la fiabilité totale du circuit initial  $(R_m)$  devient  $R_{cir}$  comme illustré dans (15).

FIGURE 12 – Schéma en blocs de la méthode TMR

$$R_{cir} = R_m^3 + 3R_m^2(1 - R_m)$$

$$R_{cir} = 3R_m^2 - 2R_m^3$$

(15)

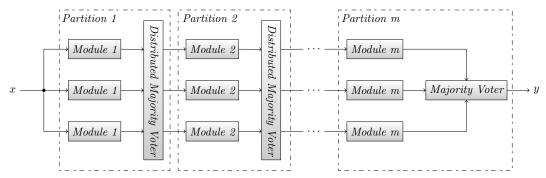

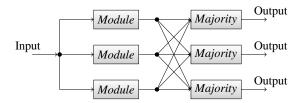

En dépit de sa simplicité, la méthode TMR offre un bon niveau de protection contre défaillances. Si une application requiert un niveau de fiabilité plus élevé que celui fourni par le TMR, il est possible de réaliser un partitionnement du circuit de telle façon qu'il soit composé par 'm' modules et sa fiabilité soit donnée par (16). En considérant que

chaque module est protégé par TMR (voir FIGURE 13), la fiabilité total du circuit peut être déterminée selon (17).

(a) Schéma TMR utilisant des partitions

(b) Distributed majority voter

Figure 13 – Circuit protégé par des partitions TMR

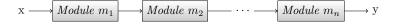

$$R_{C_1} = \prod_{k=1}^{n} (R_{m_k}) \tag{16}$$

$$R_{C_{1_{TMR}}} = \prod_{k=1}^{n} (3R_{m_k}^2 - 2R_{m_k}^3)$$

(17)

L'approche de partitionnement d'un circuit TMR peut offrir un niveau très élevé de fiabilité qui dépend de deux facteurs principaux : la quantité 'n' des modules et le placement des arbitres pour ces modules. Donc, une question qui devient intéressante est comment déterminer ces deux facteurs d'une façon optimale pour qu'un niveau de fiabilité minimale  $R_{min}$  soit atteint.

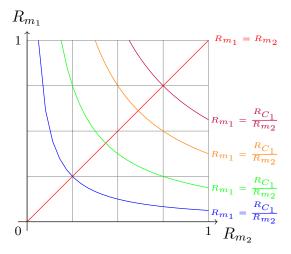

Ce problème peut être divisé en deux parties. En considérant une quantité 'n' de partitions, il faut évaluer la valeur de la fiabilité de chaque module  $R_{m_k}$  pour que la fiabilité totale  $R_{C_{1_{TMR}}}$  soit maximisée. Cela peut être obtenu avec la méthode des multiplicateurs de Lagrange appliquée dans les équations (16) et (17) conforme décrit en (18).

$$g(R_{m_n}, R_{m_{n-1}}, \cdots, \lambda) = \prod_{k=1}^n (3R_{m_k}^2 - 2R_{m_k}^3) - \lambda (\prod_{k=1}^n (R_{m_k}) - R_{C_1})$$

(18)

La résolution de ce problème implique une série de dérivées partielles comme décrit ci-après :

$$\begin{cases} \frac{\partial}{\partial R_{m_1}}g = (6R_{m_1} - 6R_{m_1}^2) \prod_{k=2}^n (3R_{m_k}^2 - 2R_{m_k}^3) - \lambda \prod_{k=2}^n (R_{m_k}) = 0 \\ \frac{\partial}{\partial R_{m_2}}g = (6R_{m_2} - 6R_{m_2}^2)(3R_{m_1}^2 - 2R_{m_1}^3) \prod_{k=3}^n (3R_{m_k}^2 - 2R_{m_k}^3) - \lambda R_{m_1} \prod_{k=3}^n (R_{m_k}) = 0 \\ \frac{\partial}{\partial R_{m_3}}g = (6R_{m_3} - 6R_{m_3}^2) \prod_{k=1}^2 (3R_{m_k}^2 - 2R_{m_k}^3) \prod_{k=4}^n (3R_{m_k}^2 - 2R_{m_k}^3) - \lambda R_{m_1} R_{m_2} \prod_{k=4}^n (R_{m_k}) = 0 \\ \vdots \qquad \vdots \qquad \vdots \qquad \vdots \qquad \vdots \\ \frac{\partial}{\partial R_{m_n}}g = (6R_{m_n} - 6R_{m_n}^2) \prod_{k=1}^{n-1} (3R_{m_k}^2 - 2R_{m_k}^3) - \lambda \prod_{k=1}^{n-1} (R_{m_k}) = 0 \end{cases}$$

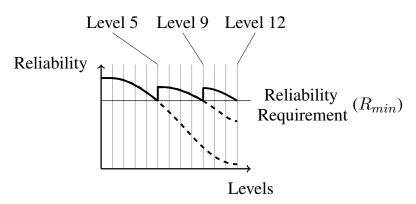

Par inspection, il peut être déterminé qu'une solution qui maximise la valeur de  $R_{C_{1_{TMR}}}$  en considérant l'utilisation de 'n' modules est  $R_{m_1} = R_{m_2} = \cdots = R_{m_n} = R_{C_1}^{1/n}$ . C'est-à-dire, le circuit doit être partitionné en modules de fiabilités aussi identiques que possible. En utilisant ce résultat, l'équation (17) devient (19). De plus, ce résultat permet l'évaluation du nombre de modules 'n' qui doivent être utilisés pour qu'un niveau de fiabilité minimale  $R_{min}$  soit atteint.

$$R_{C_{1_{TMR}}} = (3R_{C_1}^{2/n} - 2R_{C_1}^{3/n})^n (19)$$

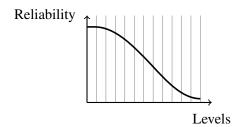

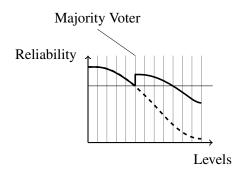

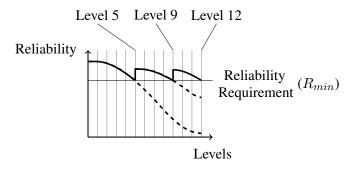

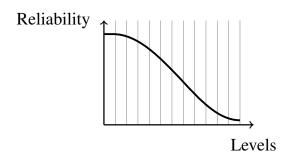

La littérature ne reporte pas l'existence d'outils permettant la mise en œuvre automatique de la procédure de partitionnement d'un circuit TMR. Pour faire face à ce problème, nous proposons une méthode basée sur une idée très simple. D'abord, il faut visualiser l'évolution de la fiabilité du signal par rapport aux niveaux logiques comme illustré dans la Figure 14. Dans ce cas, un niveau logique est défini comme un nœud qui présente la capacité de devenir la frontière d'un module.

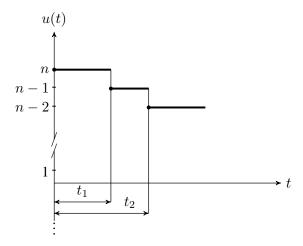

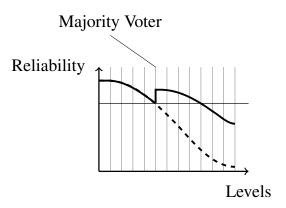

Si un arbitre est inséré dans un niveau aléatoire d'un circuit, une augmentation de la fiabilité est attendue dans ce même niveau (voir FIGURE 15). En fait, le gain en fiabilité est obtenu à cause de la capacité que possède l'arbitre de corriger des erreurs simples.

C'est bien connu que le gain en fiabilité obtenu par l'utilisation de la méthode TMR dépend de la fiabilité du module  $R_m$  comme illustré par (15). En même temps, la réduction de la fiabilité du signal illustrée dans la FIGURE 14 est aussi proportionnelle à  $R_m$ . Donc, la limitation de la réduction de la fiabilité du signal d'un circuit génère la création des

FIGURE 14 – Comportement de la fiabilité du signal d'un circuit par rapport aux nombre de niveaux

FIGURE 15 – L'insertion d'un arbitre dans un niveau aléatoire du circuit

blocs logiques de fiabilités aussi égales que possible. Cela est la première conclusion pour obtenir une solution optimale. Si ce seuil est défini par la fiabilité minimale du circuit, le résultat sera un nombre des modules 'n' très proche de la valeur optimale. Cette procédure est illustrée dans la FIGURE 16.

FIGURE 16 – Circuit TMR utilisant une distribution du processus de vote

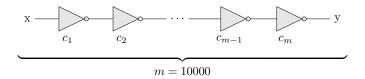

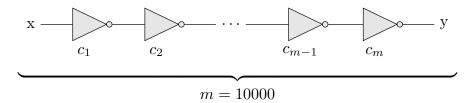

Ce résultat peut être mieux analysé en considérant un circuit simple comprenant 10000 inverseurs logiques identiques (même fiabilité  $R_m = 99.99\%$ ) connectés dans une structure en cascade (voir FIGURE 17).

La fiabilité totale du circuit  $R_c$  peut être évaluée à l'aide de l'outil SPR ( $R_c = 56.7654\%$ ). En admettant que la contrainte de fiabilité minimale est  $R_{min} = 99.9\%$ , la

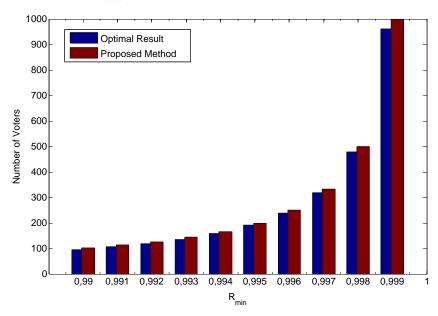

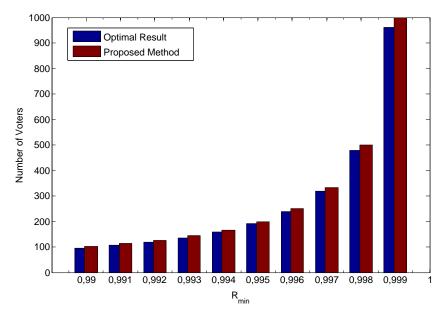

Figure 17 – Inverseurs logiques en cascade

méthode proposée insère 1000 arbitres. Tous les modules ont la même quantité de composants (N=10) sauf le premier (N=11) et le dernier (N=9). Il résulte de (19) que la quantité minimale de modules pour attendre le valeur de  $R_{min}$  est égal à 961. Cependant, cela voudrais dire que chaque partition devrait avoir 10.4058 inverseurs ce qui est impossible. La solution la plus proche possible sera l'utilisation de 10 inverseurs par module, ce qui correspond à la quantité de 1000 arbitres insérés, la même obtenue par la méthode proposée. La FIGURE 18 illustre le comportement de la méthode proposée en considérant plusieurs valeurs de  $R_{min}$ . Il peut être observé que les résultats sont proches des résultats optimaux pour tous les valeurs de  $R_{min}$  considérés.

Figure 18 – Nombre d'arbitres insérés par la méthode proposée

### Conclusion

Avec l'évolution technologique, la fiabilité joue un rôle de plus en plus important dans la conception des circuits intégrés. L'analyse de fiabilité doit être utilisée dans le flot de conception du circuit pour identifier le besoin d'utilisation des techniques de durcissement. Dans la littérature il y a plusieurs techniques d'analyse et de durcissement d'un circuit intégré. Cependant, ces téchinques présentent des limitations du fait de la complexité

d'analyse. En conséquence, le développement des nouvelles méthodes d'analyse aussi bien que des techniques de durcissement deviennent nécessaires. Dans cette thèse, plusieurs méthodes et outils d'analyse et durcissement ont été proposés.

Concernant l'analyse de fiabilité, la métrique mathématique «effective reliability» permet la prise en considération de la tolérance aux erreurs de l'application cible pour évaluer la fiabilité du circuit, alors que l'outil FIFA a été développé pour accélérer le processus d'analyse de fiabilité basée sur l'injection de fautes.

Dans le domaine de durcissement d'un circuit, deux techniques ont été développées pour identifier les portes logiques les plus critiques d'un circuit. Cela est une étape fondamentale pour l'application d'un processus de durcissement sélectif. Pour les applications qui ont besoin d'un niveau de fiabilité très élevé, un méthode automatique de partitionnement d'un circuit TMR a été élaborée. La performance optimale de cette méthode a été prouvée mathématiquement aussi bien que par simulation.

# Symbols and Abbreviations

q Gate reliability

1-q Gate unreliability

$q_i$  Reliability of bit i

$\lambda, \lambda(t)$  Failure rate

$Cha_i$  Hardening affinity parameter

R(t),  $\hat{R}(t)$  Reliability function

$R_i$  Reliability of bit i

u(t) Step function

$R_{ack}$  Probability of errors being masked according to the application

$egin{array}{ll} R_{nom} & {

m Nominal\ reliability} \\ R_{eff} & {

m Effective\ reliability} \\ R_{practical} & {

m Practical\ reliability} \\ {

m ALM} & {

m Adaptive\ logic\ module} \\ \end{array}$

ASMBL Advanced silicon modular block

AUED All-unidirectional error detecting code

BUED Burst unidirectional error detecing code

CCC Clock conditioning circuit

CD Code distance

CLB Configurable logic block

CMOS Complementary metal-oxide-semiconductor

CMT Clock management tile

DCM Digital clock management

DMA Direct memory access

DRAM Dynamic random-access memory

DUT Device under test

ECC Error correcting code

EDC Error detecting code

EDF Électricité de France

EEPROM Electrically erasable programmable read-only memory

EMI Electromagnetic interference

EPROM Erasable programmable read only memory

FA Full Adder

FIT Failures in time

FPGA Field-programmable gate array

HALT Highly accelerated life test

HD Hamming distance

IEC, CEI International electrotechnical commission

IP Intellectual propertyITM Ideal transfer matrix

ITRS International technology roadmap for semiconductors

JEDEC Joint electron devices engineering council

JTAG Joint test action group

LAB Logic array block

LE Logic element

LET Linear energy transfer LSB Least significant bit

LUT Look-up table

MBU Multiple-bit upset MCU Multiple-cell upset

MOSFET Metal-oxide-semiconductor field-effect transistor

MSB Most significant bit

MTBF Mean-time-between-failures

MTTF Mean-time-to-failure NMR N-modular redundancy OTP One time programmable

PBR Probabilistic binomial reliability model

PIP Programmable interconnect point

PLL Phase-locked loop

PTM Probabilistic transfer matrix

RAM Random-access memory RTL Register transfer level

SBD Soft breakdown

SEE Single-event effect

SEFI Single-event functional interrupt

SEL Single-event latch-up

SER Soft error rate

SET Single-event transient SEU Single-event upset

SPICE Simulation program with integrated circuit emphasis

SPR Signal probability reliability model

SPR-MP SPR multi-path model

SRAM Static random-access memory

STMR Selective triple modular redundancy

TMR Triple modular redundancy

TSC Totally self-checking

t-UED t-unidirectional error detecting code

ULA Ultra-low alpha

VHDL Very high speed integrated circuit hardware description language

VLSI Very-large-scale integration

## Contents

| In | Introduction 44 |                                                |            |  |

|----|-----------------|------------------------------------------------|------------|--|

| 1  | Bac             | ckground on Reliability                        | 51         |  |

|    | 1.1             | Introduction                                   | 51         |  |

|    | 1.2             | Reliability analysis                           | 51         |  |

|    |                 | 1.2.1 Faults in VLSI circuits                  | 55         |  |

|    |                 | 1.2.2 Reliability issues in FPGAs              | 59         |  |

|    |                 | 1.2.3 Prior works on reliability analysis      | 62         |  |

|    | 1.3             | Reliability improvement of integrated circuits | 68         |  |

|    |                 | 1.3.1 Modular redundancy                       | 68         |  |

|    |                 | 1.3.2 Voting strategies                        | 71         |  |

|    |                 | 1.3.3 Selective Hardening                      | 72         |  |

| 2  | FIF             | FA Tool                                        | <b>7</b> 5 |  |

|    | 2.1             | Introduction                                   | 75         |  |

|    | 2.2             | FIFA Tool                                      | 75         |  |

|    |                 | 2.2.1 FIFA Architecture                        | 77         |  |

|    |                 | 2.2.2 Reliability Assessment                   | 81         |  |

|    |                 | 2.2.3 Synthesis Results                        | 82         |  |

|    |                 | 2.2.4 Parallelizing the FIFA Fault Generation  | 84         |  |

|    |                 | 2.2.5 Results                                  | 88         |  |

|    |                 | 2.2.6 Conclusion                               | 89         |  |

|    |                 |                                                |            |  |

| 3  |                 | ective Reliability                             | 91         |  |

|    | 3.1             | Introduction                                   | 91         |  |

|    | 3.2             | Error tolerance                                | 92         |  |

|    | 3.3             | Effective reliability                          | 94         |  |

|    | 3.4             | Quality metrics                                | 95         |  |

|    |                 | 3.4.1 Definitions                              | 95         |  |

36 CONTENTS

|              |      | 3.4.2 Quality metric 1: bit significance        | 96 |

|--------------|------|-------------------------------------------------|----|

|              |      | 3.4.3 Quality metric 2: relative error          | 97 |

|              | 3.5  | Simulation results                              | 98 |

|              |      | 3.5.1 Median filter                             | 98 |

|              |      | 3.5.2 8-bit ripple carry adder                  | 00 |

|              |      | 3.5.3 4-bit multiplier                          | 02 |

|              | 3.6  | Conclusion                                      | 04 |

| 4            | Sele | ective Hardening 10                             | 07 |

|              | 4.1  | Introduction                                    | 07 |

|              | 4.2  | Avoiding Critical Errors in Integrated Circuits | 07 |

|              |      | 4.2.1 Nominal reliability                       | 07 |

|              |      | 4.2.2 Practical reliability                     | 08 |

|              |      | 4.2.3 Selectively applying TMR                  | 09 |

|              | 4.3  | Using a Cost Function to Detect Critical Gates  | 14 |

|              |      | 4.3.1 Cost function profiling                   | 16 |

|              |      | 4.3.2 Experimental results                      | 19 |

|              |      | 4.3.3 Comparison with related works             | 20 |

|              | 4.4  | Conclusion                                      | 21 |

| 5            | Opt  | imizing Voter Placement for TMR Systems 12      | 23 |

|              | 5.1  | Introduction                                    | 23 |

|              | 5.2  | TMR approach                                    | 23 |

|              | 5.3  | Partitioning a TMR design                       | 25 |

|              | 5.4  | Problem of automatically inserting voters       |    |

|              | 5.5  | Proposed method                                 | 29 |

|              | 5.6  | Conclusion                                      | 34 |

| 6            | Con  | cluding Remarks 13                              | 35 |

| $\mathbf{A}$ | Oth  | er Methods for Reliability Improvement of ICs   | 39 |

|              | A.1  | Fault detection and correction                  | 39 |

|              |      | A.1.1 Basic principles                          | 39 |

|              |      | A.1.2 Fault detection techniques                | 40 |

|              | A.2  | Evolvable hardware                              | 49 |

| В            | Bas  | ics on FPGAs                                    | 53 |

|              | B.1  | FPGA technologies                               | 53 |

|              |      | B.1.1 Fusible link technology                   | 53 |

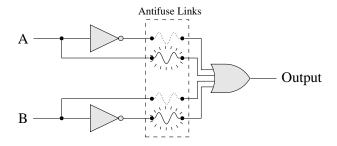

|         | B.1.2  | Antifuse                 | 154 |

|---------|--------|--------------------------|-----|

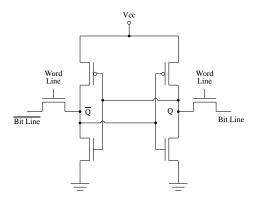

|         | B.1.3  | Static memory technology | 156 |

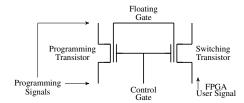

|         | B.1.4  | Flash technology         | 157 |

|         | B.1.5  | Summary                  | 159 |

| B.2     | FPGA   | s architectures          | 159 |

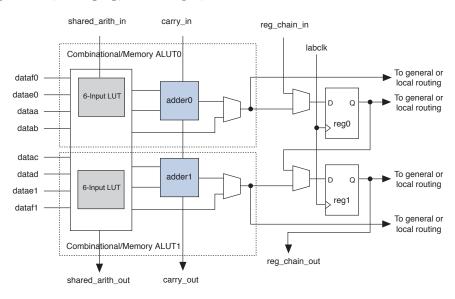

|         | B.2.1  | Altera                   | 159 |

|         | B.2.2  | Xilinx                   | 162 |

|         | B.2.3  | Actel                    | 165 |

|         | B.2.4  | Lattice                  | 167 |

| Conclu  | ısion  |                          | 169 |

| Glossa  | ry     |                          | 171 |

| Notati  | ons    |                          | 171 |

| Bibliog | graphy |                          | 184 |

38 CONTENTS

# List of Figures

| 1.1  | Number of functioning parts of a circuit at time t          | 53               |

|------|-------------------------------------------------------------|------------------|

| 1.2  | Bathtub curve                                               | 54               |

| 1.3  | Residue induced intermittent fault in a DRAM chip           | 57               |

| 1.4  | Effects of a high-energy ion hitting a semiconductor device | 58               |

| 1.5  | Fault simulation approach proposed by Ogus                  | 63               |

| 1.6  | PTM representation for an AND gate                          | 64               |

| 1.7  | Basic interconnection models of PTM                         | 64               |

| 1.8  | SPR matrix for the output of a 2-input OR gate              | 65               |

| 1.9  | Propagation of the SPR matrices through a circuit           | 65               |

| 1.10 | TMR concept envisaged by Von Neumann                        | 69               |

| 1.11 | TMR performance regarding reliability improvement           | 69               |

| 1.12 | TMR with three majority voters                              | 70               |

| 1.13 | Word-Voter proposed in [21]                                 | 71               |

| 0.1  |                                                             | 70               |

| 2.1  | General scheme of the proposed tool                         | 78<br><b>-</b> 2 |

| 2.2  | General scheme of a saboteur                                | 78               |

| 2.3  | FIFA Timing diagram of communication signals                | 80               |

| 2.4  | Example of a step by step execution of Algorithm 1          | 81               |

| 2.5  | Synthesis results of the FIFA tool                          | 83               |

| 2.6  | A simple parallel architecture for FIFA                     | 85               |

| 2.7  | The proposed parallel architecture for FIFA                 | 85               |

| 2.8  | Example of a fault pattern generation sequence              | 86               |

| 2.9  | Pascal's triangle                                           | 87               |

| 2.10 | Total logic elements                                        | 89               |

| 2.11 | Number of clock cycles                                      | 89               |

| 3.1  | Example of a logical masking                                | 92               |

| 3.2  | Bit-flip occurrence in a sine wave                          | 93               |

| 3.3  | General schema for reliability calculation                  | 95               |

|      |                                                             |                  |

| 3.4  | Example of matrix <b>E</b> considering 3 errors                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

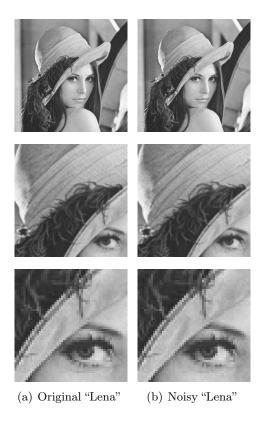

| 3.5  | Comparison between the original and the noisy "Lena" pictures $\ \ldots \ \ldots \ 100$                                                                             |

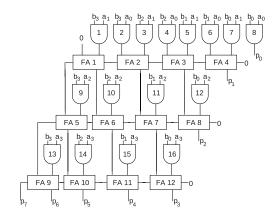

| 3.6  | Structure of FA (full adder) block                                                                                                                                  |

| 3.7  | Schema of FA block                                                                                                                                                  |

| 3.8  | Structure of a 4-bit multiplier block                                                                                                                               |

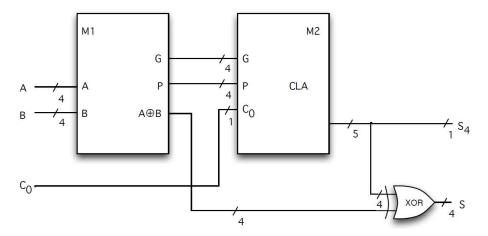

| 4.1  | 4-bit fast adder circuit                                                                                                                                            |

| 4.2  | 74283 gate-level schematic                                                                                                                                          |

| 4.3  | Simulation results for the 74283 circuit                                                                                                                            |

| 4.4  | Cost function profile for the circuit $c432$                                                                                                                        |

| 4.5  | Cost function profile for the circuit $c499 \dots $           |

| 4.6  | Both heuristics applied to the circuit $c1355$                                                                                                                      |

|      |                                                                                                                                                                     |

| 5.1  | TMR block scheme                                                                                                                                                    |

| 5.2  | Reliability gain using TMR                                                                                                                                          |

| 5.3  | Partitioning a TMR design                                                                                                                                           |

| 5.4  | $C_1$ comprises $n$ modules serially interconnected                                                                                                                 |

| 5.5  | Plot of $R_{m_1} = \frac{R_{C_1}}{R_{m_2}}$ for different values of $R_{C_1}$                                                                                       |

| 5.6  | Reliability of a circuit versus its number of levels                                                                                                                |

| 5.7  | Insertion of a majority voter                                                                                                                                       |

| 5.8  | Distributing the voting process of a TMR circuit                                                                                                                    |

| 5.9  | Cascade of inverters                                                                                                                                                |

| 5.10 | Number of voters inserted by the proposed technique                                                                                                                 |

| 5.11 | Circuit 74283 - Gate level                                                                                                                                          |

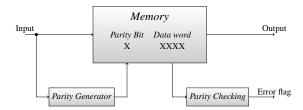

| A.1  | Example of a duplex comparison scheme                                                                                                                               |

| A.2  | Computer memory using parity checking                                                                                                                               |

|      |                                                                                                                                                                     |

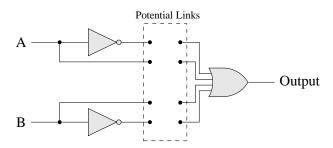

| B.1  | Programmable circuit concept                                                                                                                                        |

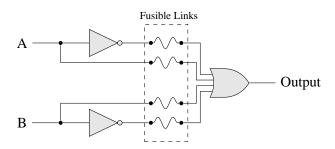

| B.2  | Programmable circuit with intact fusible links                                                                                                                      |

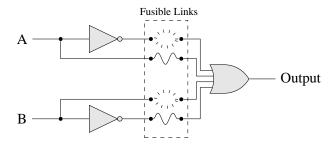

| B.3  | Programmed circuit with output $Y = A + \bar{B}$                                                                                                                    |

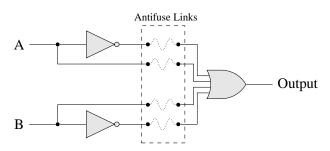

| B.4  | Programmable circuit with intact antifuses                                                                                                                          |

| B.5  | Programmed circuit with output $Y = A + \bar{B}$                                                                                                                    |

| B.6  | Static Memory Cell                                                                                                                                                  |

| B.7  | Flash memory cell - ProASIC3                                                                                                                                        |

| B.8  | ALM High-Level Block Diagram                                                                                                                                        |

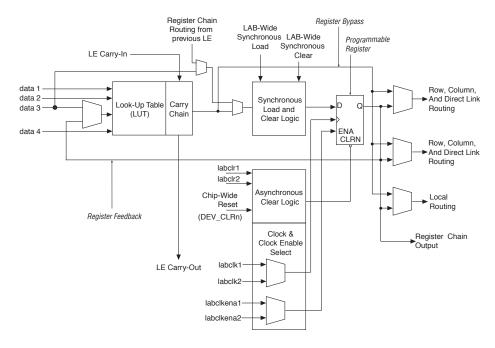

| B.9  | LE Block Diagram                                                                                                                                                    |

| B.10 | Example of devices using the ASMBL architecture $\dots \dots \dots$ |

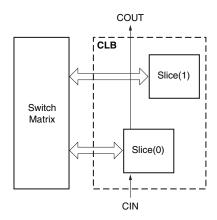

| B.11 | High-level block diagram of a CLB in Spartan FPGAs $\ \ldots \ \ldots \ \ldots \ 164$                                                                               |

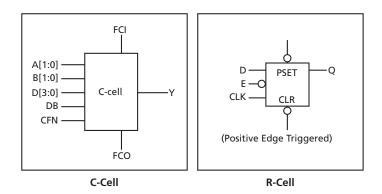

| B.12 AX C-Cell and R-Cell        |

|----------------------------------|

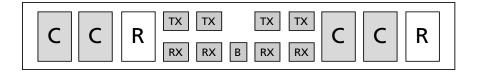

| B.13 AX SuperCluster Arrangement |

| B.14 PFU block diagram           |

# List of Tables

| 1.1 | Programming technology properties summary                           |

|-----|---------------------------------------------------------------------|

| 2.1 | Fuse platform vs. FIFA tool                                         |

| 3.1 | Effective reliability evaluation for different error tolerances     |

| 3.2 | Reliability values for the output bits of a full adder              |

| 3.3 | R <sub>eff</sub> for different error tolerances (CRA8)              |

| 3.4 | Reliability values for each output bit of the 4-bit multiplier      |

| 3.5 | $R_{\rm eff}$ for different error tolerances (MUL4)                 |

| 4.1 | Reliability values of three different architectures of an adder 108 |

| 4.2 | Error analysis for the gates of the circuit 74283                   |

| 4.3 | Reliability Analysis of 74283                                       |

| 4.4 | Hardware affinity $(Cha_i)$ parameters for some cells               |

| 4.5 | Results for the sum of elements heuristic, $K=10$                   |

| 4.6 | Results for the percent wise heuristic, $X = 50\%$                  |

| 5.1 | Placement of the voters for the circuit 74283                       |

| 5.2 | Reliability of gates based on their area                            |

| 5.3 | Placement of the voters for the 74283 circuit                       |

| A.1 | 3-bit Berger code – $B_0$ scheme                                    |

| A.2 | Bose code for data words comprising 4 bits                          |

| A.3 | Syndrome Table for Hamming (7,4) code                               |

| B.1 | Programming technology properties summary                           |

| B.2 | Altera Devices Comparison                                           |

| B.3 | Xilinx Devices Comparison                                           |

| B.4 | Actel Devices Comparison                                            |

| B.5 | Lattice Devices Comparison                                          |

The first electronic computer was built in Antanasoff's Iowa State College in 1942 [22] and used rather unreliable components. Improve the system reliability was a major concern and techniques such as duplexing with comparison, triplication with voting, control codes, among others, were proposed. Indeed, important researches were done by J. Von Neumann, E. F. Moore and C. E. Shannon using redundancy as a mean to build reliable systems from less reliable components [23, 24].

Since then, the integrated circuit technology has underwent an exponential evolution as predicted by the *Moore's law* [1,2]. Nowadays devices are shrinking into the decananometer range, allowing the fabrication of chips containing billions of transistors, and operating at very high speeds (multiple GHz). In such scale, new physical phenomena, such as Van Der Waals and Casimir forces, appear leading to new fabrication methodologies and affecting the components reliability [3]. Further, interconnect systems are becoming very complex, particularly with the introduction of the 3-D die integration scheme [4]. In fact, the higher density of integrated circuits together with the higher complexity of the interconnections lead to a higher probability of erroneous components in a die. Meanwhile, the higher frequencies pose strict limits to timing, thus also increasing the probability of timing errors [5]. In other words, a reduction in manufacturing yield is expected, as well as in the overall circuit reliability [6–10].

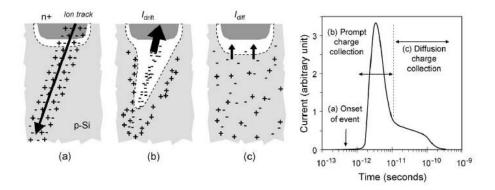

Consequently, faults have become more and more likely to occur in deep-submicron technologies. Permanent faults can be significantly reduced by performing deep investigations during offline testing [25]. On contrary to that, transient faults depend on environmental conditions, and therefore they randomly occur during circuit operation. In the past, these faults used to be a concern only on the design of memories. However, the technology scaling has increased the susceptibility of combinational blocks to thermal bit-flips, radiation events, among others, so that their resulting error rates are approaching those of memories [26, 27]. This is a serious menace to circuits designed to operate under critical environments such as nuclear power plants, avionics, among others, and therefore solutions to construct fault-tolerant circuits are necessary.

This dissertation is a result of a CIFRE partnership between EDF R&D and Télécom

Paristech. The motivations for this work can be explained as follows. EDF is one of the world's largest producers of electricity with main activity in nuclear power. EDF's control-command systems are based on electronics devices/circuits. Nuclear power plants consider safety as a very high priority in their systems, and electronic circuits must be in accordance to several technical standards such as the IEC 62566 [11], the IEC 60987 [12], and the IEC 61513 [13] in order to be qualified to operate in such critical environments. Particularly, the use of programmable devices poses a great challenge to be qualified since the functionality of the IC is not defined by the founder of the physical component, but by the designer of the application. Further, the technical standard IEC 62566 states that the benefits accomplished by the use of redundancy in an electronic circuit must be balanced with the corresponding increase in the system complexity as well as in the fault coverage. Because of that, methods to analyze and to improve the reliability of electronic circuits to be used in nuclear power plants are a major concern.

The main objective of the current work is to propose methods to analyze and to improve the reliability of circuits in order to facilitate their qualification according to the aforementioned technical standards. Therefore, different strategies that allows both to achieve a very high level of reliability in a circuit and to control the amount of redundancy adding are required. These methods must be developed in such a way that they can be used to construct circuits using programmable devices as well as for circuits tailored for a specific function, e.g. ASICs. Also, the proposed solutions must be able to be appended to traditional design flows of integrated circuits.