#### Modélisation de plate-forme avionique pour exploration de performance en avance de phase

Michaël Lafaye

#### ▶ To cite this version:

Michaël Lafaye. Modélisation de plate-forme avionique pour exploration de performance en avance de phase. Autre. Télécom ParisTech, 2012. Français. NNT: 2012ENST0065. pastel-01001760

#### HAL Id: pastel-01001760 https://pastel.hal.science/pastel-01001760

Submitted on 4 Jun 2014

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **Doctorat ParisTech**

#### THÈSE

pour obtenir le grade de docteur délivré par

#### Télécom ParisTech

présentée et soutenue publiquement par

#### Michaël LAFAYE

le 19 novembre 2012

#### Modélisation de Plate-Forme Avionique pour Exploration de Performance en Avance de Phase

Directeur de thèse : **Pr. Laurent Pautet, Telecom ParisTech** Directeur de thèse : **Dr. Marc Gatti, Thales Avionics**

#### Jury

M. Elie NAJM, Professeur, LTCI, Telecom ParisTech Président du jury

M. Jean-Charles FABRE, Professeur, LAAS, Institut National Polytechnique de Toulouse Rapporteur

M. Paul LE GUERNIC, Directeur de Recherche, IRISA, Université de Rennes Rapporteur

M. Jean-Loup TERRAILLON, Directeur du Service Logiciel Embarqué, Examinateur

Agence Spatiale Européenne

M François PECHEUX, Enseignant chercheur, LIP6, Université Pierre et Marie Curie Paris 6 Examinateur Professeur, DTIM, Office National d'Etudes et de Examinateur Recherches Aérospatiales

ii

#### Remerciements

Il est temps d'écrire les derniers mots de ce manuscrit, et refermer le chapitre de ma thèse. "L'important n'est pas la destination mais le voyage". Un voyage de trois années dont je retiens, au-delà de l'aboutissement, l'expérience accumulée dans les bons moments comme dans les moments plus compliqués. "Les pierres font partie du chemin".

Je repense également aux différentes rencontres, aux personnes qui ont contribué, d'une manière ou d'une autre, à mener à bien ce voyage.

Je remercie mes encadrants, Laurent Pautet et Marc Gatti, pour m'avoir montré la voie. Leurs conseils m'ont permis de rester sur le bon chemin. "Pour connaître le chemin, interroge celui qui en vient"

Je remercie également Jean-Charles Fabre et Paul Le Guernic qui ont accepté d'être les rapporteurs de ce mémoire, ainsi que Bernard Lecussan, Elie Najm, François Pecheux et Jean-Loup Terraillon pour avoir accepté de faire partie de mon jury.

Mes remerciements vont également à mes collègues de Thales. Les nombreux échanges que nous avons eu ont contribué à ce travail, chacun m'apportant son expérience dans ou ou plusieurs domaines connexes à ma thèse.

Je pense bien évidemment à tous mes amis. Les doctorants, docteurs, post-docs et autres personnes de Thales et Telecom : Gilles, Simon, Cuauhtemoc, Fabien, Xavier J., Antoine, Sebastien T., Azin, Hoa, Nora, Asma, Nesrine, Elie, Sylvain, Imen, Joe, Marilena, Damien, Silviu, Greg, Thomas M., Khalil, Donguy, Xavier G., Thomas R., Sebastien G., Etienne, Olivier, Hayette...grâce aux bons moments passés ensemble, le quotidien n'aura pas été que labeur permanent (les sessions projet C vont me manquer!).

Je pense aussi à Tom, Mathilde, Céline et Seb, Elise et Dom, Hayder, David, Sophie...qui, n'étant ni à Thales ni à Telecom, ne m'ont pas forcément vu souvent (la thèse est une maitresse exigeante!) mais sont restés présents.

Une pensée particulière à ma compagne, Atoosa. Nous avons travaillé sur nos thèses respectives côte à côté, soutenant presque en même temps. Chacun a remonté le moral de l'autre dans les moments difficiles, nous permettant de mener à bien cette aventure, et entamer ensemble un nouveau voyage.

Enfin, je remercie ma famille pour leurs encouragements, et plus particulièrement ma soeur et mes parents. Toujours présents, soutien permanent, je leur dois la réussite de mes études, et cette thèse est aussi la leur.

#### Résumé

De nos jours, les systèmes embarqués temps-réels critiques intègrent de plus en plus de composants, et voient leur complexité augmenter. Les systèmes avioniques ont suivi cette évolution, voyant augmenter leurs processus de développement.

Dès lors, les développeurs de plates-formes avioniques se sont tournés vers les méthodes de modélisation en avance de phase (i.e. en tout début de cycle de développement), afin d'anticiper les performances de celles-ci et aider à leur dimensionnement. Particulièrement, l'exploration de l'utilisation des ressources matérielles de la plateforme par la partie applicative (l'ensemble des applications) est le point central de cette exploration des performances. Si les méthodes de modélisation actuelles offrent la possibilité de modéliser une plate-forme depuis les exigences jusqu'au niveau architectural, elles ne sont pas encore adaptées à la modélisation comportementale. Elle ne permettent donc pas l'étude du comportement et la comparaison de différentes architectures d'une plate-forme en avance de phase.

Mes travaux de thèse ont pour but d'offrir un processus de modélisation et simulation de plate-forme avionique répondant à cette problématique. L'objectif est de compléter les méthodes de modélisation actuelles pour apporter une analyse plus fine des performances d'une plate-forme en avance de phase, et les comparer avec les exigences. Pour cela, nous proposons une approche en quatre étapes : i) une étape de modélisation des applications et d'extraction des stimuli applicatifs; ii) une étape de modélisation architecturale du système basée sur AADL (Architecture Analysis and Design Language) et son annexe ARINC653; iii) une étape de génération d'un modèle comportemental de la partie matérielle et intergicielle du système en SystemC-TLM; iv) une étape de simulation et d'analyses, où les stimuli applicatifs sont exécutés par le modèle comportemental, et les performances extraites comparées aux exigences système. Enfin, nous avons validé notre méthode sur un cas d'étude avionique que nous présenterons également.

**Mots-clés**: systèmes embarqués temps-réel critiques, systèmes avioniques, modélisation, simulation, AADL, SystemC-TLM

#### **Abstract**

Nowadays, real-time critical embedded systems are more and more complex due to an increase of the integrated components. Following that trend, avionic systems development complexity increases too.

So early modeling processes are more and more used in order to anticipate on platforms performance and help sizing them. Particularly, hardware resources usage exploration is a key aspect for performance exploration. Current processes allow to model avionic platform from requirements to architectural level of abstraction, but they do not allow to model a behavioral avionic platform. Thus, they do not allow to explore the hardware resources usage of the platform, neither to compare some alternatives of architectures at early phase of development cycle.

My PhD work presents our avionic platform modeling and simulation process that answer that problem. The goal is to complete current modeling processes to offer more accurate early performance analysis, and compare them with the system requirements. For that, we propose a for steps method: i) an application modeling and stimuli extraction step; ii) an architectural modeling step, based on the AADL (Architecture Analysis and Design Language) and its ARINC653 annex; iii) a behavioral execution platform model (hardware and middleware) generation step with SystemC-TLM; iv) a simulation and analysis step, when performance are compared with system requirements. At last, we will present our validation part on an avionic case study.

**Keywords**: real-time critical embedded systems, avionics systems, modeling, simulation, AADL, SystemC-TLM

### **Table des matières**

|    | Introduction Générale |       |         |                                                             |    |

|----|-----------------------|-------|---------|-------------------------------------------------------------|----|

|    | 1                     | Intro | oductio | on                                                          | 3  |

|    |                       | 1.1   | Conte   | xte avionique                                               | 4  |

|    |                       |       | 1.1.1   | Application avionique                                       | 4  |

|    |                       |       | 1.1.2   | Architecture des systèmes avioniques                        | 5  |

|    |                       | 1.2   | Problé  | ématique générale                                           | 11 |

|    |                       |       | 1.2.1   | Une nouvelle architecture avionique                         | 11 |

|    |                       |       | 1.2.2   | Adapter les méthodes de conception d'une plate-forme        | 11 |

|    |                       | 1.3   | Objec   | tifs et approche                                            | 12 |

|    |                       |       | 1.3.1   | Objectif                                                    | 12 |

|    |                       |       | 1.3.2   | Approche                                                    | 12 |

|    |                       | 1.4   | Plan c  | du mémoire                                                  | 13 |

| II | E                     | njeu  | x Indu  | ustriels                                                    |    |

|    | 2                     | Pro   | blémat  | ique industrielle                                           | 17 |

|    |                       | 2.1   | Introd  | uction                                                      | 18 |

|    |                       | 2.2   | Exploi  | ration des performances en avance de phase                  | 19 |

|    |                       | 2.3   | Modél   | lisation de la plate-forme avionique                        | 20 |

|    |                       |       | 2.3.1   | Niveaux d'abstraction pour la modélisation de plate-forme . | 20 |

|    |                       |       | 2.3.2   | Modélisation de systèmes avioniques                         | 22 |

|    |                       |       | 2.3.3   | Résumé                                                      | 24 |

|    |                       | 2.4   | Modél   | lisation d'une application                                  | 25 |

|    |                       |       | 2.4.1   | Niveau d'abstraction pour la modélisation                   | 25 |

|   |      | 2.4.2  | Organisation des stimuli                                    | 27 |

|---|------|--------|-------------------------------------------------------------|----|

|   | 2.5  | Evalua | ation des performances de la plate-forme en avance de phase | 28 |

|   | 2.6  | Synth  | èse                                                         | 29 |

| 3 | Etat | de l'A | rt                                                          | 31 |

|   | 3.1  | Introd | uction                                                      | 32 |

|   | 3.2  | Langa  | ages de modélisation                                        | 33 |

|   |      | 3.2.1  | Introduction                                                | 33 |

|   |      | 3.2.2  | Langages synchrones et méthodes formelles                   | 33 |

|   |      | 3.2.3  | Langage de modélisation système                             | 34 |

|   |      | 3.2.4  | Langages de modélisation architecturale                     | 34 |

|   |      | 3.2.5  | Langages de description matérielle                          | 36 |

|   |      | 3.2.6  | Résumé                                                      | 36 |

|   | 3.3  | Métho  | odes de modélisation de plates-formes avioniques            | 37 |

|   |      | 3.3.1  | Introduction                                                | 37 |

|   |      | 3.3.2  | Modélisation d'une plate-forme globale                      | 38 |

|   |      |        | 3.3.2.1 Modélisation architecturale                         | 38 |

|   |      |        | 3.3.2.2 Modélisation physique                               | 41 |

|   |      |        | 3.3.2.3 Modélisation mixte                                  | 41 |

|   |      | 3.3.3  | Modélisation du réseau avionique                            | 43 |

|   |      | 3.3.4  | Modélisation des services ARINC653 pour les systèmes d'ex-  |    |

|   |      |        | ploitation avioniques                                       | 44 |

|   |      | 3.3.5  | Modélisation d'une application avionique                    | 45 |

|   | 3.4  | Langa  | ages et méthode de modélisation sélectionnés                | 46 |

|   |      | 3.4.1  | AADL                                                        | 47 |

|   |      |        | 3.4.1.1 Composants                                          | 47 |

|   |      |        | 3.4.1.2 Interfaces, connections et déploiement              | 48 |

|   |      |        | 3.4.1.3 Extensions et outils                                | 49 |

|   |      | 3.4.2  | SystemC                                                     | 50 |

|   |      |        | 3.4.2.1 Structure du langage                                | 50 |

|   |      |        | 3.4.2.2 Bibliothèque TLM                                    | 51 |

|   |      |        | 3.4.2.3 Communications                                      | 52 |

|   |      |        | 3.4.2.4 Outils                                              | 54 |

|   | 3.5  | Synth  | èse                                                         | 54 |

#### III Approche adoptee

| 4 | Met | nodologie                                     |                                              | 59 |  |  |  |

|---|-----|-----------------------------------------------|----------------------------------------------|----|--|--|--|

|   | 4.1 | Rappel des objectifs                          |                                              | 60 |  |  |  |

|   | 4.2 | .2 Structure globale                          |                                              |    |  |  |  |

|   | 4.3 | es de la partie applicative et génération des |                                              |    |  |  |  |

|   |     | stimuli                                       |                                              | 63 |  |  |  |

|   |     | 4.3.1 Objectifs                               |                                              | 63 |  |  |  |

|   |     | 4.3.2 Extraction de la                        | configuration logicielle                     | 63 |  |  |  |

|   |     | 4.3.3 Génération des                          | stimuli applicatifs                          | 64 |  |  |  |

|   |     | 4.3.4 Résumé                                  |                                              | 66 |  |  |  |

|   | 4.4 | Modélisation architectu                       | urale de la plate-forme avionique            | 67 |  |  |  |

|   |     | 4.4.1 Objectifs                               |                                              | 67 |  |  |  |

|   |     | 4.4.2 Démarche                                |                                              | 67 |  |  |  |

|   |     | 4.4.3 Introduction des                        | s spécificités avioniques                    | 68 |  |  |  |

|   |     | 4.4.4 Ajout de proprié                        | étés                                         | 70 |  |  |  |

|   |     | 4.4.5 Résumé                                  |                                              | 70 |  |  |  |

|   | 4.5 | Génération d'un modè                          | ele comportemental de la plate-forme d'exé-  |    |  |  |  |

|   |     | cution                                        |                                              | 70 |  |  |  |

|   |     | 4.5.1 Objectifs                               |                                              | 70 |  |  |  |

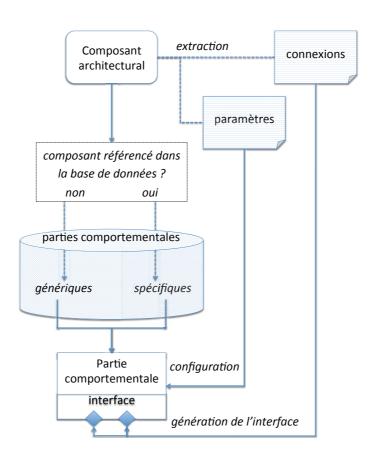

|   |     | 4.5.2 Génération des                          | composants comportementaux                   | 71 |  |  |  |

|   |     | 4.5.3 Résumé                                  |                                              | 74 |  |  |  |

|   | 4.6 | Exploration des perform                       | mances de la plate-forme                     | 74 |  |  |  |

|   |     | 4.6.1 Objectifs                               |                                              | 74 |  |  |  |

|   |     | 4.6.2 Simulation                              |                                              | 74 |  |  |  |

|   |     | 4.6.3 Analyses                                |                                              | 75 |  |  |  |

|   |     | 4.6.4 Résumé                                  |                                              | 76 |  |  |  |

|   | 4.7 | Synthèse                                      |                                              | 76 |  |  |  |

| 5 | Мар | ping des éléments ma                          | atériels AADL en SystemC                     | 79 |  |  |  |

|   | 5.1 | Introduction                                  |                                              | 81 |  |  |  |

|   | 5.2 | Modélisation des spéc                         | ificités avioniques au sein d'un modèle AADL | 82 |  |  |  |

|   |     | 5.2.1 Modélisation du                         | partitionnement temporel                     | 82 |  |  |  |

|   |     | 5.2.2 Modélisation du                         | u partitionnement spatial                    | 83 |  |  |  |

|   |     | 5.2.3 Modélisation de                         | e l'ordonnancement                           | 83 |  |  |  |

|   | 5.3  | Extrac                                                 | Extraction des paramètres du modèle AADL 8  |                                                          |     |  |  |  |

|---|------|--------------------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|--|--|--|

|   |      | 5.3.1                                                  | Extraction                                  | on des paramètres des composants matériels de la         |     |  |  |  |

|   |      |                                                        | plate-for                                   | me                                                       | 84  |  |  |  |

|   |      | 5.3.2                                                  | Extraction                                  | on des paramètres de la partie applicative de la plate-  |     |  |  |  |

|   |      |                                                        | forme                                       |                                                          | 85  |  |  |  |

|   |      | 5.3.3                                                  |                                             | Extraction des paramètres de connexion de la plate-forme |     |  |  |  |

|   |      |                                                        | matérielle                                  |                                                          |     |  |  |  |

|   | 5.4  | Génér                                                  | ration de la plate-forme matérielle SystemC |                                                          |     |  |  |  |

|   |      | 5.4.1                                                  | Descript                                    | ion du comportement d'un composant                       | 86  |  |  |  |

|   |      |                                                        | 5.4.1.1                                     | Base d'automates comportementaux                         | 87  |  |  |  |

|   |      | 5.4.1.2 Extension des paramètres AADL pour l'adressage |                                             |                                                          |     |  |  |  |

|   |      | des automates SystemC                                  |                                             |                                                          |     |  |  |  |

|   |      |                                                        | 5.4.1.3                                     | Configuration de l'automate                              | 90  |  |  |  |

|   |      |                                                        | 5.4.1.4                                     | Modélisation du système d'exploitation                   | 91  |  |  |  |

|   |      | 5.4.2                                                  | Générat                                     | ion d'une interface générique : le container matériel    | 92  |  |  |  |

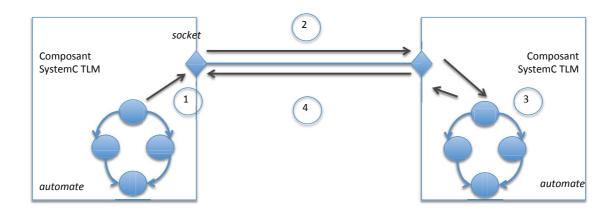

|   |      |                                                        | 5.4.2.1                                     | Rappel du principe de communication TLM                  | 92  |  |  |  |

|   |      |                                                        | 5.4.2.2                                     | Le Container : principe                                  | 94  |  |  |  |

|   |      |                                                        | 5.4.2.3                                     | Le Container : mécanisme d'abonnement et filtrage        | 96  |  |  |  |

|   |      | 5.4.3                                                  | Intégrati                                   | on                                                       | 98  |  |  |  |

|   | 5.5  | Synthe                                                 | èse                                         |                                                          | 100 |  |  |  |

| 6 | Métl | hode d                                                 | e généra                                    | tion des stimuli applicatifs en avance de phase          | 101 |  |  |  |

|   | 6.1  | Introdu                                                | uction .                                    |                                                          | 102 |  |  |  |

|   | 6.2  | Modél                                                  | isation d'ı                                 | une application en avance de phase                       | 102 |  |  |  |

|   |      | 6.2.1                                                  | Principe                                    |                                                          | 102 |  |  |  |

|   |      | 6.2.2                                                  | Descript                                    | ion des tâches applicatives                              | 103 |  |  |  |

|   | 6.3  | Génér                                                  | ation des                                   | stimuli applicatifs                                      | 104 |  |  |  |

|   |      | 6.3.1                                                  | Principe                                    |                                                          | 104 |  |  |  |

|   |      | 6.3.2                                                  | Adaptati                                    | on aux variantes architecturales de la partie maté-      |     |  |  |  |

|   |      |                                                        | rielle de                                   | la plate-forme                                           | 105 |  |  |  |

|   | 6.4  | Synthe                                                 | èse                                         |                                                          | 108 |  |  |  |

#### **IV** Validation

| 7 | Exp          | érimen | ntations et Résultats                                          | 111      |  |  |  |

|---|--------------|--------|----------------------------------------------------------------|----------|--|--|--|

|   | 7.1          | Introd | uction                                                         | 112      |  |  |  |

|   | 7.2          | Cas d  | 'Etude                                                         | 112      |  |  |  |

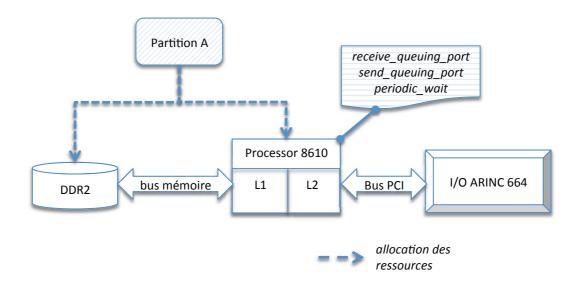

|   |              | 7.2.1  | Calculateur avionique                                          | 112      |  |  |  |

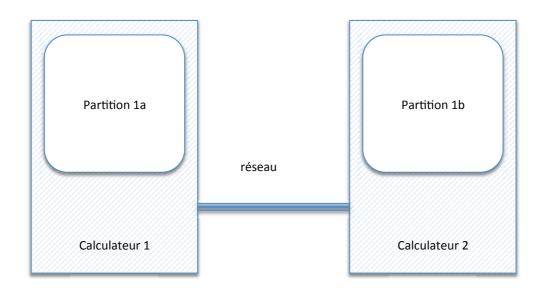

|   |              | 7.2.2  | Plate-forme avionique                                          | 113      |  |  |  |

|   | 7.3          | Mise 6 | en oeuvre du processus sur un calculateur                      | 114      |  |  |  |

|   |              | 7.3.1  | Description des applications                                   | 115      |  |  |  |

|   |              | 7.3.2  | Modélisation architecturale du calculateur                     | 117      |  |  |  |

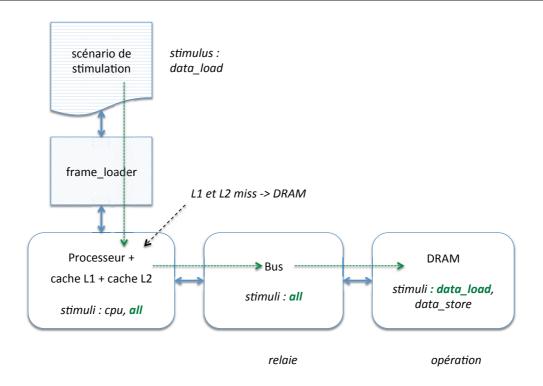

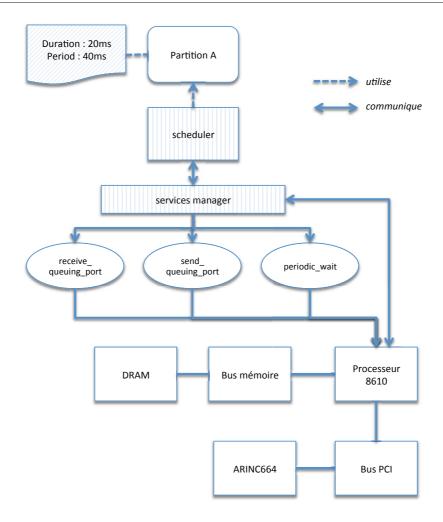

|   |              | 7.3.3  | Génération de la plate-forme d'exécution en SystemC            | 118      |  |  |  |

|   |              | 7.3.4  | Simulation et analyse des résultats                            | 120      |  |  |  |

|   | 7.3.5 Résumé |        |                                                                |          |  |  |  |

|   | 7.4          | Mise 6 | en oeuvre du processus sur une plate-forme                     | 123      |  |  |  |

|   |              | 7.4.1  | Présentation de la plate-forme de test                         | 123      |  |  |  |

|   |              | 7.4.2  | Modélisation du réseau ARINC664                                | 124      |  |  |  |

|   |              | 7.4.3  | Modélisation des services de l'API ARINC653                    | 125      |  |  |  |

|   |              | 7.4.4  | Modélisation d'un calculateur au sein de la plate-forme        | 126      |  |  |  |

|   |              |        | 7.4.4.1 Modélisation architecturale                            | 126      |  |  |  |

|   |              |        | 7.4.4.2 Modélisation comportementale                           | 127      |  |  |  |

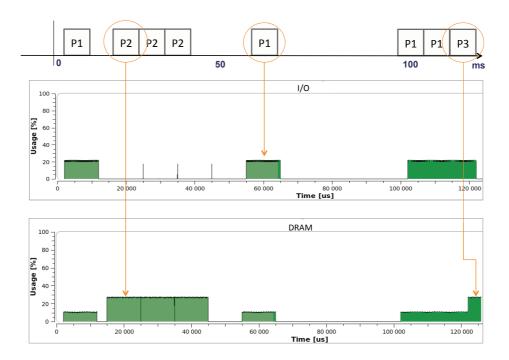

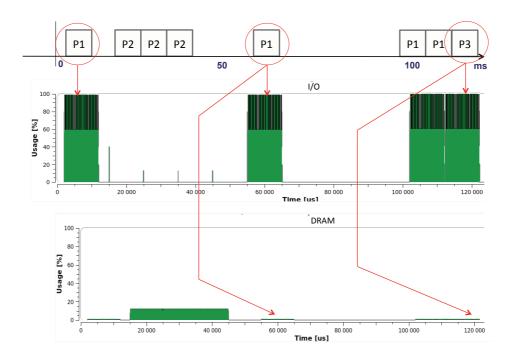

|   |              | 7.4.5  | Simulation et analyses des résultats                           | 128      |  |  |  |

|   |              |        | 7.4.5.1 Analyse des temps d'exécution                          | 128      |  |  |  |

|   |              |        | 7.4.5.2 Temps de simulation                                    | 129      |  |  |  |

|   |              |        | 7.4.5.3 Extraction de l'utilisation des ressources matérielles | 130      |  |  |  |

|   | 7.5          | Synth  | èse                                                            | 132      |  |  |  |

|   |              |        |                                                                |          |  |  |  |

| _ | ono          | lucior | n Générale                                                     | 135      |  |  |  |

| C | OHC          | iusioi | Generale                                                       | 133      |  |  |  |

| 8 | Con          | clusio | ns et Perspectives                                             | 137      |  |  |  |

|   | 8.1          | Rappe  | el des contributions                                           | 138      |  |  |  |

|   |              | 8.1.1  | Génération d'un modèle comportemental de plate-forme d'exe     | <b>-</b> |  |  |  |

|   |              |        | cution à partir d'un modèle architectural                      | 138      |  |  |  |

|   |              | 8.1.2  | Modélisation d'une application en avance de phase              | 139      |  |  |  |

|   | 8.2          | Concl  | usion                                                          | 139      |  |  |  |

#### Table des matières

| Bibliogra | aphie    |                             | 145 |

|-----------|----------|-----------------------------|-----|

|           | 8.3.2    | Perspectives                | 142 |

|           | 8.3.1    | Limites                     | 141 |

| 8.        | 3 Limite | s et perspectives           | 141 |

|           | 8.2.3    | Automatisation du processus | 140 |

|           | 8.2.2    | Résultats expérimentaux     | 140 |

|           | 8.2.1    | Méthodologie                | 139 |

|           |          |                             |     |

# Liste des illustrations

| 1.1 | Architecture fédérée                                                       | 5  |

|-----|----------------------------------------------------------------------------|----|

| 1.2 | Architecture intégrée, dite "IMA"                                          | 6  |

| 1.3 | Architecture logique d'un réseau avionique                                 | 7  |

| 1.4 | Description d'un calculateur au sein d'une architecture IMA                | 8  |

| 1.5 | Exemple d'un schéma d'ordonnancement fixe MAF                              | 10 |

| 1.6 | Acteurs de la conception d'un calculateur avionique                        | 10 |

| 2.1 | Cycle de développement d'un système, dit "cycle en V"                      | 19 |

| 2.2 | Niveaux d'abstractions adressés par les méthodes de modélisation ac-       |    |

|     | tuelles                                                                    | 22 |

| 2.3 | Exemple de réponse à un stimuli pour différents niveaux d'abstraction .    | 24 |

| 2.4 | Décomposition d'une application à différents niveaux d'abstraction         | 26 |

| 2.5 | Relation entre les niveaux de modélisation et les blocs applicatifs        | 27 |

| 3.1 | Aperçu des langages de modélisation de systèmes embarqués                  | 37 |

| 3.2 | Processus de modélisation mixte                                            | 42 |

| 3.3 | Architecture d'un système avionique décrite par le standard ARINC653       | 44 |

| 3.4 | Exemple de modélisation architecturale à l'aide des composants AADL        | 47 |

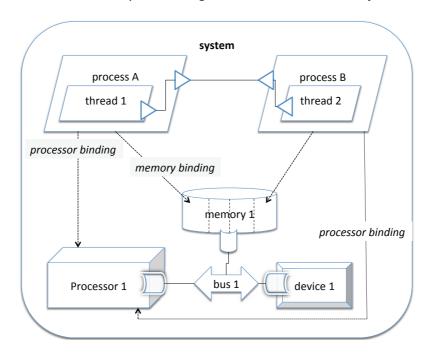

| 3.5 | Structure d'un système modélisé en SystemC                                 | 50 |

| 3.6 | Traitement d'une trame TLM                                                 | 53 |

| 4.1 | Méthode de modélisation : vue générale                                     | 62 |

| 4.2 | Génération d'une séquence de stimuli à partir d'un bloc algorithmique .    | 65 |

| 4.3 | Elaboration d'un scénario de simulation                                    | 66 |

| 4.4 | Modèle architectural d'une plate-forme                                     | 69 |

| 4.5 | Génération d'un modèle comportemental de composant matériel                | 72 |

| 4.6 | Exemple de représentation comportementale d'un service : get partition     |    |

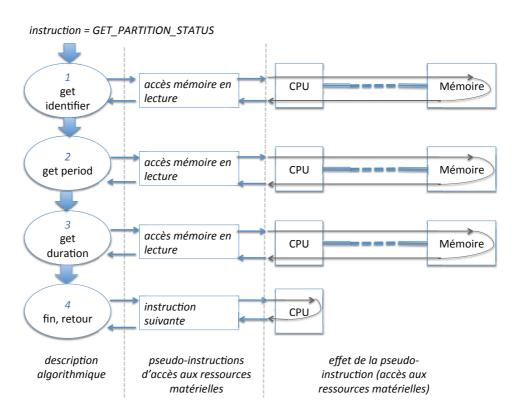

|     | status                                                                     | 73 |

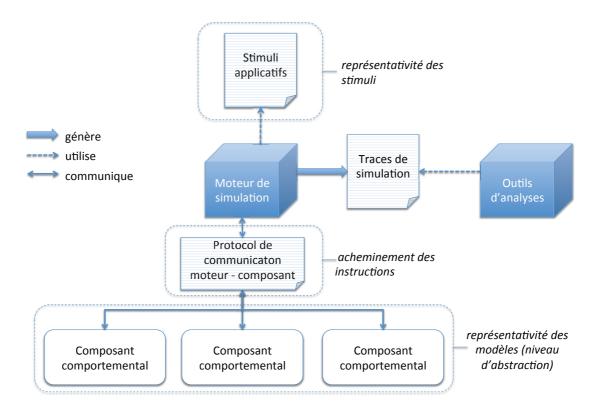

| 4.7 | Phase de simulation de la plate-forme matérielle et système d'exploitation | 75 |

| 5.1  | Modélisation du partitionnement temporel en AADL                          | 82  |

|------|---------------------------------------------------------------------------|-----|

| 5.2  | Modélisation du partitionnement spatial en AADL                           | 83  |

| 5.3  | Exemple d'ordonnancement de type ARINC-653                                | 84  |

| 5.4  | Exemple d'automate comportemental                                         | 88  |

| 5.5  | Processus de sélection de l'automate comportemental                       | 89  |

| 5.6  | Configuration d'un composant SystemC au sein de notre méthode             | 90  |

| 5.7  | Traitement des communications par le couple container-composant           | 97  |

| 5.8  | Processus de transformation du modèle architectural AADL vers le ni-      |     |

|      | veau comportemental SystemC                                               | 99  |

| 6.1  | Méthode de génération de stimuli par patrons de génération                | 105 |

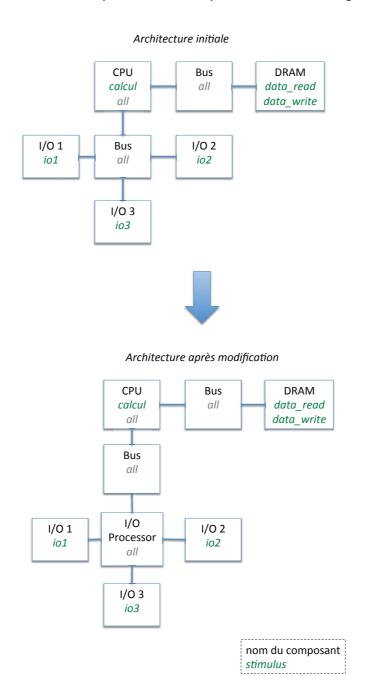

| 6.2  | Modification de l'architecture sans modification du jeu de stimuli        | 106 |

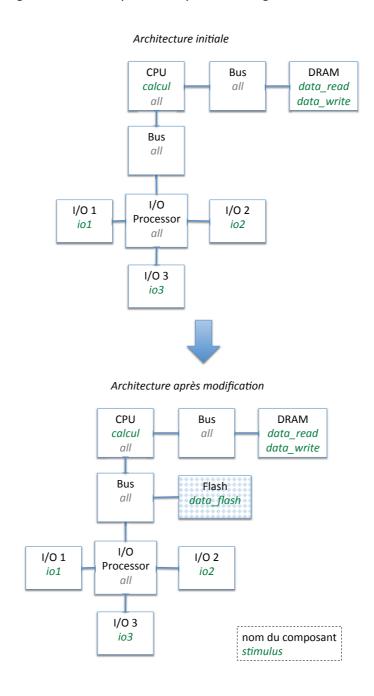

| 6.3  | Modification de l'architecture avec modification du jeu de stimuli        | 107 |

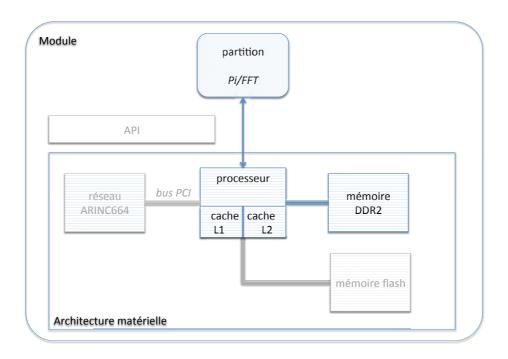

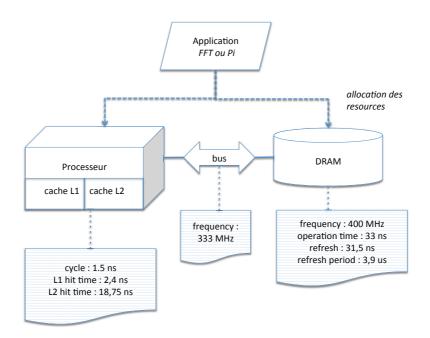

| 7.1  | Architecture du coeur du calculateur avec partition applicative           | 113 |

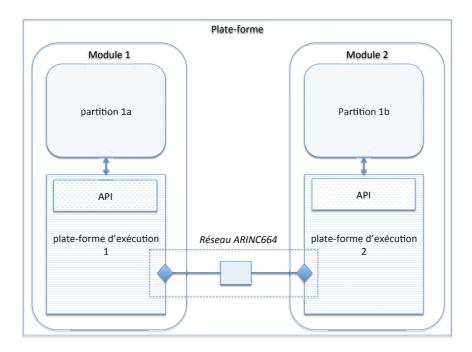

| 7.2  | Architecture de la plate-forme de test                                    | 114 |

| 7.3  | Représentation architecturale du calculateur de test                      | 117 |

| 7.4  | Exemple de caractérisation de l'automate comportemental SystemC de        |     |

|      | mémoire à partir du modèle AADL                                           | 119 |

| 7.5  | Acheminement d'un stimulus vers le composant cible                        | 120 |

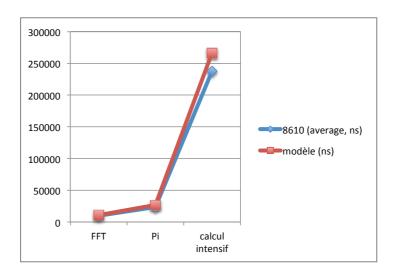

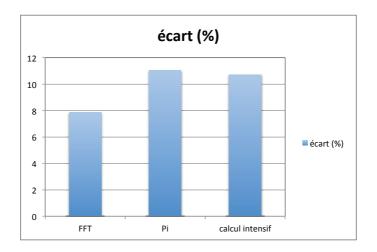

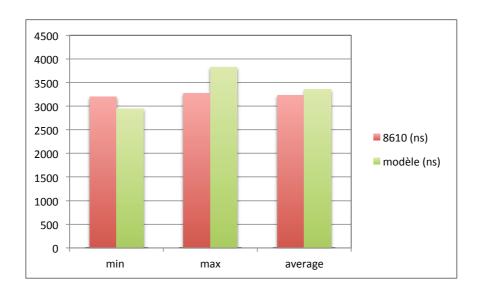

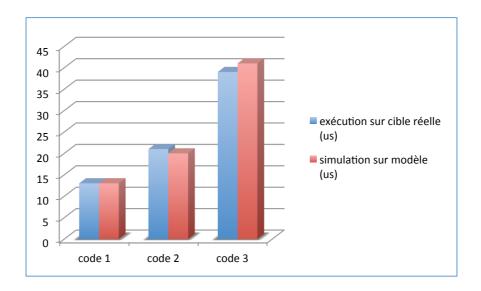

| 7.6  | Comparaison des temps d'exécution des trois applications                  | 121 |

| 7.7  | Représentation de l'écart moyen entre l'exécution réelle et la simulation |     |

|      | sur modèle des trois applications tests                                   | 121 |

| 7.8  | Comparaison des temps d'exécution minimum, moyen et maximum pour          |     |

|      | l'application calcul de Pi                                                | 122 |

| 7.9  | Architecture simplifiée de la plate-forme de test                         | 123 |

| 7.10 | Représentation du modèle architectural AADL du calculateur de test au     |     |

|      | sein de la plate-forme                                                    | 126 |

| 7.11 | Schéma du modèle comportemental du calculateur de test généré en          |     |

|      | SystemC                                                                   | 128 |

| 7.12 | Comparaison entre les temps d'exécution réels et simulés pour les dif-    |     |

|      | férents codes exécutés                                                    | 129 |

| 7.13 | temps de simulation des différents codes exécutés                         | 129 |

| 7.14 | Comparaison entre les temps d'exécution réels et simulés pour les dif-    |     |

|      | férents codes exécutés                                                    | 130 |

| 7.15 | Comparaison entre les temps d'exécution réels et simulés pour les dif-    |     |

|      | férents codes exécutés                                                    | 131 |

# Première partie Introduction Générale

# **Chapitre 1**

# Introduction

#### SOMMAIRE

| 1.1 | CONT  | EXTE AVIONIQUE                                         | 4  |

|-----|-------|--------------------------------------------------------|----|

|     | 1.1.1 | Application avionique                                  | 4  |

|     | 1.1.2 | Architecture des systèmes avioniques                   | 5  |

| 1.2 | PROB  | LÉMATIQUE GÉNÉRALE                                     | 11 |

|     | 1.2.1 | Une nouvelle architecture avionique                    | 11 |

|     | 1.2.2 | Adapter les méthodes de conception d'une plate-forme . | 11 |

| 1.3 | OBJE  | CTIFS ET APPROCHE                                      | 12 |

|     | 1.3.1 | Objectif                                               | 12 |

|     | 1.3.2 | Approche                                               | 12 |

| 1.4 | PLAN  | DU MÉMOIRE                                             | 13 |

#### 1.1 Contexte avionique

Suivant la loi de Moore, la miniaturisation des composants électroniques a conduit à une augmentation du nombre de composants intégrés au sein d'une puce, augmentant par là ses performances. Le domaine avionique, qui constitue notre cadre de recherche, a été confronté comme tous les domaines industriels à la nécessité d'augmenter la puissance de calcul de ses systèmes, afin de pouvoir traiter un plus grand nombre d'applications. Toutefois, l'intégration de nouveaux composants ou nouvelles technologies ne peut se faire qu'en adaptant ceux-ci aux contraintes spécifiques du domaine, notamment les contraintes de sécurité et de consommation énergétique.

Plate-forme avionique: nos travaux portent sur les systèmes que l'on appelle plate-forme avionique. Il s'agit d'un système embarqué temps réel critique, composé de plusieurs calculateurs chargés d'exécuter les fonctions avioniques qui permettent le bon déroulement du vol. Comme le précise [Brunette et al., 2005], ces calculateurs sont eux-mêmes des sous-systèmes avioniques, composés d'éléments matériels, d'un système d'exploitation et hébergeant une ou plusieurs applications. En tant que système embarqué, la plate-forme doit pouvoir fonctionner avec des contraintes de ressources limitées, comme un espace mémoire limité ou encore une consommation énergétique autorisée plafonnée. La notion de temps réel implique que le système doit exécuter ses fonctions dans le respect de contraintes temporelles (deadlines), au risque de défaillances graves. Enfin, l'aspect critique induit que le non respect de ces contraintes temporelles peut avoir des conséquences dramatiques allant jusqu'au crash de l'avion et la perte de vies humaines.

#### 1.1.1 Application avionique

Au niveau logiciel, le développement d'une application avionique se fait suivant le respect de la norme DO-178B, "Règlementation pour le développement de logiciels dans le secteur aéronautique" [RTCA, 1992]. Dans l'optique de la certification, chaque application doit, en plus de fournir certains documents de conception, être conforme à certains objectifs de tests et de couverture de tests. Il existe plusieurs niveaux de criticité au sein de la DO-178B, appelés niveaux DAL (Design Assurance Level), traduisant les conséquences d'une erreur dans le fonctionnement d'une application :

- Niveau DAL A : conséquences catastrophiques ;

- Niveau DAL B : conséquences dangereuses ;

- Niveau DAL C : conséquences majeures ;

- Niveau DAL D : conséquences mineures ;

- Niveau DAL E : sans effet sur la sécurité.

A titre d'exemple, une application chargée du contrôle des commandes de vol sera d'un niveau DAL A, tandis que les applications de gestion des services de détente des passagers (projection de films, etc.) seront DAL E. Ainsi, les objectifs de tests et de couverture de tests sont différents suivant le niveau DAL de l'application. Au niveau le plus élevé (niveau A), la couverture de code par les jeux de tests doit être complète, c'est-à-dire qu'elle doit couvrir toutes les conditions d'exécution et vérifier que le comportement dans telle condition est conforme au scénario prévu.

#### 1.1.2 Architecture des systèmes avioniques

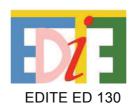

**Architecture fédérée**: auparavant, l'exécution des applications avioniques se faisait au travers d'une architecture dite fédérée. Comme le montre la figure 1.1, chaque calculateur a la charge d'exécuter une unique application. De plus, les communications entre applications de chaque calculateur se font via un canal dédié. Cette architecture implique que chaque calculateur est conçu et optimisé pour l'application qu'il doit exécuter, de même que les interfaces et liens de communications doivent être adaptés aux besoins des échanges à effectuer.

FIGURE 1.1 – Architecture fédérée

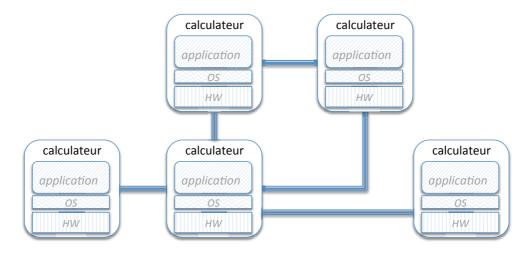

**Architecture intégrée**: lors de la dernière décennie, une nouvelle architecture a fait son apparition que l'on peut voir sur la figure 1.2. Cette architecture suit un nouveau principe dit d'architecture intégrée ou IMA (Integrated Modular Avionics). Les enjeux de cette nouvelle architecture sont de concevoir des calculateurs plus génériques, configurables, et pouvant exécuter plusieurs applications dont le niveau DAL est différent.

L'IMA a pour but de réduire l'empreinte environnemental de la plate-forme : moins de calculateurs implique une consommation d'énergie et un poids réduits, et moins d'espace occupé dans l'appareil [Li and Xiong, 2009]. Un autre aspect qui accompagne l'IMA concerne les communications entre les calculateurs. Auparavant entièrement dédiées, certaines communications se font désormais au travers d'un réseau standar-disé, l'ARINC-664, que présentent [Alena et al., 2006] et [Alena et al., 2007].

FIGURE 1.2 – Architecture intégrée, dite "IMA"

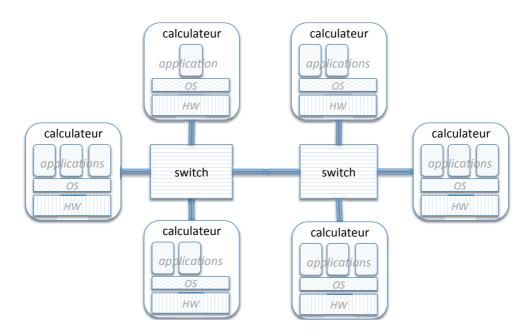

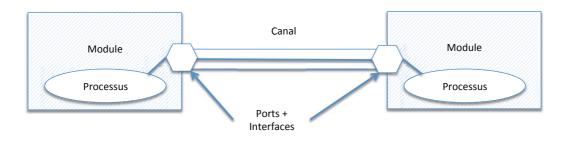

ARINC-664 : réseau avionique : l'ARINC-664, via le standard [Aeronautical-Radio-Inc, 2002c] définit un réseau déterministe basé sur Ethernet (norme 802.3). Comme le précise la partie 2 du standard [Aeronautical-Radio-Inc, 2002b], il assure la bonne transmission des données d'un calculateur à l'autre dans le respect de contraintes temporelles. Le fait de regrouper la majeure partie des communications au sein de ce réseau autorise là aussi une réduction de l'espace occupé, et sa réutilisation dans différentes architectures.

Concernant la description physique du réseau, celui-ci est composé de terminaux et de switchs. Les terminaux communiquent directement avec le calculateur et envoient les données sur le réseau. Les switchs sont chargés de router les messages vers le bon terminal. Concernant la partie logique, des "Virtual Links" (VL), ou chemins logiques, sont définis lors de la configuration du réseau. Ils représentent les différentes routes utilisées pour faire transiter les données d'un terminal à un autre. [Charara, 2007] nous donne plusieurs exemples de configurations d'un réseau ARINC664. La partie 1 du standard, [Aeronautical-Radio-Inc, 2002a], définit que chaque chemin logique reçoit une priorité et une bande passante, permettant d'acheminer les données en un temps maximum borné et connu. Le schéma 1.3 nous offre une vue logique du réseau, représenté par les chemins de communications autorisés entre les différents calculateurs.

FIGURE 1.3 – Architecture logique d'un réseau avionique

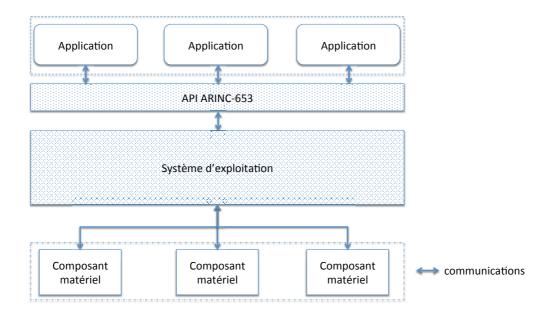

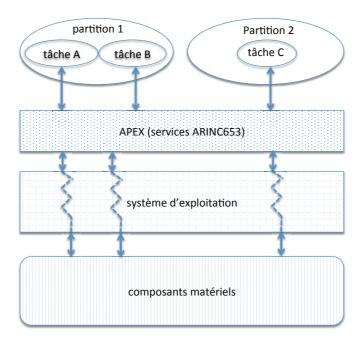

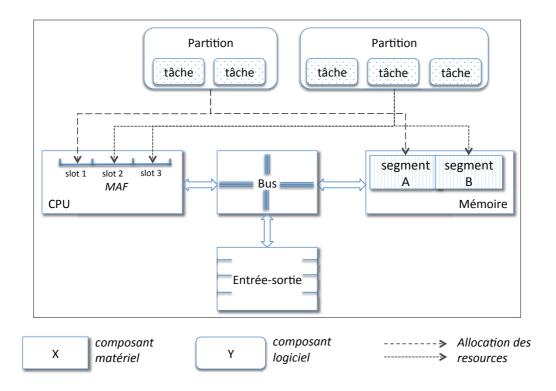

ARINC-653 : interface de programmation standard pour architecture intégrée : le principe d'architecture intégrée permet d'assurer une indépendance entre le développement des applications et le développement de la plate-forme d'exécution (système d'exploitation et architecture matérielle). En effet, une application avionique comporte deux ensembles d'instructions : les instructions de calcul et les appels aux services du système d'exploitation. Ce dernier offre un ensemble de services standar-disés par le standard ARINC-653 [Aeronautical-Radio-Inc, 2006], et permet, comme nous le voyons sur la figure 1.4, la séparation des applications vis-à-vis de la plate-forme d'exécution sous-jacente.

FIGURE 1.4 – Description d'un calculateur au sein d'une architecture IMA

Le standard ARINC-653 [Aeronautical-Radio-Inc, 1997] permet de faire cohabiter les différentes applications d'un même calculateur tout en respectant les principes de sûreté. Car si l'IMA permet de réduire le nombre de calculateurs en regroupant plusieurs applications sur un nombre réduit d'entre eux, cela ne doit pas se faire au détriment de la performances ni de la sûreté. Une application doit avoir accès aux ressources matérielles suffisamment souvent, et ce malgré la "concurrence" des autres applications sur le même calculateur. De même, une erreur lors de l'exécution de l'une de ces applications ne doit pas avoir de conséquences sur les autres applications hébergées sur le même calculateur. Afin de respecter ces exigences de sûreté, le standard ARINC-653 définit le principe de partitionnement spatial et temporel. Chaque application avionique est découpée en une ou plusieurs partitions, "boites" logicielles

isolées les unes des autres. Cette isolation permet de contenir une erreur d'exécution au sein d'une partition, sans contagion aux autres applications. Ainsi pour résumer, nous avons deux types de partitionnement :

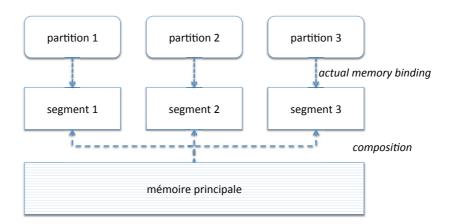

- Le partitionnement spatial : chaque partition logicielle possède son propre espace mémoire dans lequel elle seule peut aller écrire ;

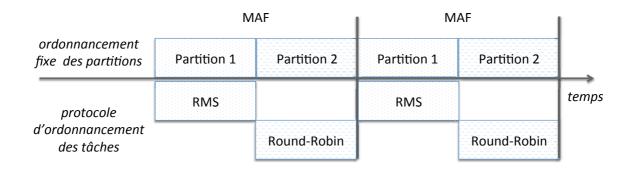

- Le partitionnement temporel : chaque partition s'exécute au moins une fois pendant la MAF. Pendant cette période, la partition a accès à l'ensemble des ressources matérielles auxquelles elle est "abonnée" (processeur, zone mémoire dédiée et les entrées-sorties auxquelles elle a l'autorisation d'accéder).

Les services ARINC653 peuvent être classés en six catégories principales :

- Gestion des partitions : fixer / récupérer le mode de la partition (IDLE, COLD, NORMAL, etc.);

- Gestion des processus : récupérer les valeurs des propriétés (identifiant, priorité), suspendre le processus, le stopper, le relancer, etc.;

- Gestion du temps : mettre en attente un processus, récupérer le temps absolu, etc.;

- Gestion des communications inter-partitions : gestion des queues de messages inter-partition (queuing), gestion des tampons de messages inter-partition (sampling);

- Gestion des communications intra-partitions : gestion des queues de messages intra-partition (buffer), gestion des tampons de messages intra-partition (blackboard), gestion des sémaphores et évènements;

- Gestion des pannes.

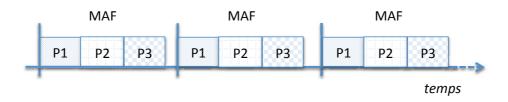

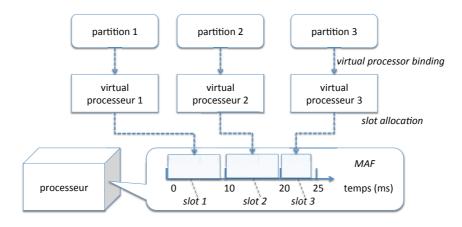

L'ordonnancement des partitions se fait suivant un schéma d'exécution fixe afin d'assurer le déterminisme lors de l'exécution. Ce schéma d'exécution est nommé MAF (Major Frame) dans le standard ARINC-653, dont nous donnons un exemple dans la figure 1.5. La MAF assure l'accès à l'ensemble des ressources matérielles à une partition pendant au moins une fenêtre temporelle. Au sein de chaque partition s'exécutent des processus, équivalents à des tâches logicielles, qui sont ordonnancées suivant un schéma adapté aux tâches périodiques comme RMS (Rate Monotonic Scheduling) [Liu and Layland, ].

FIGURE 1.5 – Exemple d'un schéma d'ordonnancement fixe MAF

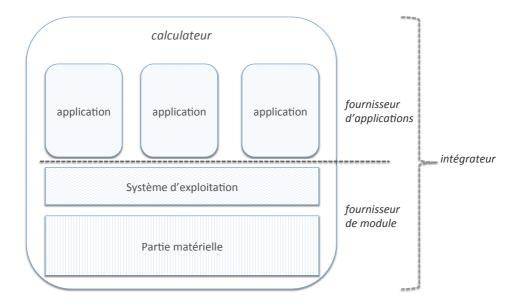

Nous avons vu que l'IMA permet de dissocier le développement des applications du développement du module (système d'exploitation et partie matérielle). Cette indépendance a renforcé la spécialisation des différents acteurs participant à la conception d'un calculateur. Nous distinguons trois catégories d'acteurs, comme le résume le schéma 1.6. Les applications sont généralement développées par les fournisseurs d'applications, ou développeurs d'applications; la plate-forme matérielle (composants matériels et système d'exploitation) est développée par le fournisseur de module ou plate-formiste, tandis que l'intégration se fait par l'intégrateur, généralement l'avionneur (Aribus, Boeing, etc.). Nos travaux s'inscrivent dans le domaine du fournisseur de module ce qui signifie que nous avons accès aux informations concernant le module (système d'exploitation et composants matériels), mais pas forcément aux applications qui seront exécutées. Cette précision est utile car elle est une composante de notre problématique qui va être décrite dans le chapitre 2.

FIGURE 1.6 – Acteurs de la conception d'un calculateur avionique

#### 1.2 Problématique générale

#### 1.2.1 Une nouvelle architecture avionique

Nous venons de voir que le principe IMA permet de développer une plate-forme avionique à l'empreinte réduite (en terme de consommation d'énergie, d'espace occupé et de poids), tout en conservant les performances et les propriétés de sûreté en place dans les architectures fédérées. Toutefois, le fait de regrouper plusieurs applications de niveau DAL différents sur un même calculateur a entrainé une augmentation de la complexité de développement par rapport aux architectures fédérées : dans ces dernières, chaque calculateur exécute une seule application, la non propagation d'une faute est ainsi en grande partie assurée par l'architecture elle-même de par l'absence d'autres applications sur le même hôte. Dans le cas de l'IMA, la mise en place des mécanismes spécifiques a été nécessaire afin d'assurer le respect de ce type de contrainte.

#### 1.2.2 Adapter les méthodes de conception d'une plate-forme

Pour faire face à cette augmentation de la complexité et tenir les délais de livraison, il a été nécessaire d'adapter les méthodes de conception actuelles, voire en développer de nouvelles [Ott, 2007]. Les phases de conception détaillée et d'implémentation se sont adaptées aux nouvelles contraintes induites par l'IMA, et n'offrent désormais que peu de marge de manoeuvre pour tenter de réduire les temps de développement. Les recherches en vue d'optimiser le processus de développement se sont donc tournées vers la phase amont du processus, constituée par les phases de spécification et pré-dimensionnement de la plate-forme. Dans ce domaine, de nouvelles méthodes liées à la modélisation de plate-forme ont vu le jour. Toutefois ces méthodes, qui permettent de modéliser des systèmes temps-réels, ne sont pas forcément adaptées aux spécificités de l'avionique (partitionnement, réseau commun déterministe, etc.), et ne sont souvent pas suffisamment robustes pour être utilisées en phase amont du processus, notamment au niveau de la modélisation de l'applicatif en avance de phase. Nous verrons dans le chapitre 2 quelles sont les spécificités d'une modélisation en avance de phase, et les points techniques à résoudre. Dans le chapitre 3 nous verrons plusieurs méthodes de modélisation de systèmes temps-réel et leurs limitations pour l'application au domaine avionique en avance de phase.

#### 1.3 Objectifs et approche

#### 1.3.1 Objectif

Notre objectif principal est d'aider au dimensionnement d'une architecture matérielle avionique en fonction d'applications qu'elle aura à exécuter. Plus spécifiquement, l'objectif est de fournir une méthode de modélisation offrant la possibilité d'anticiper les performances, notamment temporelles, de la plate-forme, afin de pré-valider l'architecture au regard des exigences qu'elle doit respecter. Ce modèle pourra être amené à servir de base de travail lors des discussions autour de la plate-forme entre le plate-formiste et l'avionneur. Pour répondre à cela, la modélisation doit prendre en compte les spécificités des architectures avioniques actuelles, et doit être capable de fournir des résultats suffisamment représentatifs en s'adaptant aux contraintes de la modélisation en toute phase amont du processus de développement.

#### 1.3.2 Approche

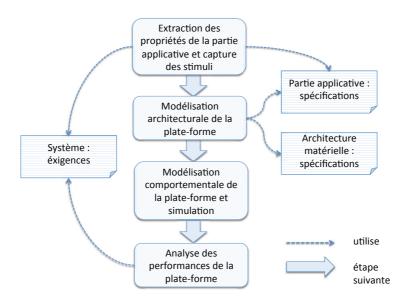

Nous proposons une méthode de modélisation de la plate-forme avionique en plusieurs étapes [Lafaye et al., 2010a]. Une première étape d'extraction des caractéristiques dimensionnantes de la partie applicative en avance de phase, deux étapes de modélisation à différents niveaux d'abstraction de la plate-forme prenant en compte les spécificités avioniques, et enfin une étape d'analyse des performances de la plate-forme au regard des exigences. Cette approche s'appuie sur des méthodes existantes de modélisation architecturale, et vient enrichir celles-ci afin de descendre en abstraction et fournir un modèle comportemental de la plate-forme d'exécution (partie matérielle et système d'exploitation). Ce modèle comportemental autorise l'exécution de stimuli applicatifs et l'analyse dynamique de la réponse de la plate-forme à ces stimuli, via l'étude de la consommation de ses ressources. L'analyse des temps d'exécution suite à la réception d'un stimulus, ou encore l'analyse de la consommation d'énergie de la plate-forme sur une période donnée, sont quelques-unes des analyses que l'on souhaite pouvoir mener. Ces analyses sont ensuite mise en regard des spécifications afin de pré-valider ou non l'architecture proposée pour la plate-forme.

#### 1.4 Plan du mémoire

Ce mémoire s'organise autour de quatre parties principales, dans lesquelles nous allons détailler notre approche, les choix effectués, son implémentation et la validation expérimentale. La partie II définit le cadre de nos travaux. Nous détaillerons dans le chapitre 2 les problèmes spécifiques liés à la modélisation d'un système avionique en avance de phase, en posant les objectifs à atteindre par notre approche. Dans le chapitre 3 nous présenterons les méthodes de modélisation de systèmes temps-réels, et plus spécifiquement celles touchant au domaine avionique. Nous y verrons les atouts et manques de chacune d'entre elles .

La partie III présentera notre approche en elle-même. Dans le chapitre 4, nous verrons l'approche proposée afin de répondre aux objectifs posés dans le chapitre précédent, ainsi que les points techniques auxquels il a fallu répondre. Nous verrons comment chaque partie du processus répond à l'un de ces points. Les chapitres 5 6 détailleront nos contributions qui mettent en oeuvre notre approche, ainsi que les choix techniques et solutions adoptés.

La partie IV via le chapitre 7 présentera les expérimentations effectuées afin de valider notre approche sur un cas d'étude avionique réel fourni par notre partenaire Thales Avionics, et mettra l'accent sur la mise en oeuvre des contributions. Enfin, conclurons dans le chapitre 8 de la partie V.

# Deuxième partie Enjeux Industriels

# **Chapitre 2**

# Problématique industrielle

#### **SOMMAIRE**

| 2.1 | INTRODUCTION                                                       |  |

|-----|--------------------------------------------------------------------|--|

| 2.2 | EXPLORATION DES PERFORMANCES EN AVANCE DE PHASE 19                 |  |

| 2.3 | MODÉLISATION DE LA PLATE-FORME AVIONIQUE 20                        |  |

|     | 2.3.1 Niveaux d'abstraction pour la modélisation de plate-forme 20 |  |

|     | 2.3.2 Modélisation de systèmes avioniques                          |  |

|     | 2.3.3 Résumé                                                       |  |

| 2.4 | MODÉLISATION D'UNE APPLICATION                                     |  |

|     | 2.4.1 Niveau d'abstraction pour la modélisation                    |  |

|     | 2.4.2 Organisation des stimuli                                     |  |

| 2.5 | EVALUATION DES PERFORMANCES DE LA PLATE-FORME EN AVANCE            |  |

|     | DE PHASE                                                           |  |

| 2.6 | <b>SYNTHÈSE</b>                                                    |  |

#### 2.1 Introduction

Nous venons de voir que la conception des plates-formes avioniques est une opération dont la complexité s'est accrue ces dernières années, du fait de l'IMA. Nous avons vu dans le chapitre 1 que les deux objectifs principaux de ce type d'architecture peuvent se résumer à :

- Permettre la réduction du nombre de calculateurs au sein d'une plate-forme, afin de réduire l'empreinte de cette dernière (diminution de la consommation, diminution de l'espace occupé et diminution du poids de la plate-forme);

- Faciliter la réutilisation des calculateurs lors de la conception de nouvelles platesformes, en apportant plus de généricité.

Toutefois, ce changement d'architecture a engendré des changements dans les règles de conception. Par exemple, dans les architectures fédérées, le fait de n'autoriser qu'une application par calculateur permet, en cas de défaillance, de limiter relativement facilement l'impact de cette défaillance sur les autres applications hébergées sur les autres calculateurs. Sur les architectures IMA, où un calculateur peut héberger plusieurs applications, il est nécessaire de garantir que chaque application n'aura que des interactions très limitées avec les autres applications afin d'éviter la propagation d'erreurs. Le respect de ce type de contraintes dans les nouvelles architectures avioniques a engendré le développement de nouveaux mécanismes qui ont un impact sur la complexité du processus de conception et de vérification.

Parallèlement, les avionneurs demandent à pouvoir disposer des plates-formes de plus en plus tôt. Les plates-formistes ont donc cherché à mieux orienter leur processus de développement, afin de détecter au plus tôt certaines erreurs de conception et limiter leur impact sur la suite du développement. Notamment, afin de dimensionner au mieux la plate-forme en fonction des exigences, les plates-formistes se sont tournés vers la modélisation de plate-forme en avance de phase avec pour but d'offrir une meilleure représentation des spécifications de la plate-forme, et mieux rendre compte des choix architecturaux.

#### 2.2 Exploration des performances en avance de phase

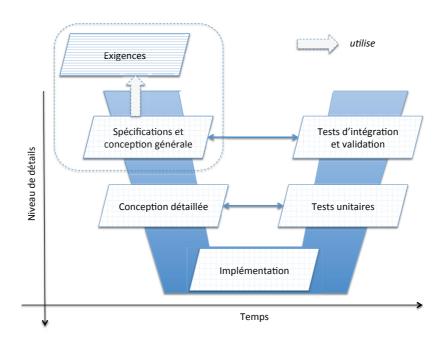

Cette opération consiste en une exploration des performances de la plate-forme en phase amont du processus de conception. Les performances sont généralement des performances temporelles, mais peuvent également être d'un autre type comme la consommation d'énergie. Si l'on reprend le cycle de développement classique en V de la figure 2.1, l'avance de phase correspond à la phase de spécifications et de conception générale. A ce niveau là, l'architecture du système n'est pas encore concrète, mais décrite par un ensemble de documents qui définissent les spécifications matérielles et logicielles que doivent respecter la plate-forme.

FIGURE 2.1 – Cycle de développement d'un système, dit "cycle en V"

Dans l'idéal, l'exploration des performances en avance de phase permet d'étudier la réponse de la plate-forme à l'exécution d'une ou plusieurs applications. Pour cela sont analysés i) l'utilisation des ressources matérielles de la plate-forme, ii) les limites d'utilisation de la plate-forme. Ces analyses permettent ensuite de vérifier le respect des exigences. Toutefois, à ce niveau très amont du processus de conception, l'ensemble des informations concernant la plate-forme n'est pas toujours fourni ou sont limitées. Nous avons vu par exemple dans le chapitre 1 que le code source des applications n'est que rarement accessible. Ceci exclut l'utilisation de méthodes de virtualisation pour la prédiction de performances, car elles nécessitent le binaire

d'une application pour l'exécuter sur un modèle détaillé d'architecture.

D'autre part, l'opération de modélisation et d'exploration des performances d'une plateforme en avance de phase doit être relativement rapide. L'objectif étant de mieux orienter le processus de développement pour limiter la perte de temps causée par des problèmes de dimensionnement d'architecture, il est impératif de ne pas perdre plus de temps lors de la modélisation que l'on en gagne sur la suite du processus. Ainsi, les méthodes de modélisation fine de plate-forme basées sur des modèles très détaillés de type VHDL ou Verilog, sont eux aussi exclus.

Depuis quelques années, des méthodes de modélisation en avance de phase de systèmes embarqués ont fait leur apparition afin d'offrir un modèle de plate-forme accompagné d'outils d'analyses. Ces méthodes ont été enrichies afin de prendre en compte les aspects temps-réels. Par exemple, la méthode de modélisation décrite dans [Dissaux and Singhoff, 2008] permet de modéliser un système temps-réel, et d'effectuer de premières analyses sur le dimensionnement des ressources telle que l'allocation de mémoire. Toutefois, dès lors que l'on cherche à modéliser en avance de phase des systèmes plus spécifiques comme les systèmes avioniques, les méthodes actuelles souffrent de manques i) au niveau de la modélisation des différentes parties du système, du fait du manque d'informations, ii) de la prise en compte des spécificités du domaine avionique. Dans la suite, nous allons détailler les trois étapes clés de l'exploration en avance de phase des performances d'une plate-forme avionique. Nous donnerons les contraintes liées au domaine avionique et les différents problèmes auxquels se heurtent les méthodes actuelles.

#### 2.3 Modélisation de la plate-forme avionique

#### 2.3.1 Niveaux d'abstraction pour la modélisation de plate-forme

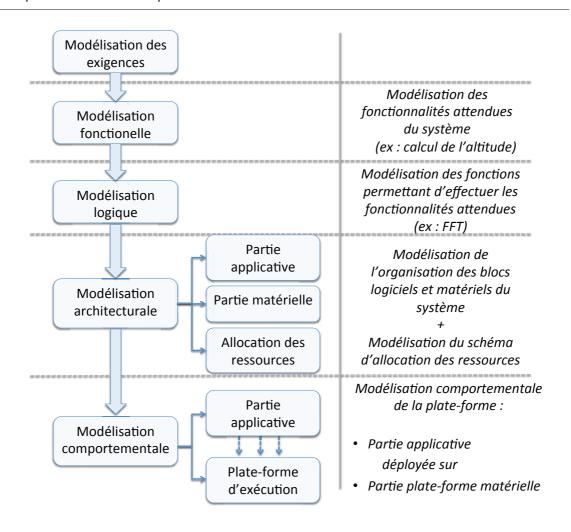

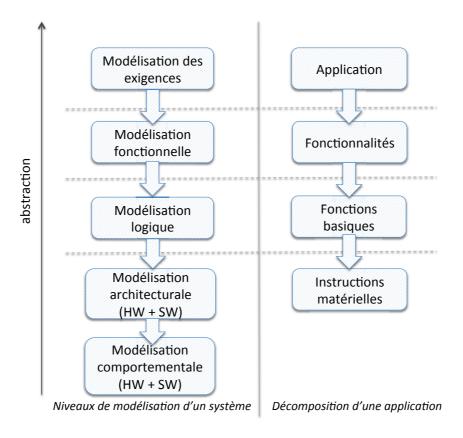

Les méthodes de modélisation de systèmes ont fait leur apparition dans le but, dans un premier temps, de rendre plus intelligible par les utilisateurs les spécifications logicielles et matérielles d'un système en les traduisant en un modèle architectural. Ces méthodes se sont peu à peu enrichies, offrant de plus en plus de possibilités de modélisation, pour finalement offrir de modéliser la plate-forme à plusieurs niveaux d'abstraction. Nous distinguons principalement cinq niveaux de modélisation :

- Niveau modélisation des exigences, où ces dernières sont exprimées de manière à pouvoir y associer les futures fonctionnalités logicielles ou matérielles;

- Niveau modélisation fonctionnelle, où l'on décrit les fonctionnalités que devra remplir le système (calcul de trajectoire, calcul d'altitude, gestion de la lumière du cockpit etc.);

- Niveau modélisation logique, où les fonctionnalités définies ci-dessus sont découpées en une ou plusieurs fonctions, au sens informatique;

- Niveau modélisation architecturale, où le système est modélisé sous forme de composants logiciels déployés sur des composants matériels;

- Niveau modélisation comportementale, où le système est modélisé sous forme de composants comportementaux plus ou moins détaillés réagissant à des stimuli applicatifs.

Comme nous le voyons sur le schéma 2.2, seuls les deux derniers niveaux de modélisation, architecturale et comportementale, sont représentatifs d'une plate-forme. C'est-à-dire que ces niveaux permettent de distinguer les parties logicielles et matérielles, contrairement aux deux niveaux d'abstractions qui viennent juste avant.

Ainsi, dans l'optique de mener des analyses de dimensionnement et de respect des exigences système, seuls les niveaux de modélisation architecturale et comportementale nous intéressent. Ces analyses passent par des études ciblées comme l'ordonnançabilité des partitions logicielles par l'ordonnanceur (respect des deadlines), ou l'exploration de l'utilisation des ressources matérielles (utilisation mémoire, ou consommation énergétique du CPU entre autres exemples). Toutefois, pour le domaine avionique, l'utilisation de méthodes de modélisation de plate-formes nécessite l'adaptation des méthodes de modélisation actuelles.

FIGURE 2.2 – Niveaux d'abstractions adressés par les méthodes de modélisation actuelles

## 2.3.2 Modélisation de systèmes avioniques

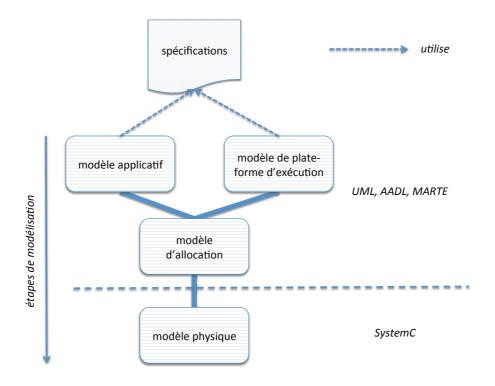

Si les méthodes existantes permettent de modéliser en avance de phase les systèmes à haut niveau d'abstraction, elles se limitent souvent à une description architecturale. Les méthodes offrant une modélisation comportementale en avance de phase du système restent marginales pour deux principales raisons. La première concerne les informations souvent limitées disponibles en avance de phase. Particulièrement, le code des applications n'est pas forcément accessible. En effet, le monde de l'avionique, nous l'avons vu dans le chapitre 1, se compose de plusieurs acteurs qui n'interagissent que ponctuellement, chacun développant de son côté une partie de la plate-forme. Les tests d'intégration et les analyses de dimensionnement se font par la

suite, lorsque la plate-forme matérielle est développée, c'est-à-dire en aval du processus de conception du système. Nous avons donc ici une première contrainte : le non accès au code source des applications.

La seconde raison freinant la modélisation en avance de phase d'une plate-forme tient au fait que le modèle doit pouvoir être élaboré rapidement. Or, contrairement à une description architecturale où les éléments de la plate-forme sont caractérisés par leurs principales propriétés, la description comportementale de tous ces éléments est une opération plus longue, car elle nécessite de définir en plus leur comportement. De plus, une description comportementale du système d'exploitation, nécessaire si l'on souhaite étudier en détails l'utilisation des ressources matérielles d'une plate-forme, est une opération encore plus longue et compliquée que pour les autres éléments de la plate-forme du fait des mécanismes mis en oeuvre.

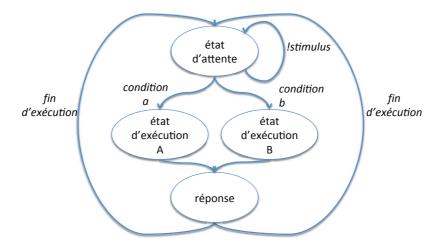

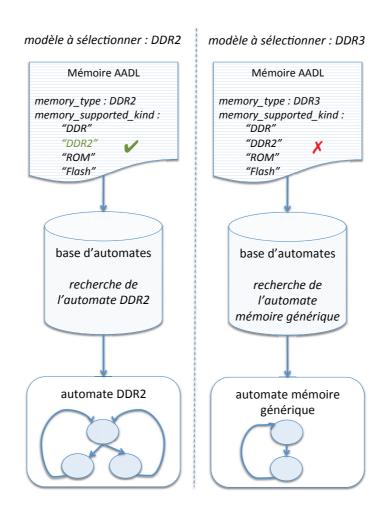

Or, si un modèle architectural permet d'effectuer des premières analyses de dimensionnement comme il est décrit dans [de Niz and Rajkumar, 2006] ou [Singhoff et al., 2004] par exemple, celui-ci ne permet pas de venir extraire les l'utilisation des ressources matérielles au cours du temps et suivant le contexte d'exécution. L'absence d'informations comportementales dans la description des composants du modèle empêche d'étudier la réponse d'un ou plusieurs composants à un ou plusieurs stimuli. L'exemple de la figure 2.3 montre qu'un modèle architectural de mémoire configuré par les latences d'accès en lecture et écriture rendra une réponse uniforme en cas de requête, tandis qu'un modèle comportemental de mémoire pourra faire intervenir des différences de latence pour un même stimuli, en fonction du contexte. Nous avons donc ici deux contraintes : temps de modélisation et exploration, et niveau de précision du modèle et des informations que l'on peut en retirer.

FIGURE 2.3 – Exemple de réponse à un stimuli pour différents niveaux d'abstraction

#### 2.3.3 Résumé

Nous avons vu qu'il est nécessaire de disposer d'un modèle plus fin que le modèle architectural si l'on veut explorer les performances d'une plate-forme et les comparer avec les exigences. Un modèle de type comportemental permet d'extraire la réponse de la plate-forme en réaction aux différents stimuli applicatifs qu'elle devra traiter, et ainsi autorise l'analyse de l'utilisation des ressources de la plate-forme. Toutefois, l'élaboration d'un modèle comportemental précis du système, à l'aide de langages tels VHDL par exemple, est une opération complexe et longue si l'on ne possède pas déjà tous les modèles comportementaux des éléments de la plate-forme. La méthode d'exploration des performances en avance de phase doit donc répondre aux deux critères identifiés suivants :

- Critère 1 : proposer une méthode de modélisation de la plate-forme malgré le manque d'informations disponibles, particulièrement l'absence du code source des applications;

- Critère 2 : proposer une méthode d'élaboration relativement rapide d'un modèle comportemental de la partie matérielle, qui vient affiner le modèle précédent, afin d'étudier dynamiquement la réponse de celle-ci aux stimuli applicatifs.

# 2.4 Modélisation d'une application

#### 2.4.1 Niveau d'abstraction pour la modélisation

L'objectif de cette étape est de modéliser une application avionique avec pour but d'en extraire ses principales caractéristiques et son comportement, pour ensuite élaborer un scénario de simulation pour le modèle de plate-forme. Nous l'avons vu à plusieurs reprises, les applications amenées à être exécutées par la future plate-forme ne sont ici pas toujours accessibles. Il n'est donc pas possible d'appliquer des méthodes de parcours de code afin d'en retirer leur comportement et les différents paramètres dimensionnants, tels que les appels aux fonctions de l'APEX, comme c'est le cas dans le projet [la Camara et al., 2007]. Or, si les informations extraites à ce stade ne sont pas suffisamment représentatives de l'application, les performances extraites par la suite seront trop imprécises. Il en va de même si l'écart entre le niveau de précision de ces informations et celui du modèle de la plate-forme d'exécution générée en aval du processus de modélisation est trop grand.

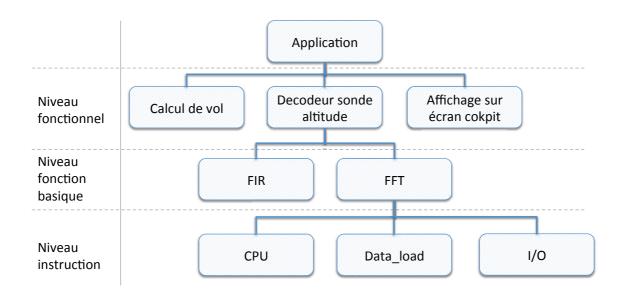

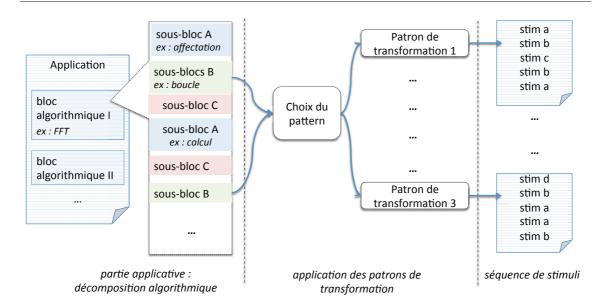

Afin de répondre à cette difficulté, il convient dans un premier temps de définir le niveau de granularité des stimuli que l'on souhaite générer. Ceux-ci sont à mettre en relation d'une part avec le modèle comportemental de la plate-forme, et d'autre part avec le niveau de granularité souhaité lors de l'analyse de performances, qui déterminera le niveau de modélisation de l'application. Le temps d'exécution du scénario de simulation est également un facteur à prendre en compte ; en effet, plus la granularité de la modélisation de la partie applicative est élevée (i.e. plus le nombre de stimuli généré dans le scénario est grand), plus l'exécution sera longue. La figure 2.4 nous montre à quels niveaux d'abstraction peut se décomposer une application.

FIGURE 2.4 – Décomposition d'une application à différents niveaux d'abstraction

Ces niveaux rappellent les niveaux de modélisation que l'on a exposé dans la section précédente. Depuis le niveau de l'application elle-même, celle-ci est affinée en blocs fonctionnels, représentant les fonctionnalités attendues de l'application. Vient ensuite le niveau blocs logiques ou fonctions de base, représentant les fonctions -au sens informatique/algorithmique- permettant la réalisation des fonctionnalités précédentes. Enfin, le niveau instructions de bases représente l'accès aux différentes ressources matérielles de la plate-forme.

Or, nous avons vu dans la section précédente que pour mener à bien l'analyse des performances depuis le modèle de plate-forme, ce dernier devait être de niveau comportemental afin de pouvoir étudier les accès et la consommation des ressources matérielles. Ainsi, si l'on se réfère au schéma 2.5, nous voyons que le niveau de granularité instruction correspond le mieux au niveau modélisation comportementale de la plate-forme matérielle.

FIGURE 2.5 – Relation entre les niveaux de modélisation et les blocs applicatifs

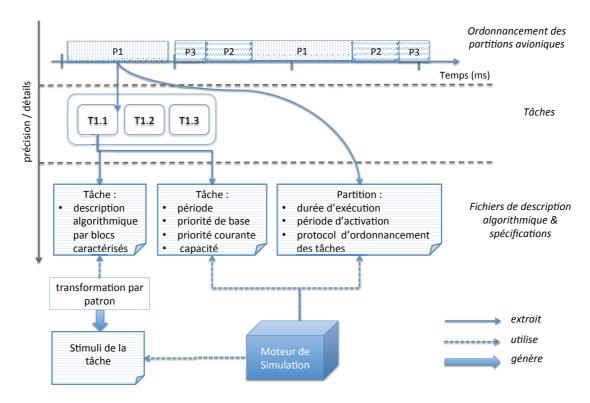

#### 2.4.2 Organisation des stimuli

La seconde partie de notre étape d'extraction des stimuli applicatifs concerne leur organisation en un scénario de simulation. L'exécution des partitions au sein d'un même calculateur étant effectuée suivant le principe d'isolation temporelle, via le schéma d'exécution fixe, la MAF, nous savons donc déjà comment seront organisées temporellement les partitions. Connaissant également le découpage de la partition en tâches, et le schéma d'ordonnancement associé, il est ainsi possible d'extraire un schéma d'exécution de ces tâches et du code applicatif associé. Les besoins pour la génération de ce scénario de simulation consistent en deux points : i) un ensemble de caractéristiques des tâches et ii) une description comportementale du code de cette tâche pour organiser les futures stimuli décrivant le comportement de la tâche (enchainement des séquences de calcul, d'appel services, etc.). Ces besoins nous ramènent au critère 1 identifié dans la section précédente : fournir une méthode de modélisation comportementale de toutes les parties de la plate-forme, dont la partie applicative à laquelle nous nous sommes particulièrement intéressés ici.

# 2.5 Evaluation des performances de la plate-forme en avance de phase

L'objectif de cette étape est double, puisqu'elle doit d'une part offrir certaines garanties quant à la représentativité des résultats obtenus, d'autre part établir si l'architecture proposée pour la plate-forme permet d'exécuter la partie applicative dans le respect des exigences fournies en entrée. Au début de ce chapitre nous avons vu que l'analyse des performances d'une plate-forme passe par l'analyse de l'utilisation de ses ressources. Dans notre cas, nous mettons l'accent sur l'utilisation des ressources matérielles de la plate-forme, afin d'être capable de déterminer la compatibilité entre la partie applicative et la plate-forme matérielle. Nous avons identifié précédemment que les composants de cette partie matérielle doivent être décrits avec leur partie comportementale, afin de pouvoir étudier la réponse d'un composant à un stimuli applicatif.

La validité d'une simulation est définie comme étant la représentativité du comportement du système et des résultats produits lors d'une simulation [Albert, 2009]. La représentativité de la simulation dépend ainsi en premier lieu de la méthode utilisée. S'appuyer sur un moteur de simulation existant et validé permet de s'assurer que l'exécution du scénario de simulation se fait sans erreurs. Outre la bonne exécution du scénario, il est nécessaire de s'assurer que les stimuli sont bien acheminés vers les composants cibles. D'autre part, le niveau de représentativité des résultats de simulation dépend du niveau d'abstraction du modèle de plate-forme, et du niveau de précision des stimuli. Une granularité faible, et donc un niveau d'abstraction élevé, peut entraîner des écarts relativement importants avec l'exécution des applications sur la plate-forme réelle. Enfin, une fois les performances extraites, il est nécessaire de mettre en regard celles-ci avec les exigences données en entrée afin de vérifier la compatibilité entre l'architecture de plate-forme proposée, ses performances, et ces exigences.

# 2.6 Synthèse

Nous avons vu que face à l'augmentation de la complexité dans la conception des plates-formes avioniques, l'exploration de leurs performances en avance de phase est un besoin croissant. Elle doit répondre aux critères identifiés dans ce chapitre :

- Critère 1 : l'approche doit fournir un modèle de la plate-forme décrivant les différentes parties du système : la partie applicative, la partie matérielle, le système d'exploitation et l'allocation des ressources. Particulièrement, elle doit fournir ou permettre de générer de manière relativement rapide un modèle comportemental de la partie matérielle et des services ARINC653 utilisés dans l'optique d'étudier la réponse de la plate-forme matérielle aux stimuli applicatifs (temps d'exécution);

- Critère 2 : l'approche doit offrir une méthode de modélisation comportementales de la partie applicative sans avoir accès au code source, et sans aller à l'encontre des contraintes de confidentialité. Elle doit également permettre d'extraire un ensemble de paramètres suffisamment représentatifs, afin de pouvoir générer un scénario de simulation du modèle comportemental précédent;

- Critère 3 : l'approche doit permettre d'exécuter ce scénario sur la plate-forme d'exécution, afin de déterminer la compatibilité entre ses performances et les exigences qu'elle doit respecter.

Dans la suite, nous allons détailler comment notre méthode répond à chacun des points ci-dessus, au travers de sa mise en oeuvre sur deux cas d'études que nous présenterons dans la partie 7.

# **Chapitre 3**

# Etat de l'Art

## SOMMAIRE

| 3.1 | INTRO | DUCTION                                              | 32 |

|-----|-------|------------------------------------------------------|----|

| 3.2 | LANG  | AGES DE MODÉLISATION                                 | 33 |

|     | 3.2.1 | Introduction                                         | 33 |

|     | 3.2.2 | Langages synchrones et méthodes formelles            | 33 |

|     | 3.2.3 | Langage de modélisation système                      | 34 |

|     | 3.2.4 | Langages de modélisation architecturale              | 34 |

|     | 3.2.5 | Langages de description matérielle                   | 36 |

|     | 3.2.6 | Résumé                                               | 36 |

| 3.3 | MÉTH  | ODES DE MODÉLISATION DE PLATES-FORMES AVIONIQUES     | 37 |

|     | 3.3.1 | Introduction                                         | 37 |

|     | 3.3.2 | Modélisation d'une plate-forme globale               | 38 |

|     |       | 3.3.2.1 Modélisation architecturale                  | 38 |

|     |       | 3.3.2.2 Modélisation physique                        | 41 |

|     |       | 3.3.2.3 Modélisation mixte                           | 41 |

|     | 3.3.3 | Modélisation du réseau avionique                     | 43 |

|     | 3.3.4 | Modélisation des services ARINC653 pour les systèmes |    |

|     |       | d'exploitation avioniques                            | 44 |

|     | 3.3.5 | Modélisation d'une application avionique             | 45 |

| 3.4 | LANG  | AGES ET MÉTHODE DE MODÉLISATION SÉLECTIONNÉS         | 46 |

|     | 3.4.1 | AADL                                                 | 47 |

|     |       | 3.4.1.1 Composants                                   | 47 |

|     |       | 3.4.1.2 Interfaces, connections et déploiement       | 48 |

|     |       | 3.4.1.3 Extensions et outils                         | 49 |

| 3.4.2    | SystemC |                      | 50 |

|----------|---------|----------------------|----|

|          | 3.4.2.1 | Structure du langage | 50 |

|          | 3.4.2.2 | Bibliothèque TLM     | 51 |

|          | 3.4.2.3 | Communications       | 52 |

|          | 3.4.2.4 | Outils               | 54 |

| 3.5 SYNT | HÈSE    |                      | 54 |

#### 3.1 Introduction

Contexte: un système embarqué ne se définit plus de nos jours comme un ensemble de composants, mais comme un ensemble de sous-systèmes, intégrant toujours plus d'éléments pour faire face au besoin croissant de puissance de calcul. Les plates-formes avioniques n'échappent pas à la règle et se définissent elles aussi comme un ensemble de sous-systèmes reliés entre eux, à savoir les calculateurs reliés par le réseau ARINC664. De plus, la rupture technologique induite par le changement de principe de conception de ces plates-formes, l'IMA, a nécessité le développement de nouvelles méthodes pour s'adapter aux contraintes toujours plus complexe de développement de ces architectures intégrées. Nous l'avons vu dans le chapitre 1, l'IMA autorise désormais un calculateur à exécuter plusieurs applications de niveaux de criticité différents, alors qu'auparavant chaque calculateur n'exécutait qu'une application.

**Objectif**: l'objectif de nos travaux est d'apporter une contribution au développement de ces nouvelles méthodes de conception. Plus particulièrement, nous nous sommes intéressés aux techniques de modélisation et d'exploration des performances d'un système embarqué en avance de phase, i.e. en tout début de cycle de développement. Ces méthodes permettent de modéliser l'architecture matérielle et/ou logicielle d'un système, avec plus ou moins de détails suivant le niveau d'abstraction choisi. S'appuyant notamment sur des langages de modélisation, l'objectif premier est de traduire les spécifications logicielles et matérielles en un modèle sur lequel il est possible d'effectuer diverses analyses pour la pré-validation de choix d'architecture et/ou le pré-dimensionnement du système en fonction de la partie applicative. Dans nos travaux, nous nous sommes appuyés sur ces outils et méthodes existants, que nous avons cherché à adapter aux spécificités de l'avionique.

Organisation du chapitre: nous allons voir dans ce chapitre les méthodes de modélisation de systèmes embarqués temps-réel en avance de phase. Nous commencerons par un aperçu des langages de modélisation sur lesquelles celles-ci s'appuient. Nous verrons ensuite plus spécifiquement les travaux existants de modélisation de plate-forme avionique, et en quoi ils constituent une base qu'il a fallu enrichir pour s'adapter aux différentes problématiques liées à la modélisation en avance de phase.

# 3.2 Langages de modélisation

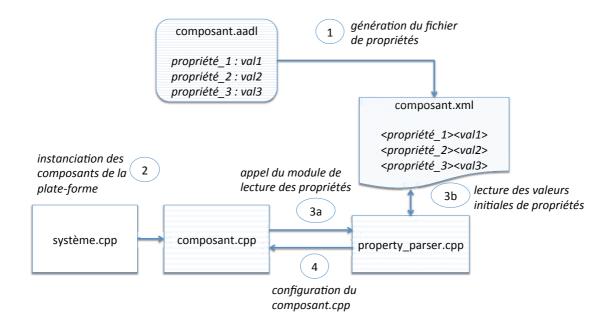

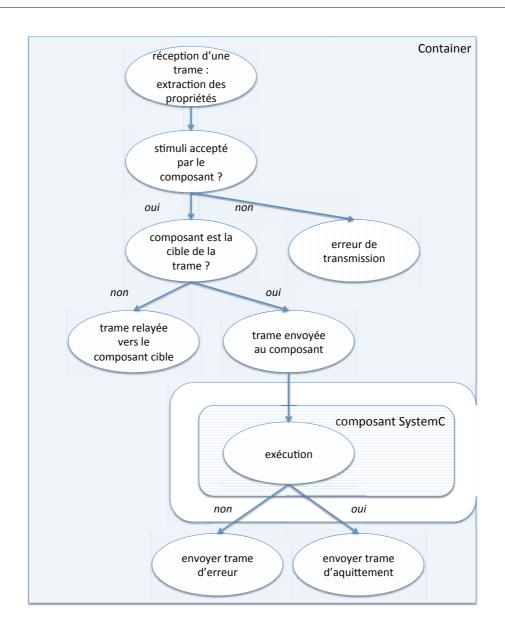

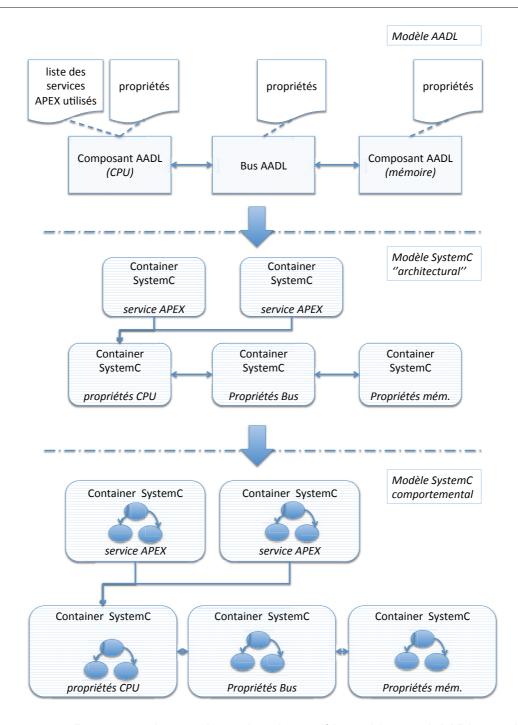

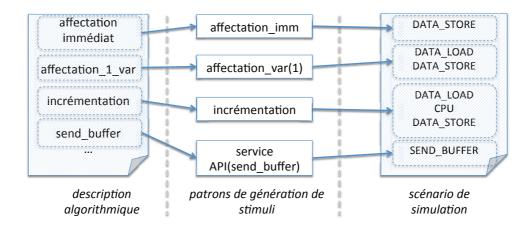

#### 3.2.1 Introduction