# Study and optimization of the growth of a-Si:H on wet-chemically textured c-Si substrates for the enhancement of a-Si:H/c-Si heterojunction solar cells

Igor Paul Sobkowicz

# ▶ To cite this version:

Igor Paul Sobkowicz. Study and optimization of the growth of a-Si:H on wet-chemically textured c-Si substrates for the enhancement of a-Si:H/c-Si heterojunction solar cells. Physics [physics]. Ecole Doctorale Polytechnique, 2014. English. NNT: . tel-01120054

# HAL Id: tel-01120054 https://pastel.hal.science/tel-01120054

Submitted on 24 Feb 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Igor Paul SOBKOWICZ

# Study and optimization of the growth of a-Si:H on wet chemically-textured c-Si substrates for the enhancement of a-Si:H/c-Si heterojunction solar cells

Doctoral thesis in Materials Science

# **Thèse**

présentée en vue d'obtenir le grade de

# Docteur de l'Ecole Polytechnique

Spécialité Physique/Science des Matériaux par

# Igor Paul SOBKOWICZ

igor.sobkowicz@polytechnique.edu

Cette thèse a été soutenue le 9 décembre 2014 à 14h00 Amphithéâtre Becquerel – Ecole Polytechnique devant le jury composé de:

| Ass. Prof. | René Van Swaaij        | Rapporteur         |

|------------|------------------------|--------------------|

| Dr.        | Erwann Fourmond        | Rapporteur         |

| Prof.      | Christophe Longeaud    | Examinateur        |

| Dr.        | Lars Korte             | Examinateur        |

| Dr.        | Stefaan De Wolf        | Examinateur        |

| Dr.        | Thierry Mélin          | Invité             |

| M.         | Mathieu Rouquié        | Invité             |

| Prof.      | Pere Roca i Cabarrocas | Directeur de thèse |

When I saw the pyramids of Giza, it dawned on me that these could not have been made out of (111) planes solely...

A mes chers parents,

# Acknowledgements

It's hard to know where to start...3 years at LPICM, constantly meeting new people, gathering new ideas, getting inspired...Let's start from the top.

This Ph.D. thesis has been carried out at the LPICM lab of Ecole Polytechnique within the framework of the Joint-Research Team with the New Energy branch of the TOTAL group. Therefore I would like to thank Bernard Drévillon who was at the head of the LPICM lab in 2011, for allowing me to spend these last 3 years within its walls. I am thankful to Pere Roca i Cabarrocas the LPICM new director who accepted to supervise my Ph.D. thesis. I am especially thankful for his constant optimism (which sometimes needs to be balanced by a French or Russian scientist) that definitely pulls you up to the utmost and eventually leads you to better results. I am very much impressed and thankful for his incredible flexibility, for correcting my presentation and talks on Sundays, vacations, sometimes even at UTC-9, for all the 8 A.M and 8 P.M. meetings, for loading the ARCAM reactor to allow me to efficiently start on Monday morning and for many other things. On the TOTAL side, I would like to thank Fabrice of course, but also Jérôme for allowing me to be part of this joint-research project in 2011. Thank you Antoine for being my mentor: thank you for pushing me into scientific and technical multitasking, thank you for encouraging me to present my results and to get trained when opportunities showed up. Thank you for training me on the ARCAM reactor, thank you for the many HF dips that I could not perform. Thank you for your investment when launching the PECVD Cluster Tool and for your help maintaining it. I'll stop here but just know that I feel lucky to have had you around.

Talking HF, Sergey, Gilles (pronounced "Jillz"), Ludovic "Ludo", Erik, Wanghua, thank you for your help. Without it, I would have lost a lot of reactor time. I would like to thank Fabien and Jean-François from the DCSO lab who allowed us to run the craziest HF dips of all time: running with clean wafers all the way from the A1 wing 3<sup>rd</sup> floor down to the A4 wing 1<sup>st</sup> floor ARCAM room (this is how we got our best results by the way).

I would like to thank the Algécos' team now. Coralie "Coco" and Guillaume "Guigui": sorry for making up nicknames so soon after meeting you even though we did not "look after pigs together" (French saying). Thank you for welcoming me and for all your advice. You've made the transition smooth. I was also very happy to welcome Paul "Narchos" and Ronan "next-Roro" upon the end of my thesis. Your presence was quite refreshing and allowed me to finish writing in a very pleasant and positive environment. Always keep in mind that muscles must cry a river at the gym, otherwise it's just what the French call a mere promenade de santé. Thank you Jean-François for your many optical measurements and for all of our adventurous story-tellings at Mâgnan: Africa and South-America came to life at lunch-time. Thank you

Rym a.k.a. "Sputtering-Reem" for the positive impact you've had on all Ph.D. students including me. It was nice learning a few words in Arabic here and there, between two reactor pumpings. Now, my notebook is full of declensions and verbal forms. Thank you Nada and Ludo: it is in your office that we found how to double my solar cell production instantly (do the same for CAL next time and you'll become filthy rich). I would like to also thank all the newcomers: competent and fun people like Gilles a.k.a. "Jillz", Sergej, Jara and Martin. I would also like to thank Pavel for healing my tongue, which I found to be corrupt with 20 years of junk-food. Now, I can boldly say that wine tastes better than sodas. More importantly, thank you for giving me a real taste for stripping down all my results down to a point where I can proudly and undoubtedly present them in front of a crowd of ferocious scientists. Speaking of which, I take the opportunity to thank Jean-Christophe, a.k.a. "Jeanjean" or "Jeanjean Cri" or "Jeanjean Cricri" or "JC". While he obviously started on the wrong foot by putting his in my office and claiming that his desk should be there, it got much better (with time). Plasma processes and the Clusty reactor helped bringing some barriers down. More seriously, he was the best colleague ever and our workplace quickly became a very pleasant place to be. Conferences were always quite risky and usually involved some near-death experiences such as shooting, rafting and so on. Although scientific discussions often led to quite depressing conclusions, they allowed me to refine my results down to their very core and to present them in the best way. He really had a positive impact on the way I work and I'm sure many other scientists at LPICM could say the same. Thank you for your Bulgarian-nurse strategy. Although sometimes annoying, it is clearly efficient and this is how Clusty became very quickly user-friendly. Thank you for being so innovative and for repairing so many machines (that you weren't even using sometimes!). I do not forget about our third coworker either, i.e., Ka-Hyun a.k.a. "James" with his incredible knowledge on a-Si:H and inimitable "so-British" style.

Apart from the Algécos, I will always remember Aile 4 (pronounce L-katr) and the people in it: Bastien a.k.a "Bastos" and his many publications, Romain a.k.a. "Roro" and his many years of experience. I would like to especially thank the LPICM optical team. Discussions with Martin and Zuzanna were very useful to understand the impact of texturing on optical measurements. I wish you all the best with the very special ellipsometer that made us learn about servo-motors and hardware/software communication (maybe we should create a consulting startup?). Thank you Parsathi for our collaborative effort on coplanar conductivity. I did learn a lot on the a-Si:H/c-Si interface. I am not forgetting about all the people that made these 3 years quite enjoyable: Soumyadeep a.k.a. "Deep", Dennis, Gérald...I have a special thought for Mishael a.k.a. "Misha" who worked hard to obtain and maintain the high quality of our ITO and JV measurements. I'm glad that you could be part of the 20% achievement and I wish you all the best for the future.

I wish to extend my gratitude to the tech specialists: Cyril (pronounced "Syryle") (seriously, do you even own a member's pass for the gym?), Frédéric and Jérôme "Gégé", without whom we'd be out of gas, turbo-pumps and substrate holders. I cannot forget about the LGEP lab either. Thank you for your help with AFORS-HET, your measurements and the fruitful conversations with Jean-Paul, Marie, Arouna and Djicknoum. It was way more powerful than books.

I would like to thank Ecole Polytechnique for welcoming me in 2008 to pursue my studies. Thank you Cécile Vigouroux and Thanh-Tam Lê for arranging many things to make this possible. I will not forget the

high quality of the lectures I've had the honor to follow. Henri-Jean Drouhin, Emmanuel Rosencher and David Quéré are names I'll always remember: you have triggered a quite strong motivation for science and research that has led to the writing and defense of this manuscript. Last but not least, I cannot forget to mention Justin Peatross who, to me, was the first physicist to demonstrate the cool-attitude/research duality.

I would like to thank my jury: René Van Swaaij, Erwann Fourmond, Christophe Longeaud, Lars Korte, Stefaan De Wolf, Thierry Mélin, Mathieu Rouquié and Pere Roca i Cabarrocas. Thank you for accepting to be part of my Ph.D. thesis. Thank you for your useful insights and corrections. Your questioning my results and your presence during my defense bring much value to this manuscript.

Finally, even during a Ph.D. thesis, life goes on. This is why family is so important, even though they discovered my topic of research only during my defense. Having had you around was precious and knowing it has been helpful on many occasions.

# **Contents**

| n | trod | uct   | ion  | 1                                                                     | 15 |

|---|------|-------|------|-----------------------------------------------------------------------|----|

| L | Bas  | sics  | of   | photovoltaics                                                         | 21 |

|   | 1.1  | Sola  | ar e | nergy                                                                 | 22 |

|   | 1.1. | .1    | Air  | Mass                                                                  | 22 |

|   | 1.1. | .2    | Sol  | ar spectrum                                                           | 23 |

|   | 1.2  | Sen   | nico | nductor physics applied to solar devices                              | 25 |

|   | 1.2. | .1    | Bas  | sics of semiconductor physics                                         | 25 |

|   | 1    | .2.1  | a    | Semiconductor materials                                               | 25 |

|   | 1    | .2.1  | .b   | Photon energy and bandgap                                             | 26 |

|   | 1    | .2.1  | .с   | Doped semiconductors                                                  | 28 |

|   | 1    | .2.1  | .d   | Semiconductors at thermal equilibrium                                 | 28 |

|   | 1    | .2.1  | .e   | Semiconductors under light excitation                                 | 29 |

|   | 1.2. | .2    | PN   | junction                                                              | 30 |

|   | 1    | .2.2  | .a   | Formation of a pn junction                                            | 30 |

|   | 1    | .2.2  | .b   | Diffusion and drift                                                   | 31 |

|   | 1    | .2.2  | c    | Diode equations                                                       | 32 |

|   | 1.3  | Silio | con  | for PV applications                                                   | 34 |

|   | 1.3. | .1    | Bul  | k recombination and lifetime                                          | 34 |

|   | 1    | .3.1  | a    | Radiative recombination: relaxation by photon emission                | 35 |

|   | 1    | .3.1  | .b   | Band-to-band Auger recombination: energy transfer to a charge carrier | 36 |

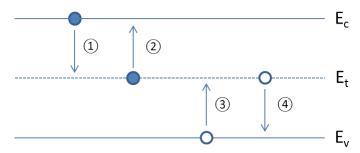

|   | 1    | .3.1  | .с   | Shockley-Read-Hall recombination: defect-assisted recombination       | 37 |

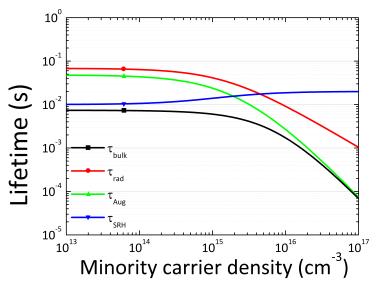

|   | 1    | .3.1  | .d   | Bulk lifetime                                                         | 39 |

|   | 1.3. | .2    | Нус  | drogenated amorphous silicon                                          | 39 |

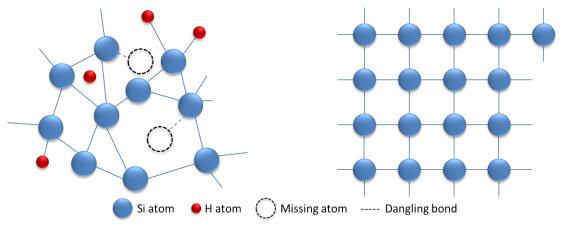

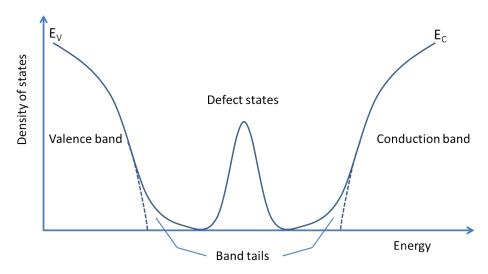

|   | 1    | .3.2  | .a   | The a-Si:H network and its consequences on the density of states      | 40 |

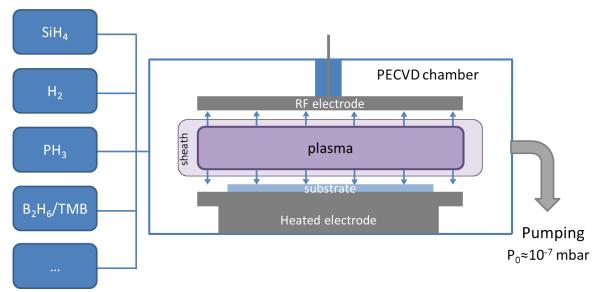

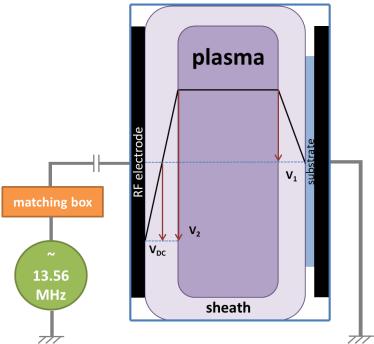

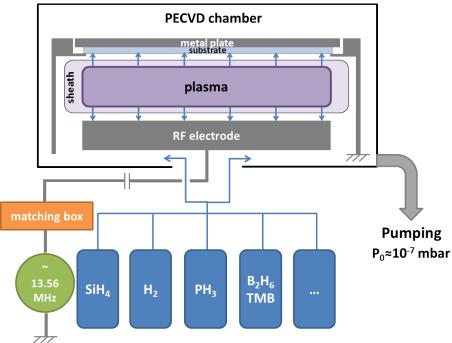

|   | 1    | 3.2   | .b   | Plasma-Enhanced Chemical Vapor Deposition (PECVD)                     | 43 |

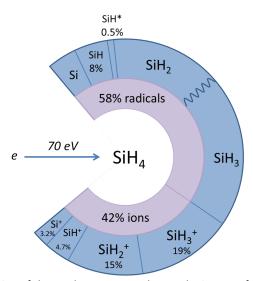

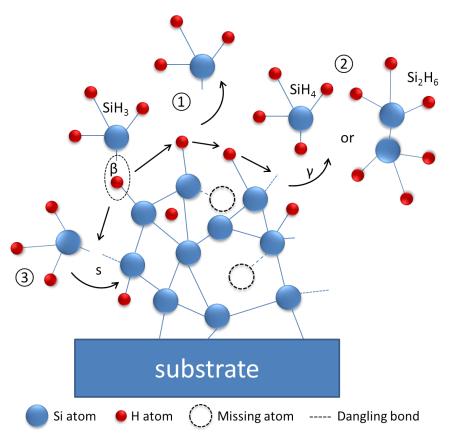

|      | 1.3.2.0 | c a-Si:H growth mechanism model                                                            | . 47 |

|------|---------|--------------------------------------------------------------------------------------------|------|

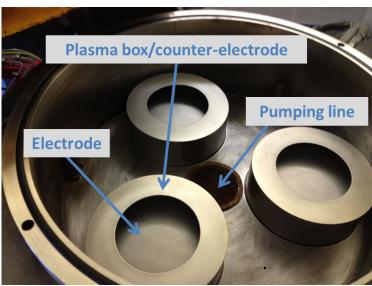

|      | 1.3.2.0 | d ARCAM reactor                                                                            | . 48 |

| 2 C  | rystal  | lline silicon surface passivation by a-Si:H                                                | 53   |

| 2.1  | Passi   | ivation and heterojunction solar cells                                                     | 54   |

| 2    | .1.1 a  | a-Si:H/c-Si heterojunction solar cells and the HiT structure                               | . 54 |

| 2    | .1.2 7  | The a-Si:H/c-Si interface                                                                  | . 57 |

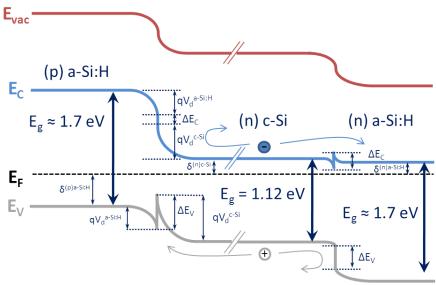

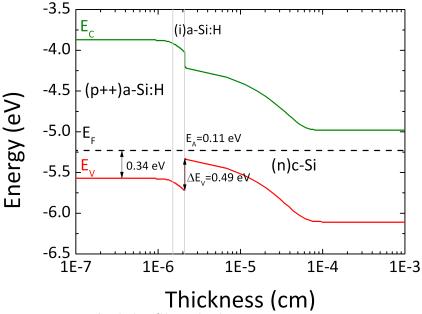

|      | 2.1.2.  | a Band offsets – inversion layer at the a-Si:H/c-Si interfaces                             | . 57 |

|      | 2.1.2.  | b The a-Si:H/c-Si heterointerface and the intrinsic layer                                  | . 58 |

| 2    | .1.3    | Surface passivation of crystalline silicon by a-Si:H                                       | . 59 |

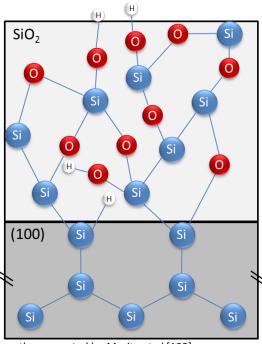

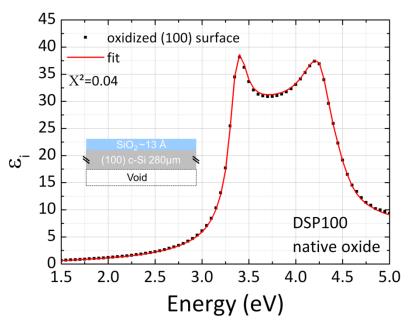

|      | 2.1.3.  | a The (100) surface                                                                        | . 59 |

|      | 2.1.3.  | b The (111) surface                                                                        | . 60 |

| 2.2  | Asse    | essing the passivating properties of the a-Si:H capping layer                              | 61   |

| 2    | .2.1 E  | Effective lifetime formalism applied to surface recombination                              | . 61 |

|      | 2.2.1.  | a Surface recombination                                                                    | . 61 |

|      | 2.2.1.  | b Effective lifetime                                                                       | . 62 |

|      | 2.2.1.0 | c Effective lifetime enhancement strategies                                                | . 63 |

| 2    | .2.2 F  | Photoconductance decay measurements                                                        | . 65 |

|      | 2.2.2.  | a WCT-120 PCD setup and its different operating modes                                      | . 65 |

|      | 2.2.2.  | b Extraction of the implied open-circuit voltage (iV <sub>oc</sub> ) from PCD measurements | . 66 |

| 3 P  | assiva  | ation of chemically wet-textured crystalline n-type wafers using                           |      |

| hydr | ogena   | ated amorphous silicon deposited by low-temperature PECVD                                  | 69   |

| 3.1  | Text    | curation of crystalline silicon                                                            | 70   |

| 3    | .1.1 E  | Bulk etching of crystalline silicon                                                        | . 71 |

| 3    | .1.2 \  | Wet etching                                                                                | . 72 |

|      | 3.1.2.  | a Isotropic wet etching of silicon                                                         | . 72 |

|      | 3.1.2.  | b Anisotropic wet etching of silicon                                                       | . 74 |

| 3    | .1.3 \  | Wet-texturing recipes for a-Si:H/c-Si heterojunction solar cells                           | . 80 |

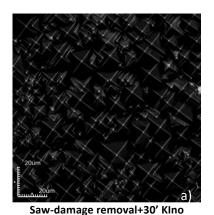

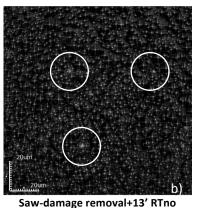

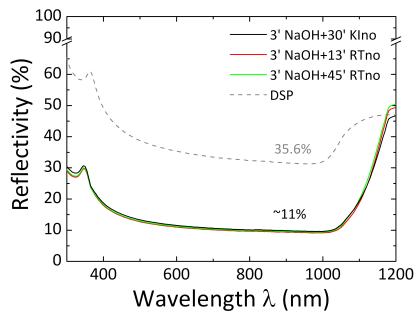

|      | 3.1.3.  | a Saw-damage removal                                                                       | . 81 |

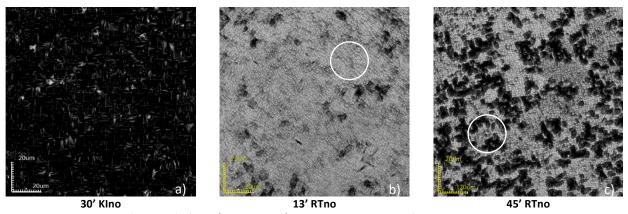

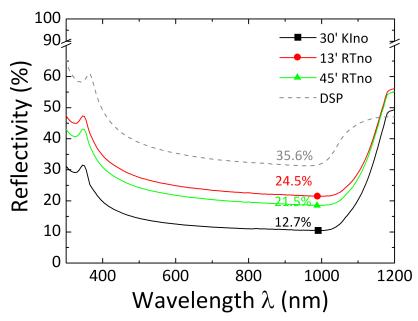

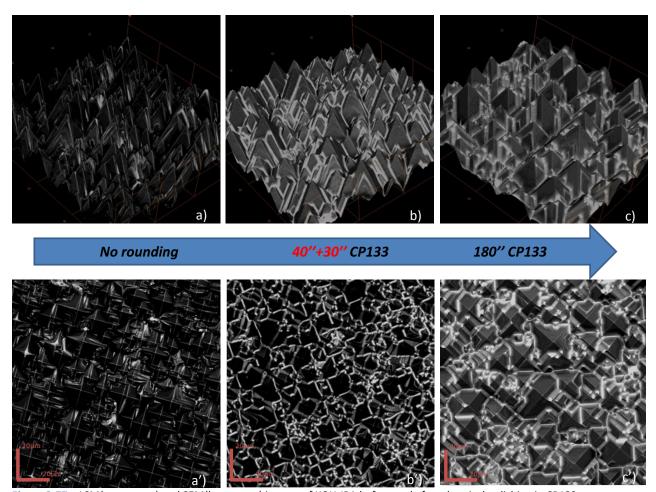

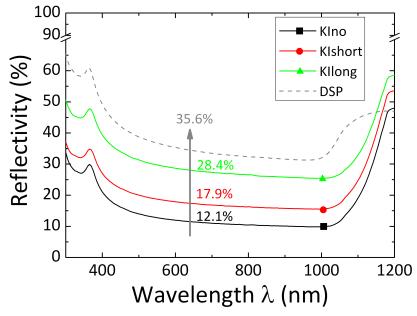

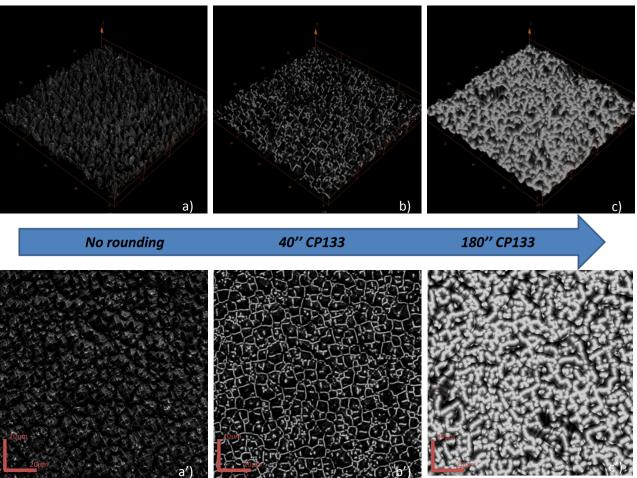

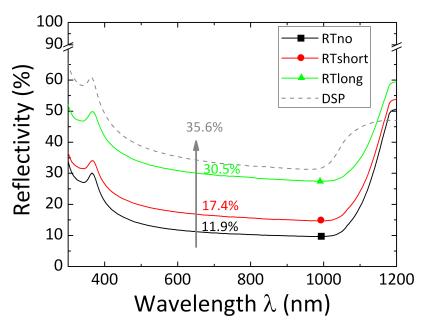

|      | 3.1.3.  | b KIno and RTno texturing recipes                                                          | . 85 |

| 3.2  | Passi   | ivation of wet-textured c-Si n-type wafers using a-Si:H                                    | 86   |

| 3    | .2.1    | Defining a cleaning procedure for our textured c-Si wafers                                 | . 86 |

|   | 3.2.2 Pas           | ssivation enhancement on textured (n)c-Si wafers                                                                             | 90    |

|---|---------------------|------------------------------------------------------------------------------------------------------------------------------|-------|

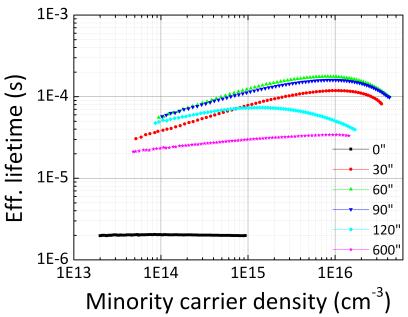

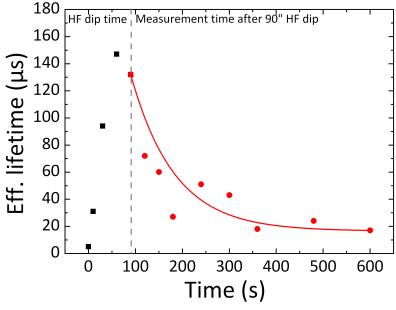

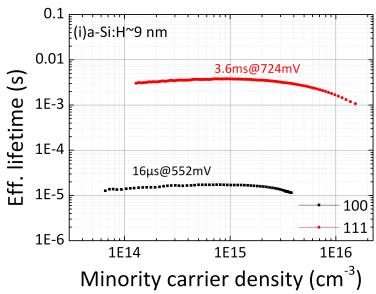

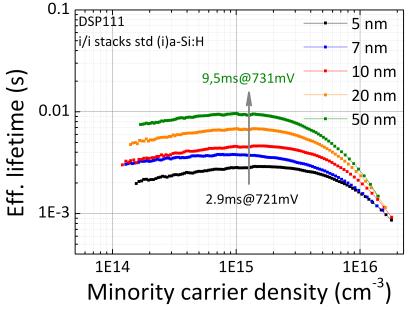

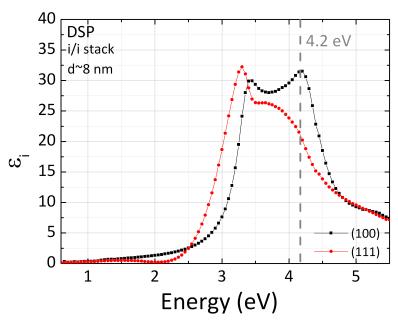

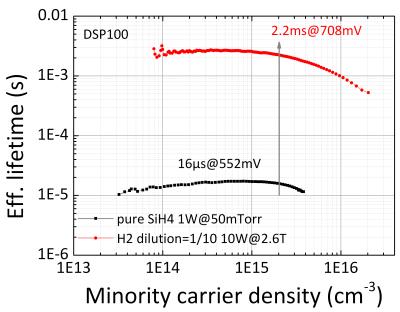

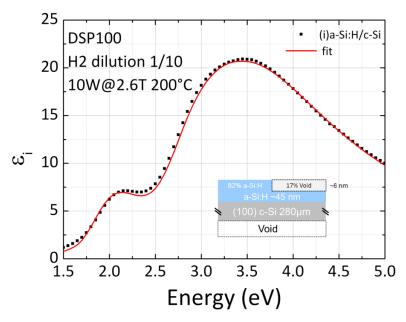

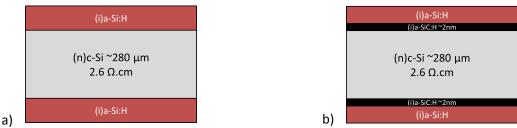

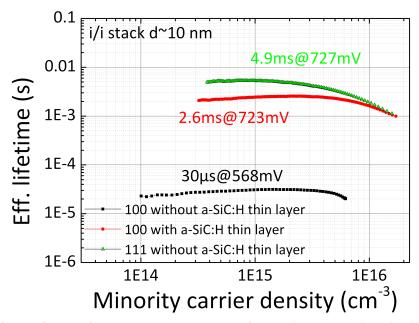

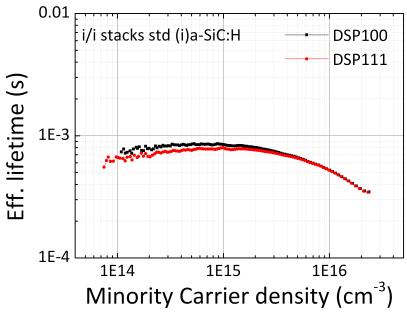

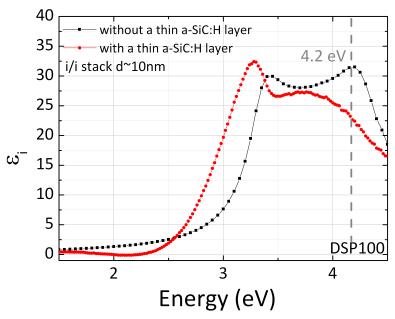

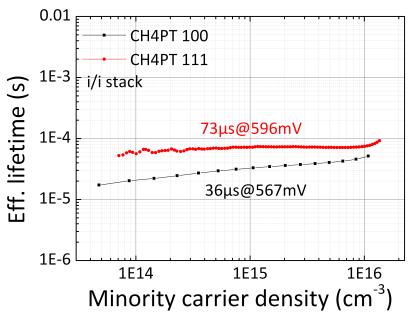

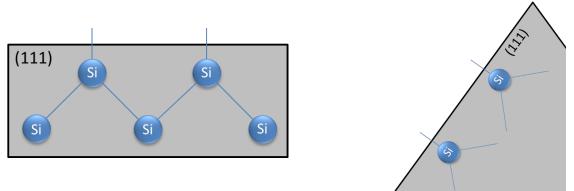

|   | 3.2.2.a             | Passivation of flat 100 and 111-oriented (n)c-Si wafers                                                                      | 90    |

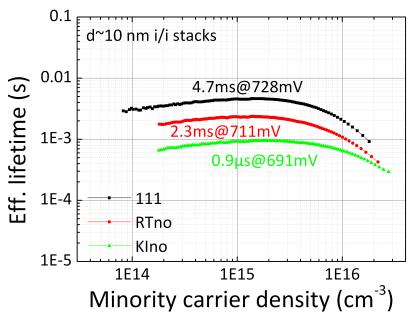

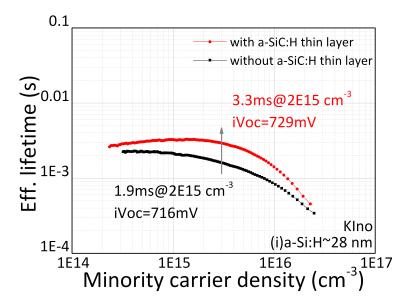

|   | 3.2.2.b             | Textured c-Si wafer passivation enhancement                                                                                  | 99    |

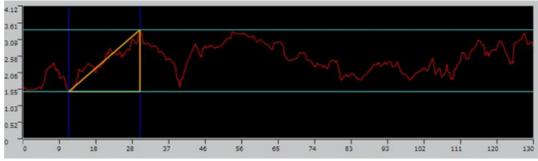

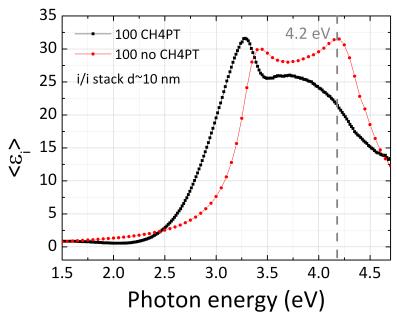

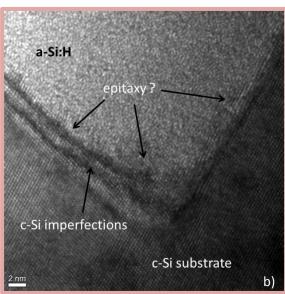

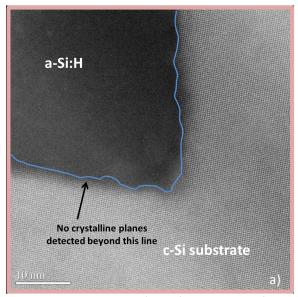

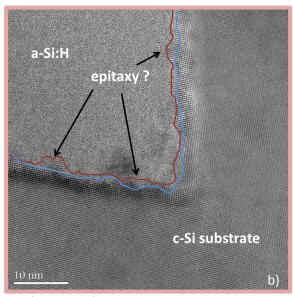

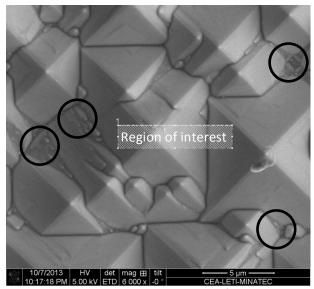

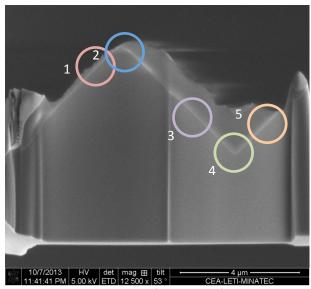

|   | 3.2.2.c             | Looking for epitaxial growth on textured c-Si wafers                                                                         | . 101 |

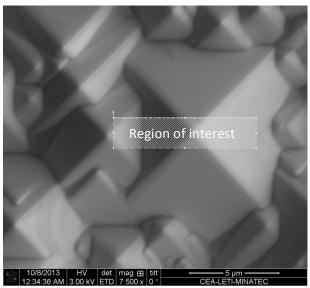

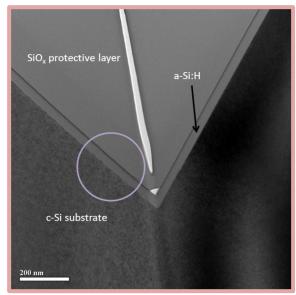

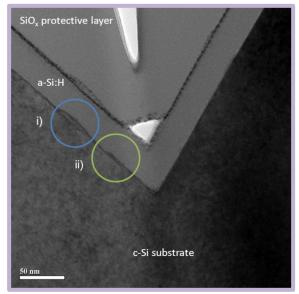

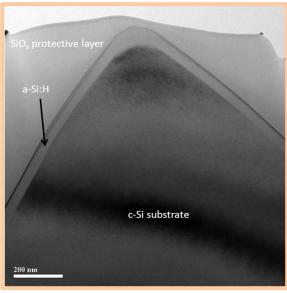

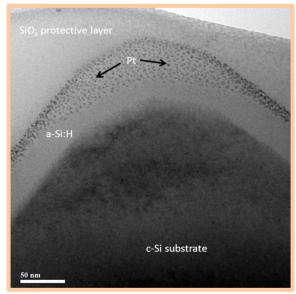

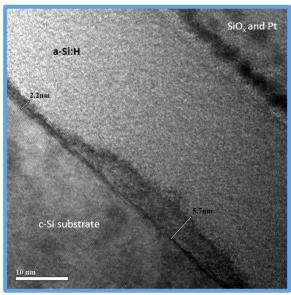

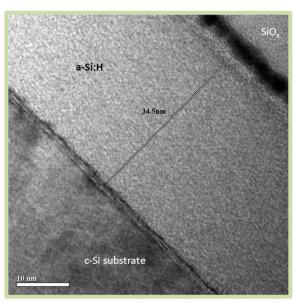

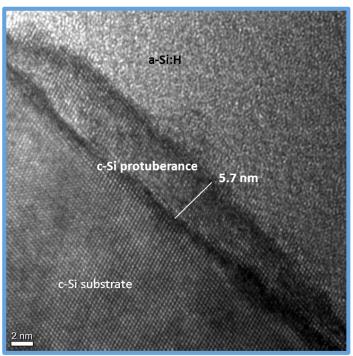

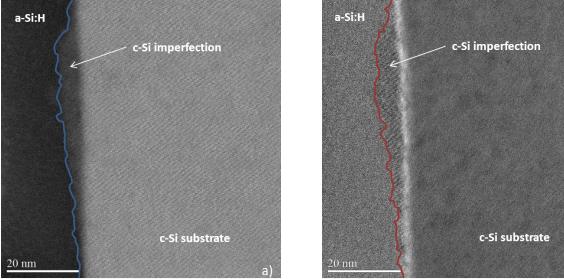

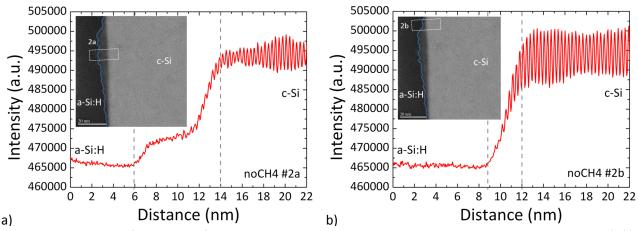

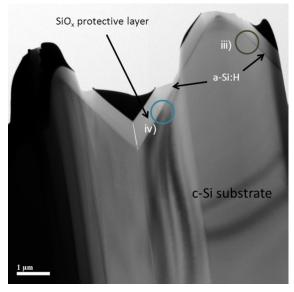

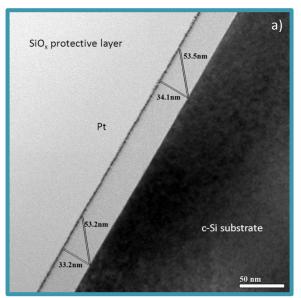

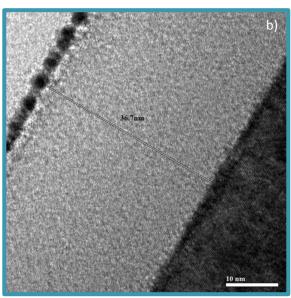

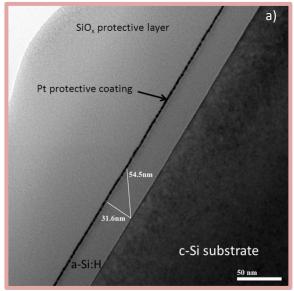

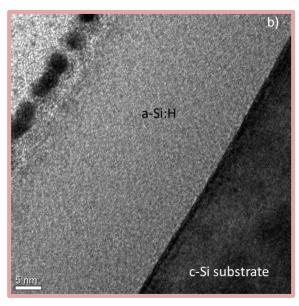

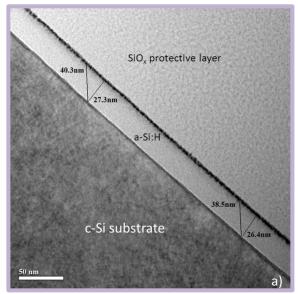

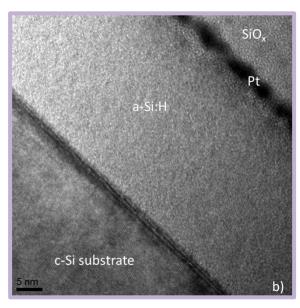

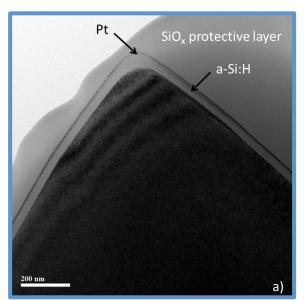

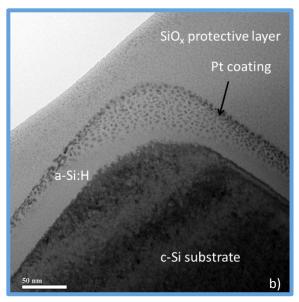

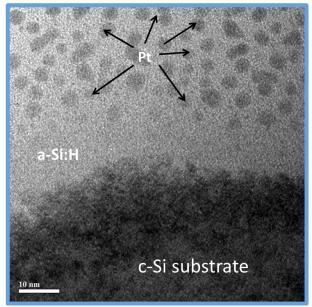

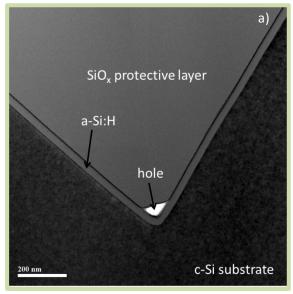

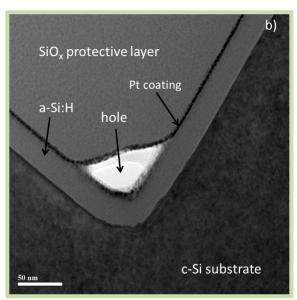

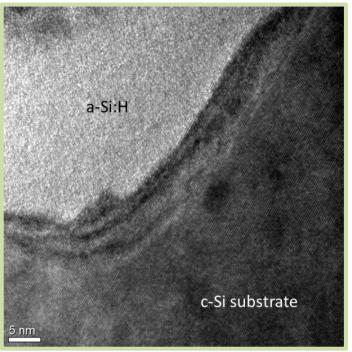

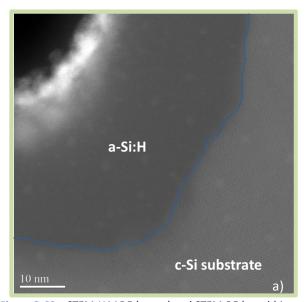

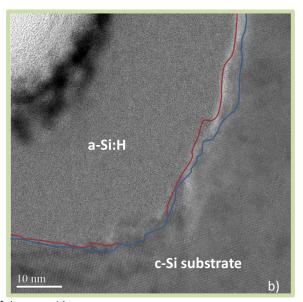

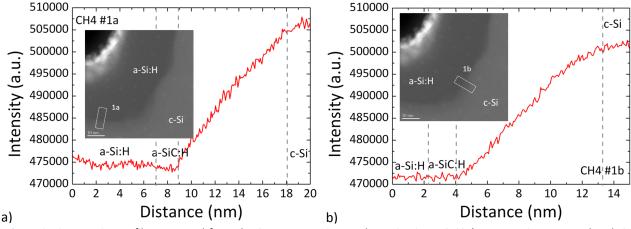

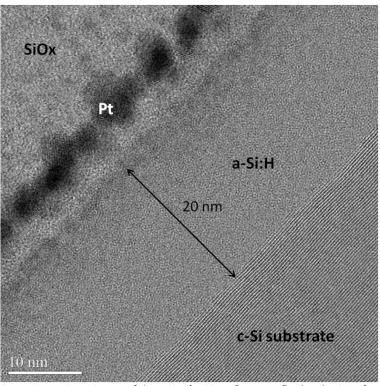

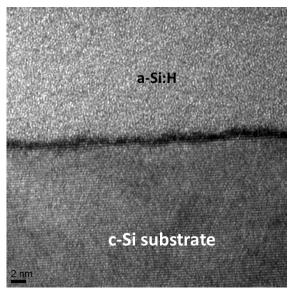

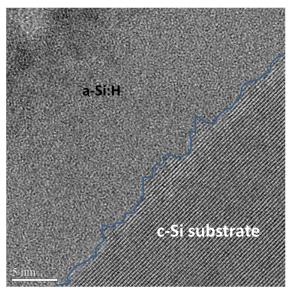

|   | 3.2.2.d             | HR-TEM and STEM analyses on passivated KIno wafers                                                                           | . 106 |

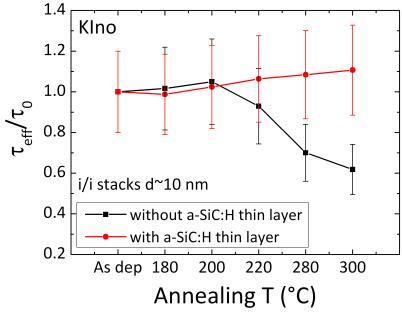

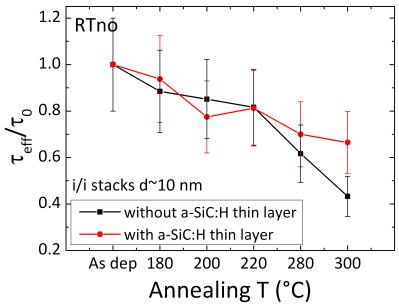

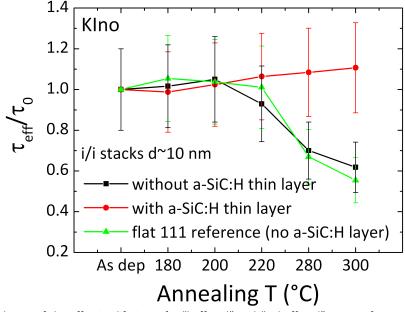

|   | 3.2.2.e<br>wafers v | Detection of epitaxial growth at the a-Si:H/c-Si interface of passivated textured c-Si ia annealing studies                  |       |

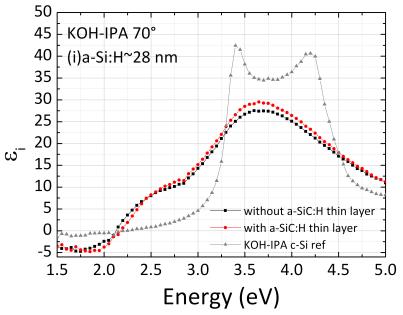

|   | 3.2.2.f<br>wafers b | Detection of epitaxial growth at the a-Si:H/c-Si interface of passivated textured c-Si by spectroscopic ellipsometry         | . 126 |

|   | 3.2.2.g             | Chemical smoothing                                                                                                           | . 127 |

| 4 | Optimiza            | ation of a-Si:H/c-Si SHJ solar cells on n-type textured wafers                                                               | 135   |

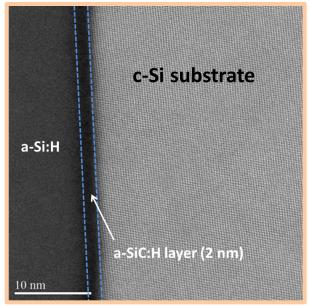

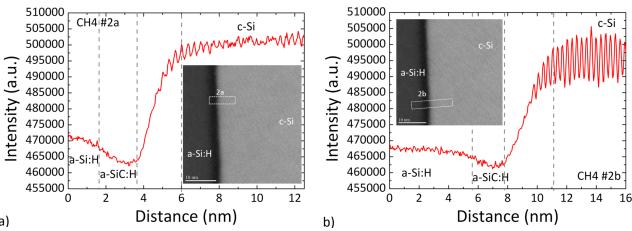

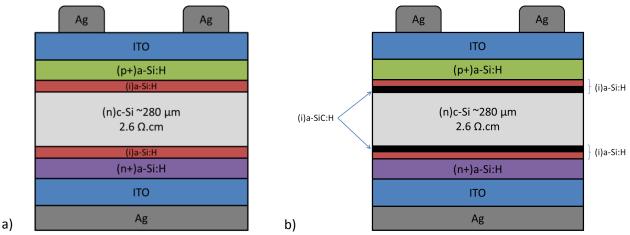

|   |                     | I thin buffer layer at the a-Si:H/c-Si interface to enhance the conversion efficiency of solar cells                         |       |

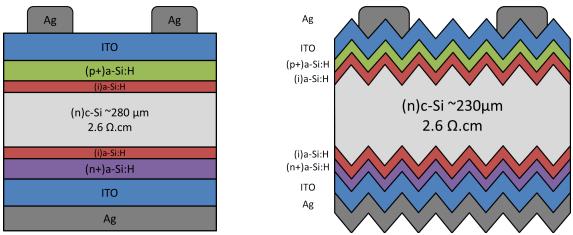

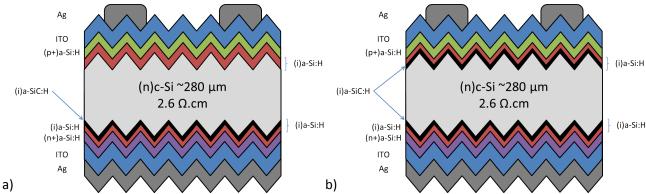

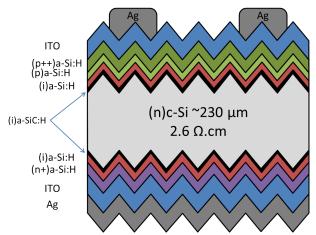

|   | 4.1.1 SH            | J solar cell fabrication chain at LPICM                                                                                      | . 136 |

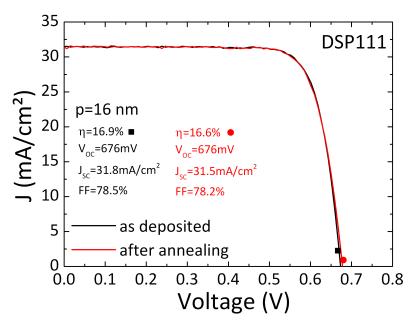

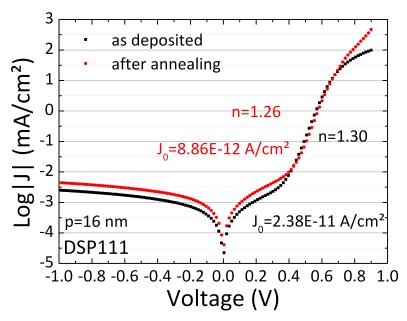

|   | 4.1.2 SH            | I solar cell performance under our standard conditions                                                                       | . 139 |

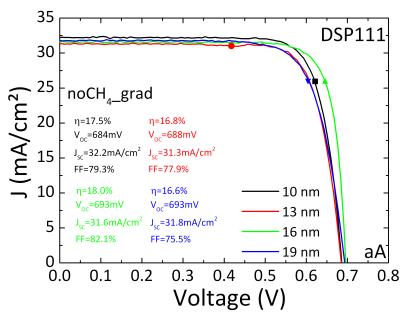

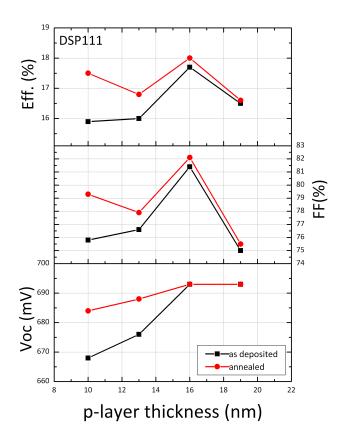

|   | 4.1.2.a             | Flat SHJ solar cells fabricated on DSP (111)-oriented c-Si wafers                                                            | . 139 |

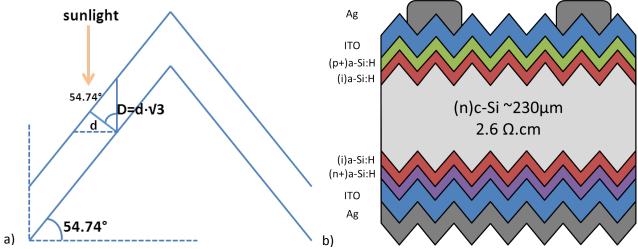

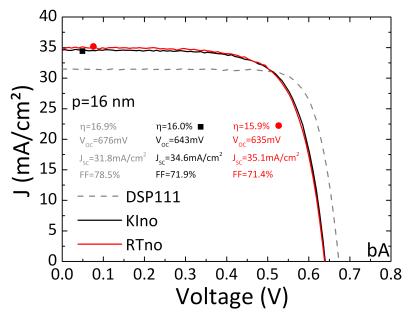

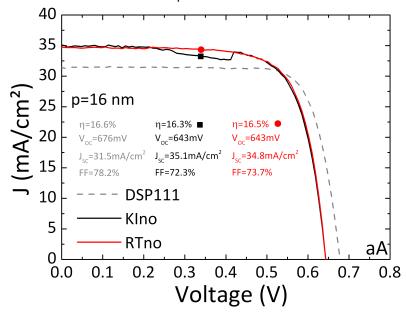

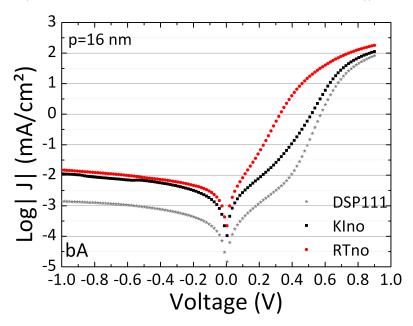

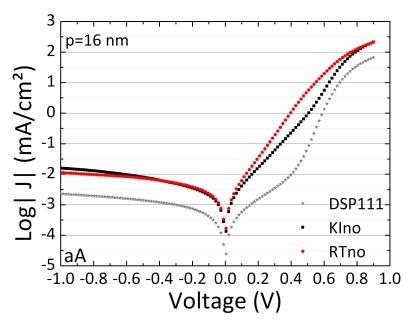

|   | 4.1.2.b             | Direct transfer of our standard SHJ recipe to textured c-Si substrates                                                       | . 141 |

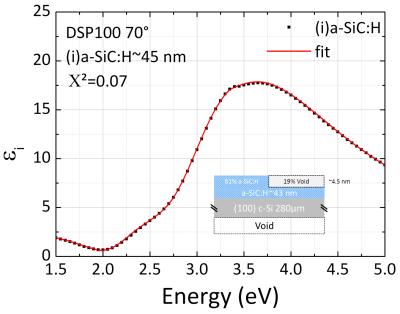

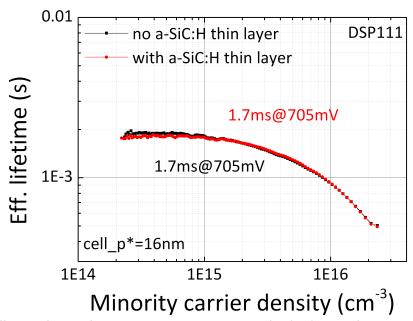

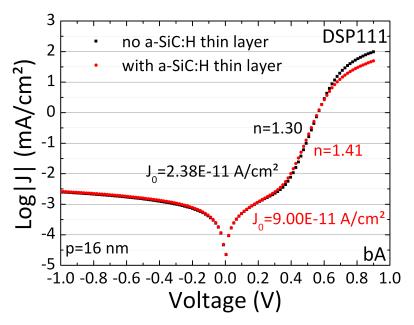

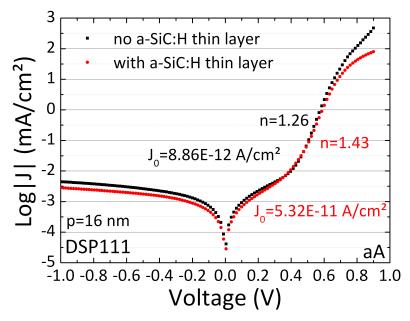

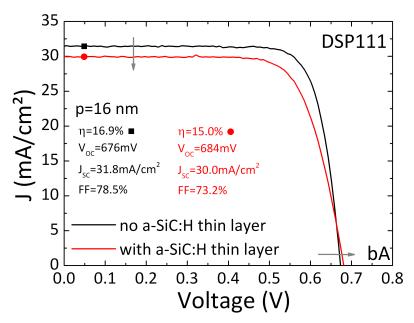

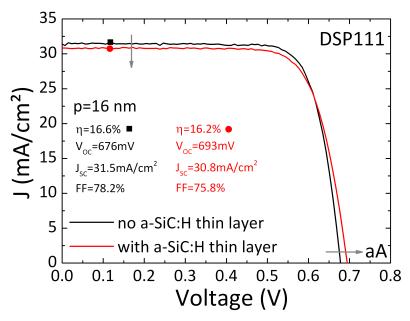

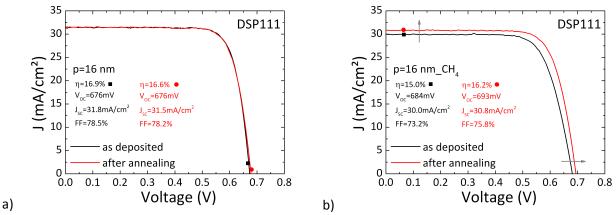

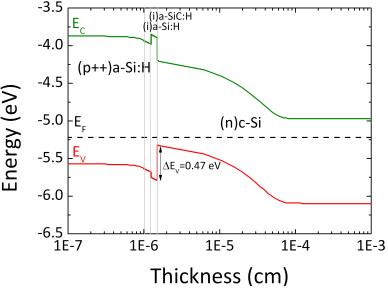

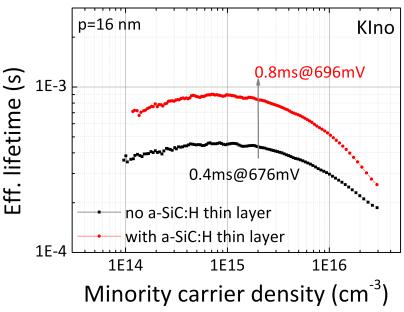

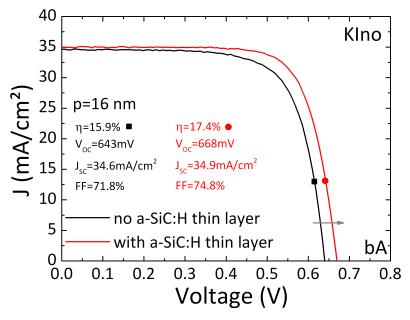

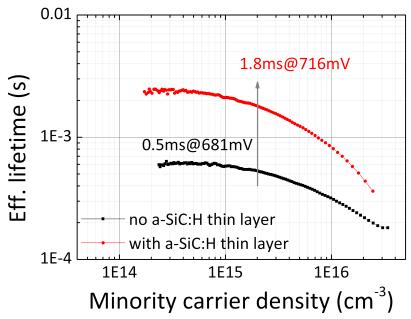

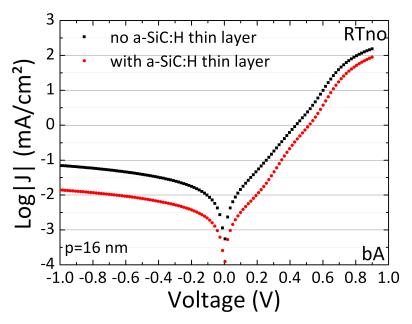

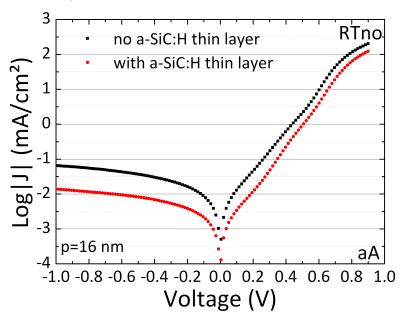

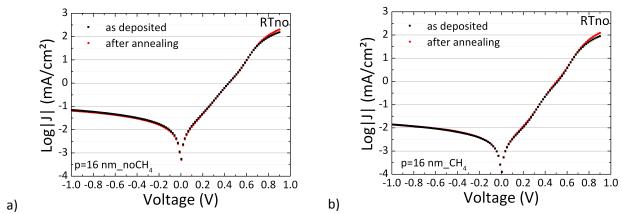

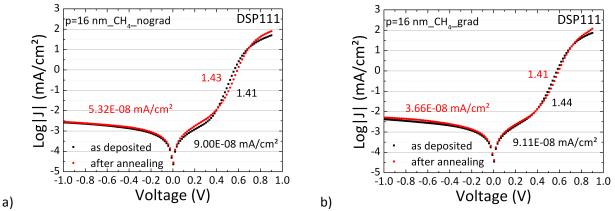

|   | 4.1.3 Im            | pact of a thin a-SiC:H layer at the a-Si:H/c-Si interface: flat (111) SHJ solar cells                                        | . 145 |

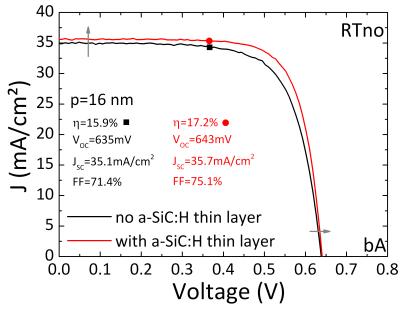

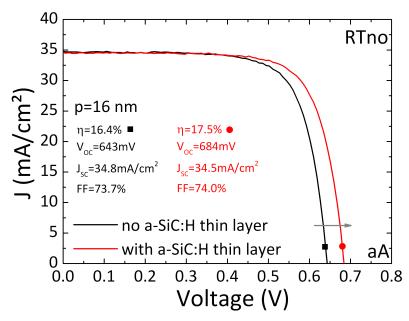

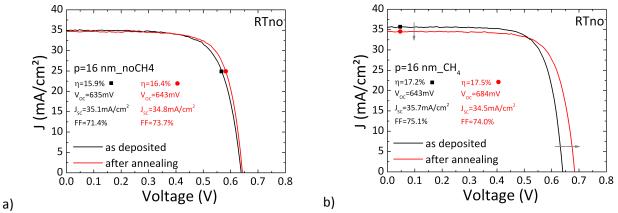

|   | 4.1.4 Im            | pact of a thin a-SiC:H layer at the a-Si:H/c-Si interface: textured SHJ solar cells                                          | . 153 |

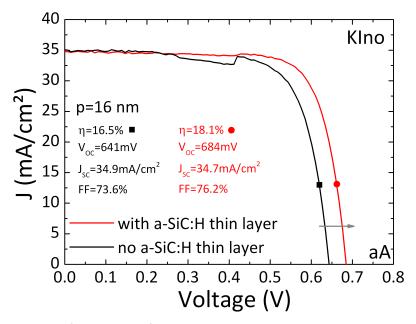

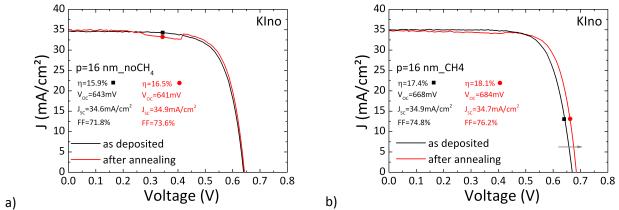

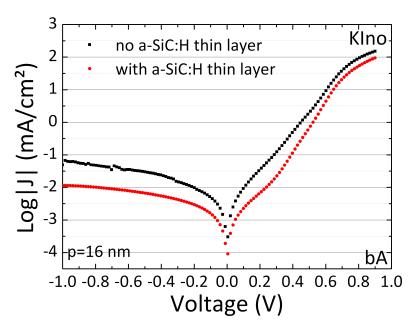

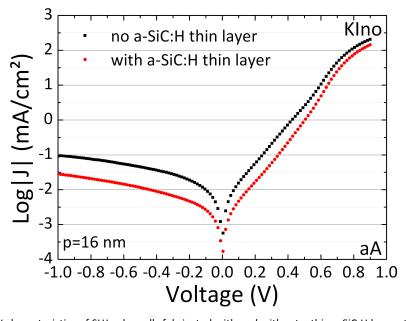

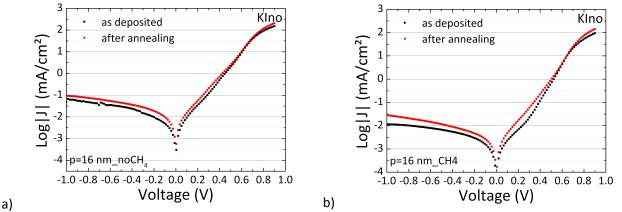

|   | 4.1.4.a             | KIno cells                                                                                                                   | . 153 |

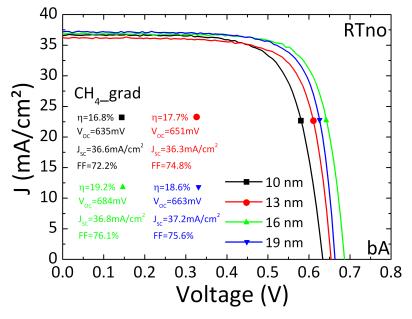

|   | 4.1.4.b             | RTno cells                                                                                                                   | . 158 |

|   |                     | lation of the passivation upon TCO sputtering. Implementation of a p-layer gradien conversion efficiency of SHJ solar cells. |       |

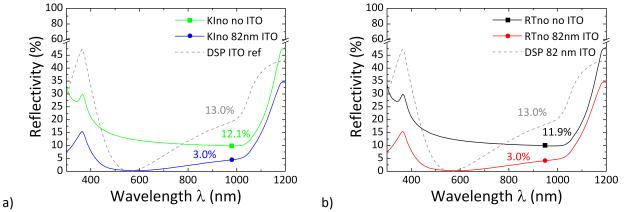

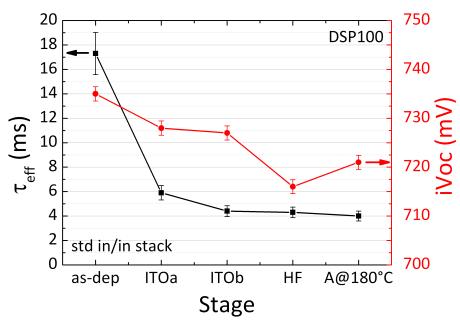

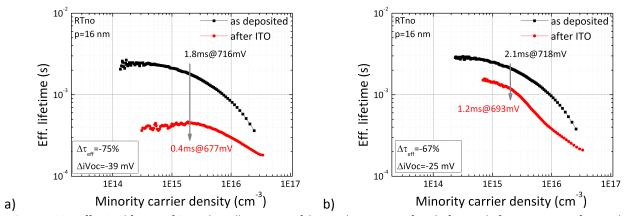

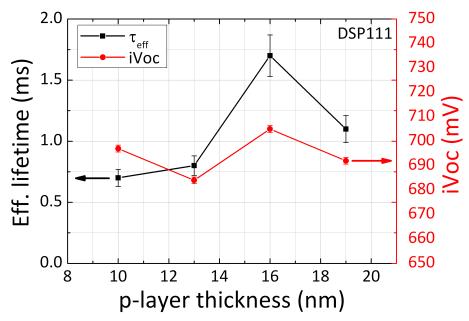

|   | 4.2.1 Pas           | ssivation degradation upon ITO sputtering                                                                                    | . 162 |

|   | 4.2.1.a             | Goal of the study                                                                                                            | . 162 |

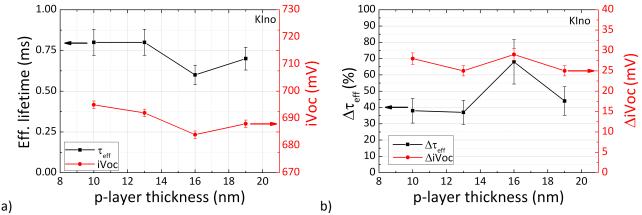

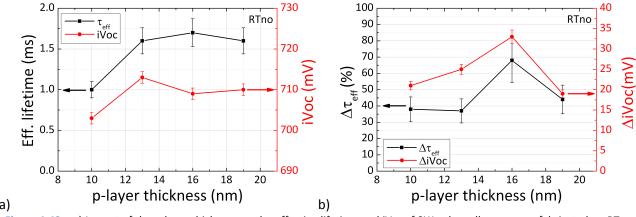

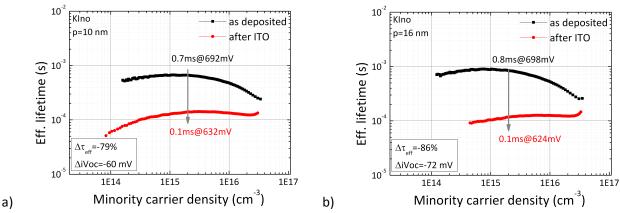

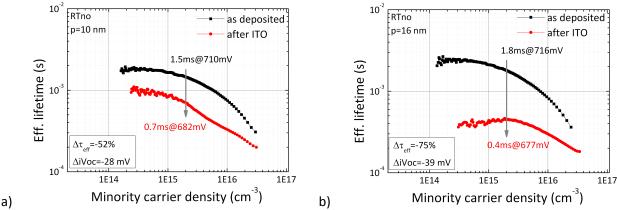

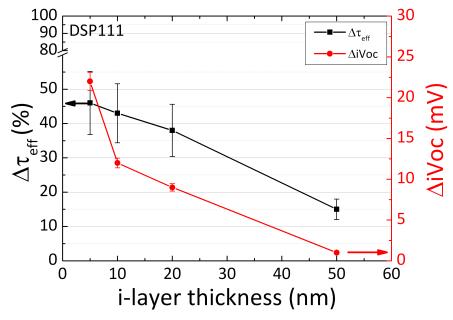

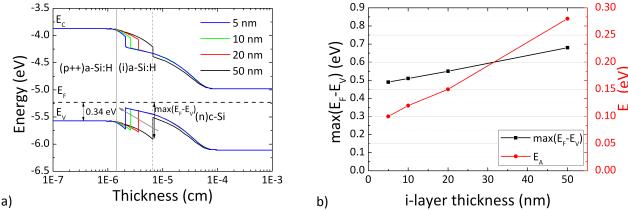

|   | 4.2.1.b             | Impact of the amorphous layer thicknesses on the passivation degradation                                                     | . 166 |

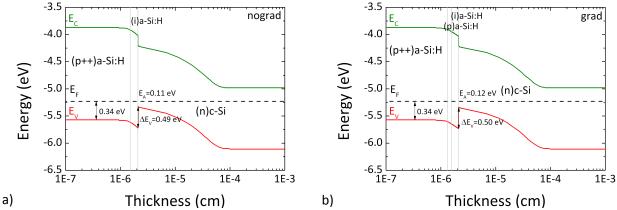

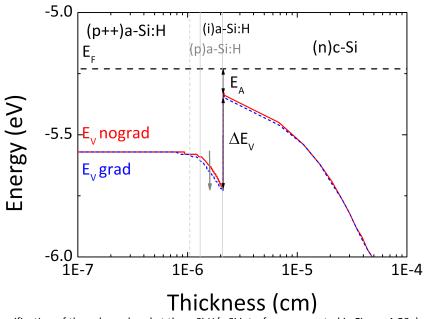

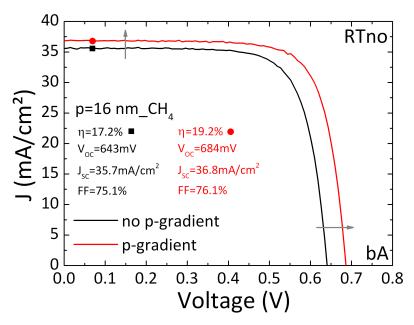

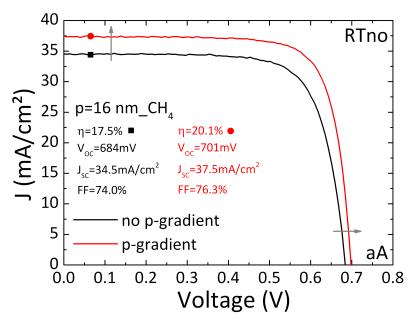

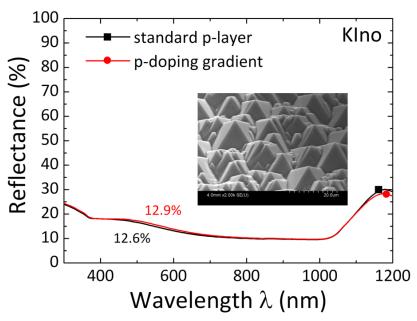

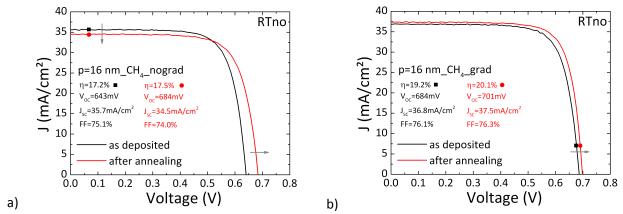

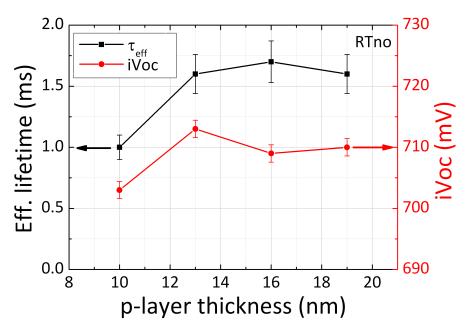

|   | 4.2.2 Im            | plementation of a p-layer gradient to lower recombination on the emitter side                                                | . 174 |

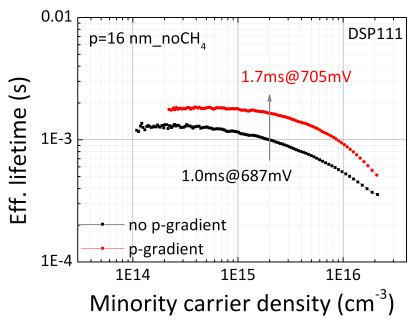

|   | 4.2.2.a             | Impact of a p-layer gradient on passivation                                                                                  | . 176 |

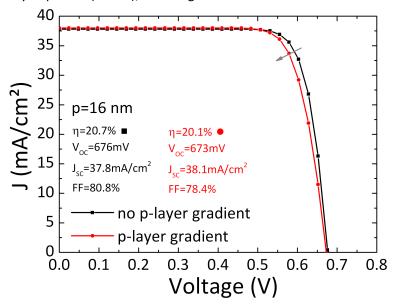

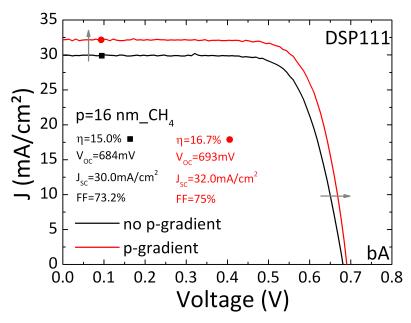

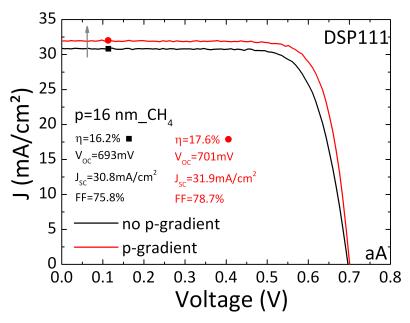

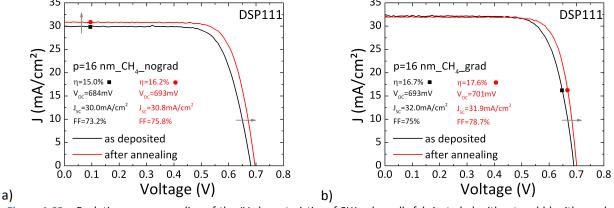

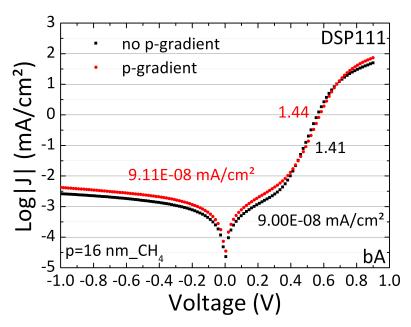

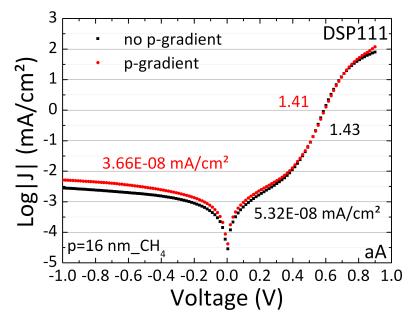

|   | 4.2.2.b             | Impact of a p-layer gradient on the performance of flat SHJ solar cell                                                       | . 177 |

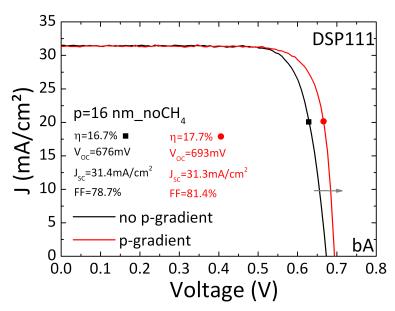

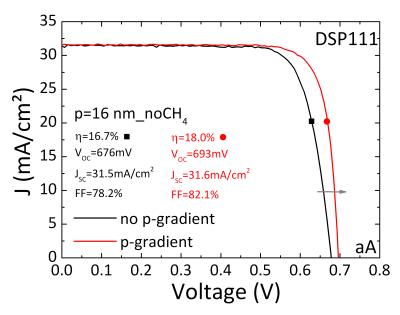

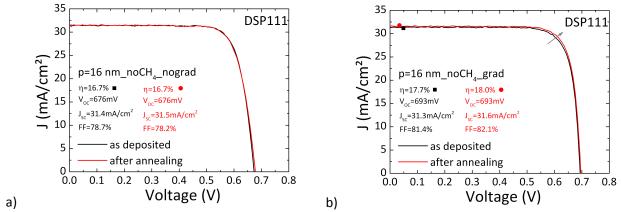

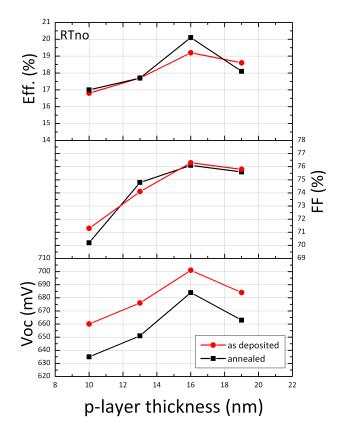

|   | 4.2.2.c             | Impact of a p-layer gradient on the performance of textured SHJ solar cell                                                   | . 185 |

|   | 4.2.2.d             | Impact of the (p++)a-Si:H layer thickness on the performance of flat and textured                                            |       |

|   | graded S            | SHI solar cells                                                                                                              | . 190 |

| 5 C    | Conclusion             | 199 |  |  |  |  |

|--------|------------------------|-----|--|--|--|--|

| 5.1    | Achievements           | 200 |  |  |  |  |

| 5.2    | Prospects              | 202 |  |  |  |  |

| Refe   | rences                 | 205 |  |  |  |  |

| List o | List of Publications22 |     |  |  |  |  |

| List o | ist of Acronyms223     |     |  |  |  |  |

| List o | ist of Figures         |     |  |  |  |  |

| List o | List of Tables         |     |  |  |  |  |

# Introduction

According to the BP statistical Review of World Energy published in June 2014, the total consumption of primary energy reached 12,730.4 Mtoe<sup>2</sup> in 2013. This approximately equals 147,668 TWh, i.e., the equivalent of 16,857 1GW power plants running at full capacity throughout a whole year. The three dominant fossil fuels, i.e., oil, natural gas and coal are the main energy sources to meet this need. Indeed, they together represent 86.7 % of this value. 87 mln barils of crude oil, 9.23 bln m<sup>3</sup> of natural gas and 16.0 Mton of coal were produced daily in 2013 to cope with the growing demand. If we follow the estimation of the world documented reserves, at this production rate only 53, 55 and 153 years of oil natural gas and coal remain on the planet, respectively. Moreover, according to the ALCEN foundation for the energy knowledge, between 1971 and 2009, the world energy consumption experienced a 40 % increase. This evolution is due to the combination of a stable consumption by industrialized countries (usually also members of OCDE) with the increasing demand in energy by fast-growing newlyindustrialized countries<sup>3</sup>. Today's energy consumption landscape brings complex challenges in the short term as well as in the longer term. The world demographic growth has an almost mechanical impact on energy consumption (+1.5% per year). Then, the increasing level of life in developed countries has direct consequences on the energy production per inhabitant (1.5% per year). However, this picture is far from frozen at this stage. Advances made in the energy production, distribution and consumption have managed to lower the energy consumption by 1% per year. Furthermore, political decisions surrounding energy production and consumption, which aim at acting against a predicted global warming in the world, will definitely shape tomorrow's landscape. The main leverages world governments intend to use are the optimization of energy consumption behaviors and efficiencies, as well as the development of renewable energies (hydroelectricity, wind power, biomass, geothermal, solar power...).

In 2010, the world production of renewable energies reached 11,392 GWh per day on average. This represents a very impressive 19.6% share of the electricity world production. Moreover, between 2000 and 2010, the electricity produced from renewable sources experienced a 43% growth. However, solar power represents only 91 GWh per day, which is a little less than 1% of the daily production of

http://www.bp.com/content/dam/bp/pdf/Energy-economics/statistical-review-2014/BP-statistical-review-of-world-energy-2014-full-report.pdf

<sup>&</sup>lt;sup>2</sup> 1 toe represents the amount of energy released by burning one ton of crude oil. It approximately equals 42 GJ or 11.63 MWh. However, one has to take into account that different crude oils have different calorific values.

<sup>&</sup>lt;sup>3</sup> China for example, has seen its energy consumption triple from 1990 to 2008. Its share in the world consumption went from 7.5% to 16.4% and the consumption per inhabitant in China is now equal to the consumption per inhabitant in the world. During the same period, the consumption in Africa increased by 50% but remains quite a small part of the total world consumption (5.7% for more than 15% of the world population).

renewable energies. Indeed, among these renewable energies, hydroelectricity plays the biggest role by providing 83% of the renewable energy produced, thanks to the recent developments in China and Brazil notably. Nevertheless, one should keep in mind that the use of solar power for electricity generation is quite recent. Moreover, between 2000 and 2010, solar power has been the fastest growing renewable energy with a spectacular average increase of 38% per year. The main contributor to this growth is solar photovoltaics (84 GWh per day). Photovoltaics allows for the direct transformation of the energy contained in a beam of light into electricity. This conversion is made possible through the photoelectric effect which was discovered in 1839 by Antoine and Edmond Becquerel and explained for the first time by Albert Einstein in 1905. In the meantime, in 1883, the first solid state photovoltaic cell was built out of selenium and reached a little less than 1% conversion efficiency[1]. The "switch" to silicon was made when Bell Labs managed to fabricate the first silicon solar cells which exhibited a more significant conversion efficiency exceeding 6%[2][3]. As a result, 90% of the PV market today is silicon-based. Indeed, silicon is an abundant earth element and cell efficiencies have been improved up to 25% on an industrial production line by the SunPower corporation in 2014[4]. Since the sun is an infinite source of energy – it provides 10,000 times the amount of energy that the humans currently consume – it has the potential to be used as a source of energy if efficiently converted, namely via PV systems. Electricity generation by solar cells remained quite expensive for many years in comparison with grid electricity. It is however becoming more and more competitive today, reaching prices as low as 0.10-0.20 €/kWh. We therefore have today a great opportunity to make solar power part of the world energy mix. The energy company TOTAL S.A. for example, is one of the six supermajor oil companies in the world with an oil and gas production of 2,299 kboe/day in 2013<sup>4</sup>. With nearly 99,000 employees in over 130 countries, it is however dedicated to rethink the energy mix of the future. In April 2011, Total bought 60% of the photovoltaic Silicon Valley company SunPower for US\$1.38 billion. They now own approximately 66% of the company<sup>5</sup>. As a result, the world's biggest solar power plant is now under construction. It is known as the Solar Star Project (formerly Antelope Valley Solar Project) and represents a 579-megawatt solar installation. When completed, the Solar Star Project should deliver enough electricity to power the equivalent of approximately 255,000 homes<sup>6</sup>. One of the greatest challenges photovoltaics needs to address today in order to be more attractive on the energy market is, therefore, to increase the cell efficiencies while reducing its production costs. Silicon heterojunction solar cells are a good candidate to achieve this goal. Indeed, as we will see later, these combine the attractive features of requiring low-cost process steps, for example by using process temperatures below 200°C, and yielding very high efficiencies, namely 24.7% in 2014[5]. The generation of photocurrent by a SHJ was first demonstrated by Fuhs et al. in 1974[6], while the first solar device was fabricated in 1983 by Hamakawa and coworkers[7] using polycrystalline silicon and a-Si:H to create the so-called Honeymoon cell. In the meantime, the outstanding passivating properties of a-Si:H in its intrinsic (undoped) form was demonstrated by Pankove et al.[8] and Sanyo improved the SHJ structure by adding a thin intrinsic buffer

<sup>&</sup>lt;sup>4</sup> 1 boe=barrel of oil equivalent, i.e., the approximate energy released by burning one barrel (42 U.S. gallons or ~159 litres) of crude oil.

<sup>5</sup> http://investors.sunpower.com/

<sup>6</sup> http://us.sunpower.com/solar-star/about/

layer at the (p)a-Si:H/(n)c-Si interface, leading to the famous HiT structure<sup>7</sup>[9]. It may be surprising however, for the reader to see the involvement of the TOTAL Company in the field of SHJ since the company produces solar panels made of silicon homojunction solar cells. In this Ph.D. thesis though, stress was not put on improving existing SHJ solar cells for direct industrial applications. SHJ solar cell performance highly relies on the quality of the interface between two materials: the crystalline silicon (c-Si) substrate and the hydrogenated amorphous silicon (a-Si:H) layer of opposite doping types deposited by PECVD. Hence, by studying SHJ solar cells one can actually study the passivating properties of a-Si:H for c-Si substrates. Results obtained through such a study can then be used to understand how the c-Si substrate interacts with its passivating layer. Therefore, passivation topics are of great interest for the TOTAL company and can perhaps lead to applications to homojunction solar cells using a low-thermal budget and low-cost a-Si:H instead of the usual SiO<sub>2</sub> and a-SiN<sub>x</sub>:H materials that are deposited at much higher temperatures. As a matter of fact, Panasonic reported in 2014 a 25.6% solar cell by combining the SHJ concept with the Interdigitated Back-Contact or IBC architecture[10]. This shows well that records can be beaten by combining different technologies.

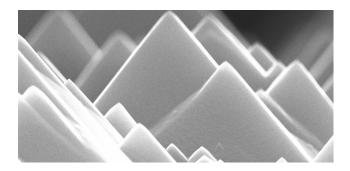

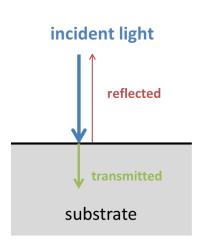

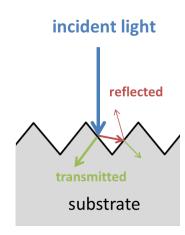

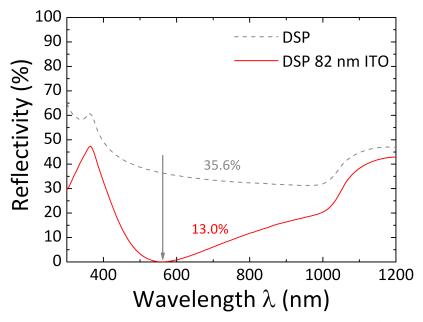

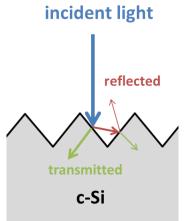

For these reasons, SHJ solar cells have been studied at LPICM since 2007. Jérôme Damon-Lacoste was the first Ph.D. student to tackle the topic of passivation of c-Si by a-Si:H deposited by PECVD at lowtemperature. He bequeathed us with important insights on the a-Si:H/c-Si interface and developed the know-how on passivation at LPICM. His work resulted in the fabrication of a 17.0% champion SHJ solar cell on a 5x5 cm<sup>2</sup> p-type substrate[11]. In 2011, Martin Labrune continued this work by studying the passivation of flat n-type substrates using the same technique and the same reactor. His work resulted in the fabrication of a 17.2% champion SHJ solar cell on 2x2 cm<sup>2</sup> n-type substrate[12]. All of these results were obtained on flat 280-µm thick high-quality TOPSIL wafers. At this point, considering the high reflectance of a flat silicon substrate, i.e., ~37% and the high levels of passivation obtained under our conditions, i.e., high effective lifetimes above 10 ms and implied Vocs close to 725 mV, the main path to higher efficiencies obviously had to go through the improvement of the device's optical properties. Indeed, as can be seen in Figure 1-1, by fostering light-trapping the reflectance can be lowered and the transmission of the light into the device bulk enhanced. Thanks to this, more photons can be absorbed by the c-Si substrate and, thus, more electron-hole pairs generated. As a result, we can potentially witness an improvement of the final short-circuit current (Jsc). It may sound easy at this stage: all we would have to do was swap the flat c-Si substrates for textured ones and fabricate higher-efficiency SHJ solar cells. The increase in J<sub>SC</sub> however, and resulting increase in the final conversion efficiency are only possible if the introduction of a textured c-Si substrate does not induce new recombination processes and extra electron-hole pairs generated through light-trapping are not lost. Moreover, the fact that we are no longer dealing with a flat substrate implies that the deposition times must be adapted to fit the newly obtained micrometer-high random pyramid landscape.

The challenges arising when swapping flat c-Si wafer for textured ones were partly unveiled at the end of Martin Labrune's Ph.D. thesis in 2011 ([12] pp. 123-127). Textured monocrystalline c-Si wafers were provided by the CEA INES within the frame of the HETSI European project.

<sup>&</sup>lt;sup>7</sup> Heterojunction with Intrinsic Thin layer.

Figure 1-1 — Schematic representation of the impact of surface texturing on the substrate light-trapping properties: the part transmitted to the substrate (green beam) is enhanced while the reflected part (red beam) is reduced.

In this case, n-type substrates of various quality and surface states were tested, and they all led to quite low effective lifetimes, i.e., below  $2\cdot10^{-5}$  s. Higher passivation levels could be reached by using textured multicrystalline substrates obtained within the framework of the French ANR project MULTIXEN, i.e., close to  $3\cdot10^{-4}$  s. However, these remained one order of magnitude lower than what could be obtained on flat monocrystalline c-Si substrates (~3 ms). These low effective lifetimes induced significant drops in the finalized device  $V_{oc}$ s that was also observed by other labs[13] while, in our case, almost no increase in  $J_{sc}$  could be observed despite the lower reflection of our textured substrates. As a result, the efficiencies obtained on textured wafers were much lower than those obtained on their flat counterparts, i.e., between 9.4 and 12.8% instead of the usual 15-17%, thus leading to what could seem like a pointless effort. Since Martin Labrune's thesis mainly focused on the passivation and epitaxial growth on flat c-Si wafers, the study of textured c-Si substrates did not go any further. Therefore, many open questions remained unanswered:

- How can we optimize the light-trapping properties of our c-Si substrates and increase the J<sub>SC</sub> of our finalized SHJ devices?

- What are the origins of the passivation drops observed at LPICM and by other labs while swapping flat wafers for textured ones?

- How can we compensate these passivation losses adequately to reach passivation levels comparable to what can be obtained on flat c-Si substrates?

- How can we increase the  $V_{\text{oc}}$  of our textured finalized SHJ solar cells towards reaching efficiencies greater than 19%?

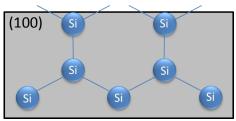

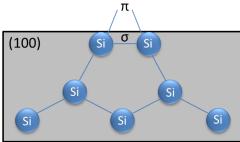

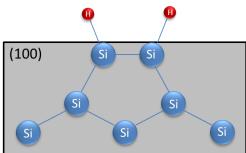

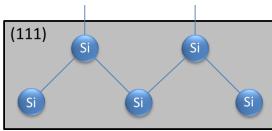

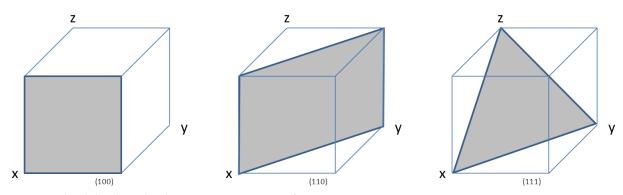

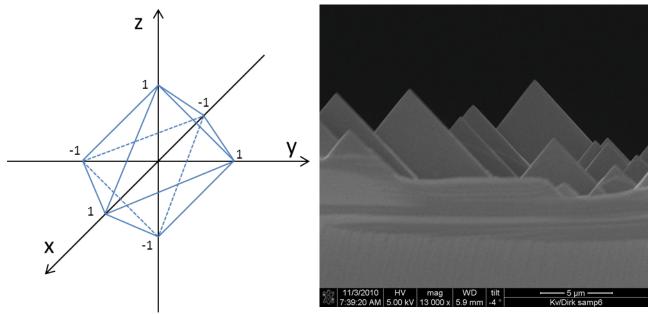

These are the challenges that I was facing when I started this Ph.D. thesis. **Chapter I** is dedicated to the introduction to basic concepts of solar power and semiconductor physics: the solar spectrum, pn junction and diode equation, recombination mechanisms within the c-Si bulk... It also presents an important material: hydrogenated amorphous silicon (a-Si:H). Its main properties are unveiled, as well as its growth mechanism. This chapter also introduces the deposition technique used throughout this thesis. **Chapter II** introduces the concept of passivation of the c-Si surface: the a-Si:H/c-Si heterojunction the interface and band offsets. It also describes the (100) and the (111) c-Si crystallographic orientations

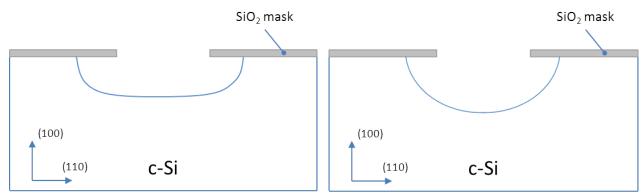

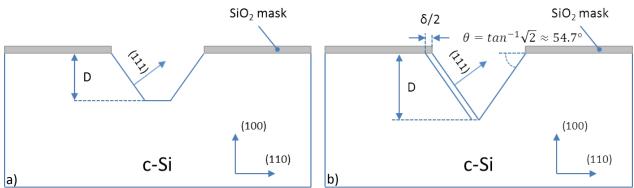

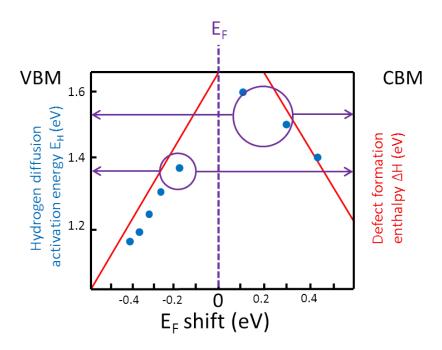

are described as it is crucial to understand texturing mechanisms. Finally, the recombination mechanisms described earlier for the c-Si bulk are adapted to surface studies to yield the effective lifetime formalism. Chapter III brings us to the heart of my study. I imagined that the best way to understand the impact of the c-Si surface states on the effective lifetimes of our textured samples would be to go deeper into the micromachining of c-Si by studying the different ways to texture crystalline silicon. Not only did I want to choose the texturing technique, but I also wanted to monitor the texturing process from the industrial as-cut wafer down to its loading into the PECVD reactor. This is why this chapter starts with a literature study coupled with the experimental results that allowed me to choose the best texturing process according to very precise criteria. This part is followed by a thorough study that combines PCD measurements and HR-TEM/STEM analysis to understand the impact of texturation on a-Si:H growth and passivation. It results in a new paradigm for textured c-Si surface and leads us to use a very specific technique to improve the a-Si:H/c-Si interface. This technique is then applied to SHJ solar cells in Chapter IV. Indeed, passivation of textured c-Si wafers is greatly improved thereby. Making this improvement applicable to enhance the conversion efficiency of SHJ solar cells takes us a step further. The third chapter's conclusions are examined on SHJ solar cell precursors made out both of flat (111) and textured c-Si wafers. This study is first carried out with effective lifetime measurements whereupon SHJ solar cells are finalized and the improvements in terms of performance are analyzed. To underscore our observations, two types of texturing recipes are used for this study. This last chapter ends with a prospective but quite interesting study on the degradation of the passivation upon the deposition of TCO by PVD. It unveils the very particular role of the p-layer in the degradation of the a-Si:H/c-Si interface.

# 1 Basics of photovoltaics

| 1.1 | Solai   | r energy                                                                | 22 |

|-----|---------|-------------------------------------------------------------------------|----|

| 1.  | 1.1     | Air Mass                                                                | 22 |

| 1.  | 1.2     | Solar spectrum                                                          | 23 |

| 1.2 | Semi    | iconductor physics applied to solar devices                             | 25 |

| 1.  | 2.1 E   | Basics of semiconductor physics                                         | 25 |

|     | 1.2.1.  | a Semiconductor materials                                               | 25 |

|     | 1.2.1.  | b Photon energy and bandgap                                             | 26 |

|     | 1.2.1.0 | Doped semiconductors                                                    | 28 |

|     | 1.2.1.0 | d Semiconductors at thermal equilibrium                                 | 28 |

|     | 1.2.1.6 | e Semiconductors under light excitation                                 | 29 |

| 1.  | 2.2 F   | PN junction                                                             | 30 |

|     | 1.2.2.  | a Formation of a pn junction                                            | 30 |

|     | 1.2.2.  | b Diffusion and drift                                                   | 31 |

|     | 1.2.2.  | Diode equations                                                         | 32 |

| 1.3 | Silico  | on for PV applications                                                  | 34 |

| 1.  | 3.1 E   | Bulk recombination and lifetime                                         | 34 |

|     | 1.3.1.  | a Radiative recombination: relaxation by photon emission                | 35 |

|     | 1.3.1.  | b Band-to-band Auger recombination: energy transfer to a charge carrier | 36 |

|     | 1.3.1.0 | Shockley-Read-Hall recombination: defect-assisted recombination         | 37 |

|     | 1.3.1.0 | d Bulk lifetime                                                         | 39 |

| 1.  | 3.2 H   | Hydrogenated amorphous silicon                                          | 39 |

|     | 1.3.2.  | The a-Si:H network and its consequences on the density of states        | 40 |

|     | 1.3.2.  | b Plasma-Enhanced Chemical Vapor Deposition (PECVD)                     | 43 |

|     | 1.3.2.0 | a-Si:H growth mechanism model                                           | 47 |

|     | 1320    | d ARCAM reactor                                                         | 48 |

# 1.1 Solar energy

The sun does emit light with a specific spectrum, and its intensity varies as a function of the wavelength. It will more or less match the radiation of a blackbody brought to a temperature of 5,800 K. However, as light travels through the atmosphere, it is attenuated by scattering and absorption. Thus, the characteristics of the sun's light impinging the Earth will vary depending on:

- scattering and absorption effects in the atmosphere

- atmosphere feature variation (thickness, chemical content...)

- data collecting latitudes

- earth's relative position with respect to the sun (seasons and time of the day)

These effects will modify the intensity, spectrum and angle of incidence of light reaching the Earth. Indeed, solar radiation has to travel through the molecules contained in the atmosphere. Ozone  $(O_3)$ , carbon dioxide  $(CO_2)$  and water vapor  $(H_2O)$ . These gases absorb photons of energy close to their molecule bond energy. As a result, most of the far IR light above 2  $\mu$ m is absorbed by carbon dioxide and water vapor, whereas ozone absorbs the main part of the light below 300 nm. For these reasons, solar cells need to be designed not for a single wavelength but for the *energy distribution* that comes from the sun and manages to get through to the Earth.

## 1.1.1 Air Mass

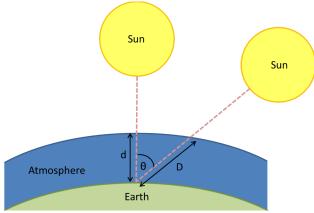

Huge amounts of data have been collected by laboratories, governments, the PV industry and aerospace community to build extraterrestrial and terrestrial standards for the solar spectral irradiance distributions. These standards are defined using the notion of Air Mass. It is the path length of light travelling through the atmosphere normalized by the shortest possible path, i.e., when the sun is overhead (zenith angle equals to zero). As can be seen in Figure 1-1, d<D and an angle  $\theta$  separates the two different paths.

Figure 1-1 – Sunlight impiging the surface of the Earth at a zenith angle equal to 0 travels a distance d. When at an angle  $\theta$ , the distance is D with d<D. We can define the so-called Air Mass by taking the inverse of the cosine of  $\theta$ .

Air Mass can be expressed using the following relation:

$$AM = \frac{1}{\cos(\theta)} = \frac{d}{D} \tag{1}$$

Thus, Air Mass 1 or AM1 corresponds to an angle  $\theta$  equal to  $0^{\circ}$ , i.e., when the sun is overhead. The range AM1 to AM1.1 ( $\theta$ =0° to  $\theta$ =25°) is useful when testing solar cell performances in equatorial and tropical regions. Likewise, the AM2 ( $\theta$ =60°) to AM3 ( $\theta$ =70°) range is useful at high latitudes such as in northern Europe. Nevertheless, most of the biggest population hubs and, hence, their solar installation and industry lie in temperate latitudes, i.e., on either sides of the Earth's 38<sup>th</sup> parallels. As a result, AM1.5 representing the spectrum at mid-latitudes ( $\theta$ =48.2°) has been commonly used as an international standard for the research community and the PV industry since the 1970s[14]. Moreover, it stands for a good average value of the yearly variations induced by season-related periodic angle changes<sup>8</sup>. Finally AMO is used by the aerospace community and represents the spectral solar irradiance received from the sun before it crosses the atmosphere, i.e., before absorption effects become significant. It should be noted that silicon solar cells are not very sensitive to the parts of the spectrum lost in the atmosphere. The crystalline silicon bandgap makes silicon solar cells more efficient at AM1 than AM0 because they cannot make much use of the very high and very low energy radiation. The efficiency can be lower at AMO but the total output power is still higher because there is still an additional and useful range of energy. Likewise, the shape of the spectrum does not significantly change with further increases in atmosphere thickness. As a result, cell efficiencies do not vary a lot for AM numbers above 1.

## 1.1.2 Solar spectrum

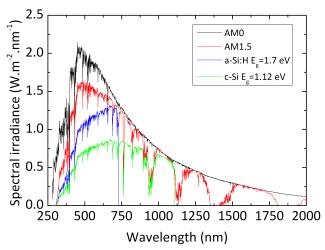

In Figure 1-2 are plotted the AMO and AM1.5 spectra together with the crystalline silicon (c-Si) and hydrogenated amorphous silicon (a-Si:H) maximum irradiance fraction utilized. Here, we clearly see the losses induced by atmospheric absorption since AMO's irradiance is much higher than AM1.5, especially in the visible range.

Figure 1-2 - AMO and AM1.5 solar irradiance spectra together with the maximum utilized energies for a-Si:H and c-Si.

Moreover, we can see that c-Si and a-Si:H are both semiconductors which cannot take full advantage of the sun's irradiance since their maximum utilized irradiance fractions are lower than the AM1.5 spectrum. This is due to the impossibility to collect the so-called *hot electrons*.

<sup>&</sup>lt;sup>8</sup> Wintertime performance in temperate latitudes correspond to an AM coefficient greater than 2 at all times of the day, even for latitudes close to the subtropical limit, i.e., 38°.

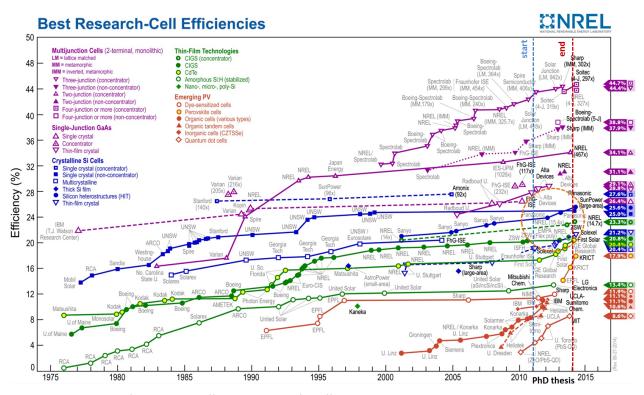

Figure 1-3 – Evolution of research-cell efficiencies in time for different PV technologies. The blue and red dashed vertical lines indicate the starting (2011) and ending (2014) years of my Ph.D. thesis, respectively.

Indeed, when light of energy higher than the semiconductor energy bandgap Eg promotes an electron from the valence band to the conduction band, the electron is transferred to a state that is higher than the conduction band edge by  $\delta E$ . As a result, instead of just recombining by giving back an energy corresponding to  $E_g+\delta E$ , the electron will first release the extra energy  $\delta E$  via thermalization. As a result, the most efficient use of light occurs around the very value of Eg. All higher energy light is absorbed but δE will always be lost, resulting in the spectra shown in Figure 1-2 for c-Si and a-Si:H. One has also to keep in mind that c-Si has an energy bandgap of 1.12 eV (~1110 nm) and a-Si:H of roughly 1.7 eV (~730 nm). This means that these semiconductors will not be able to absorb any of the light of lower energy (higher wavelength). All light above 1110 nm is therefore intrinsically lost for c-Si-based solar cells. The same goes for a-Si:H with all sunlight beyond 730 nm. Increasing the semiconductor bandgap should therefore solve the thermalization-related losses whereas decreasing its value should widen the absorbed sun spectral range. An optimum has been suggested by Shockley and Queisser in 1961. It implies an "ideal" energy bandgap of 1.4 eV and would get us to conversion efficiencies of 30%[15]. To overcome this limit, multi-junction architectures have been proposed by other PV branches. These include several absorbers of various energy bandgaps which, in turn, allow for covering a wider range of the AM1.5 spectrum while keeping the aforementioned thermalization losses as low as possible. These are mainly made out of III-V materials but some include cheaper and simpler materials and alloys, made out of a-Si:H, microcrystalline silicon (μc-Si) or polymorphous silicon (pm-Si:H)[16]. Other new hybrid structures have been reported, combining organic and inorganic materials[17]. Namely, an innovative visible-light sensitizer made out of organometal halide perovskites[18] has allowed the KRICT <sup>9</sup>to reach an impressive conversion efficiency of 17.9% in 2013[19] and to catalyze research within this branch[20]. Figure 1-3 shows a chart that is very popular in the PV community. It shows the evolution of the best research-cell efficiencies with time since 1975 until 2014. It is taken from the NREL<sup>10</sup> website<sup>11</sup> and is commonly used to situate one's work context. From this curve we can see for all kinds of cell architecture, their history and latest efficiency records. In particular, we can situate the context in which this Ph.D. work was carried out between 2011 and 2014 (blue and red dashed lines). Sanyo was the record holder at that time<sup>12</sup> for the best silicon heterojunction solar cell with an efficiency of 23%[21]. However, in three years, advances have been made in this particular field, leading to the impressive 24.7% record efficiency in 2014 by the same company (now owned by Panasonic)[5].

# 1.2 Semiconductor physics applied to solar devices

## 1.2.1 Basics of semiconductor physics

## 1.2.1.a Semiconductor materials

A semiconductor is a material with specific conductivity properties. Indeed, they can neither be completely considered as conductors nor as insulators. They have enough electrons to fill their valence bonds but no free electrons to make them conductive.

|                  |                  |                  |                  |                  |                  |                  | VIIIA            |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|                  |                  | IIIA             | IVA              | VA               | VIA              | VIIA             | ²He              |

|                  |                  | <sup>5</sup> B   | <sup>6</sup> C   | <sup>7</sup> N   | <sup>8</sup> O   | <sup>9</sup> F   | <sup>10</sup> Ne |

| IB               | IIb              | <sup>13</sup> Al | <sup>14</sup> Si | <sup>15</sup> P  | <sup>16</sup> S  | <sup>17</sup> Cl | <sup>18</sup> Ar |

| <sup>29</sup> Cu | <sup>30</sup> Zn | <sup>31</sup> Ga | <sup>32</sup> Ge | <sup>33</sup> As | <sup>34</sup> Se | <sup>35</sup> Br | <sup>36</sup> Kr |

| <sup>47</sup> Ag | <sup>48</sup> Cd | <sup>49</sup> In | <sup>50</sup> Sn | <sup>51</sup> Sb | <sup>52</sup> Te | <sup>53</sup> I  | <sup>54</sup> Xe |

| <sup>79</sup> Au | <sup>80</sup> Hg | <sup>81</sup> TI | <sup>82</sup> Pb | <sup>83</sup> Bi | <sup>84</sup> Po | <sup>85</sup> At | <sup>86</sup> Rn |

Table 1-1 – Selected part of the periodic table of elements. The blue portion shows the most common semiconductors. They can either be intrinsically semiconducting or their combination can result in useful semiconductor materials.

As a result, they are insulating when no energy is provided to their system but can become conductive otherwise, by raising the temperature, applying an electric field or under light excitation for example. They can either come from the column IV of the periodic table or from a combination of two different

-

<sup>9</sup> Korean Research Institute of Chemical Technology

<sup>&</sup>lt;sup>10</sup> National Renewable Energy Laboratory

<sup>11</sup> www.nrel.gov

<sup>&</sup>lt;sup>12</sup> In December 2009, Sanyo became a subsidiary of Panasonic when a \$4.5 bln acquisition of a 50.2% stake was completed. In July 2010, Panasonic announced that they would acquire the remaining shares of Sanyo. More information on http://panasonic.net/sanyo/news/2012/12/

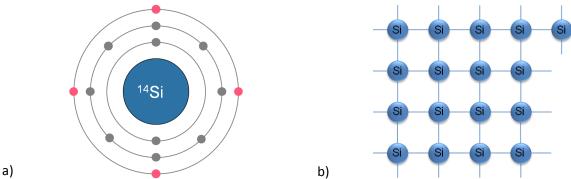

columns (III-V or II-VI), as shown in Table 1-1. For example, Si or Ge are intrinsically semiconductor materials whereas compounds such as GaAs (a binary compound), InGaAs (a ternary compound) or AllnGaP (a quarternary compound) can result in the creation of useful semiconductors. Silicon exhibits an electronic structure of 3s<sup>2</sup>3p<sup>2</sup>. As can be seen in Figure 1-4a), each silicon atom has 4 valence electrons on their external orbital. Therefore, each Si atom can share an electron with its neighboring atom to form chemical bonds. This results in the crystalline lattice described in Figure 1-4b) where all the individual atoms are linked together by covalent bonds. The electrons in these covalent bonds are held in place by these bonds and hence, they are localized and must stay in the region surrounding the atom. These electrons cannot move or jump to a higher energy level and therefore are not considered free. Thus, they cannot participate in conduction at absolute zero, i.e., when no energy is provided to the system. The minimum energy required is called the energy bandgap. It is also called the forbidden energy bandgap since any lower energy value does not allow such a transfer from a lower state of energy to a higher state of energy to take place, i.e., there is no intermediate state. When an electron leaves a lower state of energy to a higher one, it leaves an empty space behind. A negative charge is therefore missing at this level and can be considered a positive charge. This introduces the very important notion of holes. In solar cells, free electrons and holes as well as their number and energy are crucial for their operation.

Figure 1-4 — Core shell structure of silicon (a). Pink circles represent valence electrons as opposed to grey circles which are closer to the nucleus. Schematic representation of covalent bonds in a silicon crystal lattice (b). Each line represents two electrons that are shared to form a covalent bond.

## 1.2.1.b Photon energy and bandgap

When a photon hits the surface of a semiconductor, it can be reflected, absorbed or transmitted. Obviously, reflection and transmission are here considered losses since in solar devices we need to absorb the photons in order to transform them into an electrical current. To determine if light will be efficiently utilized by the semiconductor one needs to consider two parameters: the photon energy and the semiconductor bandgap. When  $E_{ph} < E_g$ , the photon is not absorbed. In some cases where the semiconducting material contains some localized states within the bandgap, the photon can be absorbed, otherwise not. When  $E_{ph} > E_g$ , the photon is absorbed by the semiconductor but the excess energy  $\delta E$  with respect to  $E_g$  will be lost via thermalization, as mentioned in 1.1.2. When  $E_{ph} = E_g$ , we find ourselves in the most efficient case of absorption since the energy is completely used for the generation of an electron-hole pair. Now, for  $E_{ph} \ge E_g$  the absorption coefficient is not constant but strongly dependent on  $E_{ph}$ . Indeed, a photon will be absorbed depending on its ability to interact with an electron. With increasing  $E_{ph}$  the absorption will become more efficient, but not the photon energy utilization.

One can simply express the absorption coefficient  $\alpha$  by:

$$\alpha = \frac{4\pi k}{\lambda} \tag{2}$$

where  $\lambda$  is the wavelength in nm<sup>13</sup> and k the extinction coefficient. This in turn will get us to the absorption depth  $1/\alpha$  or  $\alpha^{-1}$ . It is a useful parameter as it gives the distance into the material at which the light intensity drops by a factor 1/e. Indeed, as can be seen in Figure 1-5, when  $E_{ph}$  is high or  $\lambda$  short (UV/blue)  $\alpha$  will be large and, therefore, the light will be absorbed close to the semiconductor surface. Likewise, when  $E_{ph}$  is low or  $\lambda$  long (red/IR)  $\alpha$  will be small and, therefore, the light will go deeper inside the material.

Figure 1-5 - Schematic representation of the evolution of the absorption depths as a function of the incident energy photon Eph.

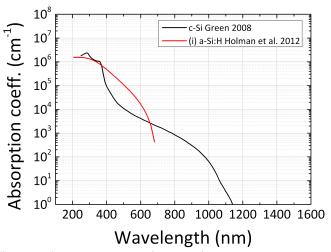

Figure 1-6 shows the absorption coefficient of c-Si (taken from [22]) and a-Si:H (taken from [23]). The data presented show that crystalline silicon "cuts" right after crossing 1,100 nm, which corresponds to its energy bandgap. Likewise, right above 700 nm light absorption inside a-Si:H vanishes. Again, this corresponds approximately to an energy bandgap of 1.7 eV, which is typical for intrinsic a-Si:H.

Figure 1-6 – Absorption coefficient  $\alpha$  of c-Si and a-Si:H as a function of the wavelength at 300K.

This is crucial for solar cell performance analyses since this will determine where the charge carriers are generated and, hence, their recombination probability. As a result, their extraction efficiency as a useful current will be impacted. With zero reflection, the intensity of the light after impinging the semiconductor surface will depend exponentially on  $\alpha$  through the relation:

$$I = I_0 e^{-\alpha x} \tag{3}$$

$<sup>^{13}</sup>$  To get the result in cm $^{-1}$ , one needs multiply k by  $10^{7}$ .

Where  $\alpha$  is in cm<sup>-1</sup>, x is the depth at which the intensity is calculated and I<sub>0</sub> is the incident light intensity before it hits the semiconductor surface. Thanks to this, we can calculate the generation rate of electronhole pairs G:

$$G = \alpha N_0 e^{-\alpha x} \tag{4}$$

where N<sub>0</sub> is the photon flux hitting the surface in photons·cm<sup>-2</sup>·s<sup>-1</sup>. Indeed, if we assume that 1 photon is responsible for the creation of 1 electron-hole pair, then the change of intensity can be directly used to express G. Thus, deriving Eq. 3 will result in Eq. 4, which tells us that the generation is at its highest rate close to the semiconductor surface whilst decreasing exponentially further away.

## 1.2.1.c Doped semiconductors

A significant feature of semiconductors is their ability to be doped. Indeed, by inserting specific atoms called dopants inside their crystal lattice an excess (n-type doping) or a deficiency (p-type) of electrons can be created, leading to a much enhanced conductivity of the material<sup>14</sup>. These tuned semiconductors are called extrinsic or doped. The conductivity will now depend on the amount of dopant inserted inside their lattices. A 1cm<sup>3</sup> sample of silicon contains approximately 5·10<sup>22</sup> atoms. While in metals each atom provides at least one free electron for conductivity, here the silicon atoms will provide approximately 10<sup>10</sup> free electron and 10<sup>10</sup> free holes. The addition of very small amounts of a doping impurity such as phosphorus will enhance the conductivity of silicon greatly by a factor of 10,000. This is made possible because it simply adds extra electrons, which become available for conduction. When adding extra electrons (n-type doping) or extra holes (p-type doping) to the semiconductor, we introduce impurities to the crystal lattice in the form of atoms that are foreign to the original material. This introduces states within the forbidden bandgap. If these are localized near the midgap, i.e., close to the Fermi level, they do not make the charge carrier transfer from the valence band to the conduction band any easier. However, if these states are closer to the valence and conduction band edges, they make the jump of the carriers from the doping states possible. Indeed, with n-doping will arise a donor level called ED whereas p-type doping will create an acceptor level called E<sub>A</sub>. These two types of doping are crucial to solar cells since they are actually built with a combination of both. To go further into details, one is referred to textbooks written by Stephen Fonash[24] or Jenny Nelson[25]. A few parameters will nevertheless be expressed in the following sections as they are key to solar cell operations.

# 1.2.1.d Semiconductors at thermal equilibrium

At thermal equilibrium, the distribution function of the electrons at an energy E is defined by Fermi-Dirac statistics. It states that the number of electrons present within the conduction band is equal to:

$$n = \int f_{F-D}(E)\rho_C(E)dE \tag{5}$$

where  $f_{\text{F-D}}$  represents the occupation probability and  $\rho_{\text{C}}$  the number of possible states for the electrons.

$<sup>^{14}</sup>$  In fact, conductivity is the most widely spread parameter in physics. Glass has a conductivity close to  $10^{-11}$ - $10^{-15}$  S/m whereas silver yields the very high conductivity value of  $6.30 \cdot 10^{7}$  S/m.

As a result we have:

$$n = N_C \exp\left(-\frac{E_C - E_F}{kT}\right) \tag{6}$$

where N<sub>C</sub> is the effective density of state within the conduction band<sup>15</sup>. The same statistics allow estimating also the number of holes present within the valence band through the relation:

$$p = \int (1 - f_{F-D}(E))\rho_V(E)dE$$

(7)

Where 1-  $f_{F-D}$  represents the hole occupancy probability<sup>16</sup> and  $\rho_V$  the number of possible states for the holes. As a result we have:

$$p = N_V \exp\left(\frac{E_V - E_F}{kT}\right) \tag{8}$$

where  $N_V$  is the effective density of state within the valence band<sup>17</sup>. A condition arises for the product of Eq. 6 by Eq. 8:

$$np = N_C N_V \exp\left(-\frac{E_C - E_F}{kT}\right) = N_C N_V \exp\left(-\frac{E_g}{kT}\right) = n_i^2$$

(9)

Where  $E_g=E_c-E_v$  and  $n_i$  is the intrinsic carrier concentration<sup>18</sup>. Note that this relation is always true as long as there is a Fermi level, i.e., as long as there is thermal equilibrium. This is no longer the case when we introduce a perturbation to the system. As we will be dealing with solar cells, it is of great importance to study the behavior of semiconductors under the most common perturbation they will be exposed to: light.

#### 1.2.1.e Semiconductors under light excitation

When a semiconductor is exposed to a perturbation such as a pulse of light, the electron populations in the valence and conduction band change. Because their relaxation time in each band is much lower than their relaxation time across the bandgap, they all stabilize momentarily in a quasi-thermal equilibrium within their respective bands. The Fermi level cannot be used anymore to define the electron occupancy. However, we can define a so-called *quasi-Fermi level for the conduction band*  $E_{Fn}$  and a *quasi-Fermi level for the valence band*  $E_{Fp}$ . As a result, the density of electron from Eq. 6 becomes:

$$n_{light} = N_C \exp\left(-\frac{E_C - E_{Fn}}{kT}\right) \tag{10}$$

<sup>&</sup>lt;sup>15</sup> Given a state density effective mass in the conduction band  $m_c$ =1.18,  $N_c$ =3.11·10<sup>19</sup> cm<sup>-3</sup> for crystalline silicon.

$<sup>^{16}</sup>$  The sum of the electron and hole occupancy probabilities must be equal to 1.

<sup>&</sup>lt;sup>17</sup> Given a state density effective mass in the conduction band  $m_v=0.81$ ,  $N_v=1.7\cdot10^{19}$  cm<sup>-3</sup> for crystalline silicon.

<sup>&</sup>lt;sup>18</sup> For crystalline silicon, Sproul and Green[26]have determined the value n<sub>i</sub>=10<sup>10</sup> cm<sup>-3</sup>.

whereas the density of holes from Eq. 8 becomes:

$$p_{light} = N_V \exp\left(\frac{E_V - E_{Fp}}{kT}\right) \tag{11}$$

In consequence, the product given in Eq. 9 becomes:

$$n_{light}p_{light} = n_i^2 \exp\left(\frac{E_{Fn} - E_{Fp}}{kT}\right)$$

(12)

where  $\mu = E_{Fn} - E_{Fp}$  is the quasi Fermi level splitting. This value is important for solar cell operations since it will define the upper bound of their  $V_{OC}$  value.

## 1.2.2 PN junction

The pn junction is the primary brick of all solar cell devices. In fact, it is the core of all rectifying devices such as diodes. In an electroluminescent diode for example, electrical current flows to produce light. In solar cell devices, the opposite event takes place. Sunlight hits the solar cell device (made of a pn junction in its core) and produces electrical current. We will see in the coming section how a pn junction transforms a photon of a given energy into an electrical current.

## 1.2.2.a Formation of a pn junction

A pn junction is created whenever joining two semiconductors of opposite doping. This can be done either by depositing a doped layer on a substrate or by diffusing dopants in a substrate that is already doped with a dopant of opposite sign. Whenever doing so, an n-type region with a high electron concentration is joined with a p-type region which has a high hole concentration.

Figure 1-7 - p- and n-type semiconductors before (left) and after (right) joining them to form a pn homojunction.

Therefore, the resulting semiconductor material is inhomogeneous in terms of free carrier concentration. In consequence, free charges start to move in order to reach homogeneity, resulting in a diffusion current. Of course, during this process, n-type dopants, i.e., phosphorus atoms, lose their free electron while p-type dopants, i.e., boron atoms, lose their extra hole. Because their initial number of protons is 15 and 5, for phosphorus and boron respectively, their ionized states will lead to a net charge of opposite sign left behind. Indeed these charges are bound to the crystalline lattice and unable to move. As a result, positive ion cores are exposed on the n side whereas on the p side, negative ion cores appear. An electric field will then arise and counter diffusion. Equilibrium is then reached when there is a

current that is equal and opposite to diffusion current. This can be expressed by saying that the overall electronic current is equal to zero or that:

$$n\mu_{\rho}\vec{\varepsilon} = -D_{\rho}\vec{\nabla}n\tag{13}$$

In other words, electrons simply do not move anymore, because of the electric field generated by the opposite signs now present on either sides of the interface between the n-doped and p-doped semiconductors. Therefore, there is an electrostatic potential such that:

$$\nabla^2 \phi(x) = -\frac{\rho(x)}{\varepsilon_0 \varepsilon_r} \tag{14}$$

This potential is called the *built-in potential* and is usually noted  $V_{bi}$ . This all happens at the interface between the two semiconductors. This region is called the *space-charge region* or *depletion region* since this part of the junction is depleted of free carriers. Its width is equal to the sum of the two components present on each side of the interface  $W_p$  and  $W_n$ . Their respective width depends on the doping levels on both sides. One should keep in mind that the higher the doping, the thinner the width since with a higher dopant concentration, the same fixed charge can be created on a much shorter length.

## 1.2.2.b Diffusion and drift

Considering Ohm's law, in presence of an electric field one can write the electronic current density as:

$$\vec{J}_e = ne\mu_e \vec{\varepsilon} \tag{15}$$

where n is the electron density, e is the electronic charge and  $\mu_e$  the electron mobility. This current which relates to the presence of an electric field is called *drift current*. Likewise, if the material is heterogeneous such that the free electron concentration varies with the position, a *diffusion current* arises which will tend to homogenize the semiconductor:

$$\vec{J}_{de} = eD_e \vec{\nabla} n \tag{16}$$

where  $D_e$  is the electron diffusion coefficient. Eq. 15 and 16 lead to the overall expression of the electronic current density:

$$\vec{J}_e = ne\mu_e \vec{\varepsilon} + eD_e \vec{\nabla} n \tag{17}$$

The same expression can be written for the holes by considering their density p, mobility  $\mu_h$  and diffusion coefficient  $D_h$ :

$$\vec{J}_h = pe\mu_h \vec{\varepsilon} - eD_h \vec{\nabla} p \tag{18}$$

These are the two most important equations in a pn junction as they determine the movements of all charge carriers through the expression of the overall current density:

$$\vec{J} = \vec{J}_e + \vec{J}_h \tag{19}$$

#### 1.2.2.c Diode equations

In the dark, the current flowing from a diode can be expressed through Shockley's law:

$$J(V) = J_0 \left[ \exp(\frac{qV}{nkT}) - 1 \right]$$

(20)

where  $J_0$  is the diode saturation current and n the ideality factor. In the case of a perfect diode, n should be equal to 1. Under light excitation, a photogeneration term  $J_{ph}$  is added to Eq. 20. However, under illumination one has to take into account parasitic effects in the form of resistances. As a result, a series  $(R_S)$  and shunt  $(R_{Sh})$  resistances are also introduced, resulting in the following equation:

$$J(V) = J_0 \left[ \exp(\frac{q(V - R_S J)}{nkT}) - 1 \right] + \frac{V - R_S J}{R_{Sh}} - J_{ph}$$

(21)

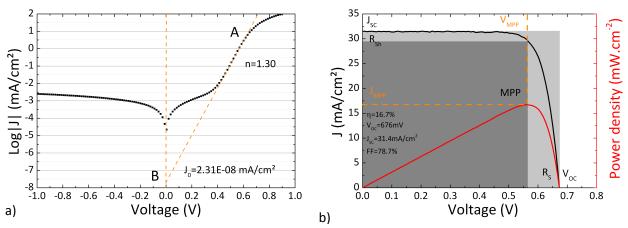

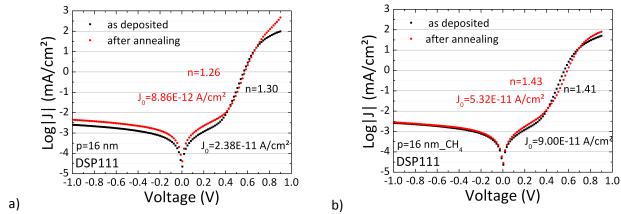

JV characteristics are the most powerful tool to assess solar cell performances. It indeed allows for the determining the ideality of the diode in the dark (parameters  $J_0$  and n) as well as the main cell parameters under illumination ( $V_{OC}$ ,  $J_{SC}$  and FF). When extracted under our standard conditions (AM1.5, 25°C), these parameters allow for the estimation of the final conversion efficiency of the solar cell. To perform such measurements during the thesis, an Oriel Sol3A Class AAA solar simulator fabricated by Newport was used. The model we had was a 94083A, which allowed us to carry out measurements under 1 Sun with certified 8"x8" homogeneity. Moreover, a temperature-controlled chuck with a water-cooled hot side, produced by Bentham, delivered a temperature stability of  $\pm 1^{\circ}$ C during our measurements. Although they can be represented in linear scale, dark JV characteristics are usually plotted using the logarithm of the absolute value of the current. This yields the typical curve shown in Figure 1-8a) in the -1 to 1 V bias range. By linearizing Eq. 20, one obtains:

$$\log J(V) = \log J_0 + \log \left[ \exp \left( \frac{qV}{nkT} \right) - 1 \right]$$

(22)

which can be approximated by:

$$\log J(V) \approx \log J_0 + \frac{qV}{nkT} \log e \tag{23}$$

Eq. 23 is now of the form v=Ax+B with:

$$\begin{cases} A = \frac{q \log e}{nkT} \\ B = \log J_0 \end{cases}$$

(24)

Considering kT=25 meV at RT,  $A \approx 17.34/n$  and that  $10^{\log(a)} = a$ , we finally have our expressions for the ideality factor n and the dark saturation current  $J_0$ :

$$\begin{cases} n \approx \frac{17.36}{A} \\ J_0 = 10^B \end{cases} \tag{25}$$

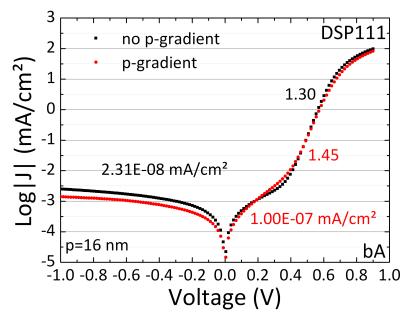

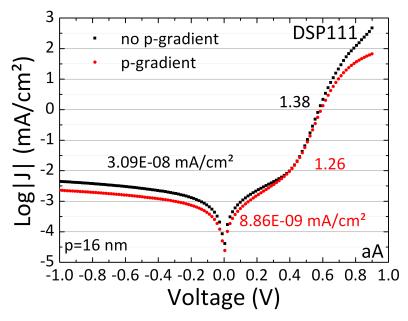

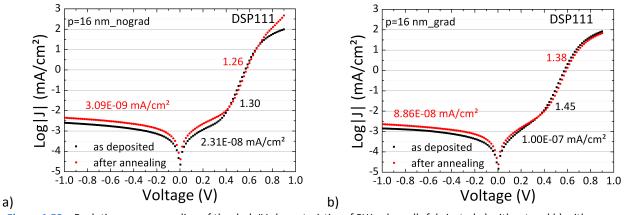

Therefore, by taking the slope A in the linear part of the dark JV characteristics (0.4<V<0.6 V bias range), we find the intercept B. In this case, A=13.8±0.03 while B=-7.78±0.01.

This yields for n and  $J_0$ :

$$\begin{cases} n = 1.26 \\ J_0 = 2.31 \cdot 10^{-8} \, mA/cm^2 \end{cases}$$

(26)

A typical JV characteristic under illumination is shown in Figure 1-8b). Three points are crucial for the determination of the solar cell performances:

- the point of open-circuit voltage, where no current flows: Voc.

- the point of short-circuit, where V=0: J<sub>SC</sub>,

- the point where the product of the voltage times the current reaches its maximum called the *maximum power point* or MPP.

The MPP determines a parameter called fill factor or FF. It is defined as the ratio:

$$FF = \frac{J_{MPP} \cdot V_{MPP}}{J_{sc} \cdot V_{oc}} \tag{27}$$

As can be seen on the curve, two rectangles are drawn. One represents the area determined by the  $J_{MPP} \cdot V_{MPP}$  product (dark grey) and the other one by the  $J_{SC} \cdot V_{OC}$  product (light grey). Their ratio yields an FF value of 78.7%. The series resistance (R<sub>S</sub>) accounts for all the resistive losses that can occur in the finalized device, from a resistive material inside up to the resistive losses induced by the metal contacts. For these reasons, we seek to reduce R<sub>S</sub> as much as possible. Contrariwise, the shunt resistance (R<sub>Sh</sub>) accounts for shunt losses that can occur because of undesirable conduction paths at the pn junction interface for example. For this reason, R<sub>Sh</sub> should be as high as possible to keep the blocking properties of the diode. These resistances can be estimated by taking the inverse of the slope at V<sub>OC</sub> and J<sub>SC</sub>, respectively.

Figure 1-8 – Typical JV characteristics a) in the dark and b) under illumination and the main parameters that can be extracted.

Thanks to the parameters extracted from the JV characteristics taken under illumination, one can estimate the conversion efficiency of the device trough the following relation:

$$\eta = \frac{J_{sc} \cdot V_{oc} \cdot FF}{P_{inc}} \tag{28}$$

where P<sub>inc</sub> is the power of the incident light.

# 1.3 Silicon for PV applications

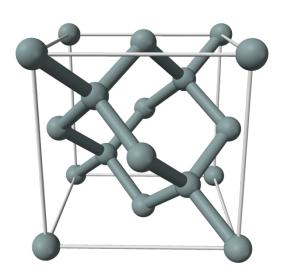

Crystalline silicon is the base of our cell architecture. It is an indirect-bandgap semiconductor with a diamond crystal structure. Its bandgap is 1.12 eV at 300 K. Because it is indirect, absorption is made more difficult than in the case of a direct bandgap materials such as a-Si:H. As a result, the thickness required to fabricate a device with c-Si as the absorber is quite large, i.e., of the order of hundreds of microns (from 98 μm up to 300 μm). For comparison, amorphous pin solar cells made with a-Si:H solely usually reach total thicknesses of the order of hundreds of nanometers. Figure 1-9 shows a crystalline silicon unit cell. As can be seen, the silicon atoms are arranged according to a diamond structure. This particular feature will lead to specific etching properties and very useful orientation selectivity. Table 1-2 displays various parameters for crystalline silicon. On these properties will depend the final performances of the solar device fabricated with this material. Indeed, the density of state, mobility and diffusion will determine how many carriers can be generated, how fast and how far they can travel before being subject to recombination. This will in turn determine the lifetime of the photogenerated carriers inside the device, i.e., how long they actually "live" inside the device. The longer they remain, the higher the chances we will have to collect them as a current. This, among other things, will determine the final conversion efficiency of the solar cell and we want it to be as high as possible.

| Effective density of states N <sub>c</sub>    | 2.8x10 <sup>19</sup> cm <sup>-3</sup>    |

|-----------------------------------------------|------------------------------------------|

| Effective density of states N <sub>v</sub>    | 1.04x10 <sup>19</sup> cm <sup>-3</sup>   |

| Energy bandgap $E_g$                          | 1.12 eV                                  |

| Intrinsic carrier concentration               | 1·10 <sup>10</sup> cm <sup>-3</sup>      |

| Electron mobility $\mu_e$                     | $\approx 1400 \text{ cm}^2/(\text{V s})$ |

| Hole mobility $\mu_h$                         | $\approx 450 \text{ cm}^2/(\text{V s})$  |

| Electron diffusion coefficient $D_e$          | $\approx 36 \text{ cm}^2/\text{s}$       |

| Hole diffusion coefficient D <sub>h</sub>     | ≈ 12 cm <sup>2</sup> /s                  |

| Electron diffusion length L <sub>diff-e</sub> | 1800 μm                                  |

| Hole diffusion length L <sub>diff-h</sub>     | 1050 μm                                  |

structure arrangement.

Figure 1-9 – Crystalline silicon unit cell showing a diamond Table 1-2 – Selected parameters describing the band structure and the electrical properties of crystalline silicon at 300K.

In this section, we will describe the different recombination processes that can occur in a semiconductor material such as crystalline silicon. Indeed, understanding them will help us pushing the photogenerated carrier lifetime limits in order to reach higher conversion efficiencies of finalized solar cell devices.

## 1.3.1 Bulk recombination and lifetime

At temperature above absolute zero, electron-hole pairs are constantly generated. These carriers eventually recombine through various mechanisms. In the case of solar cells, the electron-hole pairs are generated by an external light excitation. If we assume this excitation to have a constant intensity and steady-state conditions, we witness a situation where the excess carrier density is non-zero. Indeed, there is an excess carrier density, which can be defined through the density of carriers under thermodynamic equilibrium  $n_0$  and their recombination rate U in cm<sup>-3</sup>·s<sup>-1</sup>:

$$U = \frac{n - n_0}{\tau} = \frac{\Delta n}{\tau} \tag{29}$$

where  $\tau$  is the characteristic recombination lifetime of our recombination process and  $\Delta n=n-n_0$  the excess carrier density in the c-Si bulk. Under equilibrium though, the thermal generation rate matches the recombination rate and the excess carrier density is equal to zero. Since most of the high-efficiency solar cells work closer to mid- or high-injection levels, we will consider that both excess carrier densities are equal, therefore  $\Delta n=\Delta p$ . As stated before, carrier recombination in c-Si can occur through different mechanisms, namely three which are independent: radiative recombination, Auger recombination and the so-called SRH (stands for Shockley-Read Hall) recombination n process. The total recombination rate within the c-Si bulk will therefore be a combination of the three recombination rates  $U_{rad}$ ,  $U_{Aug}$  and  $U_{SRH}$  as follows:

$$U = U_{rad} + U_{Aug} + U_{SRH} = \frac{\Delta n}{\tau_{rad}} + \frac{\Delta n}{\tau_{Aug}} + \frac{\Delta n}{\tau_{SRH}} = \frac{\Delta n}{\tau_{bulk}}$$

(30)

where  $\tau_{rad}$ ,  $\tau_{Aug}$  and  $\tau_{SRH}$  are the recombination lifetimes related to their respective recombination rates. These three mechanisms will be described to understand how the overall recombination rate can be influenced.

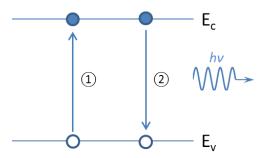

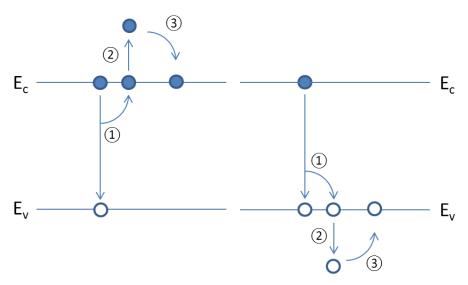

#### 1.3.1.a Radiative recombination: relaxation by photon emission

Radiative recombination is an unavoidable phenomenon taking place within the c-Si bulk. In this recombination process, the excess of energy confined within crystalline silicon is expelled in the form of a photon when two carriers of opposite charges (an electron and a hole) neutralize each other from the conduction and the valence band, respectively.

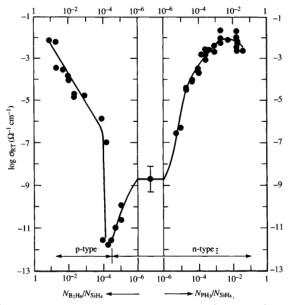

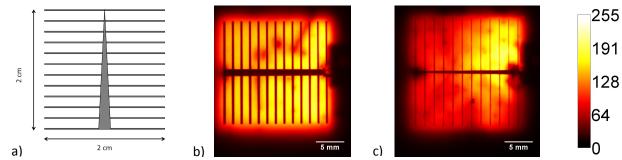

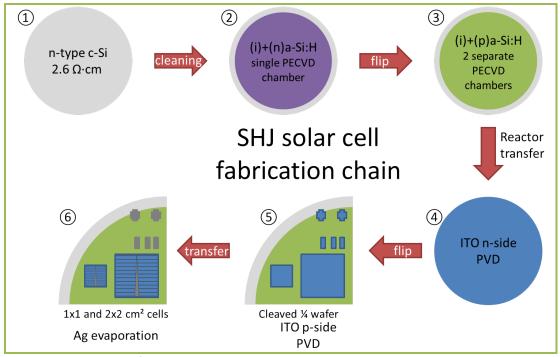

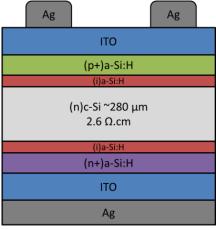

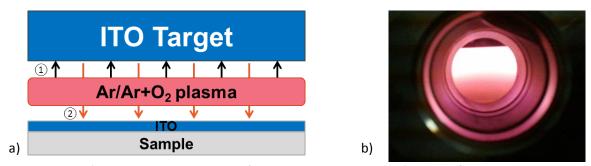

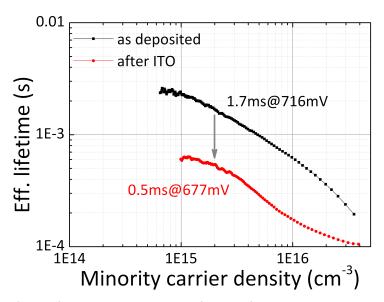

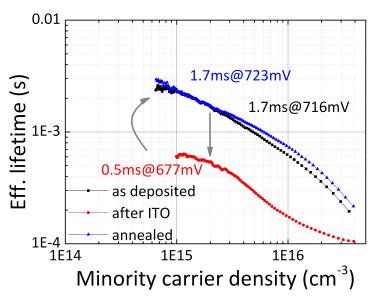

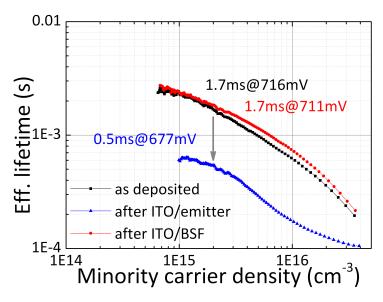

Figure 1-10 — Radiative recombination paths in a semiconductor: (1) hole from the VB recombining with an electron in the CB; (2) electron from the CB recombining with a hole in the VB. Both mechanisms result in the emission of a photon with an energy of hv.