# Architectures radio-logicielles appliquées aux réseaux véhiculaires

Carina Schmidt-Knorreck

#### ▶ To cite this version:

Carina Schmidt-Knorreck. Architectures radio-logicielles appliquées aux réseaux véhiculaires. Autre. Télécom ParisTech, 2012. Français. NNT: 2012ENST0057. tel-01145462

## HAL Id: tel-01145462 https://pastel.hal.science/tel-01145462

Submitted on 24 Apr 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Doctorat ParisTech**

## THÈSE

pour obtenir le grade de docteur délivré par

## **TELECOM ParisTech**

Spécialité « Eléctronique et Communications »

présentée et soutenue publiquement par

### Carina SCHMIDT-KNORRECK

le 04.10.2012

# Architectures Radio-Logicielles appliquées aux Réseaux Véhiculaires

Directeur de thèse : Raymond KNOPP

#### Jurv

M. Jaques PALICOT, Professeur, SUPELEC, Cesson-Sévigné

Président

M. Andreas HERKERSDORF, Professeur, Technische Universitaet Muenchen, Allemagne Rapporteur

M. Guido MASERA, Professeur, Politecnico di Torino, Italy

Rapporteur

M. Renaud PACALET, Directeur d'Etudes, Télécom ParisTech, Sophia Antipolis

Examinateur

## **Abstract**

Today, wireless communication applications have become a major part in our life. Smartphones, for instance, support more and more applications allowing us to surf on the web or to talk to our friends at any place and at any time. New products compete by providing more applications in only one device that is smaller, lighter, cheaper and of higher performance than similar products on the market. Dealing with these requirements of reconfigurable radio architectures is a very challenging task. One solution can be found in the context of Software Defined Radio (SDR). Under its umbrella, flexible hardware platforms that support a wide range of different wireless communication standards are designed. The OpenAirInterface ExpressMIMO platform developed by Eurecom and Télécom ParisTech is a very flexible SDR platform whose baseband processing engine is split over different DSPs to enable a fast and easy component replacement and component upgrade.

The main objective of this thesis is to propose the first prototype of a receiver chain for the ExpressMIMO platform in general, and in particular to assess the applicability of the platform for latency critical standards. An interesting representative of such a standard is IEEE 802.11p. The work presented in this thesis is thus settled in the automotive context where efficient physical layer implementations of the IEEE 802.11p standard required for Car-to-Car and Car-to-Infrastructure communication are still an open research topic. The first contribution is a complete design of the IEEE 802.11p receiver implemented for the ExpressMIMO platform and was therefore serving as a proof of concept in general and in particular for standards operating on short data sets. Our results prove, that an efficient receiver design is feasible for various modulation schemes when applying a centralized control flow on the platform. Different design bottlenecks have been identified and solutions to overcome these limitations are suggested.

The combination of Car-to-Car and Car-to-Infrastructure communication with information about traffic jams or merchandising applications within only one device enables various new applications for future cars. Therefore we investigate on a possible multimodal execution of IEEE 802.11p and ETSI DAB. For the design of an appropriate scheduler it is of main importance to have first key figures at hand. We provide these figures based on a detailed runtime performance evaluation and enhance our obtained results by the derivation of scheduling guidelines and the presentation of a first scheduler prototype.

Our analysis reveals that the Front-End Processing (FEP) engine is heavily charged and that the required configuration time outreaches the pure executing time for short vectors when considering an FPGA target. To meet this challenge we introduce an Application Specific Instruction-set Processor (ASIP) as the solution of choice when dealing with strong latency requirements. The presented solution is not only compared to the programmable DSP engine but also to different solutions from academia. For design comparison we mainly focus on architectural differences and the runtime performance in terms of processing time.

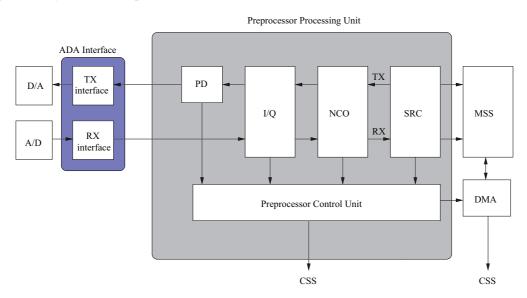

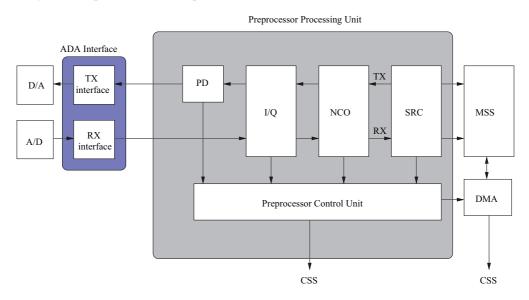

To complete the receiver chain we finally present a first Preprocessor prototype. The Preprocessor connects the external A/D, D/A converters with the remaining baseband engine and is responsible

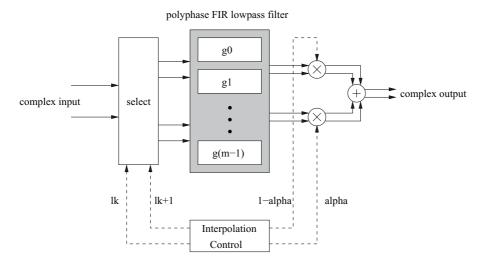

among others for I/Q imbalance correction and sample rate conversion. In this context we present a generic, flexible and hardware optimized Sample Rate Converter (SRC) operating on fractional ratios with a resolution of 1 Hz between the sampling frequencies. The design supports up to four different receive and up to four different transmit channels and is based on bandlimited interpolation.

Our results are finally generalized to ease the deployment of future standards on the ExpressMIMO platform.

## Résumé

Aujourd'hui, les applications de communication sans fil font partie de notre vie quotidienne. Les smartphones, par exemple, supportent de plus en plus d'applications qui nous permettent de surfer sur le web et de parler à nos amis en tout lieu et à tout moment. Principalement, les nouveaux produits se concurrencent sur le nombre de leurs applications. Les autres facteurs determinants sont la taille, le poids et la performance qui sont comparés au produits concurrents qu'on trouve déjà sur le marché. Répondre aux contraintes des architectures reconfigurables n'est pas toujours une tâche aisée. Des solutions existent dans le domaine de la radio logicielle (Software Defined Radio, SDR) où des plateformes flexibles qui prennent en charge un large éventail de différentes standards de communication sans fil peuvent être conçus. La plateforme OpenAirInterface ExpressMIMO qui est développée par Eurecom et Télécom ParisTech est une plateforme radio logicielle très flexible: le traitement des operations dans la bande de base est réparti sur différents DSPs pour permettre un remplacement ou une mise à jour des composants simple et rapide.

L'objectif principal de cette thèse est de proposer le premier prototype d'un récepteur pour la plateforme ExpressMIMO, et d'évaluer le potentiel de la plateforme pour les standards ayant des latences critiques en particulier. Un cas intéressant d'un tel standard est la norme IEEE 802.11p qui spécifie la communication entre plusieurs véhicules (Car-to-Car communication) ainsi que la communication entre les véhicules et l'infrastructure (Car-to-Infrastructure communication). Le travail présenté dans cette thèse se focalise donc en partie sur le domaine de l'automobile où les implémentations efficaces de la couche physique du standard IEEE 802.11p est encore un sujet de recherche ouvert. La première contribution proposée est la conception complète d'un récepteur qui est basée sur le standard IEEE 802.11p et qui a été implémentée sur la plateforme Express-MIMO. Ce system a donc servi de démonstrateur à la fois pour valider l'ensemble de la plateforme et en particulier l'utilisation de standards qui emploient des vecteurs de petite taille. Nos résultats prouvent qu'une conception efficace du récepteur est réalisable pour des schémas de modulation différents lorsqu'un un contrôle centralisé existe sur la plateforme. Des goulots d'étranglement ont pu être identifiés et des solutions ont été proposées pour surmonter ces limitations.

La combinaison dans un seul dispositif de la communication inter-véhicules avec l'information sur les embouteillages ou sur la proximité de commerces permet diverses applications nouvelles pour les futures automobiles. Par conséquent, nous étudions une possible exécution multimodal du IEEE 802.11p et du ETSI DAB. Pour la conception d'un ordonnanceur de tâches approprié, il est d'une importance principale àvoir un permier aperçu chiffré des performances. Nous fournissons des chiffres qui sont basés sur une évaluation détaillée des performances d'exploitation et nous utilisons ces résultats pour déduire l'ordonnancement optimal et nous présentons un premier prototype d'ordonnanceur.

Notre analyse, lors des expérimentations sur une cible FPGA, révèle que le Front-End Processing (FEP) DSP est lourdement chargé et que le temps de configuration requis dépasse le temps d'execution dans le cas d'operations sur des vecteurs de petite taille. Pour relever ce défi, nous proposons un Application Specific Instruction-set Processor (ASIP) comme solution lorsque les

contraintes de latence sont fortes. La solution présentée est non seulement comparée au DSP programmable, mais aussi à d'autres solutions du monde universitaire. Pour la comparaison des conceptions nous nous concentrons principalement sur les différences dans les architecture et la performance d'exécution en termes de temps de traitement.

Pour compléter la chaîne de réception, nous présentons enfin un premier prototype de Préprocesseur DSP. Le Préprocesseur connecte les convertisseurs A/D et D/A avec les autres composants de la bande de base. Il est également reponsable, entre autres, de la correction du déséquilibre entre les voies I et Q et du ré-échantillonnage. Dans ce contexte, nous présentons un convertisseur générique et flexible pour le ré-échantillonnage (Sample Rate Converter, SRC) qui travaille sur des rapports fractionnaires de fréquence d'échantillonnage avec une résolution de 1 Hz entre les fréquences. La conception prend en charge jusqu'à quatre chaînes différentes en transmission et en récpetion et est basée sur une interpolation à bande limitée.

Nos résultats sont finalement généralisés et nous montrons que notre approche facilite le déploiement de futures standards sur des plateformes tel que ExpressMIMO.

## **Acknowledgements**

During the past years, I had the chance to work with and to meet a lot of fantastic people. All of you influenced my life and taught me a lot. Not only about telecommunications and engineering but also about life. My thanks go to all of you, because without you, I would not be who I am today!

First of all I would like to thank my supervisor Raymond Knopp for his support and for giving me the chance to become a part of his great team. It was a big pleasure for me to work with you! Further thanks go to the whole LabSoC team. You guys are amazing! Thanks for all your support and your friendship throughout the past years. It was a pleasure for me to meet all of you and I hope that we can keep in touch:-)

At the end I spent six fantastic years at Eurecom. First as a student, then as a PhD student. Eurecom is an incredible place in France and I enjoyed so much meeting people from all over the world and to learn from them. I do not want to start writing names of the friends I made the past years, because I'm very afraid that I will miss someone. And I'm quite sure that you know who I mean.

Finally I would like to thank my dear husband Daniel. We started our french and even our PhD journey together and all the challenges of the past years made our relationship stronger and stronger. You are my love, my soulmate and the best friend I ever had! Thanks to your support, I was able to finish this work and I hope, that I was such a tower of strength for you than you were for me!

Thank you!

## **Table of Contents**

| Li | st of F    | igures   |                                                                    | xiii           |

|----|------------|----------|--------------------------------------------------------------------|----------------|

| Li | st of T    | Tables   |                                                                    | xiv            |

| Ac | ronyı      | ns       |                                                                    | xvii           |

| 1  | Intro      | oduction |                                                                    | 1              |

|    | 1.1<br>1.2 |          | tion and Problem Statement                                         | 1 3            |

| 2  | SDR        | Baseba   | and Processing                                                     | 7              |

|    | 2.1        | Softwa   | re Defined Radio                                                   | 7              |

|    | 2.2        | Related  | 1 Work                                                             | 8              |

|    | 2.3        | OpenA    | irInterface ExpressMIMO Platform                                   | 12             |

|    |            | 2.3.1    | Control                                                            | 13             |

|    |            |          | 2.3.1.1 Choice of the Operating System for LEON3                   | 13             |

|    |            | 2.3.2    | Baseband Design and Emulation                                      | 14             |

|    |            |          | 2.3.2.1 Generic DSP Shell                                          | 14             |

|    |            |          | 2.3.2.2 Overview of the different DSP engines                      | 16             |

|    |            |          | 2.3.2.3 Processing Times                                           | 18             |

|    |            |          | 2.3.2.4 Receiver Emulation using the Library for ExpressMIMO base- | 10             |

|    |            | 2 2 2    | band (libembb)                                                     | 18             |

|    | 2.4        | 2.3.3    | Development Methodology                                            | 19             |

|    | 2.4        | Conclu   | sions                                                              | 20             |

| 3  | IEE        | E 802.11 | p Receiver for the ExpressMIMO Platform                            | 21             |

|    | 3.1        | Motiva   | tion                                                               | 21             |

|    |            | 3.1.1    | Related Work                                                       | 22             |

|    |            | 3.1.2    | Contributions                                                      | 24             |

|    | 3.2        | -        | otion of the IEEE 802.11p Packet Structure                         | 25             |

|    | 3.3        | IEEE 8   | 02.11p Receiver Algorithms                                         | 27             |

|    |            | 3.3.1    | Packet Synchronization                                             | 27             |

|    |            | 3.3.2    | Channel Estimation                                                 | 29             |

|    |            | 3.3.3    | SIGNAL and DATA Field Detection                                    | 30             |

|    |            |          | 3.3.3.1 Channel Compensation (FEP)                                 | 30             |

|    |            |          | 3.3.3.2 Data Detection (Decoding, FEP)                             | 31             |

|    |            |          | 3.3.3.3 Deinterleaver                                              | 34<br>34       |

|    |            |          | J.J.J.T CHAIRICI DOCUMENT                                          | J <del>4</del> |

|   |            |                                                       | 3.3.3.5 Descrambling and CRC Check                                                                                                                                                         |

|---|------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.4        | System                                                | n Presentation and Receiver Versions                                                                                                                                                       |

|   |            | 3.4.1                                                 | Required Resources on the ExpressMIMO platform                                                                                                                                             |

|   |            | 3.4.2                                                 | Matlab Prototype of the IEEE 802.11p Receiver                                                                                                                                              |

|   |            | 3.4.3                                                 | Emulation of the IEEE 802.11p Receiver                                                                                                                                                     |

|   |            | 3.4.4                                                 | Hardware Prototype of the IEEE 802.11p Receiver                                                                                                                                            |

|   |            |                                                       | 3.4.4.1 C Code Optimization                                                                                                                                                                |

|   |            |                                                       | 3.4.4.2 Interrupt Handler                                                                                                                                                                  |

|   |            |                                                       | 3.4.4.3 Command Preparation at Runtime                                                                                                                                                     |

|   |            |                                                       | 3.4.4.4 Scheduling                                                                                                                                                                         |

|   |            |                                                       | 3.4.4.5 Symbol Grouping                                                                                                                                                                    |

|   |            |                                                       | 3.4.4.6 Command Preparation before starting the Receiver                                                                                                                                   |

|   | 3.5        | Results                                               | s                                                                                                                                                                                          |

|   |            | 3.5.1                                                 | Remarks                                                                                                                                                                                    |

|   |            | 3.5.2                                                 | Resource Consumption Results obtained with libembb                                                                                                                                         |

|   |            |                                                       | 3.5.2.1 Case Study: Multi-Standard Processing of IEEE 802.11p and                                                                                                                          |

|   |            |                                                       | ETSI DAB                                                                                                                                                                                   |

|   |            | 3.5.3                                                 | Runtime Performance Analysis - Hardware Results                                                                                                                                            |

|   |            |                                                       | 3.5.3.1 Constant Part                                                                                                                                                                      |

|   |            |                                                       | 3.5.3.2 Variable Part (DATA Field)                                                                                                                                                         |

|   | 3.6        | Conclu                                                | sions                                                                                                                                                                                      |

| 4 | AST        | P Design                                              | n for Front-End Processing 57                                                                                                                                                              |

| • | 4.1        | _                                                     | ation                                                                                                                                                                                      |

|   | 1.1        | 4.1.1                                                 | Related Work                                                                                                                                                                               |

|   |            | 7.1.1                                                 | 4.1.1.1 Front-End Processing Solutions                                                                                                                                                     |

|   |            |                                                       | 4.1.1.2 ASIP Design Approaches for Front-End Processing Solutions . 60                                                                                                                     |

|   |            |                                                       | 4.1.1.3 ASIP Solutions for Design Comparison                                                                                                                                               |

|   |            | 4.1.2                                                 | Contributions                                                                                                                                                                              |

|   | 4.2        |                                                       | Design Methodology                                                                                                                                                                         |

|   | 4.3        |                                                       | End Processing Algorithms                                                                                                                                                                  |

|   | 4.4        |                                                       | Version of the A-FEP (A-FEP-V1)                                                                                                                                                            |

|   | 7.7        |                                                       | Functional Specification                                                                                                                                                                   |

|   |            | 7,7,1                                                 | 4.4.1.1 ASIP Enhancements                                                                                                                                                                  |

|   |            | 4.4.2                                                 | Architecture                                                                                                                                                                               |

|   |            | 7.7.2                                                 | 4.4.2.1 Instruction Set                                                                                                                                                                    |

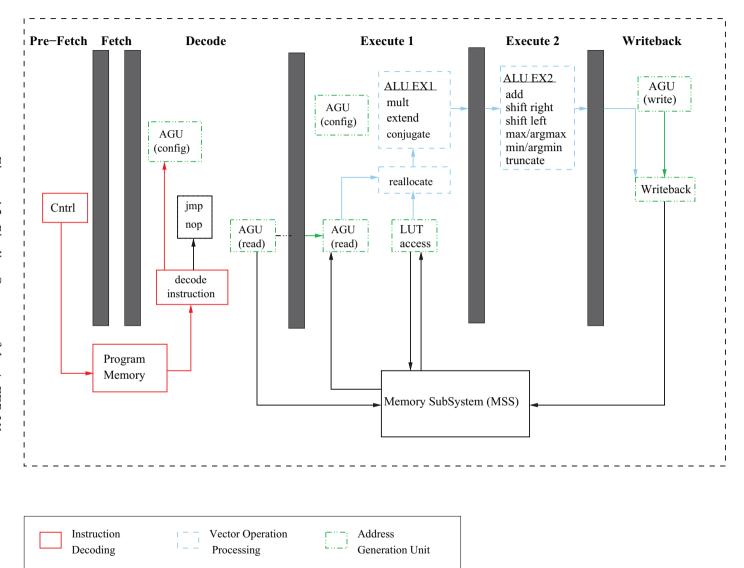

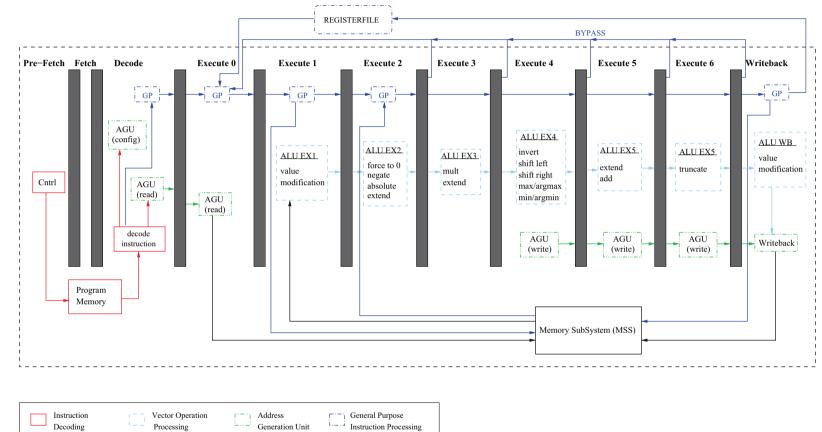

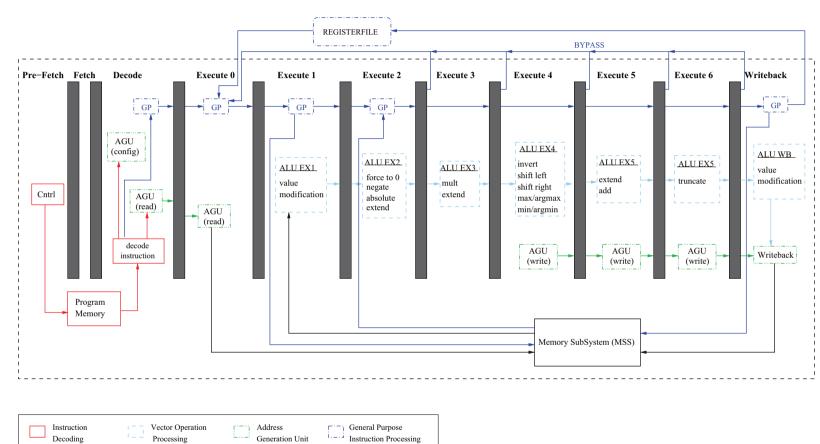

|   |            |                                                       | 4.4.2.2 Pipeline Structure                                                                                                                                                                 |

|   |            | 4.4.3                                                 | Design Comparison                                                                                                                                                                          |

|   | 4.5        |                                                       |                                                                                                                                                                                            |

|   | 4.5        |                                                       | E 1                                                                                                                                                                                        |

|   |            | Function                                              | onal Specification                                                                                                                                                                         |

|   |            | Function 4.5.1                                        | onal Specification                                                                                                                                                                         |

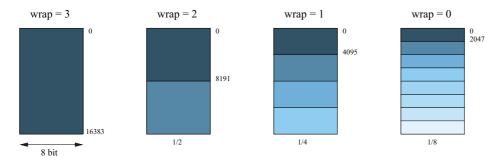

|   |            | Function 4.5.1 4.5.2                                  | onal Specification         69           Vector Processing         69           Memory Sub-System (MSS)         70                                                                          |

|   | 16         | Function 4.5.1 4.5.2 4.5.3                            | onal Specification69Vector Processing69Memory Sub-System (MSS)70Address Generation Unit (AGU)71                                                                                            |

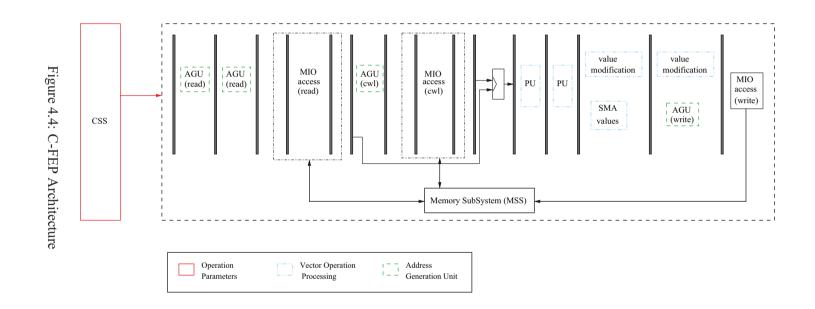

|   | 4.6        | Function 4.5.1 4.5.2 4.5.3 Archite                    | onal Specification 69 Vector Processing 69 Memory Sub-System (MSS) 70 Address Generation Unit (AGU) 71 ecture of the C-FEP 72                                                              |

|   |            | Function 4.5.1 4.5.2 4.5.3 Archited 4.6.1             | onal Specification 69 Vector Processing 69 Memory Sub-System (MSS) 70 Address Generation Unit (AGU) 71 ecture of the C-FEP 72 Synthesis Results 74                                         |

|   | 4.6<br>4.7 | Function 4.5.1 4.5.2 4.5.3 Archited 4.6.1 A-FEP       | onal Specification 69 Vector Processing 69 Memory Sub-System (MSS) 70 Address Generation Unit (AGU) 71 ecture of the C-FEP 72 Synthesis Results 74 P Design 74                             |

|   |            | Function 4.5.1 4.5.2 4.5.3 Archited 4.6.1 A-FEP 4.7.1 | onal Specification 69 Vector Processing 69 Memory Sub-System (MSS) 70 Address Generation Unit (AGU) 71 ecture of the C-FEP 72 Synthesis Results 74 Design 74 Instruction-Set and Opcode 74 |

|   |            | Function 4.5.1 4.5.2 4.5.3 Archited 4.6.1 A-FEP       | onal Specification 69 Vector Processing 69 Memory Sub-System (MSS) 70 Address Generation Unit (AGU) 71 ecture of the C-FEP 72 Synthesis Results 74 P Design 74                             |

|     |      | 4.7.4 Cycle Counts                                                           | 81         |

|-----|------|------------------------------------------------------------------------------|------------|

|     | 4.8  | Component-Wise Lookup Table - Example of a Possible Future A-FEP Instruction | 81         |

|     | 4.9  | Design Comparison and Runtime Performance                                    | 83         |

|     |      | 4.9.1 Design Comparison A-FEP vs C-FEP                                       | 83         |

|     |      | 4.9.2 Runtime Performance                                                    | 84         |

|     |      |                                                                              |            |

|     |      | 4.9.2.1 Auto-Correlation Based Packet Detection Algorithm                    | 84         |

|     |      | 4.9.3 Energy Based Coarse Packet Detection Algorithm                         | 86         |

|     | 4.10 | Conclusions                                                                  | 88         |

| 5   | Flex | ible Sample Rate Converter Design                                            | 89         |

|     | 5.1  | Motivation                                                                   | 89         |

|     | 5.1  | 5.1.1 Related Work                                                           | 91         |

|     |      |                                                                              | 91         |

|     |      | 5.1.1.1 Analog Solutions                                                     |            |

|     |      | 5.1.1.2 Digital Solutions                                                    | 92         |

|     |      | 5.1.2 Contributions                                                          | 97         |

|     | 5.2  | Functional Specification                                                     | 98         |

|     |      | 5.2.1 Preprocessor Specification                                             | 98         |

|     |      | 5.2.2 SRC Specification                                                      | 101        |

|     |      | 5.2.2.1 Derivation of the Filter Structure                                   | 101        |

|     |      | 5.2.2.2 Lowpass Filter Design                                                | 102        |

|     |      |                                                                              | 105        |

|     |      |                                                                              | 107        |

|     |      |                                                                              | 108        |

|     |      | 1 1 0                                                                        | 108        |

|     | 5.3  | 1 &                                                                          | 110        |

|     | 5.5  | ,                                                                            | 110        |

|     |      | 1 21                                                                         |            |

|     |      |                                                                              | 111        |

|     |      |                                                                              | 111        |

|     | 5.4  | <b>→</b>                                                                     | 115        |

|     |      |                                                                              | 115        |

|     |      | 5.4.2 Synthesis Results                                                      | 118        |

|     | 5.5  | Conclusions                                                                  | 118        |

| 6   | Con  | clusions and Future Work                                                     | 121        |

| U   | 6.1  |                                                                              | 122        |

|     | 6.2  |                                                                              | 122        |

|     | 6.3  | 7. 0                                                                         | 122<br>123 |

|     |      |                                                                              |            |

|     | 6.4  | $\epsilon$                                                                   | 124        |

|     |      | 1                                                                            | 124        |

|     |      |                                                                              | 125        |

|     | 6.5  | 1 71                                                                         | 125        |

|     | 6.6  | Guidelines for a Future Standard Deployment                                  | 126        |

| A   | Récu | ımé Français                                                                 | 129        |

| 1 1 | A.1  |                                                                              | 129        |

|     |      |                                                                              | 129<br>131 |

|     | A.2  |                                                                              |            |

|     |      | 1                                                                            | 131        |

|     |      | A.2.1.1 Méthodologie de Développement                                        | 132        |

| A.3      | IEEE 8           | 802.11p Récepteur pour la plate-forme ExpressMIMO                  |     |

|----------|------------------|--------------------------------------------------------------------|-----|

|          | A.3.1            | Motivation                                                         | 133 |

|          | A.3.2            | La Norme IEEE 802.11p                                              | 134 |

|          | A.3.3            | Développement du Récepteur                                         | 135 |

|          |                  | A.3.3.1 Prototype Matlab du Récepteur IEEE 802.11p                 | 135 |

|          |                  | A.3.3.2 Emulation du Récepteur IEEE 802.11p                        | 135 |

|          |                  | A.3.3.3 Prototype Matériel du Récepteur IEEE 802.11p               | 136 |

|          | A.3.4            | Résultats                                                          | 136 |

|          |                  | A.3.4.1 Résultats obtenus avec libembb                             | 136 |

|          |                  | A.3.4.2 Analyse de la performance d'éxécution - Résultats matériel | 137 |

| A.4      | Conce            | ption ASIP pour le FEP                                             | 138 |

|          | A.4.1            | Exigences du Moteur de Traitement                                  | 139 |

|          | A.4.2            | Architecture HW et Instruction-Set                                 | 140 |

|          | A.4.3            | Comparaison des Performances d'Exécution                           | 141 |

| A.5      | Conce            | ption flexible d'un Sample Rate Converter                          | 143 |

|          | A.5.1            | Motivation                                                         | 143 |

|          | A.5.2            | Design du Préprocessor et du SRC                                   | 145 |

|          | A.5.3            | Résultats                                                          | 147 |

| A.6      | Conclu           | asion                                                              | 148 |

| Bibliogr | Bibliography 157 |                                                                    |     |

## **List of Figures**

| 2.1  | Overview of a Wireless Communication System                                        |

|------|------------------------------------------------------------------------------------|

| 2.2  | Basic Building Blocks for Hardware Mapping                                         |

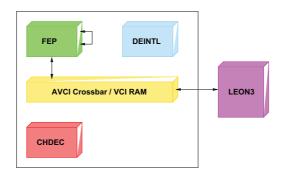

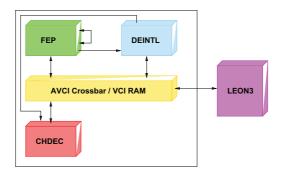

| 2.3  | Baseband Architecture of the ExpressMIMO Platform                                  |

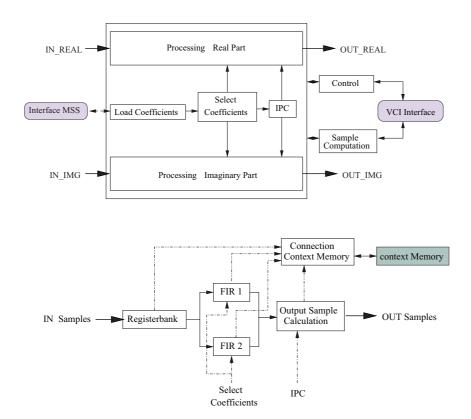

| 2.4  | OpenAirInterface Standardized DSP Shell                                            |

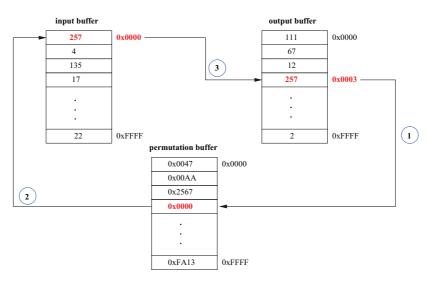

| 2.5  | Illustration of the basic (De)Interleaver Functionality                            |

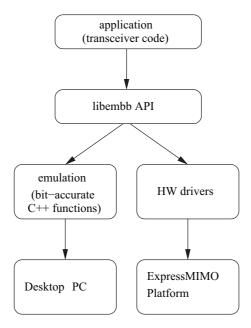

| 2.6  | libembb Processing Flow                                                            |

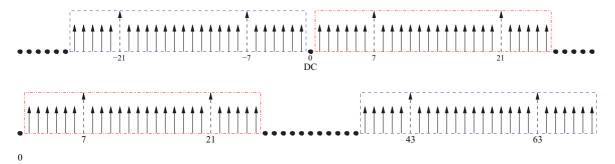

| 3.1  | IEEE 802.11p OFDM Symbol Carriers before and after Reordering                      |

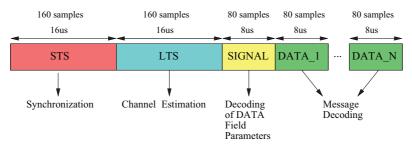

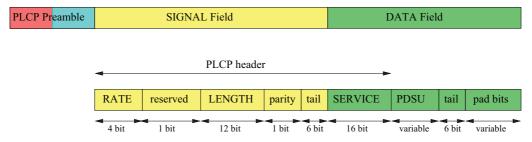

| 3.2  | IEEE 802.11p Packet Structure                                                      |

| 3.3  | Preamble Data and Control Flow                                                     |

| 3.4  | SIGNAL and DATA Field Data and Control Flow                                        |

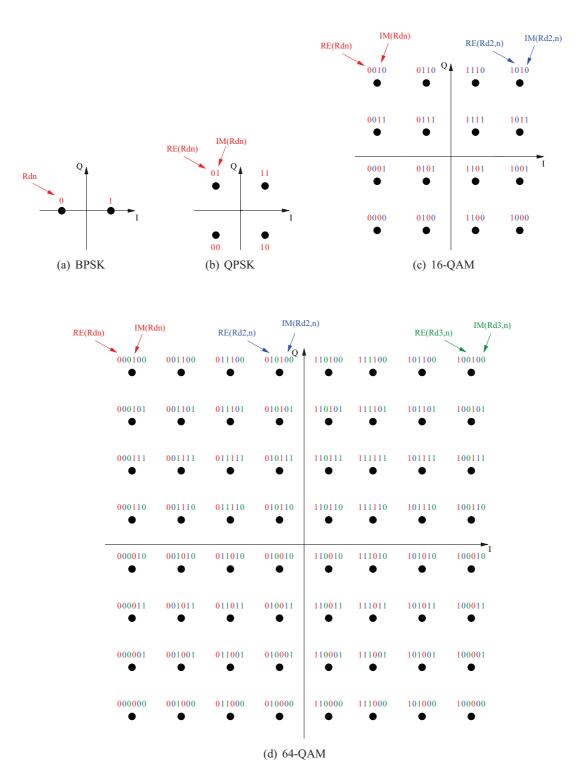

| 3.5  | Bit Constellations for the IEEE 802.11p Data Detection                             |

| 3.6  | Baseband Architecture of the ExpressMIMO Platform                                  |

| 3.7  | Emulation Codestructure                                                            |

| 3.8  | IEEE 802.11p DSP Processing and Scheduling                                         |

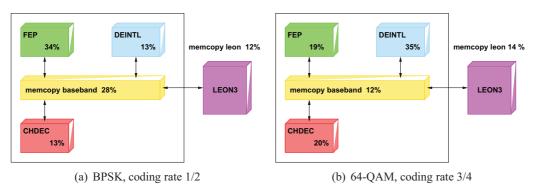

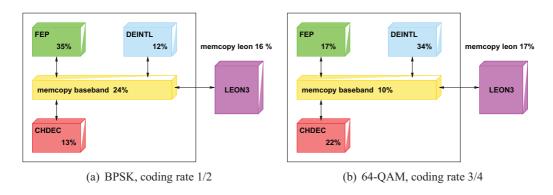

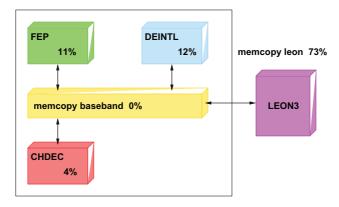

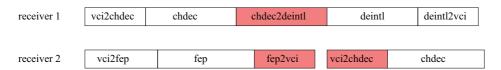

| 3.9  | Runtime Distribution - Constant Part                                               |

| 3.10 | Runtime Distribution - Data Field (group size = 1)                                 |

| 3.11 | Runtime Distribution - Data Field (group size = 8)                                 |

| 3.12 | ETSI DAB Frame                                                                     |

| 3.13 | DAB Runtime Distribution for 1 DAB Frame (96 ms)                                   |

| 3.14 | Flexible Memcopy Scheduling at Runtime                                             |

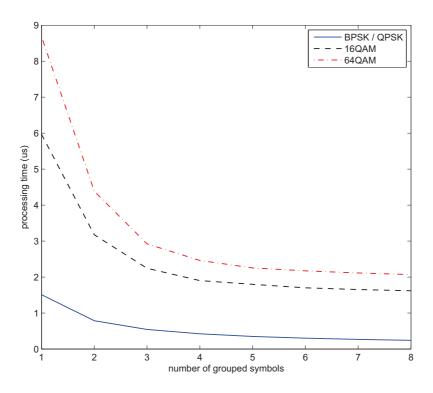

|      | Average Processing Time Data Detection                                             |

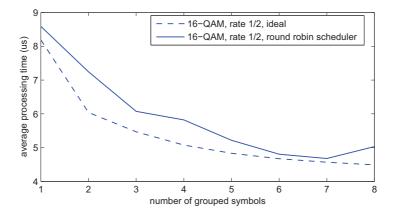

| 3.16 | Round Robin Scheduler for 16-QAM                                                   |

| 3.17 | Average FEP Processing Time                                                        |

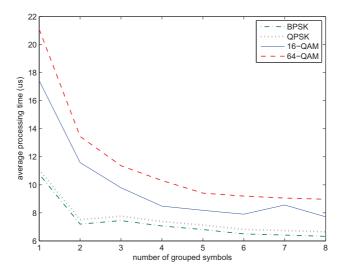

| 3.18 | Average Deinterleaver Processing Time                                              |

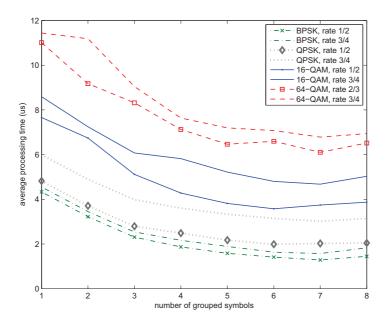

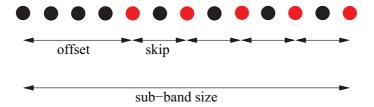

| 4.1  | Definition of Skip and Offset within one Sub-band                                  |

| 4.2  | Pipeline Structure of the A-FEP-V1                                                 |

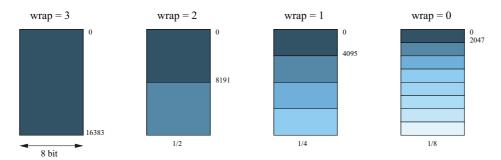

| 4.3  | Wrapping Sections FEP MSS (int8)                                                   |

| 4.4  | C-FEP Architecture                                                                 |

| 4.5  | Pipeline Structur of the A-FEP                                                     |

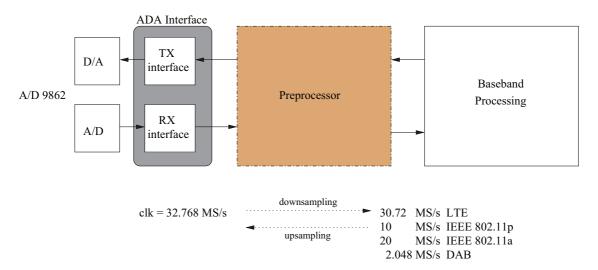

| 5.1  | The Preprocessor connects the ADA Converters with the remaining Baseband Engine 90 |

| 5.2  | Classical SRC Approach                                                             |

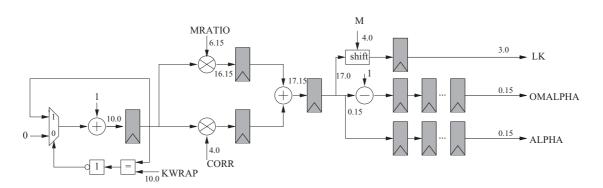

| 5.3  | Modified Standardized DSP Shell                                                    |

| 5.4  | Preprocessor Architecture                                                          |

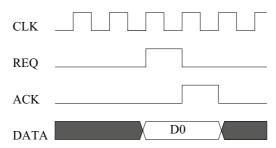

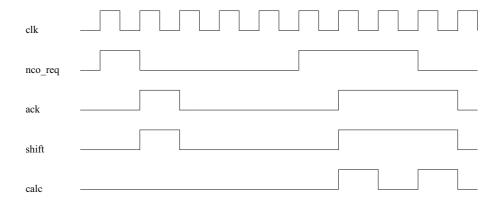

| 5.5  | Handshake Protocol                                                                 |

| 5.6  | Basic SRC Architecture                                                             |

xiv List of Figures

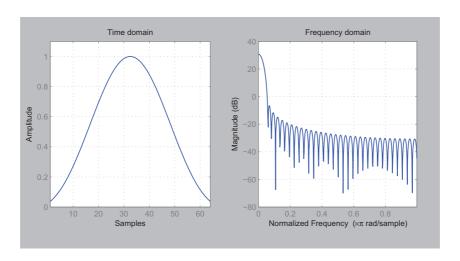

| 5.7  | Kaiser Window for $\beta = 5$                                                 | 104 |

|------|-------------------------------------------------------------------------------|-----|

| 5.8  | Filter Coefficient Distribution                                               | 106 |

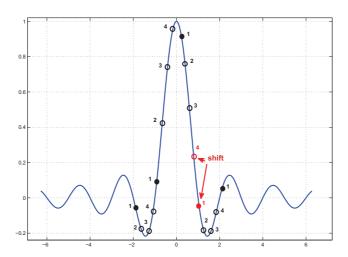

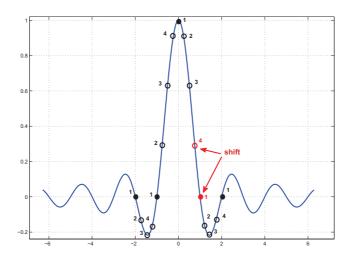

| 5.9  | Upsampling: Relation between Input and Output Samples                         | 108 |

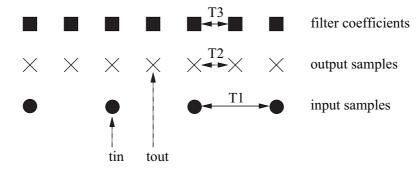

| 5.10 | SRC Upsampling Algorithm                                                      | 109 |

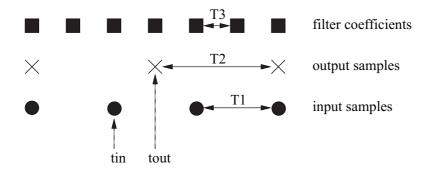

| 5.11 | Downsampling: Relation between Input and Output Samples                       | 109 |

| 5.12 | SRC Downsampling Algorithm                                                    | 110 |

| 5.13 | SRC Top Level View                                                            | 112 |

| 5.14 | Module InterpolationControl                                                   | 112 |

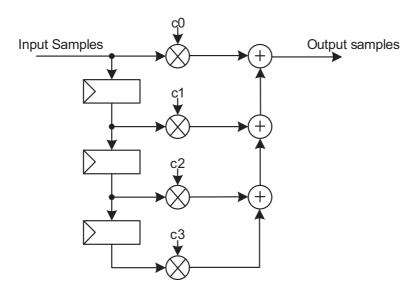

|      | Example FIR Filter with 4 Filter Coefficients                                 | 114 |

|      | Example: Upsampling by a factor of 3                                          | 114 |

| 5.17 | Example: Downsampling by a factor of 2.5                                      | 115 |

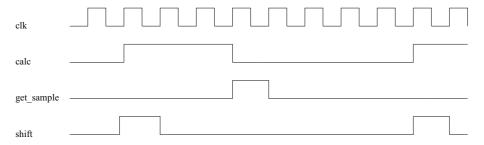

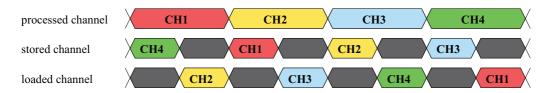

|      | Channel Scheduling                                                            | 115 |

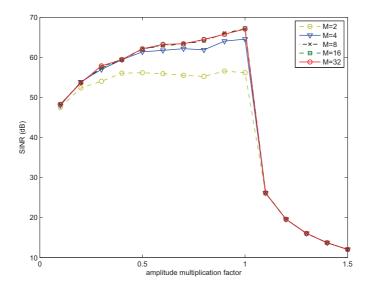

|      | SNR Performance for Changing M                                                | 117 |

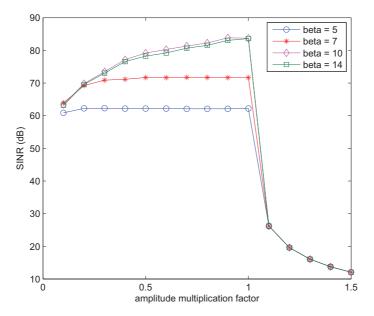

| 5.20 | SNR Performance for Changing Beta                                             | 117 |

| A.1  | L'Architecture de la Bande de Base de la Plate-Forme ExpressMIMO              | 131 |

| A.2  | OpenAirInterface Standardized DSP Shell                                       | 132 |

| A.3  | IEEE 802.11p Paquet (channel spacing 10 MHz)                                  | 134 |

| A.4  | Architecture de Bande de Base de la Plate-Forme ExpressMIMO                   | 135 |

| A.5  | Zones de Stockage Circulaires FEP MSS (int8)                                  | 140 |

| A.6  | Structure de la Pipeline du A-FEP                                             | 142 |

| A.7  | Le Préprocesseur relie les Convertisseurs ADA avec le Moteur de Bande de Base |     |

|      | restant                                                                       | 143 |

| A.8  | Channel Scheduling                                                            | 144 |

| A.9  | DSP Modifications                                                             | 145 |

| A.10 | Architecture du Préprocesseur                                                 | 146 |

## **List of Tables**

| 2.1  | ExpressMIMO Cycle Counts                                                       |

|------|--------------------------------------------------------------------------------|

| 3.1  | Modulation dependent Parameters decoded in the SIGNAL Field                    |

| 3.2  | IEEE 802.11p Specification Parameters (10 MHz Channel Spacing) 27              |

| 3.3  | Energy Detection Operations                                                    |

| 3.4  | Packet Synchronization Operations                                              |

| 3.5  | Channel Estimation Operations                                                  |

| 3.6  | Channel Compensation Operations                                                |

| 3.7  | SIGNAL Field Detection Operations (FEP)                                        |

| 3.8  | Data Field Initialization Operations                                           |

| 3.9  | Data Detection Operations                                                      |

| 3.10 | DATA Field Detection Operations                                                |

|      | DATA OFDM Symbol Grouping                                                      |

|      | Task Runtime for the DSP Engines - Constant Part                               |

|      | Task Runtime for DSP Engines (including memcopy) per DATA OFDM Symbol 43       |

|      | ETSI DAB Specification: Transmission mode I                                    |

|      | Task Runtime for DSP Engines and Memcopy for one Second of Audio Data 47       |

|      | Comparison of ETSI DAB and IEEE 802.11p                                        |

|      | FEP DAB Runtime Distribution for one Frame (96 ms)                             |

|      | FEP Runtime Distribution IEEE 802.11p                                          |

|      | Runtime Performance Results                                                    |

|      | DSP Busy Times (Constant Part) including the DMA Transfers between the DSPs 51 |

|      | FEP Busy Times DATA Field (group size of eight)                                |

|      | Deinterleaver Busy Times DATA Field (group size of eight)                      |

|      | ·                                                                              |

| 4.1  | ASPE A Configurations for the IEEE 802.11a/n Receiver                          |

| 4.2  | Synthesis Results for the C-FEP-V1 and the A-FEP-V1                            |

| 4.3  | C-FEP Vector Operations                                                        |

| 4.4  | A-FEP Vector Operations                                                        |

| 4.5  | AGU Adress Generation Examples                                                 |

| 4.6  | Instruction Set and Opcode (AGU Configuration Instructions)                    |

| 4.7  | Overview of the AGU Configuration Instruction Parameters                       |

| 4.8  | Instruction Set and Opcode (AVO Instructions)                                  |

| 4.9  | Overview of the AVO Instruction Parameters                                     |

| 4.10 | Instruction Set and Opcode (IRQ, NOP)                                          |

| 4.11 | Instruction Set and Opcode (GP - ALU)                                          |

|      | Instruction Set and Opcode (GP - LOAD / STORE)                                 |

| 4.13 | Instruction Set and Opcode (GP - BRANCH)                                       |

xvi List of Tables

| 4.14 | Instruction Set and Opcode (GP - COMPARE)                                      | 78  |

|------|--------------------------------------------------------------------------------|-----|

| 4.15 | Y[i] LUT Organization                                                          | 81  |

|      | Design Comparison A-FEP vs C-FEP                                               | 83  |

| 4.17 | A-FEP Cycle Counts and Execution Times for the IEEE 802.11p Receiver           | 84  |

| 4.18 | A-FEP Instructions for the Auto-Correlation Based Packet Detection             | 85  |

| 4.19 | C-FEP Operations for the Auto-Correlation Based Packet Detection               | 86  |

| 4.20 | Design Comparison for the Auto-Correlation Based Packet Detection              | 86  |

| 4.21 | A-FEP Instructions for the Energy Based Coarse Packet Detection                | 87  |

| 4.22 | C-FEP Operations for the Energy Based Packet Detection                         | 87  |

| 4.23 | Design Comparison for the Energy Based Coarse Packet Detection                 | 87  |

| 5.1  | Filter Coefficient Example ( $M=4$ , Seven Filter Coefficients per Filter)     | 104 |

| 5.2  | Generation of the Missing Filter Coefficients                                  | 113 |

| 5.3  | SRC Results for a Sinusoidal Test Signal                                       | 116 |

| 5.4  | SRC Results for a Sinusoidal Test Signal for Quantization Noise Measurements . | 116 |

|      | A-FEP - Opérations Vectorielles                                                |     |

| A.2  | A-FEP Performances d'Exécution                                                 | 141 |

## **Acronyms**

Here are the main acronyms used in this document. The meaning of an acronym is usually indicated once, when it first occurs in the text.

A/D Analog to Digital

ADL Architecture Description Language

AGU Address Generation Unit ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction-set Processor

ASP Application-Specific Processor

ASPE Adaptive Stream Processing Engine

ASSP Application-Specific Signal Product

AVO Arithmetic Vector Operation

C2C Car-to-Car

C2I Car-to-Infrastructure CHDEC Channel Decoder

CIC Cascaded Integrator Comb CIF Common Interleaved Frame

CISC Complex Instruction-Set Computer

CSS Control Sub-System

CWA Component-Wise Addition

CWL Component-Wise Look-Up Table

CWP Component-Wise Product CWS Component-Wise Square

CWSM Component-Wise Square of Modulus

D/A Digital to Analog

DAB Digital Audio Broadcasting

DDR Double Data Rate

DDS Direct Digital Synthesizer

DEINTL Deinterleaver

DFT Discrete Fourier Transform

DQPSK Differential QPSK DSP Digital Signal Processor

DSRC Dedicated Short Range Communication

DXP Deep eXecution Processor

ETSI European Telecommunications Standards Institute

FCC Federal Communications Commission

FDD Frequency Division Duplex

xviii List of Tables

FEP Front-End Processor

FFT Fast Fourier Transform

FIB Fast Information Block

FIC Fast Information Channel

FIR Finite Impulse Response

FPGA Field Programmable Gate

FPGA Field Programmable Gate Array freeRTOS free Real-Time Operating System

FU Functional Unit GP General Purpose

GPP General Purpose Processor HDL Hardware Description Language

HR Hardware Radio HW Hardware

IDFT Inverse Discrete Fourier Transform

IFFT Inverse Fast Fourier Transform

IIR Infinite Impulse Response

INTL Interleaver

IPC Interpolation Control

ISA Instruction-Set Architecture

ISR Ideal Software Radio

ISI Inter Symbol Interference

ITS Intelligent Transport System

LISA Language for Instruction-Set Architectures

LTE Long Term Evolution LTS Long Training Symbol

LUT Look-up Table

MAC Media Access Control

MIMD Multiple Instruction Multiple Data

MIMO Multiple Input Multiple Output

MIO Input / Output Data Space (FEP)

MIPS Millions of Instructions Per Second

MMSE Minimum Mean Square Error

MOPS Millions of Operations Per Second

MOV Move

MPDU MAC Protocol Data Unit MSC Main Service Channel MSS Memory Sub-System

NCO Numerically Controlled Oscillator

NoC Network on Chip

OFDM/A Orthogonal Frequency Division Multiplexing / Multiple Access

OS Operating System

PE Processing Entity

PER Packet Error Rate

PD Pre-Distortion

PHY Physical

PLL Phase-Locked Loop PM Program Memory PP Preprocessor PSD Power Spectral Density

PU Processing Unit RF Radio Frequency

RISC Reduced Instruction-Set Computer

RTEMS Real-Time Executive for Multiprocessor Systems

RTL Register Transfer Level

RTV Roadside To Vehicle

RX Receiver Chain

SC Synchronization Channel

SC-FDMA Single Carrier Frequency Division Multiple Access

SCR Software Controlled Radio SDMA Space Division Multiple Access

SDR Software Defined Radio

SEQ Sequencer Unit

SIMD Single Instruction Multiple Data

SIMT Single Instruction stream Multiple Tasks

SNR Signal to Noise Ratio SISO Single Input Single Output

SoC Software on Chip SRC Sample Rate Converter

STA Synchronous Transfer Architecture

STS Short Training Symbol

SU Storage Unit SW Software

TDD Time Division Duplex TMP Temporary Memory

TTA Task Triggered Architecture

TWD Twiddle Factor Memory

TX Transmitter Chain

UC Microcontroller

UCM Microcontroller Program Memory

USR Ultimate Software Radio

USRP Universal Software Radio Peripheral

VANET Vehicular Ad Hoc Network VCO Voltage Controlled Oscillator VLIW Very Long Instruction Word

VECS Vector Sum

VECSI Vector Shift

VMM Vector Max / Min

VTV Vehicle to Vehicle

WAVE Wireless Access in Vehicular Environments

W-CDMA Wideband Code Division Multiple Access

WIF Wireless Innovation Forum WIM Window Invalid Mask

WLAN Wireless Local Area Network

WSU Wireless Safety Unit

XX ACRONYMS

## **Chapter 1**

## Introduction

#### 1.1 Motivation and Problem Statement

Today, wireless communication applications have become a major part in our life. Almost every day we check our emails either on smartphones or on personal computers via Wireless Local Area Network (WLAN) connections. Besides we communicate via our mobile phones or we consult navigation systems or online maps to find our way in case we have lost our bearings. Especially for the young generation it is impossible to imagine living in a world where they cannot be connected to their friends at any place and at any time. More and more companies have recognized this trend and seek to bring new products to the market that integrate more applications in only one device, that is smaller and lighter, that costs less and that has a higher performance than competing ones.

Another interesting market for wireless communication devices can be found in the automotive industry. It is a well known fact that the demographic change leads to a rising percentage of old people, especially in Europe. In countries like Germany where there is no age limit for car driving, there is a high need for new safety applications like speed measurements, obstacle warnings or distance measurements to the car driving in front. Two key terms in this context are Car-to-Car communication (C2C) and Car-to-Infrastructure (C2I) communication which also include the provision of non-safety applications like toll collection, tourist information or mobile internet. Standards of interest are IEEE 802.11p which is an enhancement of the well known IEEE 802.11a standard used for WLAN connections, and ETSI DAB (Digital Audio Broadcasting). To combine these two standards, two approaches are imaginable. Either they are implemented individually and come with their own receivers and transmitters that have to be integrated in the car, or both of them are combined in only one device. As it is the case for the mobile phone market, these devices should be small, cheap, of high performance and should be easily adaptable to future standards. Especially the latter is very time consuming and costly when integrating separate standard technologies in a car. Therefore, a single architecture that is capable to process whatever wireless communication standard is the preferable solution, especially as there is a high interest in combining IEEE 802.11p with LTE (3GPP Long Term Evolution) in vehicular system in the near future. To deal with these increasing requirements for reconfigurable radio architectures is a very challenging task. One solution can be found in the context of Software Defined Radio (SDR). A major aim of SDR is to provide flexible platform solutions supporting a wide range of different wireless communication standards in a multimodal fashion. This approach does not only come with the advantage of a faster development and a faster deployment of new standards but also with the automatic adoption to the surroundings.

2 1. Introduction

As initially stated, we exemplify the execution of latency critical standards on the ExpressMIMO platform by means of the IEEE 802.11p standard. We further investigate in the combination with a DAB receiver. As IEEE 802.11p has been in draft version till July 2010, efficient physical layer receiver implementations are still an open research topic. And to our knowledge, so far little effort has been spent on the description of a possible multimodal SDR platform processing of these two standards of interest.

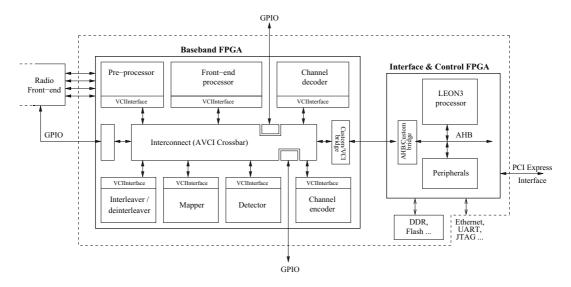

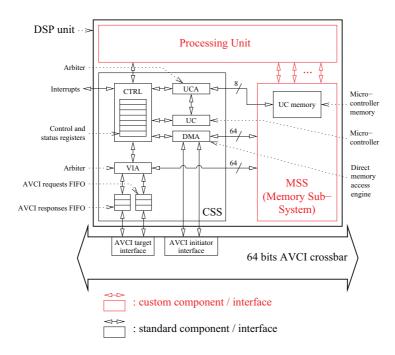

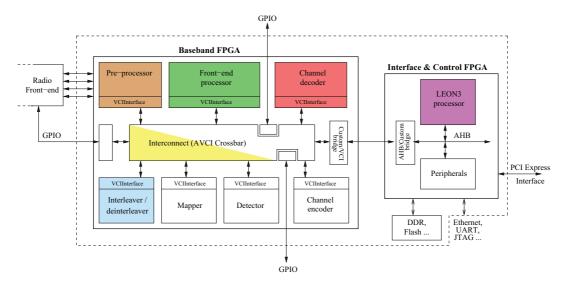

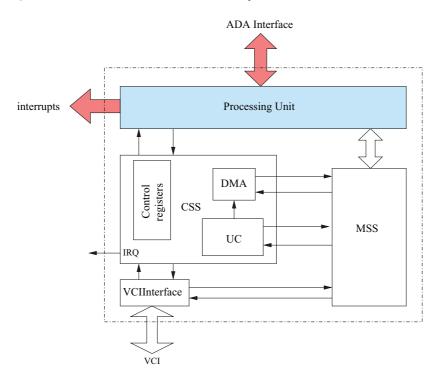

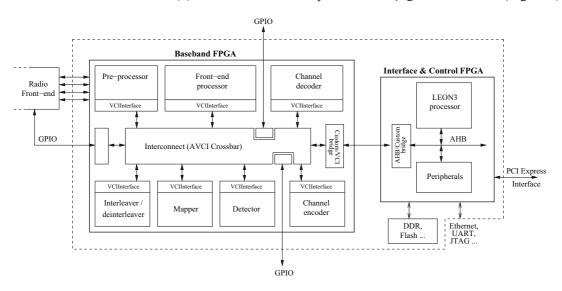

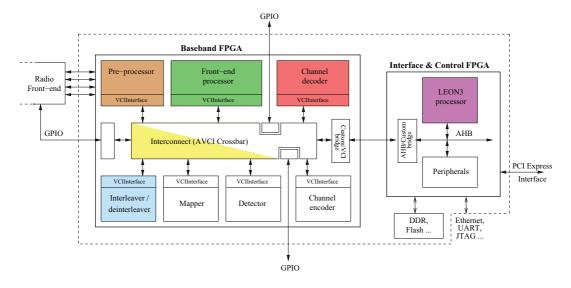

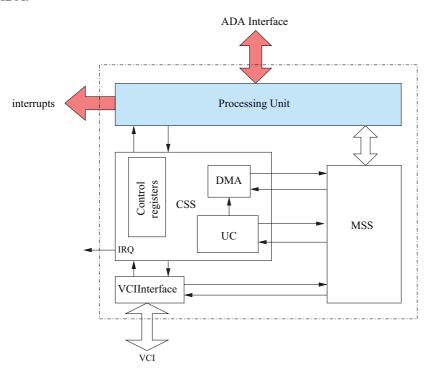

The chosen target platform is the OpenAirInterface ExpressMIMO platform developed by Eurecom and Télécom ParisTech. In contrast to other SDR platforms, the baseband processing functions are split over several independent Digital Signal Processor (DSP) engines or hardware accelerators like Channel De/Encoder, (De)Interleaver or Front-End Processor (FEP) which can be executed in parallel. This enables not only a higher performance of the whole design but further allows an easy component replacement in case future updates become necessary. The platform is capable to process up to eight different channels simultaneously (four channels in transmission, four in reception) by reusing the existing programmable resources. Main design challenge is the synchronization of these resources by providing a maximum accuracy and by meeting all the real-time requirements. The platform can further be emulated with the Library for ExpressMIMO baseband, called *libembb*, enabling an easy receiver validation and verification in a pure software environment.

At the very beginning of this thesis, the work on this platform was still ongoing. The presented receiver is thus the very first complete design that has been developed and evaluated on this target platform and that was emulated with the help of libembb. It was therefore serving as a first proof of concept of the whole design. Executing standards that operate on very small vector lengths, like IEEE 802.11p, require a fast baseband processing engine. So choosing this standard as a first use case permitted us to evaluate the current platform design to find bottlenecks and possible solutions to overcome them.

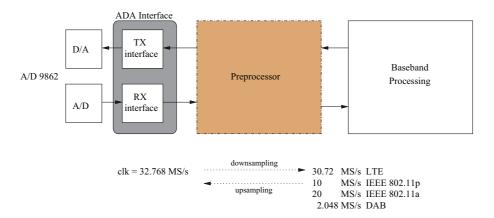

To pave the way for a complete receiver chain, the Preprocessor prototype had to be designed. The latter connects the external Analog to Digital (A/D) and Digital to Analog (D/A) converters with the entire platform and embeds among others a Sample Rate Converter (SRC) for sample rate adjustment and I/Q imbalance correction.

To achieve all these contributions, the basic objectives have been grouped in five different tasks which are more detailed in the following:

- 1. The first step is the **emulation of the IEEE 802.11p receiver with the help of the Library for ExpressMIMO baseband (libembb)** to (1) validate the chosen algorithms in a pure software environment, (2) to verify if the platform functionality is sufficient for the IEEE 802.11p receiver design and (3) to obtain first performance figures based on the pure processing time of the DSP engines. This task is an iterative one. In case it already turns out at this step, that real-time processing is not possible even when neglecting the communication overhead, the algorithms have to be reworked and verified again.

- 2. After a successful completion of the first task, the development continues with the implementation of the IEEE 802.11p receiver and its performance evaluation on the ExpressMIMO platform. This proof of concept comprises a cycle accurate simulation in Modelsim and the receiver validation on the real hardware platform.

- 3. Once the work on the IEEE 802.11p receiver is finalized, we focus on the question how DAB and IEEE 802.11p can be executed simultaneously on the ExpressMIMO platform. Due to different standard properties, this task is very challenging. For the implementation

- of a scheduler prototype we recall the performance figures obtained with libembb to derive basic guidelines for an efficient standard scheduling.

- 4. The identification of design bottlenecks and the provision of possible solutions is related to the tests on the hardware platform as mentioned in the second task. Based on the obtained results, possible algorithmic and design improvements are identified and possible solutions are provided and implemented.

- 5. To complete the IEEE 802.11p receiver chain, the final task includes the **implementation** of a Preprocessor DSP engine prototype. Here we mainly focus on the SRC as the most critical part of the Preprocessor in terms of area and space consumption.

#### 1.2 Outline and Contributions

The work presented in this thesis is structured as follows:

- First an overview of the basic terminology when talking about SDR applications is given in Chapter 2. Besides a presentation of latest SDR systems from academia and industry, a detailed description of the OpenAirInterface ExpressMIMO platform is provided. This description includes a detailed overview of the architecture as well as a presentation of the basic design methodology.

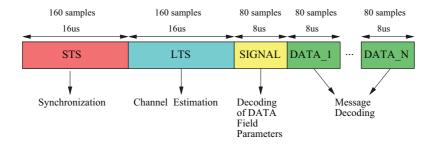

- 2. The IEEE 802.11p receiver is presented in Chapter 3. IEEE 802.11p is an enhancement of the well studied IEEE 802.11a standard commonly used in WLAN systems. In contrast to the latter, the IEEE 802.11p bandwidth has been reduced by one half, from 20 MHz to 10 MHz, to obtain OFDM (Orthogonal Frequency Division Multiplexing) symbols that are longer in time domain. This results not only in systems with large delay spreads to avoid Inter Symbol Interference (ISI) but also in stronger latency requirements which is a major design challenge as it requires a very fast baseband engine. Although the standard has been in draft form till July 2010, there are already few academic and some industrial transceiver solutions available. These solutions are mostly limited to the automotive context so that an efficient transceiver design on SDR platforms that are limited to wireless communications standards in general is still an open research topic. Implementing the IEEE 802.11p receiver on the ExpressMIMO platform comes therefore with the advantage that there are no limitations in possible combinations with other standards like LTE. Especially the combination with the latter is of high interest for future applications. Besides, the strong latency requirements of IEEE 802.11p make this standard the ideal first use case for the platform as it allows us to identify possible design bottlenecks. The obtained results are further extended by a possible combination of IEEE 802.11p and DAB. The combination of C2C and C2I communication with information about traffic jams or merchandising applications within only one device enables a lot of different future car applications. Preferred target technology are flexible SDR platforms allowing the execution of these different standards at low costs. The work on this task is still an open research topic as the necessary scheduler design is very challenging. For its design it is very important to have first key figures at hand. The results of this work have been obtained within the DeuFrako project PROTON (Programmable telematics on-board unit) / PLATA (PLAteforme Télématique multistandard pour l'Automobile) [1]. The implementation of the DAB receiver was in the responsibility of our german project partners.

4 1. Introduction

Major contributions presented in this chapter are:

an efficient physical layer implementation of the IEEE 802.11p receiver prototype for the ExpressMIMO platform (without the Preprocessor) that has been validated on the platform itself

- a Matlab prototype of the IEEE 802.11p receiver for algorithmic validation

- an IEEE 802.11p receiver emulation prototype based on the Library for ExpressMIMO baseband. The presented receiver is the first complete design implemented with the help of this library

- the identification of possible design improvements as well as their implementation. These are especially of interest for standards operating on short data sets.

- the derivation of a low latency scheduler design to execute multiple platform DSP engines simultaneously

- a detailed comparison of IEEE 802.11p and DAB

- a runtime performance comparison of IEEE 802.11p and DAB based on their emulation prototypes

- a derivation of basic guidelines for an efficient IEEE 802.11p and DAB scheduling on the ExpressMIMO platform as well as an implementation of a first scheduler design in software

Results have been presented and / or published

- (a) at the Acropolis Summer School 2012 on Cognitive Wireless Communications (Poster Presentation)

- (b) at the 7th Karlsruhe Workshop of Software Defined Radios [2]

- (c) at the 15th EUROMICRO Conference on Digital System Design (DSD'12) [3]

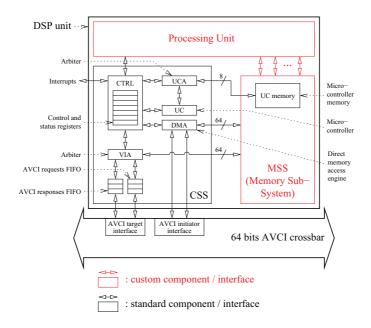

- 3. One design bottleneck that has been identified in the previous chapter is the need for an optimized FEP design for standards operating on short data sets when Field Programmable Gate Arrays (FPGAs) are chosen as target technology. Limitations of this design were related to the huge communication overhead when compared to the pure execution time for short vector lengths. The FEP contains a vector processing unit and a DFT (Discrete Fourier Transform) / IDFT (Inverse Discrete Fourier Transform) unit and allows to implement different air-interface algorithms like channel estimation or synchronization. To overcome the observed limitations, the vector processing unit has been replaced by an Application Specific Instruction-set Processor (ASIP) solution. For development we have chosen the Language for Instruction-Set Architectures (LISA) that has gained commercial acceptance over the past years. To evaluate the proposed architecture, we compare it to the programmable DSP solution as well as to two recent ASIPs from academia. The comparison is based on the actual processing related to the cycle counts.

In Chapter 4 two different ASIP solutions are presented. The first one is based on the old FEP specification that has been reworked to gain a higher performance of the design. Major contribution is the second version of the ASIP that has been extended by general purpose instructions and whose internal latencies have been decreased significantly.

The obtained results of this work have been accomplished in collaboration with RWTH Aachen, Germany, in context of the cluster of ICT research network of excellence NEW-COM++ [4] and in context of the European FP7 project ACROPOLIS (Advanced coexistence technologies for radio optimization and unlicensed spectrum) [5].

Major contributions presented in this chapter are:

- a first ASIP implementation based on the old FEP specification

- a second ASIP implementation based on the new FEP specification

- a thorough comparison of the latest ASIP version with the programmable FEP DSP engine as well as with different ASIP solutions from academia

Results have been presented and / or published

- (a) at workshops of the ACROPOLIS project

- (b) within an official research deliverable of NEWCOM++ [6]

- (c) at the DASIP'12 conference [7]

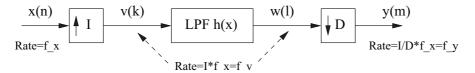

- 4. In the remainder of this thesis we focus on the design of a first Preprocessor DSP engine (Chapter 5) which is the only missing DSP engine in the IEEE 802.11p receiver chain. The Preprocessor connects the A/D, D/A converter interface with the remaining baseband engine and is responsible among others for I/Q imbalance correction, sample synchronous interrupt generation, framing and sample rate conversion. Most critical is the Sample Rate Converter (SRC) whose behavior can change dynamically at runtime. The SRC deals with the relation between the sampling rate at the A/D, D/A converters side and the baseband side. Processing the converters with a fixed master clock comes with the advantage of a low phase noise. In the past, one SRC was dedicated to each standard of interest but for the ExpressMIMO platform, this approach is too space consuming. That is why one fractional SRC architecture capable to process up- and downsampling is preferred.

The obtained results of this work have been accomplished within the cluster of ICT research network of excellence NEWCOM++.

Major contributions presented in this chapter are:

- a design of a fractional SRC able to process up to eight different channels (four in reception and four in transmission). All channels are executed on the same parameterizable hardware architecture. To guarantee a continuous filter processing, context switches between them happen instantaneously without any delay.

- an implementation of a first Preprocessor prototype for proof of concept and to complete the IEEE 802.11p receiver chain.

- an implementation of different C-models for design validation and verification.

Results have been presented and / or published

- (a) at the NEWCOM++ Winterschool on "Flexible Radio and Related Technologies", 2009

- (b) at the 6th Karlsruhe Workshop of Software Defined Radios [8]

- (c) in the FREQUENZ journal [9]

| 6 |    |                                                                                                                                           |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5. | The report finally concludes with the derivation of guidelines for a further standard deployment on the ExpressMIMO platform in Chapter 6 |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

|   |    |                                                                                                                                           |

## Chapter 2

## **SDR Baseband Processing**

The need for the design of flexible SDR platforms for the automotive context is the main motivation for the work presented in this thesis. This chapter enhances some basic terminology and presents the different possible solutions to be considered when talking about SDR systems. These solutions motivate the implementation of the chosen target platform presented in Section 2.3. Besides architectural details of the OpenAirInterface ExpressMIMO platform we further introduce the related software emulation environment and describe the basic development methodology of transceiver applications.

#### 2.1 Software Defined Radio

During the past years two major trends could be observed in the domain of wireless communications. Not only that the number of wireless communications standards was increasing rapidly, more and more standards have also been merged in more sophisticated devices like mobiles phones that include GPS and internet. To keep these devices as small as possible one preferable solution is the design of a global system that can also easily be updated to future standards. Costs are reduced not only because of the decreased manufacturing costs but also due to the decreased (re)design time in case of standard upgrades.

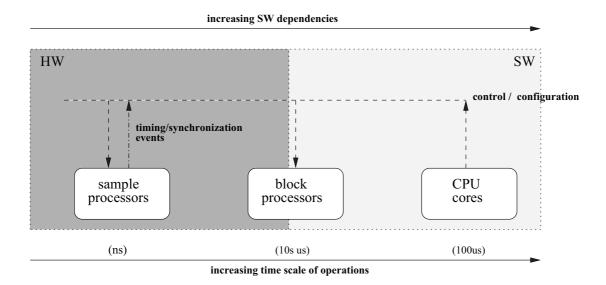

One solution to this challenging problem has been proposed by J. Mitola in [10] where he introduced the term of Software Defined Radio. Based on his initial definition, SDR has further been defined by the Wireless Innovation Forum (WIF, former SDR Forum) [11] and the EU Reconfiguration Radio Colloquium [12]. According to these sources, the ideal interpretation of SDR is a system where (1) the wideband digitization occurs next to the antenna and (2) where the actual transceiver application is running either on a desktop PC or on a very fast General Purpose Processor (GPP). Till now, common processors are still not fast enough to provide an efficient implementation of such a system [13]. Therefore today's approaches focus on baseband design for flexible hardware platforms, multiprocessor systems or Network on Chips (NoCs). The candidates for such designs are manifold and comprise among others Application-Specific Integrated Circuits (ASICs), ASIPs, DSPs or FPGAs. The final design choice depends on the application to be designed and related to that on different criteria like power efficiency, flexibility, reconfigurability and usability. Flexibility in SDR systems is usually related to reconfigurability and thus representing a system that is able to change its behavior dynamically in case the surrounding environment is changing. Or more specifically, the wireless network as well as its equipment can dynamically adapt to environment changes. Reconfigurability can be increased by two different factors: (1) a higher programmability of the design typically achieved by using FPGAs or microcontrollers and (2) by a modular design approach. The more modular an architecture is, the easier it is to replace components in case future standards or improvements of current standards require design upgrades.

SDR systems have first been developed for military targets in the context of projects like SPEAK-easy [14] and JTRS [15]. Since then, SDR has moved towards civil and daily life applications like the automotive context on which we will mainly direct our attention in this thesis. However, an exact definition of SDR can still not be found in the literature. In 2005, the Federal Communications Commission (FCC) defined SDR as "a radio that includes a transmitter in which operating parameters of frequency range, modulation type or maximum output power (either radiated or conducted), or the circumstances under which the transmitter operates in accordance with Commission rules, can be altered by making a change in software without making any changes to hardware components that affect the radio frequency emissions." [16]. In contrast, WIF has split SDR in several so-called *tiers*. Their separation is performed by means of capabilities and thus the extend of (re)configurability of a certain system.

#### • Tier 0 - Hardware Radio (HR)

Tier 0 is the simplest example of an SDR system. For its implementation only hardware components are used which results in a complete redesign in case of modifications.

#### • Tier 1 - Software Controlled Radio (SCR)

In this tier, the control functions are implemented in software, resulting in a limited number of programmable functions like interconnections.

#### • Tier 2 - Software Defined Radio (SDR)

Designs related to this tier are usually split into two parts: the control part implemented in software and the flexible hardware part. For the design of the latter, dedicated hardware blocks such as ASICs, FPGAs, DSPs, etc can be used to increase the flexibility of the design. A well-known tier 2 application are SDR platforms.

#### • Tier 3 - Ideal Software Radio (ISR)

At this tier, the entire system is programmable. Analog conversion is performed only at the antenna, speaker and microphones.

#### • Tier 4 - Ultimate Software Radio (USR)

Tier 4 has been defined for comparison purposes only. Here the system is fully programmable and switches between the air-interfaces can be performed in milliseconds.

The work presented in this thesis can be assigned to tier 2 as the chosen target architecture is a flexible SDR platform. To motivate this design choice an overview of different SDR systems is given in Section 2.2.

#### 2.2 Related Work

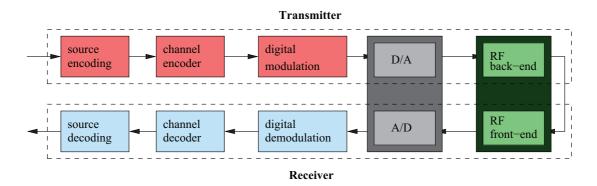

Today's wireless communication systems all follow a common processing flow illustrated in Fig. 2.1. After receiving the signal samples from the Media Access Control (MAC) layer, the transmitter chain, TX, embraces source encoding, channel encoding, digital modulation and D/A conversion before the signal is transmitted through the Radio Frequency (RF) back-end. In the other direction, the receiver chain, RX, is composed of an A/D converter, digital demodulation, channel decoding and source decoding before the samples are given to the MAC layer.

Figure 2.1: Overview of a Wireless Communication System