## Large-scale network simulation over heterogeneous computing architecture

Bilel Ben Romdhanne

#### ▶ To cite this version:

Bilel Ben Romdhanne. Large-scale network simulation over heterogeneous computing architecture. Other [cs.OH]. Télécom ParisTech, 2013. English. NNT: 2013ENST0088. tel-01151414

## HAL Id: tel-01151414 https://pastel.hal.science/tel-01151414

Submitted on 12 May 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Doctorat ParisTech**

## THÈSE

pour obtenir le grade de docteur délivré par

## Télécom ParisTech

présentée et soutenue publiquement par

#### **BIIEL BEN ROMDHANNE**

le 16 Décembre 2013

## Simulation des Réseaux à Grande Echelle sur les Architectures de Calculs Hétérogènes

Directeurs de thèse : Navid NIKAEIN et Christian BONNET

#### Jury

M. Thierry TURLETTI, DR, Diana, INRIA Sophia Antipolis M. Kaylan S. PERUMALLA, Professeur adjoint, School of CSE, Georgia Tech M. Walid DABBOUS, DR, Diana, INRIA Sophia Antipolis Mme. Elisabeth BRUNET, Professeur assistant, G2, Telecom SudParis Mme. Margaret L.LOPER, Directeur chercheur, ICL, Georgia Tech Research Institut M. Christian BONNET, Professeur, Communications mobiles, Eurecom

M. Navid NIKAEIN, Professeur assistant, Communications mobiles, Eurecom

Président Rapporteur Rapporteur Examinateur Examinateur Directeur Directeur

#### TELECOM PARISTECH

## ÉCOLE DOCTORALE STIC SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

## **THÈSE**

pour obtenir le titre de

#### Docteur en Sciences

de TELECOM ParisTech

#### Mention Informatique

présentée et soutenue par

### Bilel BEN ROMDHANNE

## Simulation des Réseaux à grande Échelle sur les architectures de calcules hètèrogénes

Thèse dirigée par Navid NIKAEIN et Christian BONNET Laboratoire EURECOM, Sophia Antipolis

soutenue le 16 Decembre 2013, devant le jury composé de:

## Acknowledgments

I think that one of my major motivation during the last three years, is my dream to write the following: I dedicate this work to my mother that supported, encouraged, powered and resourced me during too many years (thirteen exactly). A special dedication for my father also which gives me the example for a respectable life. I hope that this work will be the pride of my parents. I want to thank my lovely wife which shares with me the same experience, and sharing two PhD at the same time in the same house, is not easy at all! Finally, I hope that one day, I will read a similar dedication written by my young son Ahmed Yessine.

## Summary

## Large-scale network simulation over heterogeneous Computing architecture

The simulation is a primary step on the evaluation process of modern networked systems. The scalability and efficiency of such a tool in view of increasing complexity of the emerging networks is a key to derive valuable results. The discrete event simulation is recognized as the most scalable model that copes with both parallel and distributed architecture. Nevertheless, the recent hardware provides new heterogeneous computing resources that can be exploited in parallel.

The main scope of this thesis is to provide a new mechanisms and optimizations that enable efficient and scalable parallel simulation using heterogeneous computing node architecture including multicore CPU and GPU. To address the efficiency, we propose to describe the events that only differs in their data as a single entry to reduce the event management cost. At the run time, the proposed hybrid scheduler will dispatch and inject the events on the most appropriate computing target based on the event descriptor and the current load obtained through a feedback mechanisms such that the hardware usage rate is maximized. Results have shown a significant gain of 100 times compared to traditional CPU based approaches.

In order to increase the scalability of the system, we propose a new simulation model, denoted as general purpose coordinator-master-worker, to address jointly the challenge of distributed and parallel simulation at different levels. The performance of a distributed simulation that relies on the GP-CMW architecture tends toward the maximal theoretical efficiency in a homogeneous deployment. The scalability of such a simulation model is validated on the largest European GPU-based supercalculator the TGCC Curie with 1024 LPs each of which simulates up to 1 million nodes.

To further validate the efficiency and scalability of the proposed mechanisms and optimizations, we applied the event grouping, hybrid scheduling, and GP-CMW to popular network simulator NS-3. Results have demonstrated a gain of 25 times under a large scale deployment including 288 GPUs and 1152 CPU on the TGCC Curie.

## Résumé

## Simulation des Réseaux à grande échelle sur les architectures de calcules hètèrogénes

La simulation est une étape primordiale dans l'évolution des systèmes en réseaux. L'évolutivité et l'efficacité des outils de simulation est une clef principale de l'objectivité des résultats obtenue, étant donné la complexité croissante des nouveaux des réseaux sans-fils. La simulation a évà "nement discret est parfaitement adéquate au passage à l'échelle, cependant les architectures logiciel existantes ne profitent pas des avancées récente du matériel informatique comme les processeurs parallèle et les coprocesseurs graphique.

Dans ce contexte, l'objectif de cette thèse est de proposer des mécanismes d'optimisation qui permettent de surpasser les limitations des approches actuelles en combinant l'utilisation des ressources de calcules hétérogéne. Pour répondre à la problématique de l'efficacité, nous proposons de changer la représentation d'événement, d'une représentation bijective (évènement-descripteur) à une représentation injective (groupe d'évènements-descripteur). Cette approche permet de réduire la complexité de l'ordonnancement d'une part et de maximiser la capacité d'exécuter massivement des événements en parallèle d'autre part.

Dans ce sens, nous proposons une approche d'ordonnancement d'événements hybride qui se base sur un enrichissement du descripteur pour maximiser le degré de parallélisme en combinons la capacité de calcule du CPU et du GPU dans une même simulation. Les résultats comparatives montre un gain en terme de temps de simulation de l'ordre de 100x en comparaison avec une exécution équivalente sur CPU uniquement.

Pour répondre à la problématique d'évolutivité du système, nous proposons une nouvelle architecture distribuée basée sur trois acteurs logiciels : Un coordonnateur, un master et un worker. Cette architecture réponde simultanément aux limitations des architectures parallèles et distribuées. Nous proposons aussi une version optimisée de l'architecture qui maximise la stabilité et réduit la latence de la communication. Les expérimentations de validation ont était sur le supercalculateur hybride TGCC Curie avec 1024 instance, chacune simule un million de noeuds.

Pour proposer une valider grand-publique de notre approche, nous avons apportés des modifications au simulateur de réseaux NS-3, les modifications portent sur le générateur, l'ordonnanceur et l'exécuteur des évènements.

Les résultats comparatifs apportent la preuve que l'approche proposé ouvre des nouveaux horizons de passage à l'échelle. Nous avons pu atteindre un gain de 25x en combinant le groupement des évènements avec l'ordonnancement hybride.

## Contents

| 1 | Intr | $\operatorname{oducti}$ | ion                                              | 3          |

|---|------|-------------------------|--------------------------------------------------|------------|

|   | 1.1  | Motiva                  | ation and Objectives                             | 3          |

|   | 1.2  | Contri                  | ibutions Storyline                               | 4          |

|   | 1.3  | Thesis                  | Structure                                        | 6          |

|   | 1.4  | Public                  | eations                                          | 7          |

|   | 1.5  | Projec                  | et Deliverables                                  | 8          |

| Ι | Ba   | ckgrou                  | ınd                                              | 9          |

| 2 | Net  | work I                  | Experimentation                                  | 11         |

|   | 2.1  | Introd                  | uction                                           | 11         |

|   | 2.2  | Netwo                   | rk Experimentation Tools                         | 11         |

|   |      | 2.2.1                   | Real world Field Trial                           | 11         |

|   |      | 2.2.2                   | Real world Testbed                               | 12         |

|   |      | 2.2.3                   | Emulation Testbed                                | 13         |

|   |      | 2.2.4                   | Simulation Testbed                               | 13         |

|   |      | 2.2.5                   | Hybrid Testbed                                   | 14         |

|   | 2.3  | Netwo                   | rk Experimentation Aspects                       | 15         |

| 3 | Disc | crete E                 | Event Simulation                                 | 19         |

|   | 3.1  |                         |                                                  | 19         |

|   | 3.2  | Discre                  | te-Event Simulation                              | 19         |

|   |      | 3.2.1                   | Terminology and Components                       | 19         |

|   |      | 3.2.2                   | The Principle                                    | 20         |

|   | 3.3  | Paralle                 | el Discrete Event Simulation                     | 20         |

|   |      | 3.3.1                   | Discrete Event Simulation Limits                 | 21         |

|   |      | 3.3.2                   | Principles of Parallel Discrete Event Simulation | 21         |

|   |      | 3.3.3                   | Parallel Simulation Model and Algorithms         | 22         |

| 4 | Har  | dware                   | Trends                                           | <b>2</b> 5 |

|   | 4.1  |                         |                                                  | 25         |

|   | 4.2  | Evolut                  |                                                  | 25         |

|   |      | 4.2.1                   | CPU: Historical Evolution and Trends             | 25         |

|   |      | 4.2.2                   | GPU: Historical Evolution and Trends             | 26         |

|   |      | 4.2.3                   | Emerging Solutions                               | 27         |

|   |      | 4.2.4                   | Multi-Core accelerator                           | 27         |

|   | 4.3  | Paralle                 | el Programming: Models and API                   | 28         |

|   |      | 4.3.1                   | Pthreads                                         | 28         |

|   |      | 4.3.2                   | OpenMP                                           | 28         |

xii Contents

|   |     | 4.3.3            | MPI                                                    | 29         |

|---|-----|------------------|--------------------------------------------------------|------------|

|   |     | 4.3.4            | CUDA                                                   | 29         |

|   |     | 4.3.5            | OpenCL                                                 | 29         |

| _ | ъ 1 | . 1.33           | 77 1                                                   | 0.1        |

| 5 |     | ated V           |                                                        | 31         |

|   | 5.1 |                  | luction                                                | 31         |

|   | 5.2 | _                | Scale Simulation                                       | 31         |

|   | 5.3 |                  | Issues                                                 | 33         |

|   |     | 5.3.1            | Data Representation                                    | 33         |

|   | E 1 | 5.3.2            | Event Scheduling                                       | 34         |

|   | 5.4 | Consid           | derations Heterogeneous Computing Considerations       | 34         |

| Π | Co  | ontrib           | utions                                                 | 39         |

| 6 | Cur | $\mathbf{etsim}$ | : An Experimentation Framework to Discover Scalability |            |

|   | Hor | rizons           |                                                        | 41         |

|   | 6.1 | Introd           | luction                                                | 41         |

|   | 6.2 | Funda            | mental Concepts                                        | 42         |

|   |     | 6.2.1            | The Worker Pool                                        | 43         |

|   |     | 6.2.2            | Separation Between an Event and Its Description        | 43         |

|   |     | 6.2.3            | Massive Parallel Event Generation                      | 43         |

|   | 6.3 | Cunet            | sim Software Architectures                             | 44         |

|   |     | 6.3.1            | The Worker Design                                      | 44         |

|   |     | 6.3.2            | The Master Design                                      | 46         |

|   |     | 6.3.3            | Legacy Architecture for Multi-Core CPU                 | 47         |

|   | 6.4 | Comp             | arative Performances Results                           | 48         |

|   |     | 6.4.1            | Simulation Runtime                                     | 50         |

|   | 6.5 | Techn            | ical Challenges of GPU-based Simulation                | 53         |

|   |     | 6.5.1            | Synchronization Challenge                              | 53         |

|   |     | 6.5.2            | Memory Management Challenge                            | 55         |

|   |     | 6.5.3            | Precision Issue                                        | 56         |

|   | 6.6 | Config           | guration Issues of GPU-Oriented Simulation             | 56         |

|   |     | 6.6.1            | Space Representation and partitioning                  | 56         |

|   |     | 6.6.2            | Tuning Parameters: Block Size as a Study Case          | 56         |

|   | 6.7 | Conclu           | usion                                                  | 58         |

| 7 | •   |                  | vents Scheduler                                        | <b>5</b> 9 |

|   | 7.1 |                  | luction                                                | 59         |

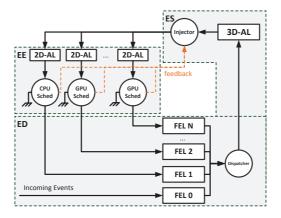

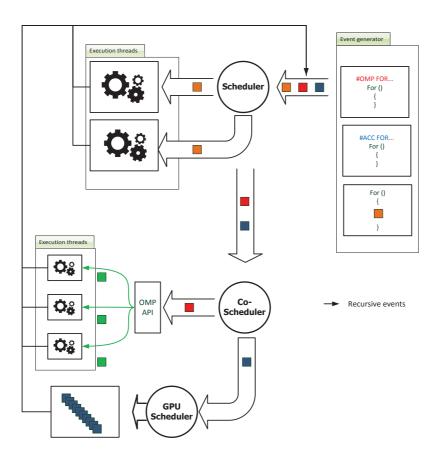

|   | 7.2 |                  | Tybrid Scheduler                                       | 61         |

|   |     | 7.2.1            | Model and Components                                   | 61         |

|   |     | 7.2.2            | Scheduling Algorithms                                  | 62         |

|   | 7.3 |                  | mance Evaluation                                       | 67         |

|   |     | 7.3.1            | Scenario & Setup                                       | 68         |

|   |     | 7.3.2            | Comparative Evaluation                                 | 69         |

|          | •••  |

|----------|------|

| Contents | X111 |

| Contents | AIII |

|          |      |

|              | 7.4<br>7.5<br>7.6 | 7.3.3 Performance Analysis                                              | 70<br>74<br>75<br>76 |

|--------------|-------------------|-------------------------------------------------------------------------|----------------------|

| 8            |                   | eral Purpose Coordinator-Master-Worker Model                            | 79                   |

| O            | 8.1               | Introduction                                                            | 79                   |

|              | 8.2               | The General Purpose Coordinator-Master-Worker Model                     | 81                   |

|              |                   | 8.2.1 Events Management: Description, Scheduling and Execution .        | 82                   |

|              |                   | 8.2.2 The Synchronization Mechanism of the GP-CMW Model                 | 87                   |

|              |                   | 8.2.3 GP-CMW Communication Model                                        | 88                   |

|              | 8.3               | Comparative Evaluation                                                  | 90                   |

|              |                   | 8.3.1 Comparative Performance Evaluation                                | 91                   |

|              |                   | 8.3.2 Inherent Performance Evaluation                                   | 93                   |

|              | 8.4               | Related Work                                                            | 101                  |

|              | 8.5               | Conclusion                                                              | 103                  |

| 9            | Stuc              | dy Case of PADS Methodology Deployment: NS-3                            | 105                  |

|              | 9.1               | Introduction                                                            | 105                  |

|              | 9.2               | Overview                                                                | 106                  |

|              | 9.3               | Events scheduling on NS-3                                               | 107                  |

|              | 9.4               | NS-3 Events scheduler extensions                                        | 109                  |

|              |                   | 9.4.1 The Explicit CPU Parallelism                                      | 110                  |

|              |                   | 9.4.2 The Implicit CPU Parallelism                                      | 111                  |

|              |                   | 9.4.3 The GPU Offloading                                                | 112                  |

|              |                   | 9.4.4 The Co-scheduler Approach                                         | 113                  |

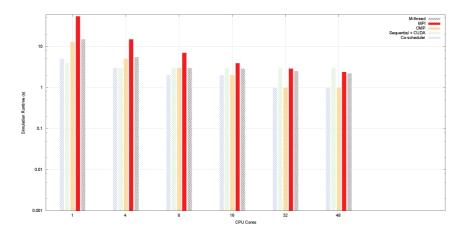

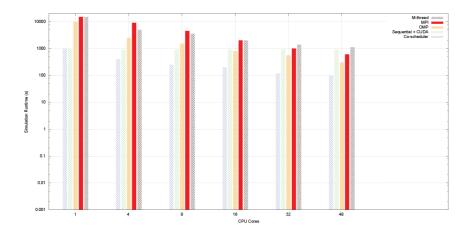

|              | 9.5               | Comparative evaluation                                                  | 115                  |

|              |                   | 9.5.1 Medium Load                                                       | 115                  |

|              |                   | 9.5.2 High Load                                                         | 116                  |

|              | 9.6               | Conclusion                                                              | 117                  |

|              |                   |                                                                         | 110                  |

| 111          | ı C               | onclusion                                                               | 119                  |

| 10           | Con               | clusion                                                                 | 121                  |

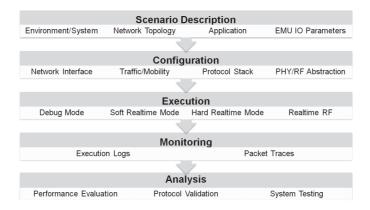

| $\mathbf{A}$ | Exp               | erimentation Methodology                                                | 123                  |

|              | A.1               | Introduction                                                            | 123                  |

|              | A.2               | Scientific Experimentation                                              | 124                  |

|              | A.3               | $Open Air Interface\ Experimentation\ methodology\ .\ .\ .\ .\ .\ .\ .$ | 124                  |

|              |                   | A.3.1 Open<br>Air<br>Interface Formal Experimentation Methodology       | 125                  |

|              |                   | A.3.2 Methodology Implementation                                        | 126                  |

|              | A.4               | Conclusion                                                              | 127                  |

| В            | Rés               | umé Étendue                                                             | 129                  |

| XIV          | Contents |

|--------------|----------|

|              |          |

| Bibliography | 151      |

| Dibliography | 191      |

## List of Figures

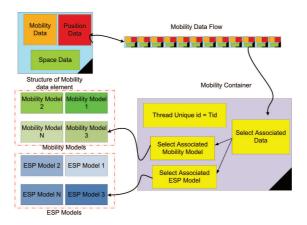

| 6.1  | Mobility Events pattern                                                |

|------|------------------------------------------------------------------------|

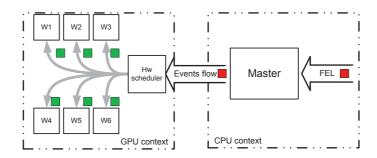

| 6.2  | Simplified master/workers model that targets GPU execution 47          |

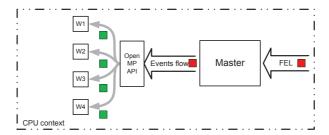

| 6.3  | Simplified master/workers model that targets CPU execution 48          |

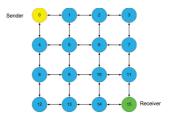

| 6.4  | Simple Grid Topology                                                   |

| 6.5  | End-to-End Packet Loss:                                                |

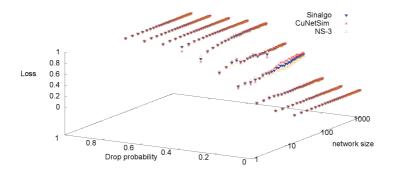

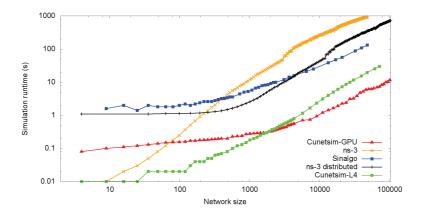

| 6.6  | Simulation runtime of the static network:                              |

| 6.7  | Simulation runtime of the mobile network:                              |

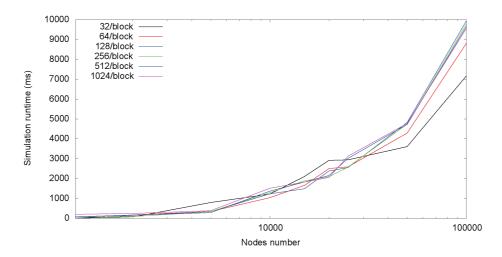

| 6.8  | Block size impact                                                      |

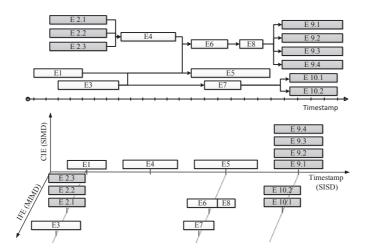

| 7.1  | Events reordering and storage: top figure schematizes an events de-    |

|      | pendency diagram while bottom figure schematizes how they will be      |

|      | reordered and stored. Events dependency is transformed to interval. 62 |

| 7.2  | Event scheduler model                                                  |

| 7.3  | Statistical table used for recalibration                               |

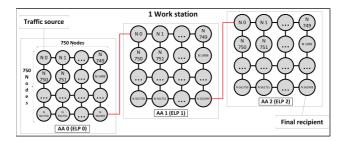

| 7.4  | Topology of the benchmarking scenario                                  |

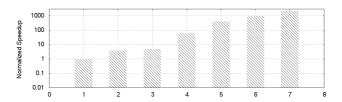

| 7.5  | Normalized speedup with respect to the sequential runtime 72           |

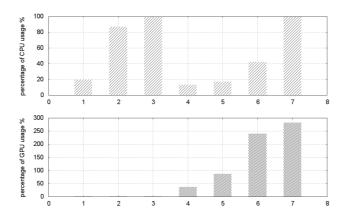

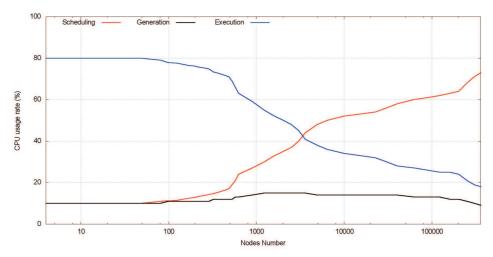

| 7.6  | The hardware usage rate                                                |

| 7.7  | The scheduling cost                                                    |

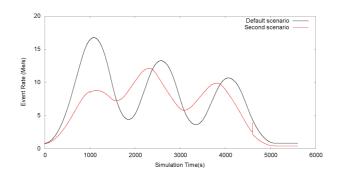

| 7.8  | Variation of the input rate vs Time                                    |

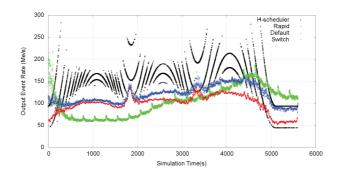

| 7.9  | Output event rate of different algorithms                              |

| 7.10 | Average decision path length during the simulation                     |

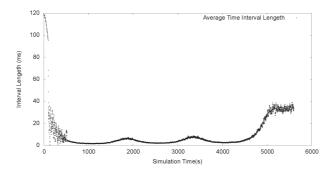

| 7.11 | Average interval length during the simulation. It closely reflects the |

|      | events dependency                                                      |

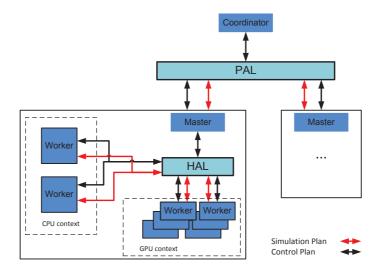

| 8.1  | The GP-CMW blocks diagram:                                             |

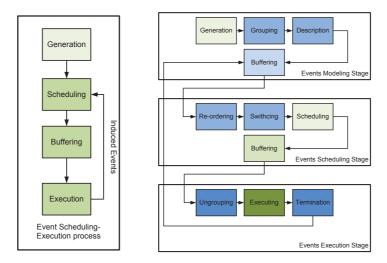

| 8.2  | Events Life Cycle                                                      |

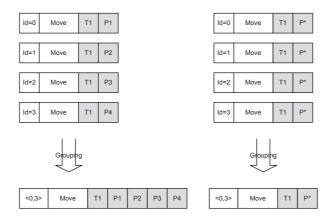

| 8.3  | Examples of events grouping:                                           |

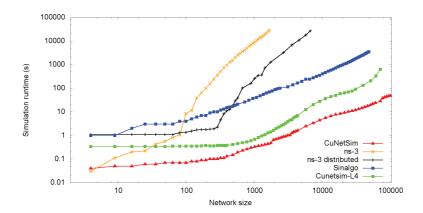

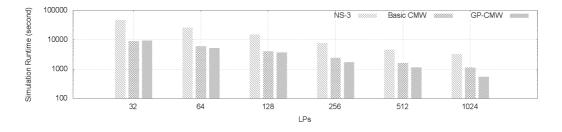

| 8.4  | The simulation runtime of the studied simulators:                      |

| 8.5  | The synchronization delay as a function of the number of LPs 93        |

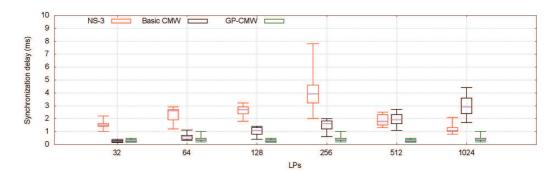

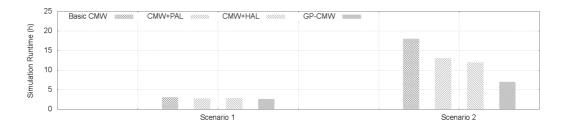

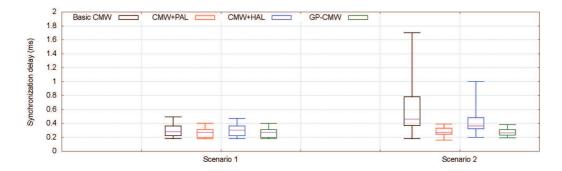

| 8.6  | The impact of the PAL and HAL on the simulation runtime: 96            |

| 8.7  | The synchronization delay as a function of the scenario and the con-   |

|      | figuration                                                             |

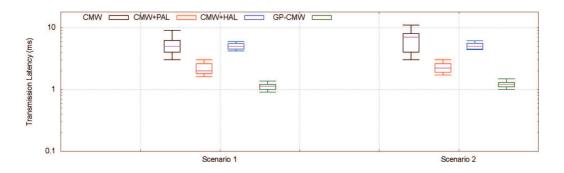

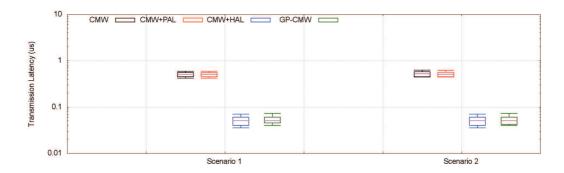

| 8.8  | The average external communication latency:                            |

| 8.9  | The average internal communication latency:                            |

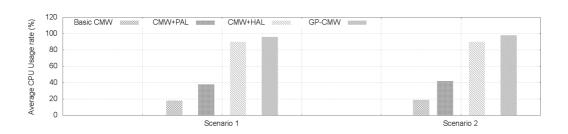

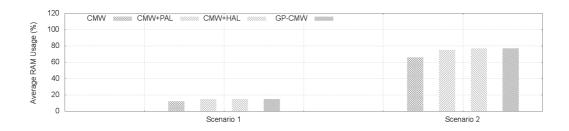

| 8.10 | The average CPU usage rate:                                            |

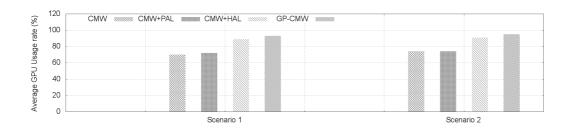

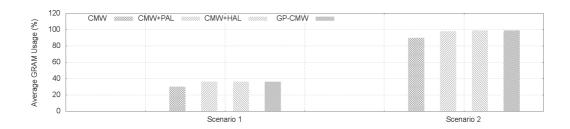

| 8.11 | The average GPU usage rate:                                            |

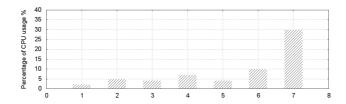

| 8.12 | The average RAM usage rate:                                            |

| 8.13 | The average GRAM usage rate:                                           |

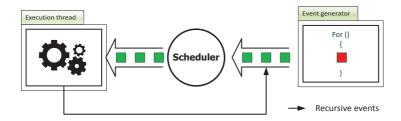

| 9.1  | Default NS-3events scheduling approach:                                |

xvi List of Figures

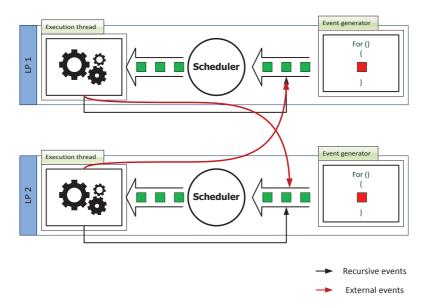

| 9.2 | Distributed event scheduling approach in NS3:                        | 108 |

|-----|----------------------------------------------------------------------|-----|

| 9.3 | Scheduling Cost as a function of nodes number                        | 110 |

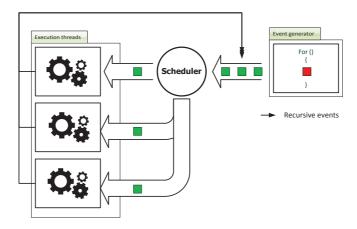

| 9.4 | Explicit CPU parallelism:                                            | 111 |

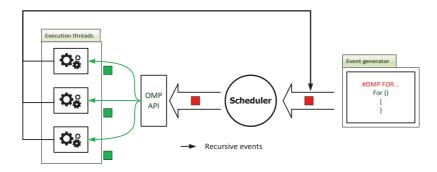

| 9.5 | Implicit CPU parallelism:                                            | 112 |

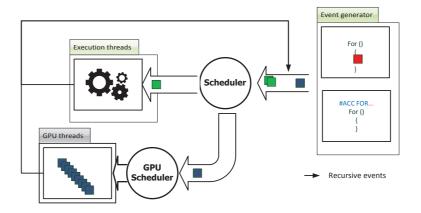

| 9.6 | GPU offloading:                                                      | 113 |

| 9.7 | CO-scheduling approach:                                              | 114 |

| 9.8 | Simulation runtime of each configuration as a function of the number |     |

|     | of CPU cores ( 1000 nodes)                                           | 117 |

| 9.9 | Simulation runtime of each configuration as a function of the number |     |

|     | of CPU cores (500K nodes)                                            | 118 |

|     |                                                                      |     |

| A.1 | Experimentation Workflow                                             | 125 |

| A.2 | The user experimentation workflow:                                   | 127 |

## List of Tables

| 2.1 | Characteristics of exciting experimentation tools | <br>17 |

|-----|---------------------------------------------------|--------|

| 7.1 | List of different scheduling approaches           | <br>69 |

## Acronyms

Here are the main acronyms used in this document. The meaning of an acronym is usually indicated once, when it first appears in the text.

OAI Open Air Interface CORE Core Emulator

FPGA Field-Programmable Gate Array

CPU Central Processing Unit GPU Graphic Processing Unit

SoC System on Chip NOC Network on Chip FSM Finite State Machine

EP Event Pattern

UDG Unit Disk Graph

QUDG Quas-Unit Disk Graph

GPGPU General-Purpose Processing on Graphic Processing Unit

CIE Cloned Independent Events IFE Independent Foreign Events

## Introduction

## 1.1 Motivation and Objectives

Over the last decades, we have witnessed a great progress and an increasing need for discrete event simulation in a large range of scientific application. In particular, discrete event paradigm is useful for time-stepped simulation, which provides leaps in time and asynchronous updates (at potentially staggered virtual times) to different parts of the state.

The distributed DES was recognized as mostly adequate for large scale and complex simulation since it supports distributed features. In that context, network simulation was a leading research area that provides a significant portion of recent innovation in term of discrete event simulation theory and practice. Especially, large scale simulation appears as a real need when targeting the study of large systems evolving hundreds of thousands of simulated elements such as network nodes. Distributed simulation that relies on independent logical processes (LP) which communicate through message is enough for traditional large scale simulation where nodes are easily isolated. This paradigm requires minimizing the interaction between LPs compared to that within each LP to maintain the efficiency of the system. However, when targeting to simulate intensive interactive systems such that of modern wireless and mobile network, this paradigm becomes obsolete: we need either a very large LP that cover all dependents elements, or a low communication latency for inter-LP communication. Indeed, recent hardware provides several new features that increases the available computing power but requires a modified software architecture. The main hardware innovation is the usage of multi-core resources which enable parallel processing. Currently, the usage of multi-computing resource on the same LP remains in exploration phases. One fundamental corner of the usage of many computing resources is the parallel event scheduling that aims to execute several events concurrently while conserving the simulation correctness. Accordingly, the main research motivation of this thesis is the scalability issue of discrete event simulation (DES) in view of the heterogeneous computing. This thesis emphasis fours objectives:

- Studying and evaluating the pertinence of using emerging computing solution on large scale simulation.

- Reconsidering the event-driven simulation concept to maximize the usage of heterogeneous computing solutions.

- Designing a scalable methodology for general purpose, large scale and intensive simulation.

- Proposing a new scheduling approach that unlocks the DES bottleneck.

## 1.2 Contributions Storyline

In the 2010/2011 time frame, when we started to work in this thesis, we set as objective to increase the scalability of the intern simulation/emulation framework OAI. However, this goal required that we first transform the platform, from the concept of rapid validation tool to that of scientific experimentation tool. Thus, before addressing the large scale issues, ensuring the reproducibility is a primary requirement that we must guarantee. Therefore, we design an experimentation methodology that defines a five-stepped workflow. That approach is largely inspired from existing methodologies used in large scale simulation and emulation frameworks [121, 117, 133]. When we started addressing the scalability issue, we first rely on a software engineering methodology that aims to identify computing bottlenecks and resolving them based on five possible approaches: GPU offloading, CPU parallelism, vector-processing parallelism, code optimization and compiling optimization. Each of these approaches provides a gain and induces an overhead. While this methodology delivers a real improvement in terms of performance and runtime, it becomes caducous when the overhead overpasses the gain. Accordingly, we admit the limit of this step once we reach the efficiency boundary.

With this experience in mind, we conclude that an architectural and fundamental work is required to propose an innovated answer to the scalability issue. Hence, we survey related works that discuss large scale simulation in the area of network simulation, and we determine four key issues:

- 1. Discrete event simulation is the most dominant approach to model large scale system while providing functional features such as the interoperability.

- 2. Event scheduling is a major issue in parallel simulation and more particularly, events-dependency detection is an expensive operation in terms of algorithm complexity.

- The communication between distinct machines remains a major limiting factor of distributed simulation. Indeed, FLOPS becomes cheap while the communication is expensive.

- 4. Backward compatibility with sequential system is always maintained, transforming parallel simulation into an extension rather than a standard.

These observations give rise to a new principal of events managements which is the generation of independent and parallel events, without subsequent control during the scheduling phase. Even if it looks like as a promising idea, its realization into the OAI requires a major redesign work which may impact several projects that use

it as a validation and experimental platform. Thus, occurs the idea of creating a new simulator to validate the concept of generating grouped event in one hand and the pertinence of using the GPU as a simulation context for parallel execution on the other hand. We expect to increase the simulation efficiency by reducing the simulation runtime for a given scale, but also increasing the simulation scalability by allowing a unique logical process to handle much more simulated elements than what can be done by a CPU. The proposed simulation framework is named as Cunetsim: CUDA network simulator. Initial implementation provides six elementary services: mobility, connectivity, buffers management, broadcasting, traffic generator and power management. Based on a GPGPU software design, the simulation processing is defined by a list of time-stamped entries. At each entry, all nodes process the same event but on different data. Conceptually, the event-scheduler handles one entry for all nodes. The GPU driver and hardware transform that entry into a group of threads, each of which processes an event of one node. According to this methodology, we take advantage of the hardware management of threads and the automatic hardware synchronization of simulated nodes. In contrast with traditional parallel simulation, we avoid complex scheduling policies that aim to detect event dependency. We also compress the event representation which in turn reduces the scheduling cost. While earliest results were promising in term of efficiency and scalability, new requirements emerge: how to communicate with the outside world? How to handle complex scenarios with heterogeneous node definition? And more importantly how to overcome the GPU memory size limitation?

The interesting results of the initial Cunetsim implementation simplify a new framework to create a parallel and generic version that features parallel simulation over multiple GPUs. Further, we introduce a dynamic event scheduler that handles variable inputs and an extended event generator to support realistic scenario. The concept of an entry evolves from being relative to all nodes to becoming relative to a sub group of simulated nodes. Nevertheless, the simulation logic remains invariant: an entry is a compressed representation of a group of events that will be executed in parallel. The design pattern that we adopt for this solution is the Master-worker model where the master is a CPU process that manages the simulation and workers are assimilated to the GPU cores that execute events. Unfortunately, the event scheduling remains a centralized path where all entries must flow before being executed. Thus, when the number of execution resources increases (several GPUs, each of which includes thousands of cores), the event scheduler reappears as a bottleneck. Accordingly, we conclude this research phase with two results: first, it is possible to use a great computing power for a very large logical process efficiently using the grouped events concept. Second, the event scheduling remains the main bottleneck for large scale parallel simulation if it is centralized.

To further push the scalability boundary, we go one step back, and we reconsider the hardware architecture: while the GPU is a powerful processor, it requires the CPU as a host. Moreover, the CPU is evolving to the multi-core architecture providing additional flexible computing resources. Thus, we can combine both CPU and GPU on the same simulation rather than using the CPU solely as a manager. As from this

analysis the idea of the hybrid event scheduler emerged. The hybrid event scheduler is a pseudo-conservative scheduler that aims to execute events on the most adequate target between available executions resources. In particular, it switches grouped events to the GPU and isolated ones to the CPU. This approach maximizes the usage of heterogeneous computing resources on the shared memory. The gain from the proposed hybrid event scheduler proved to be significant and can reach up to 3x compared to traditional GPU scheduler.

The next intuitive step was to address the scalability further; we decide to distribute the simulation framework through a meta-computing infrastructure. Therefore, we incrementally design a three-tier software architecture donated as general purpose coordinator-master-worker (GP-CMW) model. It extends the *Master-Worker* model by introducing a top-level process which manages masters. In contrast with existing distributed simulation framework, the proposed architecture reduces significantly the management overhead through the network. The performance of a distributed simulation that relies on the GP-CMW architecture tends toward the maximal theoretical efficiency. The scalability of the system was validated on the largest European GPU-based supercomputer with 1024 LPs each of which simulates up to 1 million nodes. Accordingly, we had crossed a scalability boundary by combing parallel and distributed architecture into one global model that simplifies the management effort from the user point of view.

Finally, To validate the efficiency of the proposed concepts, we apply them to the popular network simulator NS-3 with the objective of a large scale deployment on the largest European hybrid super-computer(the TGCC Curie), which includes up to 288 GPUs and 1152 CPU. In particular, we customize the event scheduler of NS-3 and the event generation model in order to highlight the efficiency of the hybrid scheduling policy. This validation approach provides a proof of concept for the scalability and the robustness of the proposed model under production conditions. Further, we proved that maximizing the LP size until using the totality of a computing node is much more efficient than increasing the number of LPs within one computing node.

## 1.3 Thesis Structure

This thesis is structured around two parts. The first part includes background chapters that aim at providing a global view of the thesis context and investigation areas. In particular, the second chapter presents the network experimentation tools. The third chapter focus on the discrete event simulation and the fourth chapter highlights the hardware trends that lead the evolution of our work. The first part is concluded in the fifth chapter that presents related works which address large scale issues in network simulation or in DES. The second part of the thesis includes contributions chapters. The sixth chapter presents the Cunetsim framework that we use to explore the scalability horizons. The seventh chapter presents the hybrid event scheduler that aims at maximizing the hardware usage rate of het-

1.4. Publications 7

erogeneous hardware including CPU and GPU. The eighth chapter introduces the general purpose Coordinator-master-worker model that regroups the distributed and the parallel simulations on one optimized model. To conclude this part, the ninth chapter presents a study case of PADS methodology deployment through the ns-3 simulator. Finally, the thesis is concluded in the tenth chapter.

#### 1.4 Publications

- C1- B.R. Bilel, N. Navid, K. Raymond, B. Christian, OpenAirInterface large-scale wireless emulation platform and methodology, MSWIM'11, The 14th ACM International Conference on Modeling, Analysis and Simulation of Wireless and Mobile Systems, 31 october-4 Nov, Miami Beach, FL, USA.

- P1- B.R. Bilel, N. Navid, Cunetsim: a new simulation framework for large scale mobile networks, SIMUTOOLS'12, Proceedings of the 5th International ICST Conference on Simulation Tools and Techniques, 19-23 March, Desenzano, Italy.

- C2- B.R. Bilel, N. Navid, Cunetsim: A GPU based simulation testbed for large scale mobile networks, ICCIT'12, Communications and Information Technology (ICCIT), 2012 International Conference on, 19-21 June, Hammamet, Tunisia.

- C3- B.R. Bilel, N. Navid, M.S.M. Bouksiaa, *Hybrid cpu-gpu distributed framework* for large scale mobile networks simulation, <u>DSRT</u>'12, Distributed Simulation and Real Time Applications (DS-RT), 2012 IEEE/ACM 16th International Symposium on, 25-27 October, Dublin, Ireland.

- C4- B.R. Bilel, N. Navid, B. Christian, Coordinator-Master-Worker Model For Efficient Large Scale Network Simulation, SIMUTOOLS'13, Proceedings of the 6th International ICST Conference on Simulation Tools and Techniques, 5-7 March, Cannes, France.

- P2- B.R. Bilel, N. Navid, M.S.M. Bouksiaa, B. Christian, Scalability demonstration of a Large Scale GPU-based Network simulator, SIMUTOOLS'13, Proceedings of the 6th International ICST Conference on Simulation Tools and Techniques, 5-7 March, Cannes, France.

- C5- **B.R. Bilel**, N. Navid, M.S.M. Bouksiaa, B. Christian, *Hybrid scheduling for event-driven simulation over heterogeneous computers*, <u>PADS</u>'13, ACM SIGSIM Conference on Principles of Advanced Discrete Simulation (PADS), 19-22 May, Montreal, Canada.

- P3- B.R. Bilel, N. Navid, M.S.M. Bouksiaa, B. Christian, Events flow stability demonstration for a hybrid GPU-CPU scheduling in large scale network, PADS Colloquium'13, ACM SIGSIM Conference on Principles of Advanced Discrete Simulation -PhD Colloquium-(PADS), 19-22 May, Montreal, Canada.

J1- B.R. Bilel, N. Navid, B. Christian, General-Purpose Coordinator Master worker Model for Large Scale Distributed Simulation, submitted to <u>SMPT</u>, simulation modelling practice and theory Journal.

## 1.5 Project Deliverables

- D1- LOLA D4.1 Specification of PHY&MAC Adaptations for the Target Architectures.

- D2- LOLA D5.1 Testbeds Definition.

- D3- LOLA D5.2 Testbed 2: First report on Integration of WP3 Traffic Models and WP4 L2 Algorithms on Testbed 1.

- D4- CONECT D4.1 Testbed deployment and scenario specification.

- D5- CONECT D2.1 : STATE-OF-THE-ART ON PACKET LEVEL COOPERATION TECHNIQUES.

# Part I Background

## Network Experimentation

#### 2.1 Introduction

Since the introduction of the first interconnected machines, the usage of a digital communication has grown rapidly and is part of all human and economy domain. Nowadays, networks are presents everywhere, in each home, company, car, and may be with each person on the earth. This evolution impacts both network size and data amounts that increase continuously. Accordingly, investigating or modifying any components of that gigantic system requires a complex validation process. Thus, after an initial theoretical analysis, algorithms and protocols are generally evaluated experimentally. To cope with the broad range of requirements that recent network experiments need to fulfill, different evaluation techniques have been established. In this chapter, we survey the most common experiment tools, and classify them according to their implementation granularity and realism level.

## 2.2 Network Experimentation Tools

A network experimentation tool is a framework that allows the experimenter to realize a given experiment. Several peripheral services can be added to this definition such as pre-definition service that help the experimenter to define the experiment or archiving/analyzing tools that simplify the usage of the output.

Regarding the literature reviews, classification works consider two fundamental parameters: the implementation granularity and the realism level. Accordingly, we highlight five principal approaches to network experimentation: real world field trial, real world testbed, emulation testbed , simulation testbed and hybrid testbed.

#### 2.2.1 Real world Field Trial

Real world field experiment consists of deploying an experimental subject through real world infrastructure in order to study its behavior, efficiency or limits. In general, experimenters use real computers and network equipment, where they rapidly deploy their subjects of study (protocols, hardware, software). This approach was one of the first validation methods in network research and industry because its initialization requirements are limited and it provides realistic results. Nevertheless, given the number and complexity of the factors involved in the current networks, real world fields display three limitations:

- Precision: the real world experiment is based on a black-box approach where the system is evaluated as a whole. Thus, it is difficult to isolate a part of the system in order to analyze its impact, behavior or performance. Consequently, debugging and profiling activities are incompatible with such method.

- Reproducibility: a real world experiment is by definition, achieved in an open context where real traffic and real equipment cohabit with experimental one. As a consequence, it is hard to control environmental parameters that may influence the experiment. Thus, the reproducibility of such experiments is limited and remains an open issue.

- Scalability: the scalability of real world field is relatively limited due to three reasons:

- 1. The deployment cost

- 2. The management complexity

- 3. The monitoring issues.

#### 2.2.2 Real world Testbed

Real world testbed experiment consists on the deployment of the studied subject on a dedicated experimental infrastructure that imitates real world conditions [128]. By agreement, the testbed can be isolated or integrated onto a real and production context [71]. In contrast with experimentation, testbed increases the control by providing formal experimentation methodologies. Nevertheless, the reproducibility and the scalability of such an experiment remain challenging. In fact, the complexity of controlling all relevant parameters in a field test is precisely why so many users often turn to setting up testbeds where they can measure or control a large number of environmental parameters of interest and easily reproduce the same experiment over and over again. There are three principal tendencies that guide tested investigation: (1) Increasing the realism level (2) increasing the control and (3) increasing the scalability.

- 1. Increasing the realism level implies that the testbed grows as close as possible to target networks by incorporating the totality of involved components that may influence the experimentation [34, 116]. However, experimentation control and scalability remain limited due to inherent cost of such solutions.

- 2. Increasing the experimentation control implies the specification of environmental characteristics such as the transmission medium, medium access and usage, traffic patterns, power consumption, etc. That feature is particularly important for wireless network understanding that requires a full control of the medium[11, 115]. Indeed, the scalability of such approach remains a restriction.

3. Increasing the scalability implies the usage of additional resources. However, according to the high cost of such testbed, the leading approach is to federate foreign testbeds into a large infrastructure that can be shared between involved teams [112, 40]. In fact, federated real world testbeds such as [70] increases the tradeoff between the experimentation reproducibility and its realism level compared to field experimentation.

### 2.2.3 Emulation Testbed

In the literature reviews, researchers talk about emulation when a sub part of the studied system is partially modeled using a mathematic or software representation while the other parts of the system are real. Another work considers an experiment as an emulation when the environment of the studied subject becomes fully controlled. Regarding network emulation frameworks, literature reviews highlight the control of the experiment. The objective is to be able to configure all the parameters of an experiment execution. Depending on the framework goal, modeled components may be either the medium, the hardware or software. Emulating the network medium is typically used in wireless context where the channel specification and modeling are under improvement [50, 29, 63].

In particular, FPGA based framework such as [66, 19] provide a full control on the medium environment, propagation, collision and dispersion. Using FPGAs as development context is also used in emulation context to study the radio medium [18]. Modeling the hardware is commonly used in network emulator that addresses protocols development such as CORE [6]. The main goal of such approach is to execute real protocol implementation that can be used in testbeds and field experimentations. Modeling the software is mainly used when the protocol stack and/or a part of the software is not the subject of study such that its real implementation did not improve the experimentation but slows the execution. A good example of software emulation is trace based network emulation [93]. Several works that can be classified as an emulation framework or approach, are positioned between [24, 59, 52, 79, 89]. Indeed, the scalability of emulation frameworks remains restricted due to the imposing cost per emulated node whatever the used emulation approach.

#### 2.2.4 Simulation Testbed

In the literature reviews, researchers talk about simulation when the experiment consists of using models to represent the studied system. In fact, each component of the simulated system is represented using a model. External elements such as the environment, foreign systems are also represented using models. Models can be defined using more or less complex algorithms [22, 68].

The challenging part of a network simulation is the representative implementation of the real system in a model [65]. To cope with the original system's complexity, the simulation model requires abstractions and simplifications, which in best-case do not produce an impact on the definitive result. Moreover, the run-time of the

simulation depends on the degree of detail in the implementation [148]. Hence, the network simulation is an appropriate tool to evaluate specific effects, but due to the modeling approach, they may not capture correctly the entire system behavior. Thus, when interpreting the results of a given simulation, it is perpetually required to take into account these limitations.

There are two main categories of simulations: continuous [25] and discrete [130] simulations. In continuous simulations, the model is represented as a set of differential equations. They are often used for researching physical phenomena, such as aerodynamics or hydraulics, which require numerical solutions. On the other side, discrete simulations implement the model as a sequence of events at discrete time points. In computer networking, the DES is an important instrument for protocol development and evaluation.

The major advantage of network simulation is unquestionably its scalability. However, its realism level is directly related to the correctness of the used models. Recent network simulators such as omnet++[137] and NS-3 [60] provide a good trade-off between models simplicity and quality. Production network simulators such as opnet [56] pushes the balance further by incorporating the real world code such as the IP stack implementation, until grazing the definition of network emulator rather that of simulator. In particular we highlight the ability of several simulation testbeds such as NS-3 to execute external software source code that can be exactly which will be used on real implementation. The feature is denoted as direct code execution [75].

#### 2.2.5 Hybrid Testbed

Each of the previous network experimentation tools presents strengths and weaknesses in terms of scalability and realism level. These features seem conflicting since

increasing the realism requires complex model or real implementation while increasing the scalability requires a reduced complexity per simulated element. However,

the need of realistic and large scale experiment rises proportionally to the growth of

networks scale. Moreover, experimentation that involves heterogeneous components

such as wireless and wired nodes gain momentum and credibility. Accordingly, the

idea of combining the usage of different experimentation tools on the same framework appears the most adequate to cope with both requirements. In the literature

reviews, we distinguish two main categories of hybrid experimentation tools: the

federating tools of the same class and the federating different experimentation class

tools.

Federated experimentation frameworks have a directed line that defines a global goal such as considering very large Internet experimentation or achieving a very large scale packet level simulation [136, 87]. For example, the Planetlab project federates different type of experimental testbeds [113, 51]. In this context, we note that the HLA protocol is a standardization that allows the federation of heterogeneous simulators[35]. While that category of hybrid experimentation targets to maximize the scalability of a given tool/framework by increasing its distribution level, it is still

limited by the inherent characteristics of the considered tool (testbed, emulation or simulation).

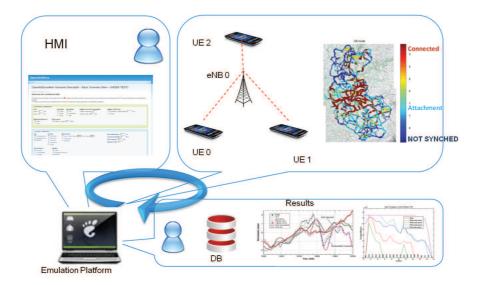

In contrast, federating different experimentation tools provides a sophisticated and flexible combination between local realistic and global large scale experimentation [53]. For example, when studying the integration of 4G equipment on the Internet, a typical hybrid experimentation will emulate 4G nodes using a full protocols stack implementation on radio devices using OpenAirInterface, emulates Wi-Fi and 3G nodes that share the same medium using CORE and simulates the network backbone using NS3. In that sense, the NEPI project [77] is one of the federating framework that aims to provide a global methodology and interface to combine a variety of network experimentation tools. To face the increasing complexity of such experimentation, federated frameworks must synchronize the global time of the experiment and primary components definition. Generally, the referential time of hybrid network experimentation is a real time while the primary components is always the node.

Finally, it has to be mentioned that tendencies of sophisticated experimentation tools such as NS3 and CORE is to provide dual or triple capabilities including emulation, simulation and visualization, which appears as an emerging feature of such tools [149].

#### 2.3 Network Experimentation Aspects

In previous sections, we classify five types of network experimentation tools, based on their realism level. Realism level and scalability can be used to classify experimentation tools. Table 2.1 summarizes a realism-based classification approach that focus on most common examples of each category. Nevertheless, the realism level remains one aspect of the experiment. A synthesis of the literature reviews highlights five major axes that define a given experimentation tool.

- 1. The architecture: the tool architecture summarizes the concepts that define the achievement of the tool. It includes the experiment base which defines how the experiment is described in the tool (components definition, topology, traffic description). The second aspect of the architecture is the component base. In fact, each component can be defined using realistic/simplified definition. Finally, the simplification aspect considers the user point of view. It is relative to the simplicity of the usage of the tool and not to the quality of the experiment.

- 2. Scientific experiment features: in order to be considered as a scientific experiment, the experimentation tool must address three features: the reproducibility, the revisability and the traffic quality. The reproducibility is the ability to reproduce the same experiment, expects to produce the same output and observes the same behavior. The revisability concerns the capacity of the experimenter to explore the studied system during the experimentation in order

to extract meaningful results. The granularity of the exploration is important in the revisability of a given experiment (including dynamic debug and profiling). The traffic quality is an experimentation feature that may define the scientific quality. Thus, the ability of a given testbed to play real traces or to generate realistic traffic is an important feature.

- 3. The effectiveness: the effectiveness of an experimentation tool defines its capacity to achieve the experiment rapidly without interference between the experiment and the experiment management. The effectiveness of a given tool also depends of its scalability, defined as its capacity to scale in terms of size of the simulated scenario (number of element, duration of the experiment, traffic load, and the scope of the space). In table 2.1, we characterize the effectiveness aspect by three parameters: the scalability, the overhead and the efficiency. The first defines the ability to scale, the second is the tradeoff between the simulation and the management processing. Finally, the efficiency of a given experimentation tool reflects its processing runtime.

- 4. The cost: the economic aspect is an important factor that determines the notoriety and the usage of a given tool. This aspect includes three characteristics: the initialization cost, the operating cost and the maintenance cost. The first defines the cost of the experiment initialization including hardware and software. The second defines the cost of the usage during an experiment (i.e. the power). The third aspect is relative to usage in the long term and describes the evolution capacity of the tool.

- 5. The usability: In contrast with previous aspects, the usability is relative to the usage experience. It includes the methodology of the experiment (that also impact the scientific aspect), the simplicity of the deployment which is very critical when addressing distributed simulation and the experiment setup that implements the experimentation methodology.

In table 2.1, we highlight the correspondence between the five classes of tools and the experimentation aspects.

Table 2.1: Characteristics of exciting experimentation tools

| Characteristic      | Filed test  | Testbed  | Emulation   | Simulation  | Hybrid     |

|---------------------|-------------|----------|-------------|-------------|------------|

| Experiment bases    | ++ Real     | + Real   | -Real/model | Model       | +/-Real    |

| Components bases    | ++Real      | ++Real   | +Real       | Algorithm   | Variable   |

| Simplifications     | absent      | Possible | Definable   | Abstraction | Variable   |

| Reproducibility     | -Insight    | Insight  | +/-Accurate | ++Accurate  | +Accurate  |

| Revisability        | +/-Insight  | +Insight | +Accurate   | + In sight  | ++Accurate |

| Traffic             | ++Real      | ++Real   | +/-Real     | +/-Real     | +Real      |

| Scalability         |             | -        | ++          | +/-         |            |

| Overhead            |             |          | -           | +/-         | +/-        |

| Efficiency          |             |          | _           | ++          | +/-        |

| Initialization Cost | (expensive) |          | +/-         | ++          | +          |

| Operating Cost      |             |          |             | ++          | +/-        |

| Maintenance Cost    |             |          | _           | ++          | +          |

| Methodology         |             | ++       | ++          | +++         | +++        |

| Deployment          | ++          | +        | +/-         |             | +/-        |

| Setup               |             | -        | +/-         | ++          | +          |

## Discrete Event Simulation

#### 3.1 Introduction

Discrete event simulation (DES) is the process of modeling the operation of a given system as a discrete sequence of events in time. Each event occurs at a given time-point of the simulation time axis and marks a change of state in the system [120]. Discrete-event simulation is largely used as a major software design approach in scientific simulation. The reason behind the success of discrete-event based simulation in computer networking is that the simulation paradigm fits very well to the considered systems. In fact, DES provides a simple yet flexible way to achieve complex experiments and to study the behavior of the systems under different conditions. In the remainder of this chapter, we provide a brief introduction to discrete-event simulation in Section 3.2 and we summarize the principals of parallel discrete event simulation (PDES) in section 3.2. In particular, we highlight issues and principles of PDES.

#### 3.2 Discrete-Event Simulation

In this section, we first introduce the basic terminology used in literature and describe their relationship. Second, we present the principal of DES and we survey the concept of time driven event scheduling. For an in-depth introduction the reader is referred to [80, 142].

#### 3.2.1 Terminology and Components

There are three notions shared among the majority of DES: the entity, the system and the discrete system.

- An *entity* is an abstraction of a particular subject of interest. An entity is described by its attributes, e.g., an entity packet could have attributes length, source and destination addresses. The term *object* is often used as synonymous.

- A system is defined by a set of entities and their relationship. The set of entities and their relationships fulfill a certain purpose, i.e., the system has a certain goal that it tries to achieve.

- A discrete system is a system whose state, defined by the state of all entities of the system, changes only at discrete points in time. The change of the state

is triggered by the occurrence of an event. What an event exactly is, depends mainly on the system and on the goal of the study., e.g. sending and receiving a packet, moving in the space or updating the battery state.

Usually, the system of interest is quite complex. In order to evaluate its performance by means of computer simulation a **model** is built. The model is a *software representation* of the system, hence it consists of selected entities of the system of interest and selected relationships between the entities. By agreement, the model is a system itself. In computer simulations, it is always the model that is considered, mainly to reduce the involved complexity and the associated cost and effort.

#### 3.2.2 The Principle

The idea of a discrete-event simulator is to jump from one event to the next, whereby the occurrence of an event may trigger changes in the system state as well as the generation of future events. The events are recorded as event descriptor (also known as the event notice) in the future event list (FEL), which is an appropriate data structure offen a time ordered structure to manage all the events in the discrete-event simulation. An event descriptor is composed of at least two information (time, type) where time specifies the time when the event will occur, and types provide the kind of an event. The future event list should implement efficient functions to insert, to find, and to remove event descriptor, which are placed in the future event list. With every discrete event time ti a snapshot of the system is created (stored in memory) that contains all required data to progress the simulation. In general, all discrete-event simulators share the following components:

- System state: a set of variables that describe the state of the system.

- Clock: the clock gives the current time during the simulation.

- Future event list: a data structure appropriate to manage the events

- Statistical counters: a set of variables that contain statistical information about the performance of the system.

- *Initialization routine*: a routine that initializes the simulation model and sets the clock to 0.

- *Timing routine*: a routine that retrieves the next event from the future event list and advances the clock to the occurrence time of the event.

- Event routine: a routine that is called when a particular event occurs during the simulation.

#### 3.3 Parallel Discrete Event Simulation

Ever since discrete event simulation has been adopted by a large research community, simulation developers have attempted to draw benefits from executing a simulation

on multiple processing units in parallel. Hence, a wide range of research has been conducted on Parallel Discrete Event Simulation (PDES). In the remainder of this section, we survey the challenges of parallel DES, common architecture and major synchronizations algorithms.

#### 3.3.1 Discrete Event Simulation Limits

Technological systems are becoming increasingly complex with the emergence of new technologies that combine wide interconnectivity with composite structures and architectures. In general, two orthogonal trends in terms of complexity can be identified: (i) an increase in structural complexity and (ii) an increase in computational complexity. Both impose high demands on the simulation architecture and the hardware executing the simulations.

We denote the size of a simulated system as an indicator of the structural complexity of a simulation model. In what concerns network research, growing systems like peer-to-peer networks and ubiquitous mobile networks, induced an enormous increase in the size of communication systems. Such large systems typically add complex be-havioral characteristics which cannot be observed in networks of smaller size (e.g., testbeds) or captured by analytical models. Thus, in order to study those characteristics, simulation models a large numbers of simulated network nodes. Since every network node is represented in memory and triggers events in the simulation model, memory consumption and computation time increase significantly. Even if the investigated network is relatively small, computational complexity becomes an important factor if the simulation model is highly detailed and involves extensive calculations [47]. In particular wireless networks which make use of advanced radio technologies such as OFDM(A) [72] and Turbo Codes [14] fall in this category. Sophisticated radio propagation models, interference modeling, and signal coding models increases the overall complexity.

Simulation frameworks aim to compensate these issues by enabling simulations to be executed in parallel on multiple processing units. By combining memory and computation resources of multiple processing units, simulation time can be reduced at the cost of higher memory requirements and management overhead. Although this approach is known for more than two decades [42, 44, 110], recent technological advances considerably reduce the hardware cost of parallel computing infrastructure. Thus making such hardware available to a large research community which hand over the spotlight on discipline [86, 127].

#### 3.3.2 Principles of Parallel Discrete Event Simulation

The approach taken by PDES is to divide a simulation model in multiple instances which are executed on independent processing units in parallel. The central challenge of PDES is thereby to maintain the correctness of the simulation. Any simulation framework exhibits three central data structures: i) state variables of the simulation model, ii) a timestamped list of events, and iii) a global clock. During

a simulation run, the scheduler continuously removes the event with the smallest timestamp (emin) from the future event list(FEL) and executes the associated handler function. T denotes the timestamp function which assigns a time value to each event and E is the set of all events in the event list. While the handler function is running, events may be added to or removed from the event list. Choosing emin is crucial as otherwise the handler function of an event ex with T(emin) < T(ex) could change state variables which are later accessed when emin is handled. In this case the future (ex) would have changed the past (emin) which we call a causal violation. Thus, we formulate the central challenge of PDES as follows: Given two events e1 and e2, decide if both events do not interfere, hence allowing a concurrent execution, or not, hence requiring a sequential execution. Parallel simulation frameworks employ a wide variety of synchronization algorithms to decide this question. The next section presents a selection of fundamental algorithms and discusses their properties.

#### 3.3.3 Parallel Simulation Model and Algorithms

A parallel simulation model is composed of a finite number of partitions which are created in accordance to a specific partitioning scheme. Three exemplary partitioning schemes are i) space parallel partitioning scheme, ii) channel parallel partitioning, and iii) time parallel partitioning. The space parallel partitioning scheme divides the simulation model along the connections between simulated nodes. Hence, the resulting partitions constitute clusters of nodes. The channel parallel partitioning scheme bases on the assumption that transmissions that utilize different (radio) channels and/or mediums do not interfere with each other. Thus, events on non-interfering nodes are considered independent. As a result, the simulation model is decomposed in groups of non-interfering nodes. However, channel parallel partitioning is not generally applicable to every simulation model, thus leaving it for specialized simulation scenarios. Finally, time parallel partitioning schemes subdivide the simulation time of a simulation run in time-intervals of equal size. The simulation of each interval is considered independent from the others under the premise that the state of the simulation model is known at the beginning of each interval. However, the state of a network simulation usually comprises a significant complexity and is not known in advance.

#### 3.3.3.1 Local Causality Constraint

A discrete-event simulation, consisting of logical processes that interact exclusively by exchanging time stamped messages obey the local causality constraint if and only if each LP processes events in non-decreasing time stamp order. In practice, the number of LPs (i.e., partitions) is equal to the number of CPUs provided by the simulation hardware. Consequently LPs directly map to physical processes. Furthermore, the timestamped and message-based communication scheme constitutes two important properties. First, they allow a transparent execution of LPs

either locally on a multi-CPU computer or distributed on a cluster of independent computers. Second, and more importantly, timestamps provide the fundamental information used by synchronization algorithms to decide which events to execute and to detect causal violations. In the literature, there are two classes of synchronization algorithms: conservative and optimistic algorithms. While conservative algorithms aim to strictly avoid any causal violation at the time of the simulation run, optimistic algorithms allow causal violations to occur, but provide means for recovering.

#### 3.3.3.2 Conservative Synchronization Algorithms

Conservative synchronization algorithms strive to strictly avoid causal violations during a simulation run. Hence, their central task is to determine the set of events which are safe for execution. In order to decide on this question, conservative algorithms rely on a set of simulation properties [43]. The Lookahead of a LP is the difference between the current simulation time and the timestamp of the earliest event it will cause at any other LP. The Earliest Input Time (EIT) denotes the smallest timestamp of all messages that will arrive at a given LP via any channel in the future. Accordingly, the Earliest Output Time (EOT) denotes the smallest timestamp of all messages that a given LP will send in the future to any other LP. Based on these definitions, a LP can safely execute all events which have a smaller timestamp than its current EIT since it is guaranteed that no messages with a smaller timestamp will arrive later.

#### Null-Message Algorithm

The simple approach presented above does not solve the synchronization problem entirely as it can cause the simulation to deadlock. This problem is addressed by the Null-Message Algorithm (NMA) which was first introduced by Misra and Chandra [317]. The algorithm uses nullmessages, i.e., messages which do not contain simulation model related information, to continuously increase the EIT of all neighboring LPs. For this purpose, null-messages carry the LP's current EOT timestamp, which is determined by adding the lookahead to its current local time. Hence, nullmessages can be considered as a promise of an LP not to send any message with a smaller timestamp than EOT in the future. Upon receiving a null-message, each LP updates its EIT to a potentially greater value. If the updated EIT has advanced beyond events in the event queue, those are now considered safe for execution. This algorithm guarantees to prevent deadlocks if the simulation model does not contain zero-lookahead cycles. However, this algorithm implies a significant management overhead. In fact, each synchronization algorithm imposes two types of overhead: messaging overhead which is caused by sending (simulation model) messages to LPs on remote machines and the actual synchronization overhead which is caused by blocking and additional (synchronization) messages that are only used by the algorithm (e.g., null-messages). While messaging overhead is a property of the simulation model, the synchronization overhead is a property of a particular algorithm.

#### 3.3.3.3 Optimistic Synchronization Algorithms

In contrast to conservative algorithms, optimistic synchronization algorithms allow LPs to simply execute all events (in time stamp order) as they come in, but without ensuring that causal violations will not occur. This probably counter-intuitive behavior is motivated by the observation that conservative algorithms sometimes block LPs unnecessarily: Often not enough information is available to mark a certain event safe, although it actually is. Hence, the simulation performance is reduced significantly. Thus, optimistic algorithms assume that an event will not cause a causal violation. This approach has two primary advantages: First, it allows exploiting a higher degree of parallelism of a simulation model. If a simulation model contains two mostly independent partitions, which interact only seldom, only infrequent synchronization is actually needed. Second, the overall performance of the parallel simulation depends less on the lookahead. Thus making it attractive to models with small lookahead such as in wireless networks. Clearly, the downside is that a causal violation leaves the simulation in an incorrect state. As a result, optimistic algorithms provide recovery mechanisms: during a simulation run, the PDES engine continuously stores the simulation state. Upon a causal violation, the simulation is rolled-back to the last state known to be correct.

# Hardware Trends

#### 4.1 Introduction

This chapter aims to highlight the hardware evolution that has accrued in the last decades. In particular, we survey parallelism and optimization features that concern CPUs and the emergence of dedicated co-processor that democratizes the large scale parallel computing. In this context, we present the GPU as a massively multicore chip and the computing accelerator as a dedicated multi-core device. In the remainder of this chapter, we first survey CPU architectures and features. Secondly, we present an overview of current GPU state of the art. Thirdly, we summarize the concept of multi-core accelerator that was inaugurated by the the Xeon Phi processor. Finally, we conclude the chapter by a survey of parallel programming APIs for such hardware.

### 4.2 Evolution of Computing Chips

#### 4.2.1 CPU: Historical Evolution and Trends

Historically, the CPU was designed to achieve all computing tasks requested by the OS. Since the introduction of the 8086 micro-processor and the democratization of the PC, the CPU improvements tell two roads: increasing the CPU frequency and extending the instructions set.

Nevertheless, increasing the frequency of the computing chip induces a phenomenal increase in thermal settings and power consumption. Accordingly, in the beginning of the previous decade, CPU manufactures recognize that increasing the frequency cannot be the future development approach. The common trend is to fit multiple CPU cores within the same chip. First attempts was really the juxtaposing of two independent CPUs which in turn limits any advanced collaboration and saturates the internal bus. Progressively, CPU architecture evolves and becomes composed of several computing cores and on-chip memory stages. The communication between different cores is progressively optimized, and the management of the distributed memory becomes mature. However, the concept of multi-core CPU relies on the independence of each core such that each of them is able to execute any task. Consequently, all cores are built following the same complex architecture which in turn reduces the ability to maximize the number of integrated cores.

On the other hand, the enhancement of the instructions set remains relevant. In particular, the introduction of vector instructions was pertinent for scientific and

multimedia usages. These instructions allow the processing of several words in one clock cycle. In the current state of the art, it is possible to process up to 4 words (256 bits) in parallel by each core using the AVX instruction set. AVX2 promises the processing of 8 words in the next CPU generation.

In parallel, CPU manufacturers continue to improve CPU architecture to provide more and more features. The trend is that, between two consecutive generations, the gain is between 10% and 20%. An additional relevant feature is the simultaneous multithreading (SMT), denoted as the hyper-threading technology by Intel and partially implemented by AMD. The concept relies on an advanced instruction scheduling that allows each hardware core to emulate the execution of two (or more) threads. Each of which is assumed to be executed on one virtual core. Depending on the optimization of the software, the relative gain could vary (between 10% and 25%).

#### 4.2.2 GPU: Historical Evolution and Trends