## Analyse Expérimentale et Numérique des Contraintes Thermomécaniques Induites lors des Procédés Émergents de Fabrication de Puces Électroniques au moyen des Capteurs Embarqués

Komi Atchou Ewuame

## ▶ To cite this version:

Komi Atchou Ewuame. Analyse Expérimentale et Numérique des Contraintes Thermomécaniques Induites lors des Procédés Émergents de Fabrication de Puces Électroniques au moyen des Capteurs Embarqués. Matériaux. Université Paris sciences et lettres, 2016. Français. NNT: 2016PSLEM006. tel-01405347

## HAL Id: tel-01405347 https://pastel.hal.science/tel-01405347

Submitted on 29 Nov 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THESE DE DOCTORAT

de l'Université de recherche Paris Sciences et Lettres PSL Research University

Préparée à

**MINES ParisTech**

# ANALYSE EXPERIMENTALE ET NUMERIQUE DES CONTRAINTES THERMOMECANIQUES INDUITES LORS DES PROCEDES EMERGENTS DE FABRICATION DE PUCES ELECTRONIQUES AU MOYEN DES CAPTEURS EMBARQUES

Ecole doctorale n° 364

SCIENCES FONDAMENTALES ET APPLIQUEES

Spécialité : Science et Genie des Materiaux

Soutenue par :

Komi Atchou EWUAME

Le 14 Juin 2016

Dirigée par :

**Karim INAL**

Pierre-Olivier BOUCHARD

# COMPOSITION DU JURY :

Prof. Roland FORTUNIER Ecole Nationale d'Ingénieurs de Saint-Etienne Président de jury

Prof. Rafael ESTEVEZ Université de Grenoble SIMAP-INP Rapporteur 1

Prof. Patrick PONS CNRS LAAS Rapporteur 2

Ing. Pascal CHAUSSE CEA - Leti Membre invité

Prof. Karim INAL Université de recherche PSL CEMEF MINES ParisTech Directeur de Thèse

Prof. Pierre-Olivier BOUCHARD Université de recherche PSL CEMEF MINES ParisTech Co-directeur

Dr. Vincent FIORI STMicroelectronics Encadrant Entreprise

## REMERCIEMENTS

« AKPE NA MI », ce qui veut dire « Merci à vous » en mina (un des dialectes togolais ②).

Comme pour la plupart des travaux, le chemin n'a jamais été droit ni simple, mais la finition a été une belle réussite.

J'aimerais adresser mes premiers remerciements à Vincent FIORI, qui m'a assisté durant ces trois années de thèse. Ses compétences en microélectronique m'ont fortement aidé à réaliser ce travail.

J'exprime tous mes remerciements à Karim INAL qui a assuré la direction scientifique de ce travail. Sa rigueur scientifique et ses expériences en expérimentation m'ont beaucoup appris.

Mes remerciements vont également à Pierre-Olivier BOUCHARD. Son expertise en simulation éléments finis a été pour moi un élément important dans la réussite de ce travail.

Merci à Sébastien GALLOIS-GARREIGNOT, pour sa disponibilité, pour son aide tout au long de la thèse.

Je remercie l'ensemble des membres de jury pour leurs intérêts pour ce travail. Merci à Roland FORTUNIER d'avoir accepté de présider le jury. Merci à Rafael ESTEVEZ et à Patrick PONS d'avoir accepté d'être les rapporteurs de ce travail et merci à Pascal CHAUSSE.

J'adresse toute ma gratitude à tous mes ami(e)s et collègues qui m'ont aidé de loin ou de près dans la réalisation de ce travail. Je remercie toutes les personnes formidables que j'ai rencontrées à STMicroelectronics de Crolles et à MINES ParisTech de Sophia Antipolis. Merci pour vos supports et vos encouragements.

Mes mots de remerciements vont aux membres de la famille CREPPY pour leurs soutiens. Ils ont été pour moi, un père, une mère, des frères et sœur durant mon séjour à Grenoble. Ils m'ont gracieusement porté dans leurs cœurs et m'ont encouragé à aller de l'avant.

Loin des yeux mais près du cœur, n'ayant pas pu assister à la soutenance malgré son désir, ma petite chérie Christel a su me donner les mots qu'il faut pour me porter haut. Merci pour ses encouragements et ses soutiens moraux.

Simple mais forte, ma plus vive gratitude va à ma famille. Je remercie mes frères Komivi Jean Claude, Edoh Rodolphe et Mawuena Ezéchiel pour leurs encouragements. Je remercie également mon père Komlavi Benjamin pour son soutien et tout son apport. Mes remerciements vont particulièrement à ma mère Akofa Sylvie qui demeure un trésor précieux pour moi. Je t'envoie un océan de câlins pour une vie entière de bonheur parce que tu le mérites bien.

# **TABLES DES MATIERES**

| REMERCIEMENTS                                                    | V    |

|------------------------------------------------------------------|------|

| TABLES DES MATIERES                                              | vii  |

| LISTE DES FIGURES                                                | xi   |

| LISTE DES TABLEAUX                                               | xv   |

| GLOSSAIRE                                                        | xvii |

| INTRODUCTION GENERALE                                            | 1    |

| I. Contexte industriel                                           | 1    |

| II. Approche adoptée                                             | 2    |

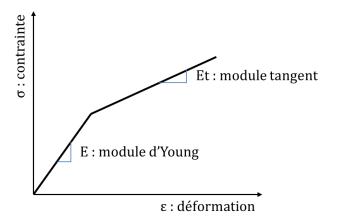

| CHAPITRE I : ETAT DE L'ART                                       | 5    |

| I. Circuit intégré                                               | 5    |

| 1. Description                                                   | 5    |

| 2. Les lois de Moore                                             | 6    |

| II. Procédés de fabrication et quelques problèmes associés       | 7    |

| 1. Front-End                                                     | 7    |

| 2. Back-End                                                      | 10   |

| III. Contraintes et défaillances induites lors de la fabrication | 13   |

| 1. Contraintes résiduelles                                       | 13   |

| 2. Défaillances dans les interconnexions                         | 15   |

| 3. Strain engineering                                            | 16   |

| IV. Méthodes d'évaluation des contraintes                        | 18   |

| 1. Démarches expérimentales                                      | 18   |

| 2. Démarches numériques                                          | 26   |

| V. Positionnement de la thèse                                    | 30   |

| SYNTHESE I                                                       | 31   |

| ABSTRACT I                                                       | 32   |

| CHAPITRE II : CONCEPTION DU CAPTEUR DE CONTRAINTE IN-SITU        | 33   |

| I. Structure du silicium                                         | 33   |

| 1. Silicium monocristallin                                       | 33   |

| 2. Silicium amorphe                                              | 34   |

| 3. Silicium polycristallin                                       | 35   |

| II. La physique de la piézorésistivité dans les semi-conducteurs | 36   |

| III. Critères de qualité                                         | 37   |

| IV Canteur de contrainte et relations caractéristiques           | 38   |

| 1.     | Description                                                                     | 38           |

|--------|---------------------------------------------------------------------------------|--------------|

| 2.     | Relations caractéristiques                                                      | 39           |

| SYNTHI | ESE II                                                                          | 48           |

| ABSTRA | ACT II                                                                          | 49           |

| CHAPIT | RE III : CALIBRATION DES CAPTEURS                                               | 51           |

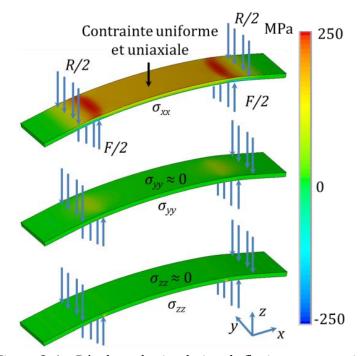

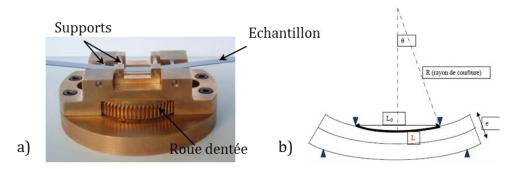

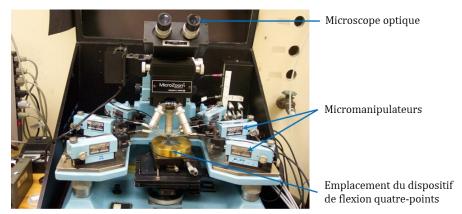

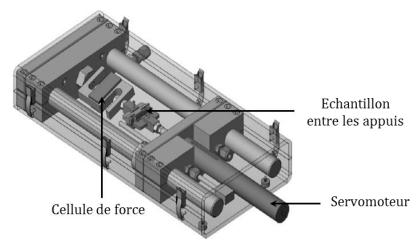

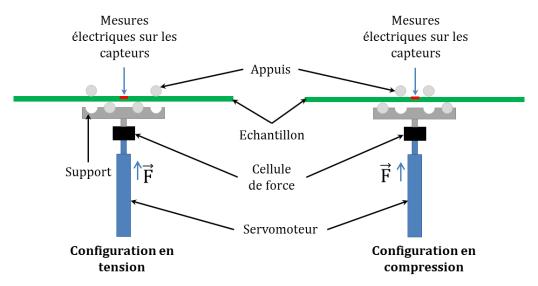

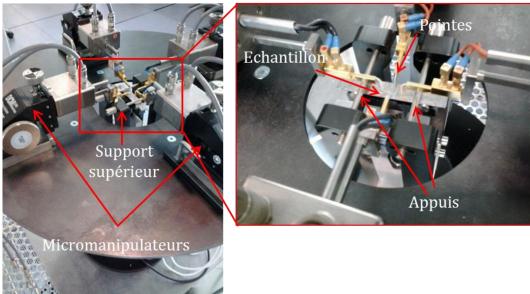

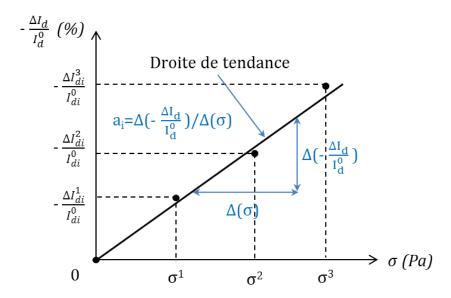

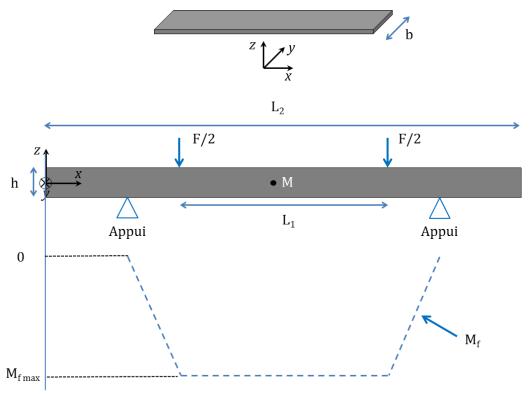

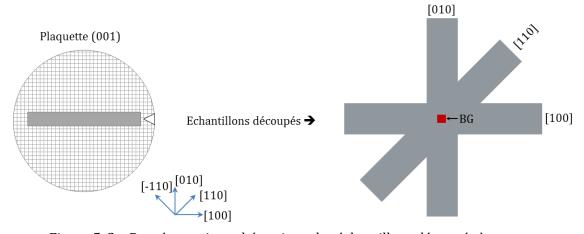

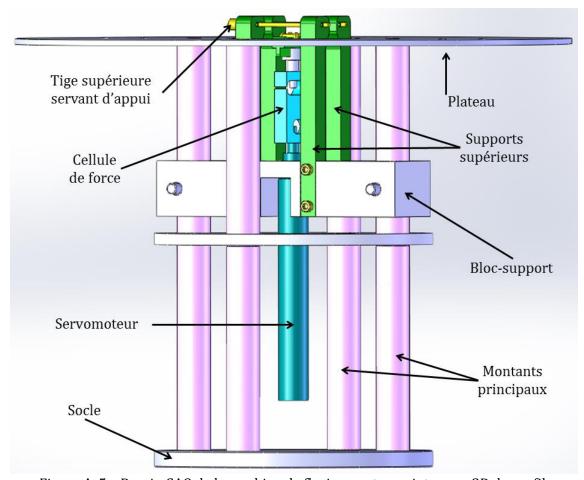

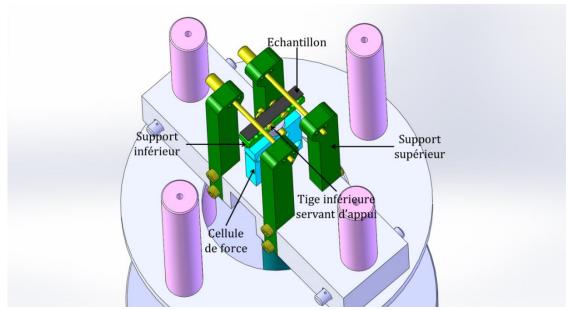

| I. (   | Conception d'une machine de flexion quatre-points                               | 51           |

| 1.     | Méthodes de calibration                                                         | 51           |

| 2.     | Conception d'une machine de flexion quatre-points dédiée à la calibration of 53 | des capteurs |

| 3.     | Mode opératoire                                                                 | 55           |

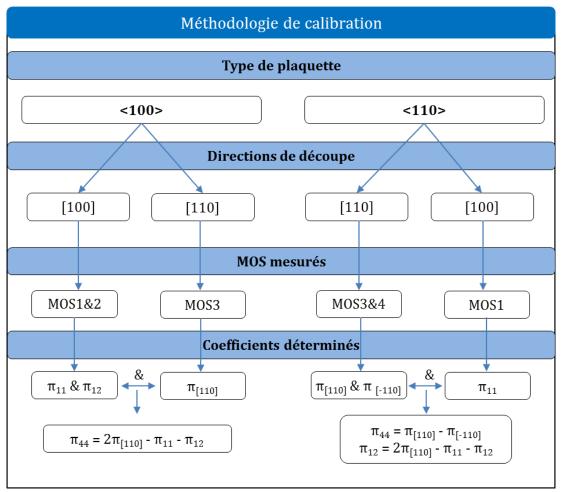

| II. I  | Méthodologie de calibration                                                     | 56           |

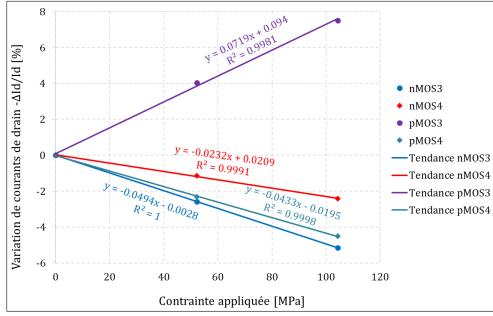

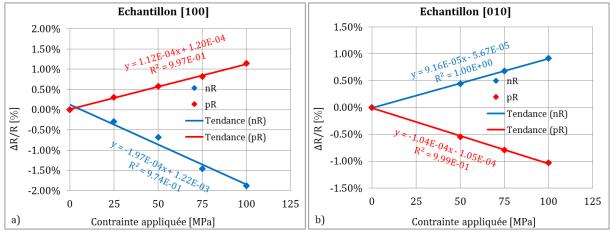

| 1.     | Plaquette <100> pour n&pMOS                                                     |              |

| 2.     | Plaquette <110> pour n&pMOS                                                     | 58           |

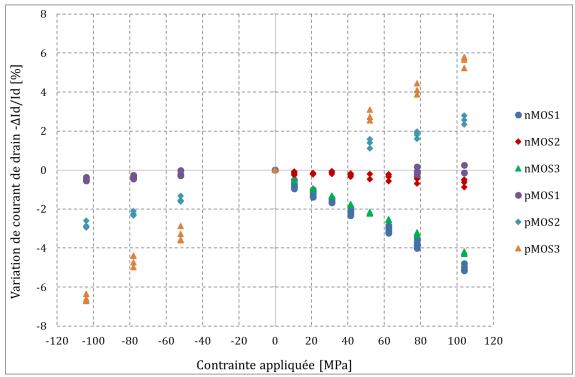

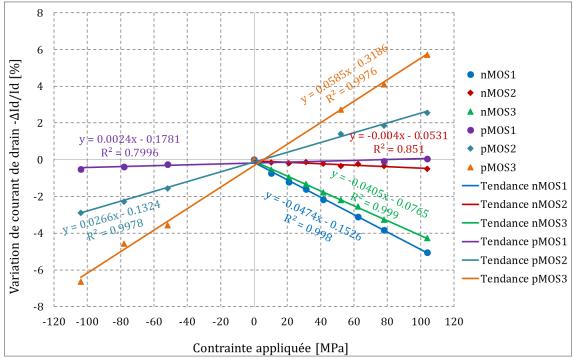

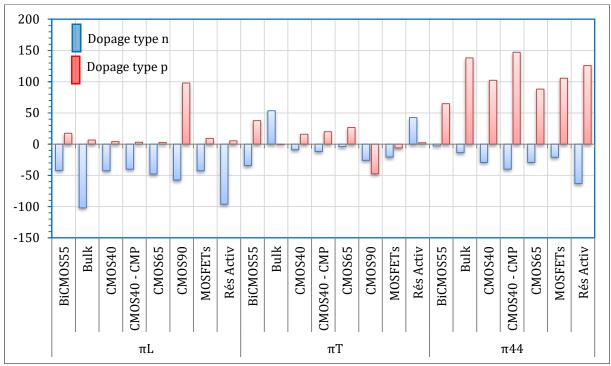

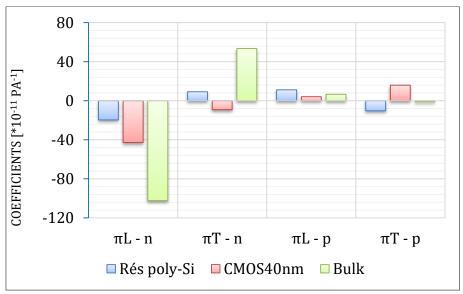

| III.   | Détermination des coefficients piézorésistifs : applications                    | 59           |

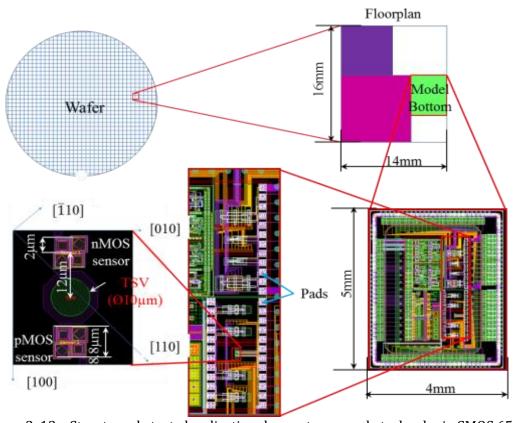

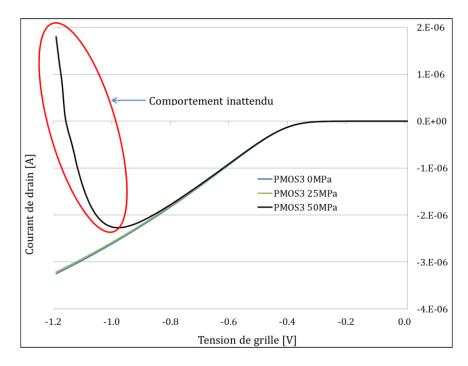

| 1.     | Technologie CMOS 65nm                                                           | 63           |

| 2.     | Technologie BiCMOS 55nm                                                         | 67           |

| 3.     | Technologie CMOS 40nm                                                           | 70           |

| 4.     | Autres tests                                                                    | 72           |

| 5.     | Bilan                                                                           | 74           |

| SYNTHI | ESE III                                                                         | 78           |

| ABSTRA | ACT III                                                                         | 79           |

| CHAPIT | RE IV : EVALUATION DES CONTRAINTES                                              | 81           |

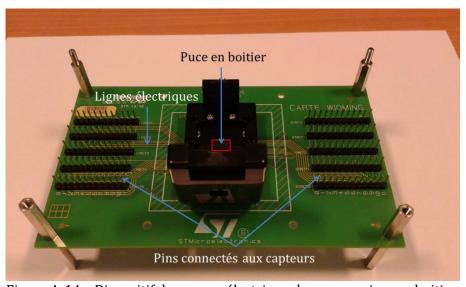

| I. S   | Stratégie de test et études de variabilité                                      | 81           |

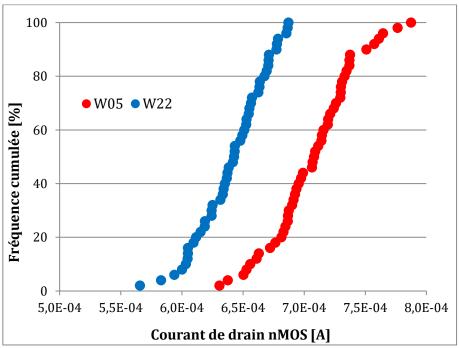

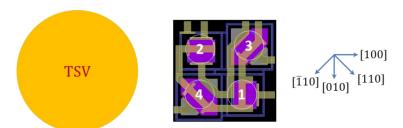

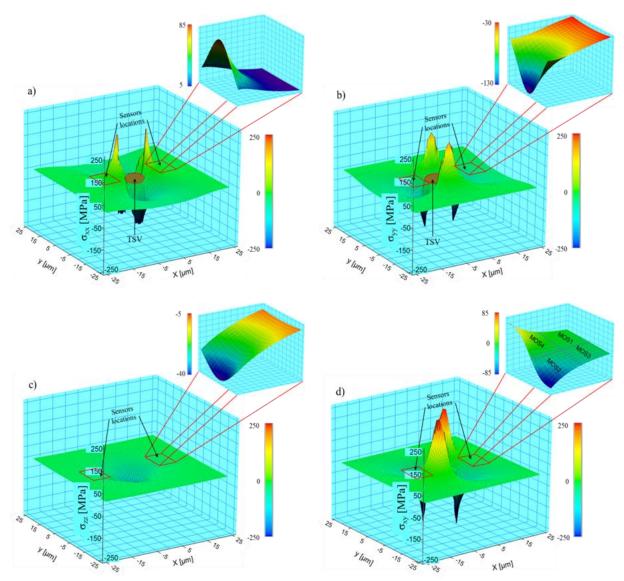

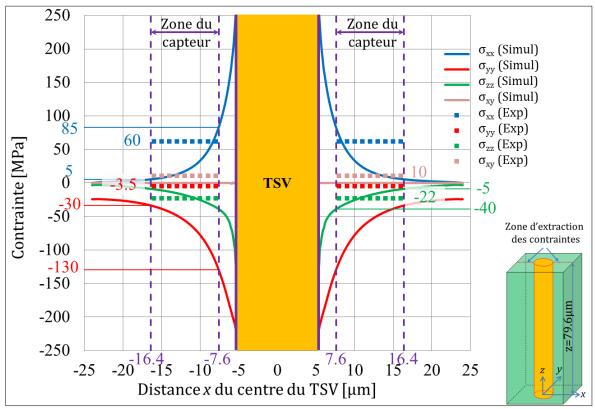

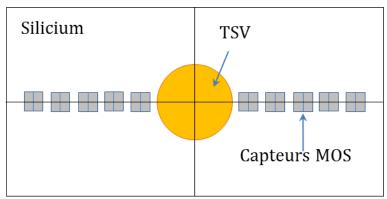

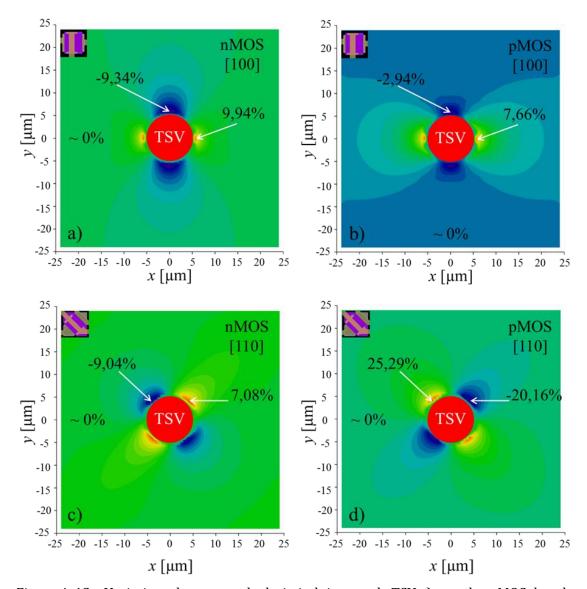

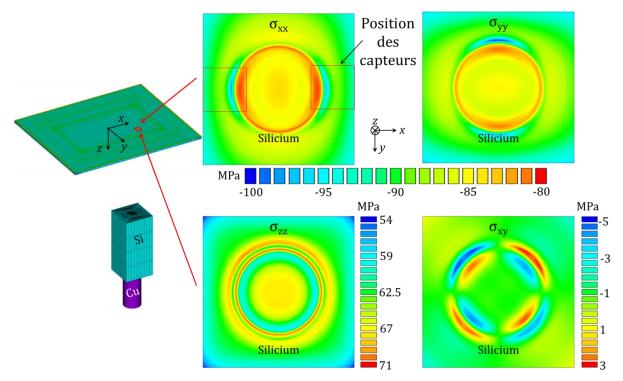

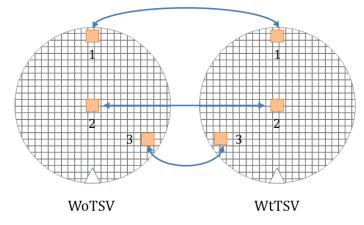

| II. I  | Etudes de contraintes induites par le TSV                                       | 85           |

| 1.     | Méthode expérimentale : utilisation des capteurs                                | 85           |

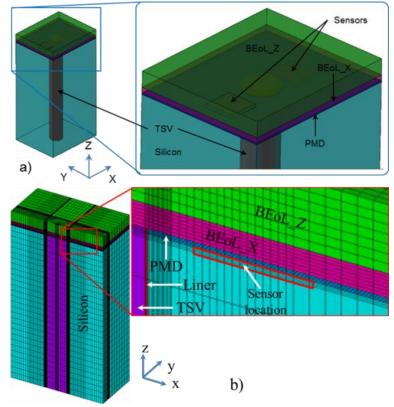

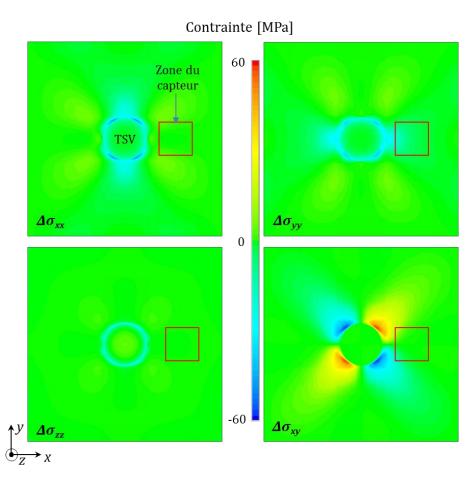

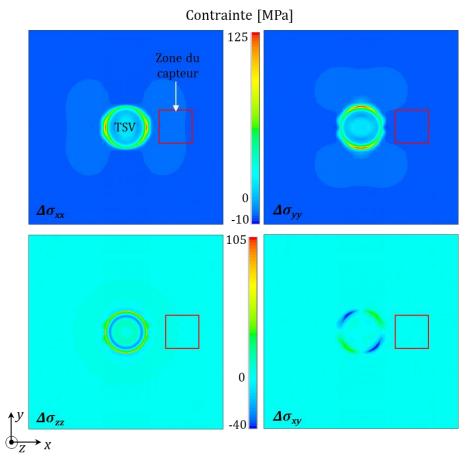

| 2.     | Approche numérique : simulation par éléments finis                              | 90           |

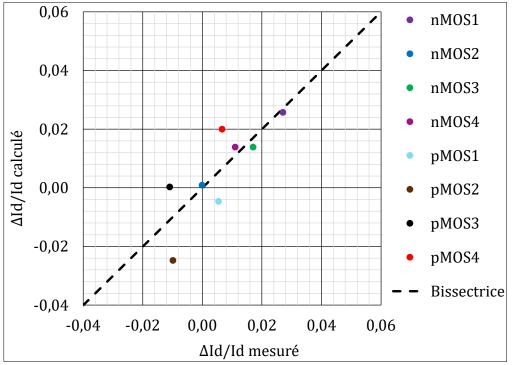

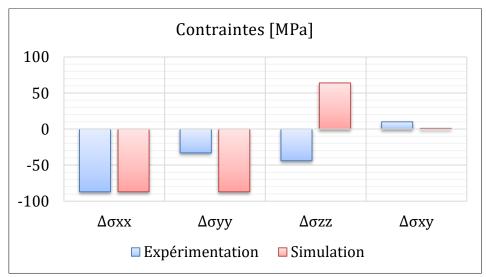

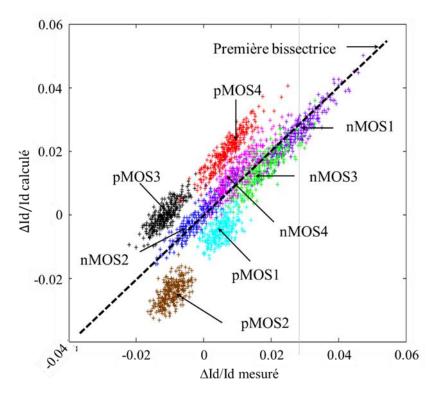

| 3.     | Corrélation et discussion                                                       | 95           |

| 4.     | Etude complémentaire : calcul de variations de courants de drain                | 96           |

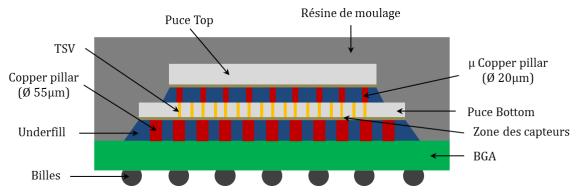

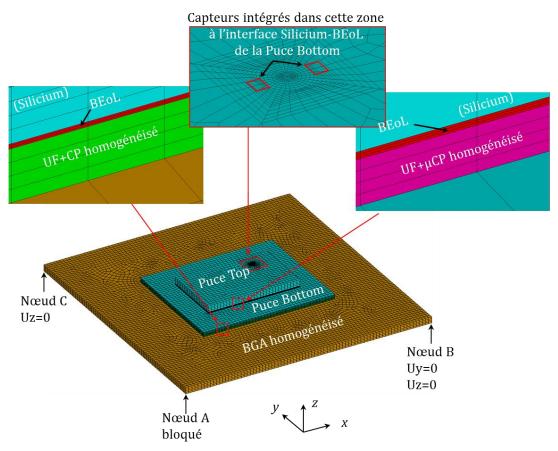

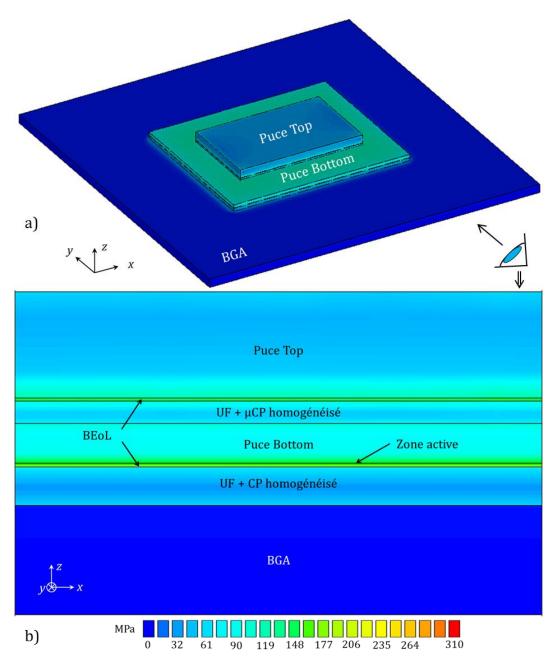

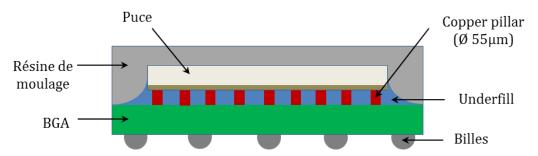

| III.   | Contraintes induites dans un empilement 3D                                      | 97           |

| 1.     | Méthode expérimentale : utilisation des capteurs                                | 98           |

| 2.     | Méthode numérique : simulation par éléments finis                               | 100          |

| 3.     | Corrélation et discussion                                                       | 105          |

| IV.    | Contraintes induites dans un empilement 2D                                      | 106          |

| V. S   | Sources d'erreurs liées à l'utilisation des transistors                         | 108          |

| SYNTHI | ESE IV                                                                          | 109          |

| ABSTRA | ACT IV                                                                          | 111          |

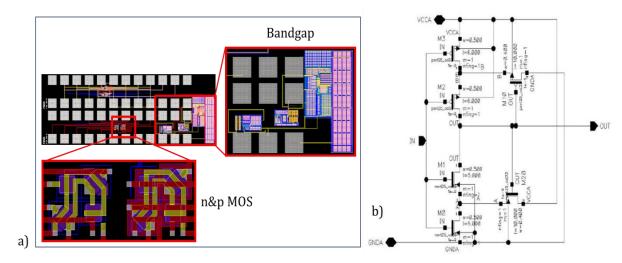

| CHAPIT | RE V : EXPLORATION DE NOUVELLES STRUCTURES                                      | 113          |

| I. S   | Structure et stratégie de test                                                  | 113          |

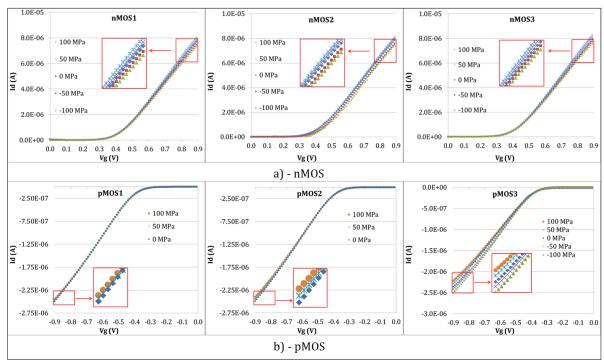

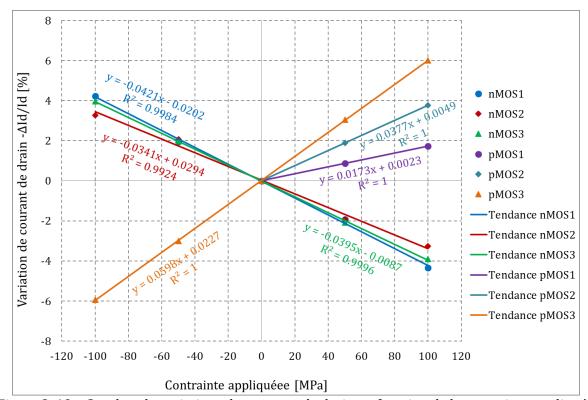

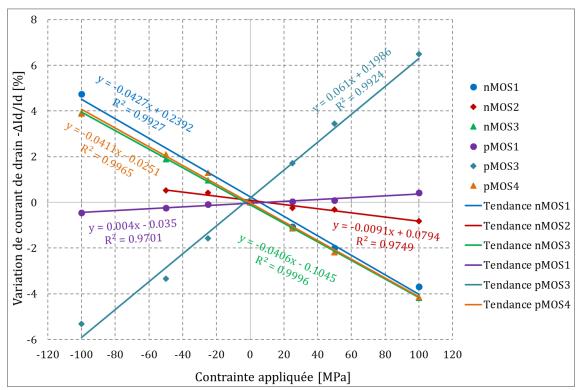

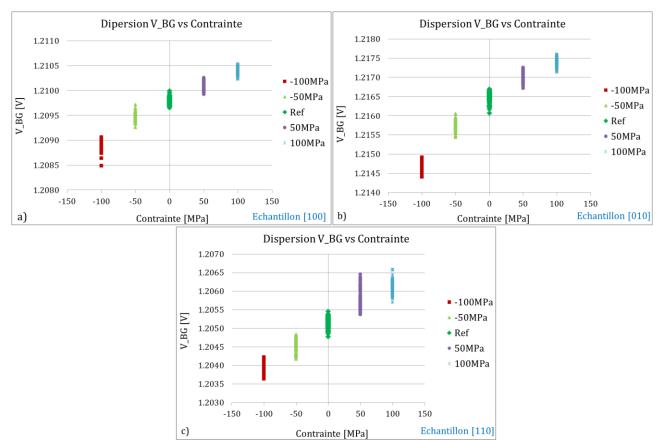

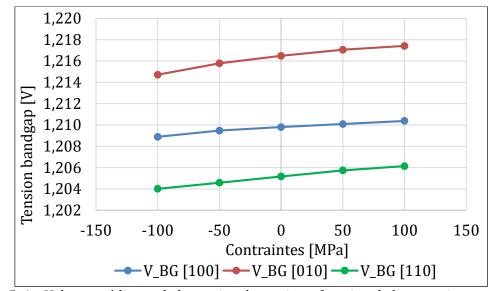

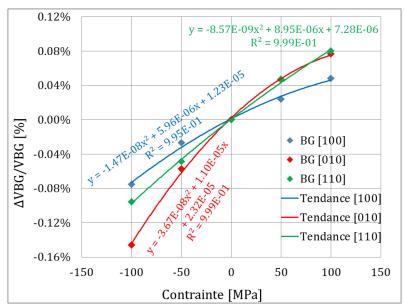

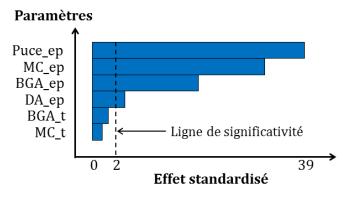

| II. Et  | tude de sensibilité / calibration                                       | 114 |

|---------|-------------------------------------------------------------------------|-----|

| 1.      | Méthodologie                                                            | 114 |

| 2.      | Résultats                                                               | 114 |

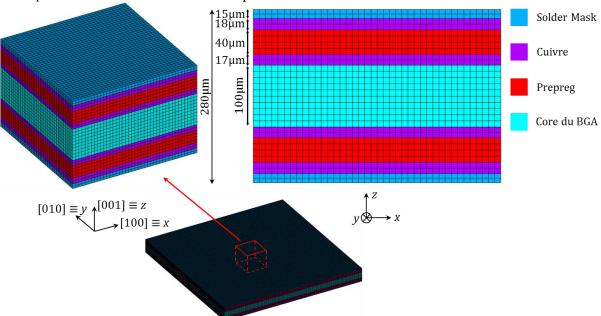

| III.    | Contraintes par simulation éléments finis                               | 117 |

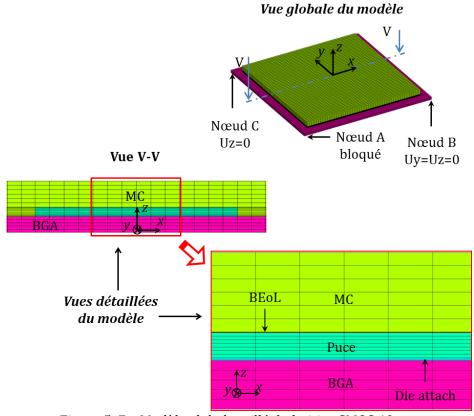

| 1.      | Description du modèle                                                   | 117 |

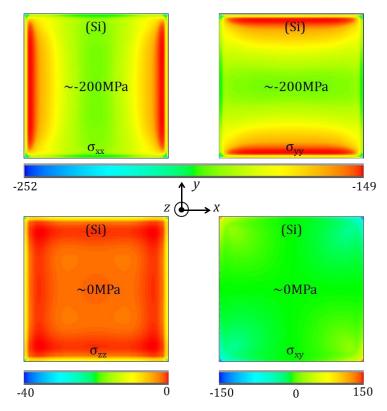

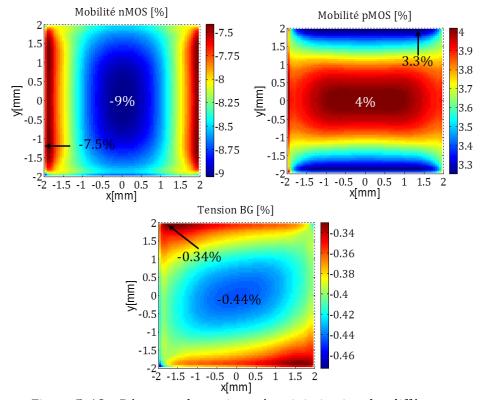

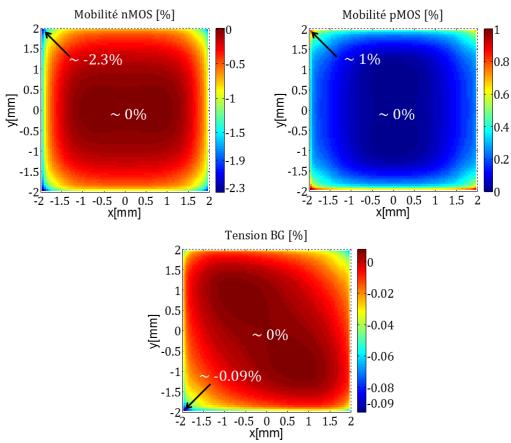

| 2.      | Résultats : contraintes induites                                        | 119 |

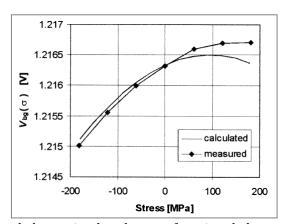

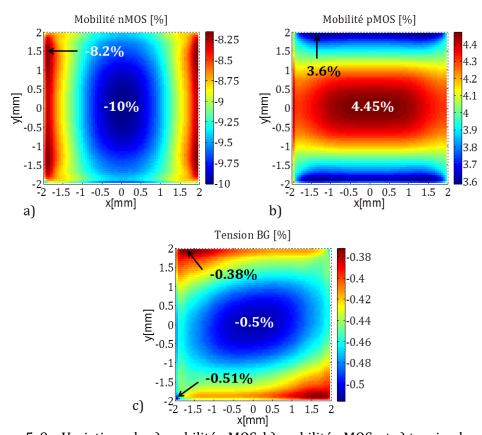

| IV.     | Impacts des contraintes sur les MOS et la structure bandgap             | 120 |

| 1.      | Relations caractéristiques                                              | 120 |

| 2.      | Résultats : impact des contraintes                                      | 121 |

| V. Et   | cude paramétrique : minimisation des contraintes                        | 122 |

| 1.      | Etude paramétrique                                                      | 122 |

| 2.      | Minimisation de la différence entre le coin et le centre de puce        | 123 |

| 3.      | Minimisation sur toute la surface de la puce                            | 126 |

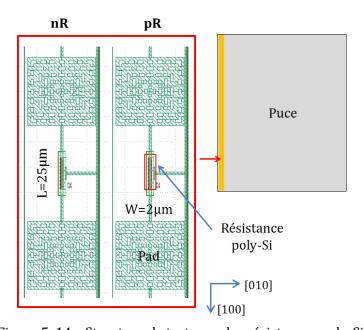

| VI.     | Etudes de sensibilité des résistances polysilicium                      | 127 |

| 1.      | Structure de test                                                       | 128 |

| 2.      | Résultats du test                                                       | 129 |

| SYNTHES | SE V                                                                    | 131 |

| ABSTRAG | CT V                                                                    | 132 |

|         | SION GENERALE ET PERSPECTIVES                                           |     |

| ANNEXE  | S                                                                       | 137 |

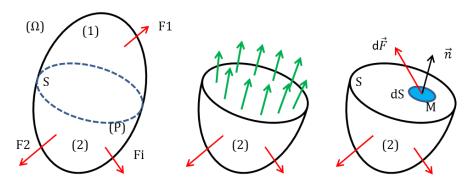

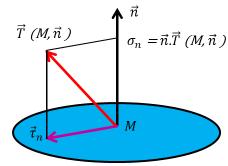

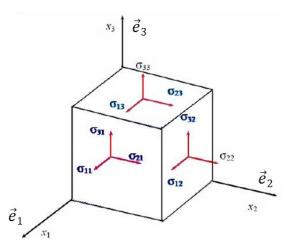

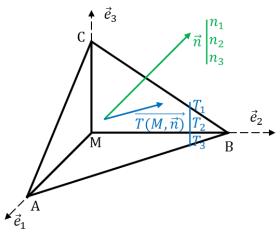

| Annex   | e A : Notions de tenseur de contraintes                                 | 137 |

| Annex   | e B : Dessin CAO de la machine de flexion quatre-points                 | 142 |

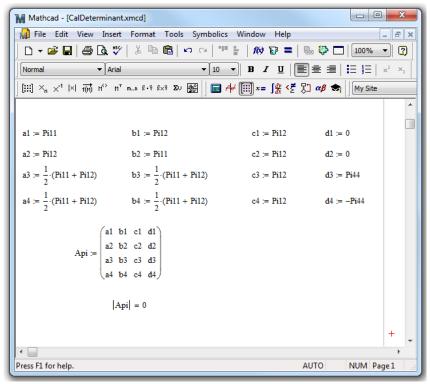

| Annex   | e C : Calcul du déterminant de la matrice [A] avec Mathcad              | 143 |

| Annex   | e D : Calcul de contrainte induite par le TSV – seconde approche        | 143 |

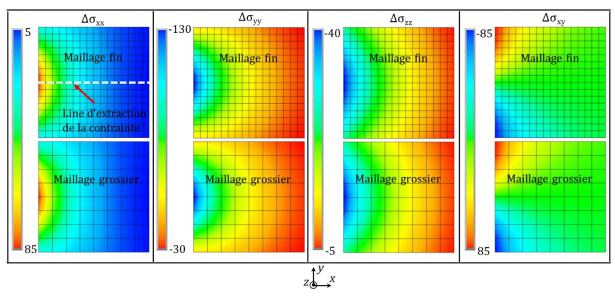

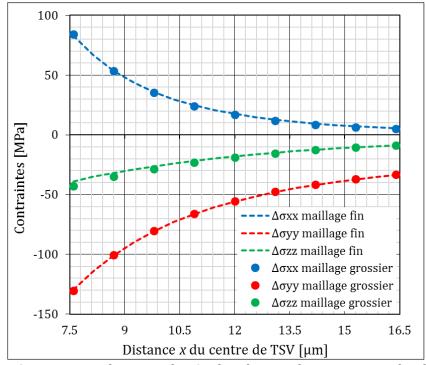

| Annex   | e E : Contrainte TSV – Etude de sensibilité au maillage                 | 145 |

| Annex   | e F : Impact de l'anisotropie du silicium et de la plasticité du cuivre | 147 |

| 1.      | Effet de l'anisotropie du silicium                                      | 147 |

| 2.      | Effet de la plasticité du cuivre                                        | 148 |

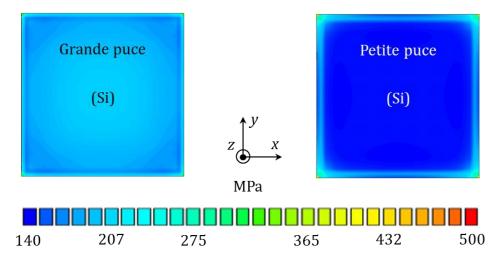

| Annex   | e G : Impact de la taille de puce sur la contrainte en CMOS40           | 150 |

| REFERE  | NCES BIBLIOGRAPHIQUES                                                   | 151 |

| RESUME  | GLOBAL                                                                  | 159 |

| GENERA  | I. ABSTRACT                                                             | 161 |

# **LISTE DES FIGURES**

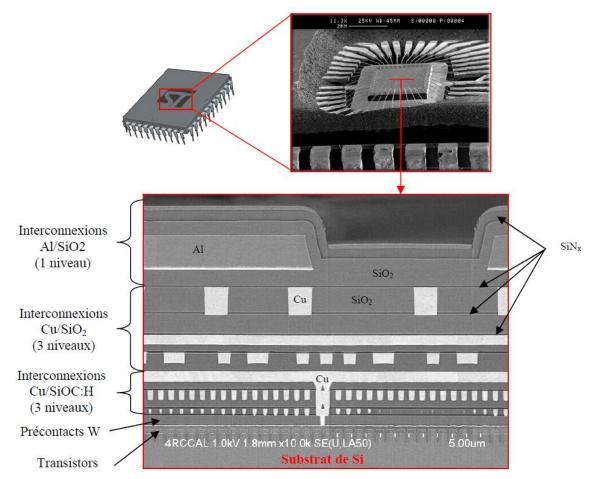

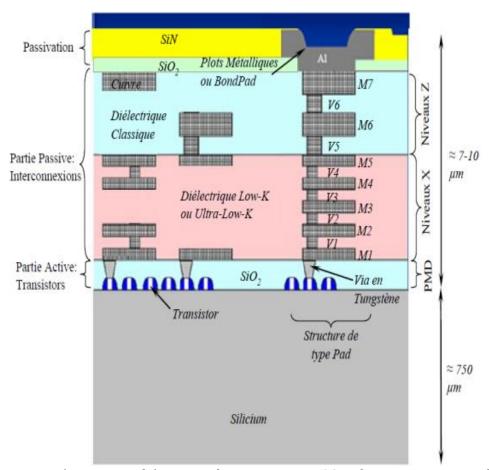

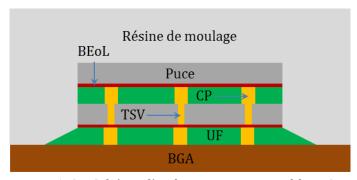

| Figure 1 – Vue en coupe d'un circuit intégré du nœud technologique 90 nm [Vayrette, 2012].                          | 1    |

|---------------------------------------------------------------------------------------------------------------------|------|

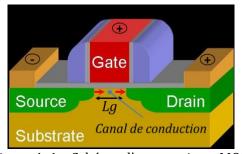

| Figure 1. 1 – Schéma d'un transistor MOS.                                                                           | 5    |

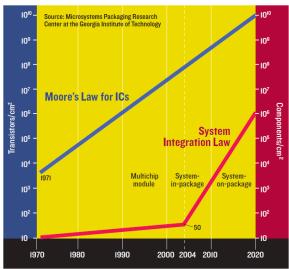

| Figure 1. 2 – Loi de Moore et loi More than Moore [Tummala, 2006]                                                   |      |

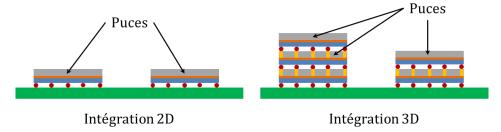

| Figure 1. 3 – Schémas montrant l'intégration 2D et 3D                                                               |      |

| Figure 1. 4 – Représentation schématique des transistors MOS et des interconnexions <b>[Galloi</b> :                |      |

| Garreignot, 2010]                                                                                                   |      |

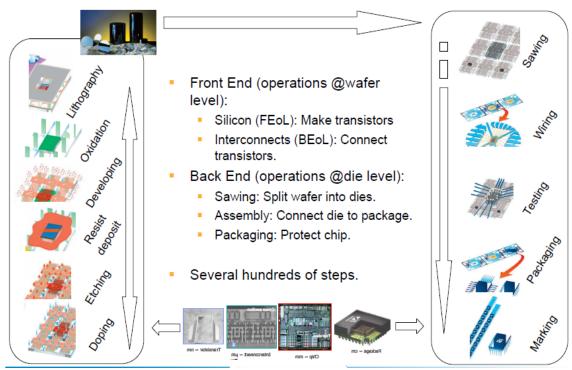

| Figure 1. 5 – Schéma descriptif du procédé de fabrication [Fiori, 2010]                                             |      |

| Figure 1. 6 – Vue montrant les lignes de découpe [Gallois-Garreignot, 2010]                                         |      |

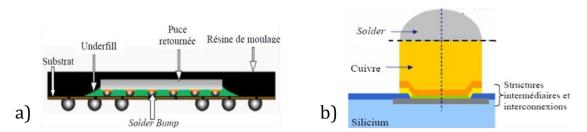

| Figure 1. 7 – a) Schéma d'un boitier avec assemblage Solder Bump, b) schéma d'un Copper Pil                         |      |

| [Gallois-Garreignot, 2010]                                                                                          |      |

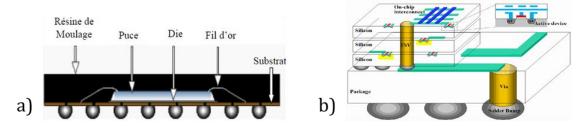

| Figure 1.8 – a) Schéma d'un boitier avec assemblage Wire Bonding, b) schéma d'un assembla                           | ge   |

| TSV [Gallois-Garreignot, 2010].                                                                                     | _    |

| Figure 1. 9 – Schéma d'un boitier avec assemblage 3D                                                                | . 12 |

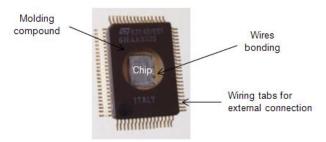

| Figure 1. 10 – Circuit Intégré [Gallois-Garreignot, 2010]                                                           | . 13 |

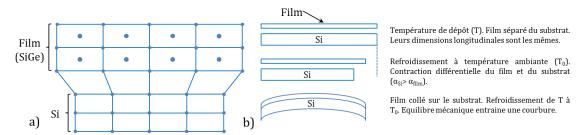

| Figure 1. 11 - Illustration de a) différence de paramètre de maille, b) la courbure générale lor                    |      |

| du refroidissement d'un film collé sur un substrat avec des CTE différents (contrainte                              |      |

| thermoélastique)                                                                                                    | . 15 |

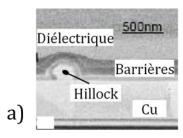

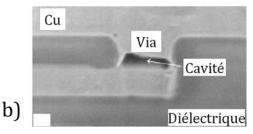

| Figure 1. 12 – Vue au microscope montrant a) un monticule (hillock) [Timma, 2009], b) la                            |      |

| formation d'une cavité [Oshima, 2002]                                                                               |      |

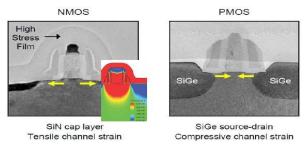

| Figure 1. 13 – Strain engineering [Fiori, 2010]                                                                     | . 16 |

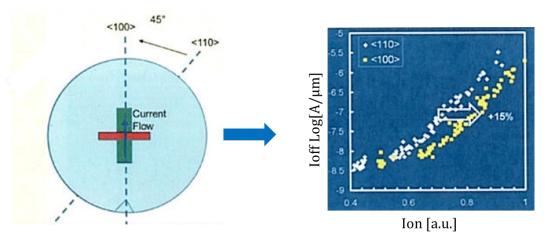

| Figure 1. 14 – Schéma montrant un gain de performance sur les pMOS par orientation du                               |      |

| silicium                                                                                                            | . 17 |

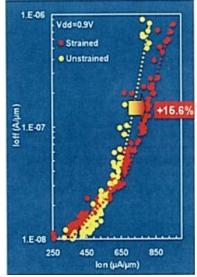

| Figure 1. 15 - Gain de performance sur les nMOS avec utilisation d'un film                                          | . 17 |

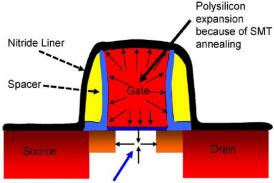

| Figure 1. 16 - Mécanisme de transfert de contrainte dans le canal d'un transistor nMOS. Grâce                       | à    |

| l'expansion thermique pendant le recuit, une contrainte de tension est induite dans le canal                        |      |

| [Pandey, 2011]                                                                                                      | . 18 |

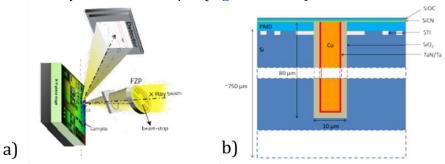

| Figure 1. 17 – a) Représentation schématique d'un TSV dans le silicium, b) Vue globale                              |      |

| schématique du dispositif expérimental. Le faisceau rayon-X est focalisé en utilisant le FZP                        |      |

| (Fresnel Zone Plate). L'angle d'incidence $\omega$ et l'angle de diffraction $2\theta$ sont montrés <b>[Vianne,</b> |      |

| 2014]                                                                                                               |      |

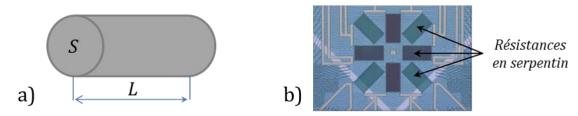

| Figure 1. 18 – a) Représentation schématique d'un fil conducteur ; b) Vue au microscope d'un                        |      |

| capteur de contrainte passif en serpentin [Vianne, 2014].                                                           | . 21 |

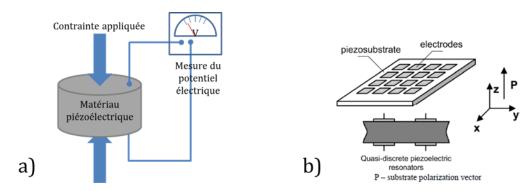

| Figure 1. 19 – Représentation schématique d'un effet piézoélectrique; b) structure                                  |      |

| piézoélectrique [Kolev, 2010].                                                                                      |      |

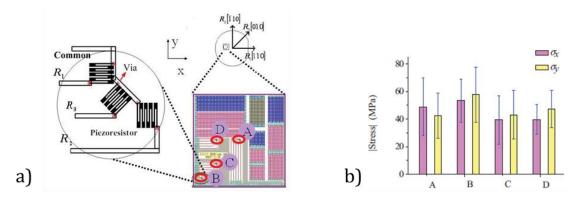

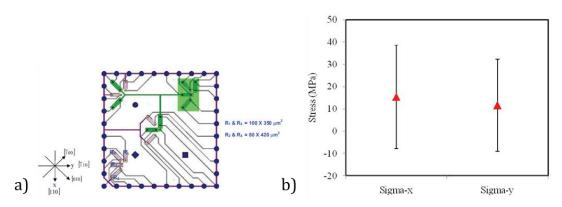

| Figure 1. 20 – Schéma de puce de test et le capteur piézorésistif en rosette, b) Contrainte abso                    |      |

| due à la mise en boitier dans les zones des capteurs [Chang, 2013]                                                  |      |

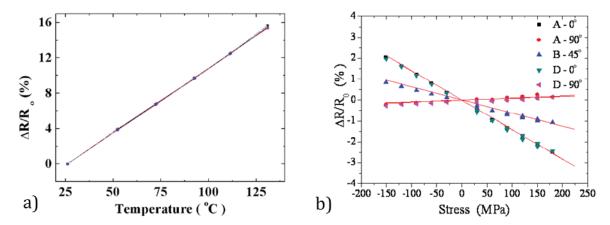

| Figure 1. 21 – Variation de résistance en fonction de a) de la température et b) de la contraint                    |      |

| appliquée à température fixe [Chang, 2013]                                                                          | . 23 |

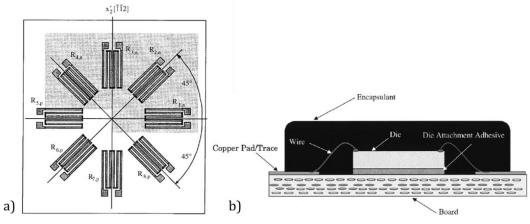

| Figure 1. 22 – a) Capteur de contrainte sur du silicium (111); b) Puce encapsulée par Wire                          | 22   |

| Bonding [Zou, 1999]                                                                                                 | . 23 |

| Figure 1. 23 – Schémas montrant a) les positions de matrice de transistors, b) le dispositif de                     | ~ .  |

| flexion quatre-points et c) la puce encapsulée [Ivankovic, 2012].                                                   | . 24 |

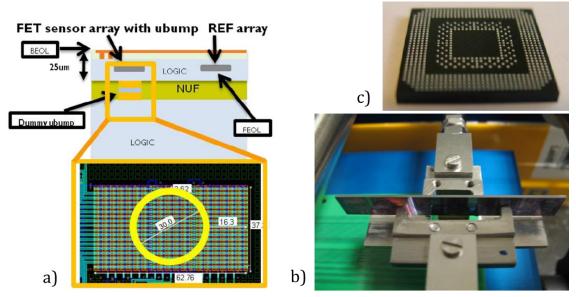

| Figure 1. 24 – a) Schéma du capteur de contrainte; b) Contraintes ( $\sigma_{xx}$ et $\sigma_{yy}$ ) mesurées après | 2.4  |

| bumping [Zhang, 2012].                                                                                              |      |

| Figure 1. 25 – Schéma de capteur de contrainte en rosette [Yong, 2013]                                              |      |

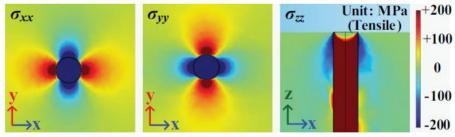

| rigure 1. 40 - Contrainte selon les axes X, V, et Z [nail, 4014]                                                    | . Z/ |

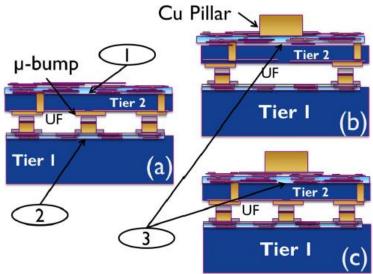

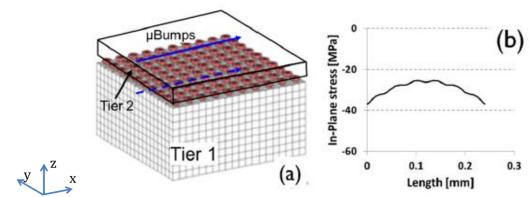

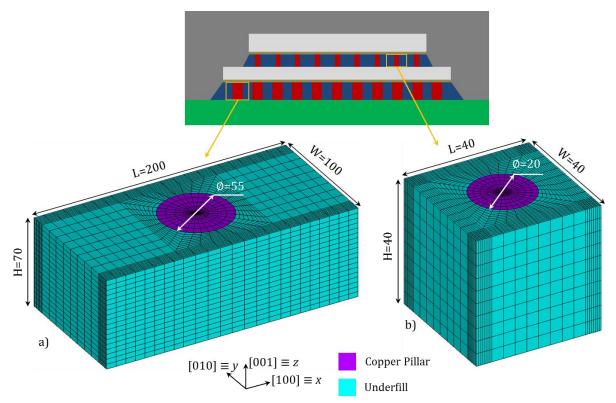

| Figure 1. 27 – Vue en coupe de trois zones différentes dans l'empilement 3D. a) matrice de micro-bumps avec un espacement de $40\mu m$ , b) Copper pillar à la partie supérieure de la puce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| fine, c) combinaison des micro-bumps et des CP <b>[Cherman, 2014]</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| bumps, et b) la contrainte simulée suivant la ligne continue bleue [Cherman, 2014]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

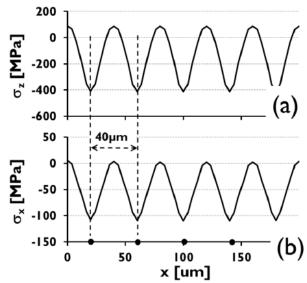

| Figure 1. 29 – a) Composante verticale $\sigma z$ et b) dans le plan $\sigma x$ de la contrainte modélisée à la                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| surface supérieure de la puce Tier1 suivant la droite reliant les centres des micro-bumps (line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9    |

| discontinue dans la Figure 1.16-a). Les points noirs indiquent les positions des micro-bumps [Cherman, 2014].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28   |

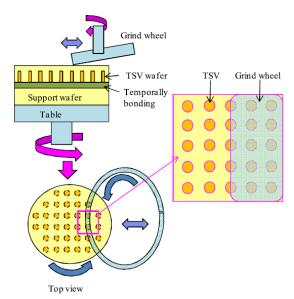

| Figure 1. 30 – Représentation schématique du procédé d'amincissement de la plaquette du                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 20 |

| silicium remplie de TSV [Che, 2014].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 29 |

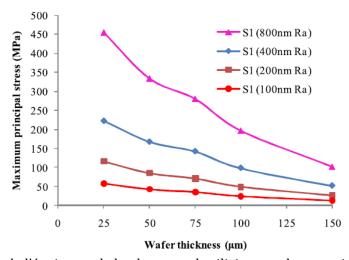

| Figure 1. 31 – Effet de l'épaisseur de la plaquette de silicium sur la contrainte maximale [Che,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 2014]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 29 |

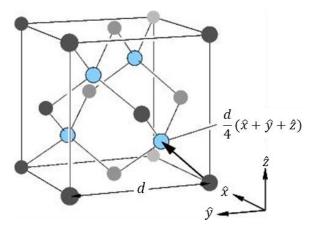

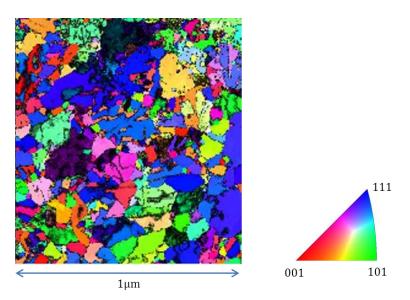

| Eigure 2.1 Maille gubique conventionnelle de la structure diament [Achgroft 1076]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24   |

| Figure 2. 1 – Maille cubique conventionnelle de la structure diamant [Ashcroft, 1976]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

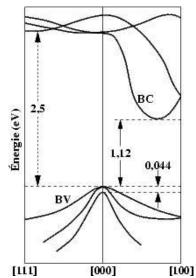

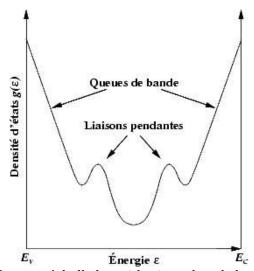

| Figure 2. 3 – Densité d'états en échelle logarithmique dans la bande interdite du silicium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 54 |

| amorphe ( $E_V$ : bande de valence, $E_C$ : bande de conduction) [ <b>Lu, 1984</b> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35   |

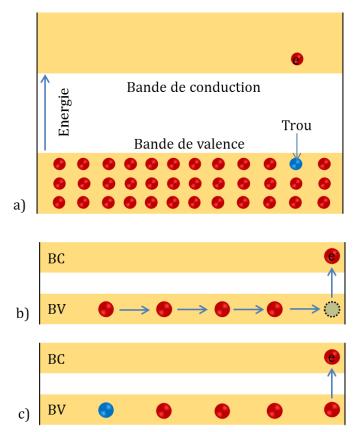

| Figure 2. 4 – Représentation schématique des bandes d'énergie pour des électrons et leurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| mouvements dans un solide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| Figure 2. 5 – Critères de qualité : a) sensibilité, b) testabilité, c) variabilité                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

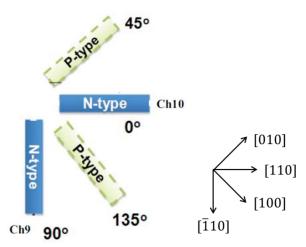

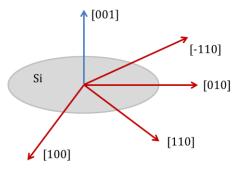

| Figure 2. 6 – Représentation schématique des directions cristallographiques d'une plaquette de la ciliaire.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

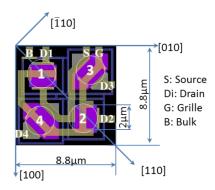

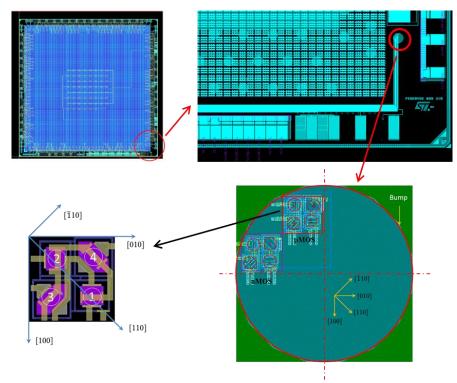

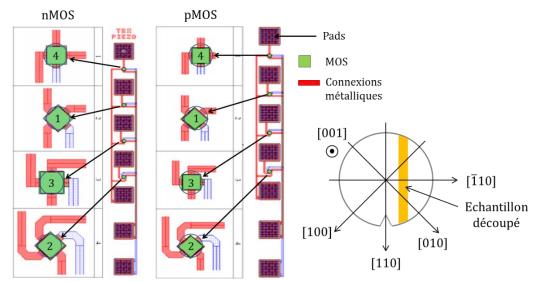

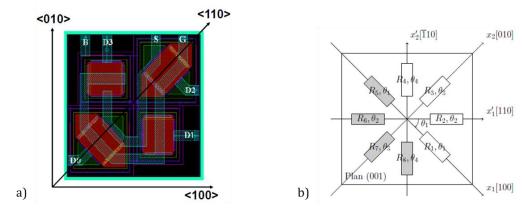

| siliciumFigure 2. 7 – Capteur de contrainte en rosette de MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

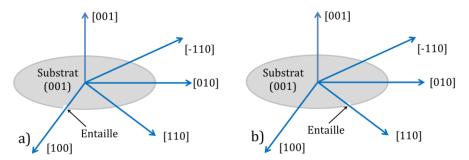

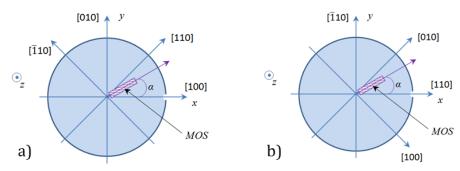

| Figure 2. 8 – Représentation schématique a) d'une plaquette <100> et b) d'une plaquette <110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Tigure 2. 6 Representation senematique a) a une plaquette \$1000 et b) a une plaquette \$11000 et b) a une plaquette \$10000 et b) a une plaquette \$100000 et b) |      |

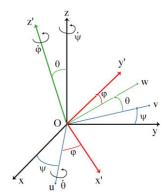

| Figure 2. 9 – Angles de rotation (angles d'Euler).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 43 |

| Figure 2. 10 – Système de coordonnées a) d'une plaquette tournée et b) d'une plaquette non                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| tournée ; α: l'angle entre le canal du MOS et l'axe x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

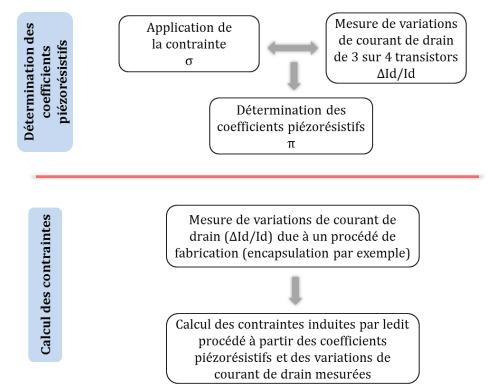

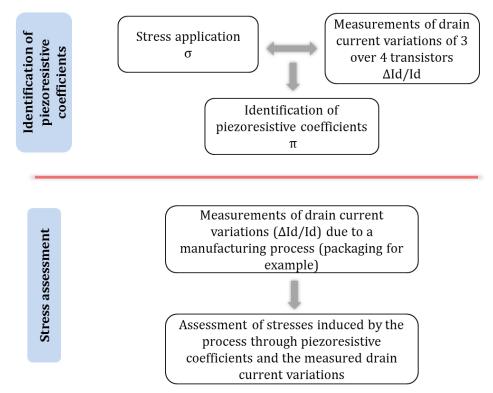

| Figure 2. 11 – Organigramme montrant la démarche globale de détermination des contraintes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| l'aide des capteurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 48 |

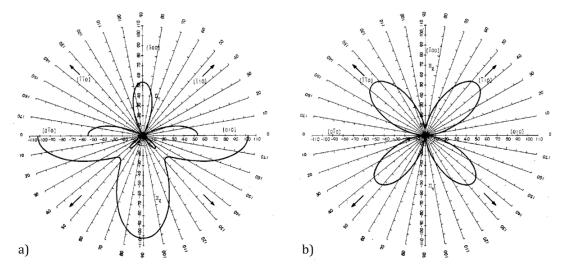

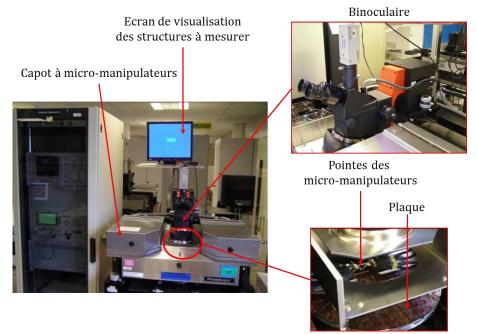

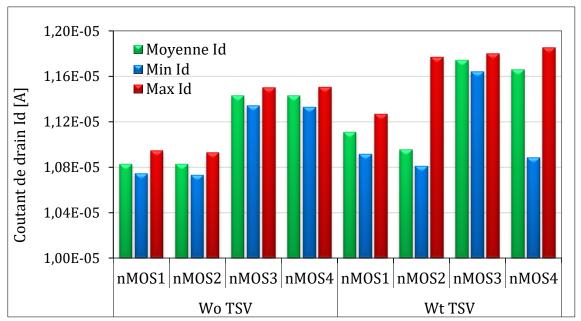

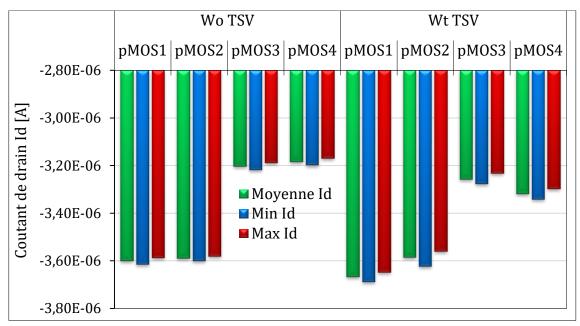

| Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 49 |