# Safe and secure model-driven design for embedded systems

Letitia Li

#### ► To cite this version:

Letitia Li. Safe and secure model-driven design for embedded systems. Embedded Systems. Université Paris Saclay (COmUE), 2018. English. NNT: 2018SACLT002 . tel-01894734

### HAL Id: tel-01894734 https://pastel.hal.science/tel-01894734

Submitted on 12 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITE PARIS-SACLAY

## Approche Orientée Modèles pour la Sûreté et la Sécurité des Systèmes Embarqués

Thèse de doctorat de l'Université Paris-Saclay préparée à Telecom ParisTech

Ecole doctorale n°580 Dénomination (STIC) Spécialité de doctorat: Informatique

Thèse présentée et soutenue à Biot, le 3 septèmbre 2018, par

### LETITIA W. LI

Composition du Jury :

| Prof. Philippe Collet                    |                       |

|------------------------------------------|-----------------------|

| Professeur, Université Côte d'Azur       | Président             |

| Prof. Guy Gogniat                        |                       |

| Professeur, Université de Bretagne Sud   | Rapporteur            |

| Prof. Maritta Heisel                     |                       |

| Professeur, University Duisburg-Essen    | Rapporteur            |

| Prof. Jean-Luc Danger                    |                       |

| Professeur, Telecom ParisTech            | Examinateur           |

| Dr. Patricia Guitton                     |                       |

| Ingénieur, Renault Software Labs         | Examinateur           |

| Dr. Ludovic Apvrille                     |                       |

| Maître de Conférences, Telecom ParisTech | Directeur de thèse    |

| Dr. Annie Bracquemond                    |                       |

| Directeur de Recherche, Institut Vedecom | Co-directeur de thèse |

|                                          |                       |

ÉCOLE DOCTORALE

Sciences et technologies de l'information et de la communication (STIC)

Titre: Approche Orientée Modèles pour la Sûreté et la Sécurité des Systèmes Embarqués

**Mots clés:** systèmes embarques, véhicules autonomes, sûreté de fonctionnement, sécurité, exploration d'architecture

**Résumé:** La présence de systèmes et d'objets embarqués communicants dans notre vie quotidienne a apporté une myriade d'avantages, allant de l'ajout de commodités et de divertissements à l'amélioration de la sûreté des déplacements et des soins de santé. Cependant, les défauts et les vulnérabilités de ces systèmes exposent leurs utilisateurs à des risques de dommages matériels, de pertes monétaires, et même de dommages corporels. Par exemple, certains véhicules commercialisés, qu'ils soient connectés ou conventionnels, ont déjà souffert d'une variété de défauts de conception entraînant des victimes. Dans

le même temps, alors que les véhicules sont de plus en plus connectés (et dans un avenir proche, autonomes), les chercheurs ont démontré la possibilité de piratage de leurs capteurs ou de leurs systèmes de contrôle interne. Cette thèse s'intéresse à la sécurité et la sûreté des systèmes embarqués, dans le contexte du véhicule autonome de l'Institut Vedecom. Notre approche repose sur une nouvelle méthode de modélisation pour concevoir des systèmes embarqués sûrs et sécurisés, basée sur la méthodologie SysML-Sec, et impliquant de nouvelles stratégies de modélisation et de vérification formelle.

Title: Safe and Secure Model-Driven Design for Embedded Systems

Keywords: embedded systems, autonomous vehicles, safe comportment, security, design space exploration

**Abstract:** The presence of communicating embedded systems/IoTs in our daily lives have brought a myriad of benefits, from adding conveniences and entertainment, to improving the safety of our commutes and health care. However, the flaws and vulnerabilities in these devices expose their users to risks of property damage, monetary losses, and personal injury. For example, consumer vehicles, both connected and conventional, have succumbed to a variety of design flaws resulting in injuries, and in some

cases, death. At the same time, as vehicles become increasingly connected (and in the near future, autonomous), researchers have demonstrated possible hacks on their sensors or internal control systems. This thesis discusses how to ensure the safety and security of embedded systems, in the context of Institut Vedecom's autonomous vehicle. Our approach involves a new model-based methodology for safe and secure design, which involve new modeling and verification methods.

#### Acknowledgments

The research presented in this thesis was sponsored by Institut Vedecom of Versailles, France and took place at Lab System-on-Chip of Telecom ParisTech in Sophia Antipolis, France.

With the conclusion of my PhD, I would like to recognize everyone who made the completion of this thesis possible: through technical support, encouragement, assisting with my post-thesis career plans, and helping me find a life in France.

I would like to thank my advisors, Professor Ludovic Apvrille and Dr. Annie Bracquemond, who have guided me through this thesis. They have taught me all about modeling, verification, safety, security, and embedded systems, and it is their suggestions and corrections who have shaped this thesis into a coherent scientific work. I have been exceptionally fortunate for their availability to aid me in more than just my research, for I could not have navigated the administrative procedures or language difficulties without them, and I am also grateful for their willingness to show me the cultural heritage of the country, such as raclette.

Next, I would like to thank all of my jury members for their time in participating in my defense, and all of the insights and the expertise they brought forth. I thank my reviewers: Professor Guy Gogniat and Professor Maritta Heisel for taking time this summer to read my thesis and offer feedback vital to its improvement, and the examiners of my jury: Professor Jean-Luc Danger, Professor Philippe Collet, and Dr. Patricia Guitton, for their interest in my research.

I would also like to thank all of the developers of TTool, fellow members of LabSoc, and co-authors, for the working environment conducive to research, and all of our shared triumphs and disasters, especially: Professor Renaud Pacalet, who originally welcomed me to LabSoc for an internship and inspired me to start a career in research, and taught me the meaning of research and the search for knowledge and understanding, Professor Tullio Tanzi, who provided our case studies on his research on drones and rovers for disaster relief, and has taught me so much about radar and to find the courage to face the rest of the world so different than what I have experienced, Professor Rabea Ameur-Boulifa, who has been an excellent source of knowledge on formalization and verification, Dr. Florian Lugou, who developed so much of TTool's security verification capabilities upon which my research is based, Matteo Bertolino, my officemate and fellow PhD student, who I am sure will forge his own career in academia, Dr. Dominique Blouin, whose work has greatly facilitated TTool development, Professor Daniela Genius of LIP6, our co-author who inspired most of our work on performance and relating between levels of abstraction, and Dr. Andrea Enrici of Nokia, the first of my fellow PhD students to graduate, who has been a great source of information regarding post-thesis life. I also thank the other researchers at Institut Vedecom, Laurent Bonic, Professor Féthi ben Ouezdou, and many others for helping with the modeling and testing on the company side.

I thank my dearest and longtime friends Dr. Sharon Chou, Adam Fagan, Clement Pit-Claudel, Andrea Wang, and Stephie Wu, for their encouragement to see this thesis through, and staying a part of my life from afar. I am grateful for these friendships who have endured time and distance, and that they have ensured that we can meet again in those brief, precious times that we are on the same side of the ocean.

And lastly, I thank my parents, who have always supported me no matter where my education and career take me. They have set an example to strive for education, knowledge, integrity, and scientific achievement, which, in my own way, I have attempted to live up to.

#### Abstract

The presence of communicating embedded systems/IoTs in our daily lives have brought a myriad of benefits, from adding conveniences and entertainment, to improving the safety of our commutes and health care. However, the flaws and vulnerabilities in these devices expose their users to risks of property damage, monetary losses, and personal injury. For example, consumer vehicles, both connected and conventional, have succumbed to a variety of design flaws resulting in injuries, and in some cases, death. At the same time, as vehicles become increasingly connected (and in the near future, autonomous), researchers have demonstrated possible hacks on their sensors or internal control systems, including direct injection of messages on the CAN bus.

Ensuring the safety of users or bystanders involves considering multiple factors. Conventional safety suggests that a system should not contain software and hardware flaws which can prevent it from correct function. 'Safety of the Intended Function' involves avoiding the situations which the system or its components cannot handle, such as adverse extreme environmental conditions. Timing can be critical for certain real-time systems, as the system will need to respond to certain events, such as obstacle avoidance, within a set period to avoid dangerous situations. Finally, the safety of a system depends on its security. An attacker who can send custom commands or modify the software of the system may change its behavior and send it into various unsafe situations.

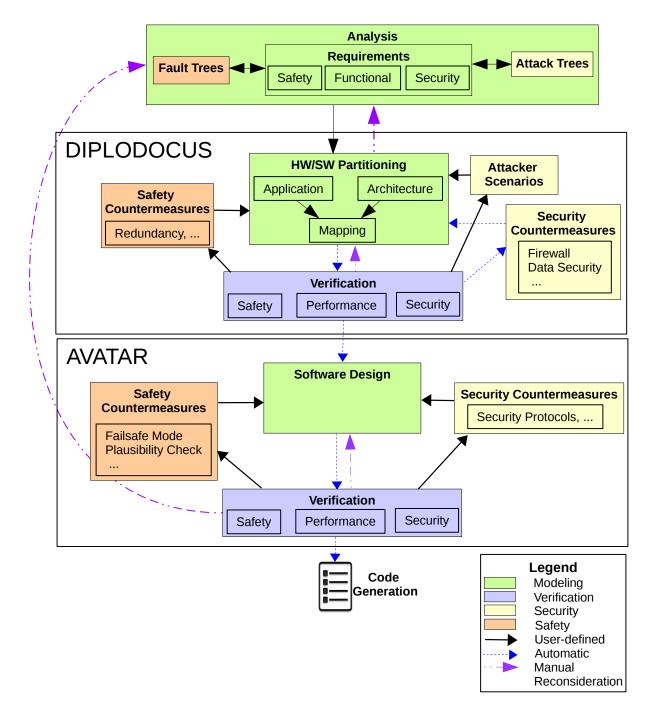

Various safety and security countermeasures for embedded systems, especially connected vehicles, have been proposed. To place these countermeasures correctly requires methods of analyzing and verifying that the system meets all safety, security, and performance requirements, preferably at the early design phases to minimize costly re-work after production. This thesis discusses the safety and security considerations for embedded systems, in the context of Institut Vedecom's autonomous vehicle. Among the proposed approaches to ensure safety and security in embedded systems, Model-Driven Engineering is one such approach that covers the full design process, from elicitation of requirements, design of hardware and software, simulation/formal verification, and final code generation. This thesis proposes a modeling-based methodology for safe and secure design, based on the SysML-Sec Methodology, which involve new modeling and verification methods.

Security modeling is generally performed in the last phases of design. However, security impacts the early architecture/mapping and HW/SW partitioning decisions should be made based on the ability of the architecture to satisfy security requirements. This thesis proposes how to model the security mechanisms and the impact of an attacker as relevant to the HW/SW Partitioning phase. As security protocols negatively impact performance, it becomes important to measure both the usage of hardware components and response times of the system. Overcharged components can result in unpredictable performance and undesired delays. This thesis also discusses latency measurements of safety-critical events, focusing on one critical to autonomous vehicles: braking as after obstacle detection. Together, these additions support the safe and secure design of embedded systems.

#### Abstract

La présence de systèmes et d'objets embarqués communicants dans notre vie quotidienne a apporté une myriade d'avantages, allant de l'ajout de commodités et de divertissements à l'amélioration de la sûreté des déplacements et des soins de santé. Cependant, les défauts et les vulnérabilités de ces systèmes exposent leurs utilisateurs à des risques de dommages matériels, de pertes financières, et même de dommages corporels. Par exemple, certains véhicules commercialisés, qu'ils soient connectés ou conventionnels, ont déjà souffert d'une variété de défauts de conception entraînant des victimes. Dans le même temps, alors que les véhicules sont de plus en plus connectés (et dans un avenir proche, autonomes), les chercheurs ont démontré la possibilité de piratage de leurs capteurs ou de leurs systèmes de contrôle interne, y compris l'injection directe de messages sur le bus CAN.

Pour assurer la sûreté des utilisateurs et des passants, il faut considérer plusieurs facteurs. La sûreté conventionnelle suggère qu'un système ne devrait pas contenir de défauts logiciels et matériels qui peuvent l'empêcher de fonctionner correctement. La "sûreté de la fonction attendue" consiste à éviter les situations que le système ou ses composants ne peuvent pas gérer, comme des conditions environnementales extrêmes. Le timing peut être critique pour certains systèmes en temps réel, car afin d'éviter des situations dangereuses, le système devra réagir à certains événements, comme l'évitement d'obstacles, dans un délai déterminé. Enfin, la sûreté d'un système dépend de sa sécurité. Un attaquant qui peut envoyer des commandes fausses ou modifier le logiciel du système peut changer son comportement et le mettre dans diverses situations dangereuses.

Diverses contre-mesures de sécurité et de sûreté pour les systèmes embarqués, en particulier les véhicules connectés, ont été proposées. Pour mettre en oeuvre correctement ces contre-mesures, il faut analyser et vérifier que le système répond à toutes les exigences de sûreté, de sécurité et de performance, et les faire la plus tôt possible dans les premières phases de conception afin de réduire le temps de mise sur le marché, et éviter les reprises. Cette thèse s'intéresse à la sécurité et la sûreté des les systèmes embarqués, dans le contexte du véhicule autonome de l'Institut Vedecom. Parmi les approches proposées pour assurer la sûreté et la sécurité des les systèmes embarqués, l'ingénierie dirigée par modèle est l'une de ces approches qui couvre l'ensemble du processus de conception, depuis la définition des exigences, la conception du matériel et des logiciels, la simulation/vérification formelle et la génération du code final. Cette thèse propose une nouvelle méthod de modélisation pour une conception sûre et sécurisée, basée sur la méthodologie SysML-Sec, et impliquant de nouvelles stratégies de modélisation et de vérification.

La modélisation de la sécurité est généralement effectuée dans les dernières phases de la conception. Cependant, la sécurité a un impact sur l'architecture/allocation; les décisions de partitionnement logiciel/matériel devraient être prises en fonction de la capacité de l'architecture à satisfaire aux exigences de sécurité. Cette thèse propose comment modéliser les mécanismes de sécurité et l'impact d'un attaquant dans la phase de partitionnement logiciel/matériel. Comme les protocoles de sécurité ont un impact négatif sur le performance d'un système, c'est important de mesurer l'utilisation des composants matériels et les temps de réponse du système. Des composants surchargés peuvent entraîner des performances imprévisibles et des retards indésirables. Cette thèse traite aussi des mesures de latence des événements critiques pour la sécurité, en se concentrant sur un exemple critique pour les véhicules autonomes : le freinage/réponse après la détection d'obstacles. Ainsi, nos contributions soutiennent la conception sûre et sécurisée des systèmes embarqués.

# Contents

| 1 | Intro | oductio  | n                                                                             | 19 |

|---|-------|----------|-------------------------------------------------------------------------------|----|

|   | 1.1   | Safety   | and Security Concerns in IoTs/Embedded Systems                                | 19 |

|   | 1.2   | Design   | of Embedded Systems                                                           | 20 |

|   | 1.3   | Proble   | m Statement                                                                   | 21 |

|   | 1.4   | Contril  | oution of this Thesis                                                         | 22 |

|   |       | 1.4.1    | Security modeling and verification in the mapping phase                       | 22 |

|   |       | 1.4.2    | Proof of Correctness of Model Transformation for Formal Security Verification | 22 |

|   |       | 1.4.3    | Attacker Modeling                                                             | 23 |

|   |       | 1.4.4    | Latency analysis                                                              | 23 |

|   |       | 1.4.5    | Proposition of a modified SysML-Sec Methodology                               | 23 |

|   |       | 1.4.6    | Taxonomy for Safe and Secure Autonomous Vehicle Design                        | 23 |

|   | 1.5   | Organi   | zation of this Thesis                                                         | 24 |

| 2 | Con   | text: Au | itonomous Vehicles                                                            | 27 |

|   | 2.1   | Safety   | and Security Flaws                                                            | 27 |

|   |       | 2.1.1    | Safety Flaws in Commercial Vehicles                                           | 27 |

|   |       | 2.1.2    | Survey of Hacks on Connected Vehicles                                         | 28 |

|   |       | 2.1.3    | Safety Limitations of Autonomous Vehicles                                     | 29 |

|   |       | 2.1.4    | Survey of Potential Attacks on Future Autonomous Vehicles                     | 30 |

|   |       | 2.1.5    | Conclusion                                                                    | 31 |

|   | 2.2   | Approa   | aches to Vehicle Safety and Security                                          | 32 |

|   |       | 2.2.1    | Proposals for Safe and Secure Automotive and Embedded System Design           | 32 |

|   | 2.3   | Taxono   | omy                                                                           | 34 |

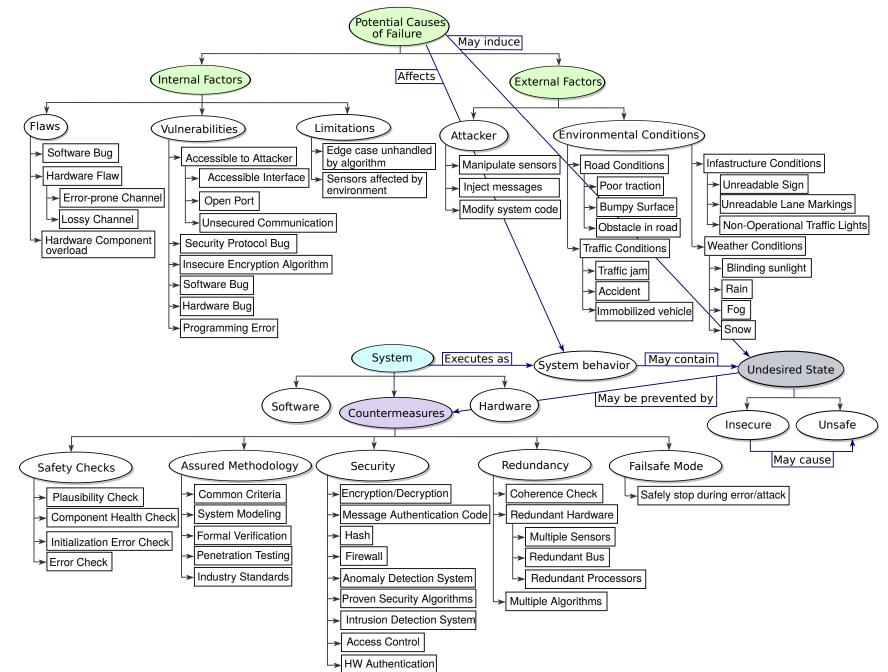

|   |       | 2.3.1    | Potential Causes of Failure                                                   | 35 |

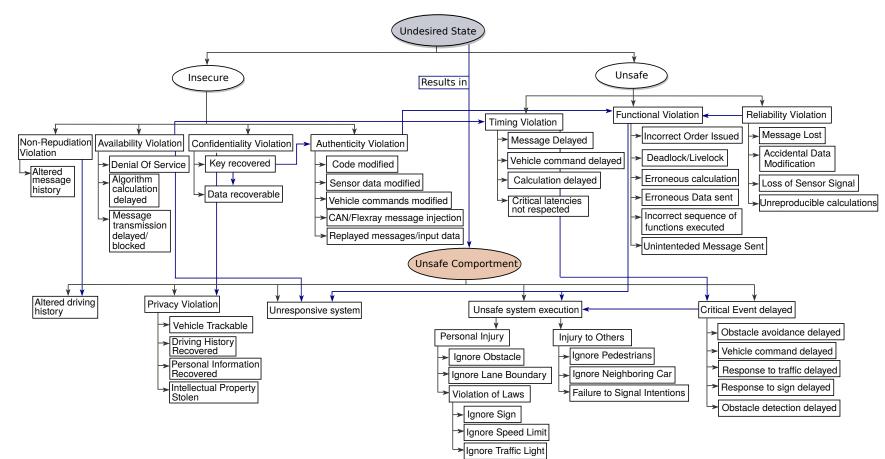

|   |       | 2.3.2    | Undesired States of System Behavior                                           | 38 |

|   |       | 2.3.3    | Unsafe Comportment                                                            | 39 |

|   |       | 2.3.4    | Countermeasures                                                               | 39 |

|   |       | 2.3.5    | Conclusion                                                                    | 39 |

|   | 2.4   |          | ermeasures                                                                    | 40 |

|   |       | 2.4.1    | Safety Countermeasures                                                        | 40 |

|   |       | 2.4.2    | Security Countermeasures                                                      | 40 |

|   |       | 2.4.3    | Secondary Effects of Countermeasures on Safety, Security, and Performance     | 42 |

|   |       | 2.4.4    | Conclusion                                                                    | 43 |

|   | 2.5   | -        | Process Requirements                                                          | 43 |

|   |       | 2.5.1    | Methodology Capabilities                                                      | 43 |

|   |       | 2.5.2    | Properties to Verify                                                          | 44 |

|   |                    | 2.5.3          | Security Properties                           |

|---|--------------------|----------------|-----------------------------------------------|

|   |                    | 2.5.4          | Conclusion                                    |

| 3 | Dolo               | ated Wor       | ·k 47                                         |

| 3 | <b>Kela</b><br>3.1 |                | re Development approaches                     |

|   | 5.1                |                |                                               |

|   |                    | 3.1.1          | 8                                             |

|   |                    | 3.1.2          |                                               |

|   | 3.2                |                | Driven Methodologies and Toolkits             |

|   |                    | 3.2.1          | Frameworks for Analysis                       |

|   |                    | 3.2.2          | Frameworks for the Design of Embedded Systems |

|   |                    | 3.2.3          | Frameworks for Software Design 56             |

|   |                    | 3.2.4          | Conclusion                                    |

| 4 | Mod                | loling M       | ethodology 61                                 |

| 4 | 4.1                | -              | ction                                         |

|   |                    |                |                                               |

|   | 4.2                |                |                                               |

|   | 4.3                | •              | is                                            |

|   |                    | 4.3.1          | Requirements                                  |

|   |                    | 4.3.2          | Attack Trees                                  |

|   |                    | 4.3.3          | Fault Trees         67                        |

|   |                    | 4.3.4          | Relationship between Analysis Phase Diagrams  |

|   | 4.4                | Design         | Phases                                        |

|   | 4.5                | HW/SV          | V Partitioning                                |

|   |                    | 4.5.1          | Application/Functional Modeling               |

|   | 4.6                | Softwar        | re Design                                     |

| 5 | Secu               | ıritv-Aw       | are HW/SW Partitioning 79                     |

|   | 5.1                | •              | tion                                          |

|   | 5.2                |                | er Model                                      |

|   | 5.3                |                | y Modeling                                    |

|   | 5.5                | 5.3.1          | Architecture Vulnerabilities                  |

|   |                    | 5.3.2          | Attacker Scenarios                            |

|   |                    | 5.3.3          |                                               |

|   |                    | 5.5.5<br>534   | 5                                             |

|   | - A                | 5.5.4          | Security Countermeasures                      |

|   | 5.4                | Conclu         | sion                                          |

| 6 | Secu               | ırity Ver      | ification 97                                  |

|   | 6.1                | Introdu        | ction                                         |

|   | 6.2                | ProVeri        | if                                            |

|   |                    | 6.2.1          | Functions                                     |

|   |                    | 6.2.2          | Declarations                                  |

|   |                    | 6.2.3          | Queries                                       |

|   |                    | 6.2.4          | Main Process         101                      |

|   |                    | 6.2.5          | Sub-processes                                 |

|   |                    | 6.2.6          | Formalizations                                |

|   |                    | 6.2.0<br>6.2.7 | DIPLODOCUS to ProVerif Translation Process    |

|   | 62                 |                |                                               |

|   | 6.3                |                | ization for Translation                       |

|   |                    | 6.3.1          | DIPLODOCUS Formalization                      |

|   |      | 6.3.2 AVATAR Formalization                                                         |

|---|------|------------------------------------------------------------------------------------|

|   | 6.4  | DIPLODOCUS to AVATAR Translation Formalization                                     |

|   |      | 6.4.1 Full DIPLODOCUS to AVATAR translation                                        |

|   |      | 6.4.2 DIPLODOCUS to AVATAR translation for Security                                |

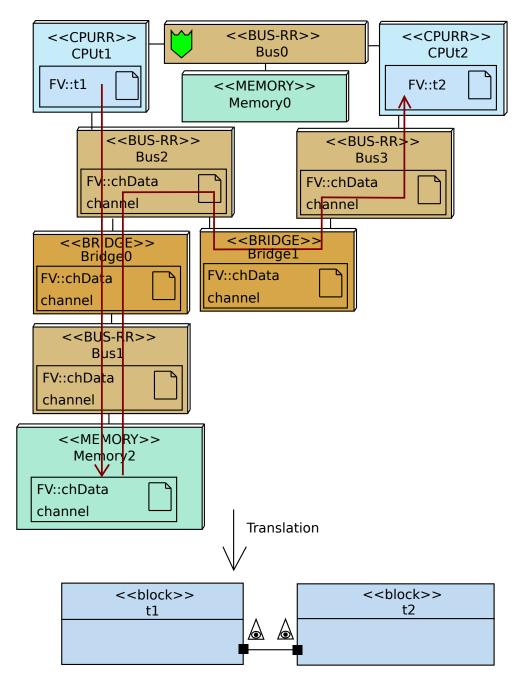

|   |      | 6.4.3 Translation of Operators                                                     |

|   | 6.5  | Translation to ProVerif                                                            |

|   |      | 6.5.1 Translation of Queries                                                       |

|   |      | 6.5.2 Translation of Tasks                                                         |

|   |      | 6.5.3 Translation of Actions                                                       |

|   | 6.6  | Proof of Correctness                                                               |

|   |      | 6.6.1 Base case                                                                    |

|   |      | 6.6.2 Inductive Step                                                               |

|   |      | 6.6.3 Conclusion                                                                   |

|   | 6.7  | ProVerif Results                                                                   |

|   | 6.8  | Automatic Generation                                                               |

|   | 0.0  | 6.8.1 Security Requirements                                                        |

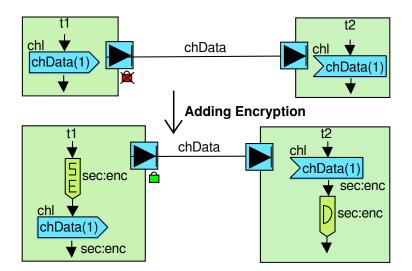

|   |      | 6.8.2 Addition of Security Operators                                               |

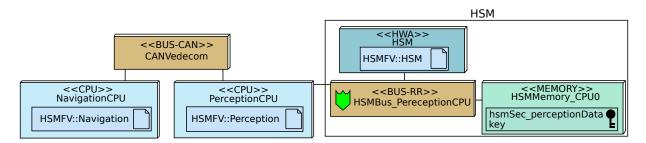

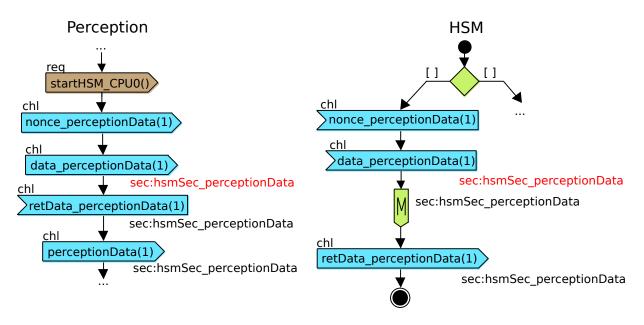

|   |      | 6.8.3 HSM Generation                                                               |

|   |      | 6.8.4         Automatic Key Mapping         112                                    |

|   |      | 6.8.5 Automatic Generation for Case Study                                          |

|   | 6.9  | Conclusion                                                                         |

|   | 0.7  |                                                                                    |

| 7 | Perf | ormance Evaluation 147                                                             |

|   | 7.1  | Introduction                                                                       |

|   | 7.2  | Latency Analysis                                                                   |

|   |      | 7.2.1 Latency Requirements                                                         |

|   |      | 7.2.2 Latency Annotations                                                          |

|   |      | 7.2.3 Latency Analysis                                                             |

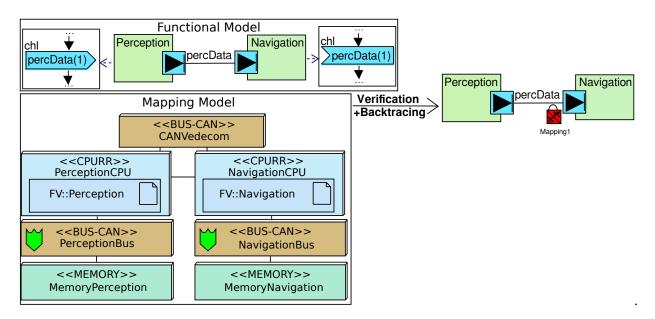

|   |      | 7.2.4 Backtracing Latencies                                                        |

|   | 7.3  | Relating Latencies across Levels of Abstraction                                    |

|   | 7.4  | Performance Impact due to adding Security                                          |

|   | 7.5  | Conclusion                                                                         |

|   |      |                                                                                    |

| 8 | Con  | clusion and Perspectives 159                                                       |

|   | 8.1  | Integration of full Safety and Security Features into Autonomous Vehicle Model 160 |

|   | 8.2  | Contributions                                                                      |

|   | 8.3  | Perspectives                                                                       |

|   |      | 8.3.1 Security for Embedded Systems in Practice                                    |

|   |      | 8.3.2 Accurate Representation of Countermeasures                                   |

|   |      | 8.3.3 Full Automatic Generation of Countermeasures                                 |

|   |      | 8.3.4 Security Modeling and Verification                                           |

|   |      | 8.3.5 Time in ProVerif                                                             |

|   |      | 8.3.6 Safety Countermeasure Modeling 166                                           |

|   |      | 8.3.7 Safety and Security Analysis Diagrams                                        |

|   |      | 8.3.8 Relationship between Safety, Security, and Performance                       |

|   |      | 8.3.9 System Resilience                                                            |

|   |      |                                                                                    |

|   |      | 8.3.10 Vulnerability Modeling                                                      |

|   |      | 8.3.11  | Improved Connections between Phases                                                  | 167 |

|---|------|---------|--------------------------------------------------------------------------------------|-----|

|   |      | 8.3.12  | Integration of Security Verification Results                                         | 167 |

|   |      | 8.3.13  | Proof of Correctness for Authenticity                                                | 167 |

|   |      | 8.3.14  | Attack Probabilities                                                                 | 167 |

| 9 | Resu | ıme     |                                                                                      | 169 |

|   | 9.1  | Introdu | lection                                                                              | 169 |

|   | 9.2  | Contex  | te                                                                                   | 171 |

|   |      | 9.2.1   | Sûreté et Sécurité des Voitures Autonomes/Connectés                                  | 171 |

|   |      | 9.2.2   | Contre-mesures proposées                                                             | 171 |

|   |      | 9.2.3   | Effets secondaires des contre-mesures pour la sûreté, la sécurité et la performance. |     |

|   |      | 9.2.4   | Travail Connexe                                                                      | 174 |

|   | 9.3  | Métho   | dologie                                                                              |     |

|   | 9.4  | Sécurit | é d'un Partitionnement Logiciel/Matériel                                             | 177 |

|   |      | 9.4.1   | Modèle d'Attaquant                                                                   | 177 |

|   |      | 9.4.2   | Modèle de Vulnérabilités                                                             | 177 |

|   |      | 9.4.3   | Scénarios d'attaque                                                                  | 178 |

|   |      | 9.4.4   | Modèle de Contre-mesures                                                             |     |

|   |      | 9.4.5   | Vérification Formelle                                                                | 180 |

|   |      | 9.4.6   | Génération Automatique de Contre-mesures                                             | 181 |

|   | 9.5  | Évalua  | tion des Performances                                                                |     |

|   |      | 9.5.1   | Mesure des Temps de Latence                                                          |     |

|   |      | 9.5.2   | Analyse de Système Sûr et Sécurisé                                                   |     |

|   | 9.6  | Conclu  | ision                                                                                |     |

|   |      | 9.6.1   | Contributions                                                                        |     |

|   |      | 9.6.2   | Perspectives                                                                         |     |

|   |      |         |                                                                                      |     |

#### Bibliography

# **List of Figures**

| 1-1  | Vedecom Autonomous Car                                                                  | 24  |

|------|-----------------------------------------------------------------------------------------|-----|

| 2-1  | Taxonomy Overview showing how Internal and External Factors can result in Unsafe Com-   |     |

|      | portment                                                                                | 35  |

| 2-2  | Taxonomy for Autonomous Vehicles Part 1                                                 | 36  |

| 2-3  | Taxonomy for Autonomous Vehicles Part 2                                                 | 37  |

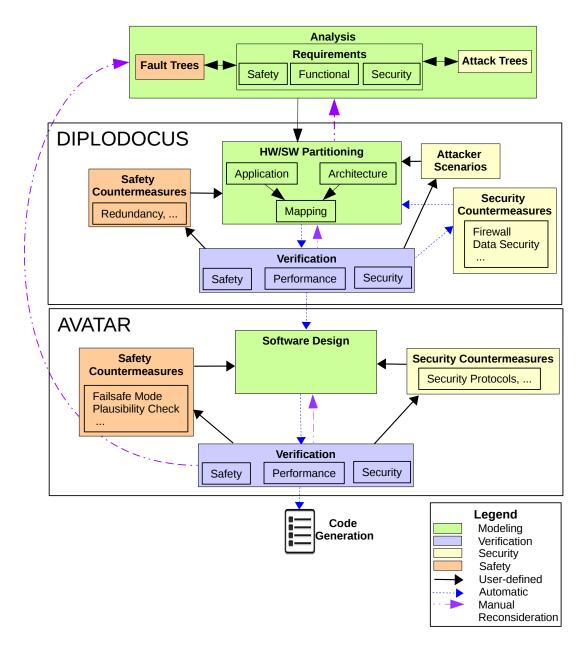

| 4-1  | Overview of SysML-Sec Methodology for the Design of Safe and Secure Embedded Systems    | 64  |

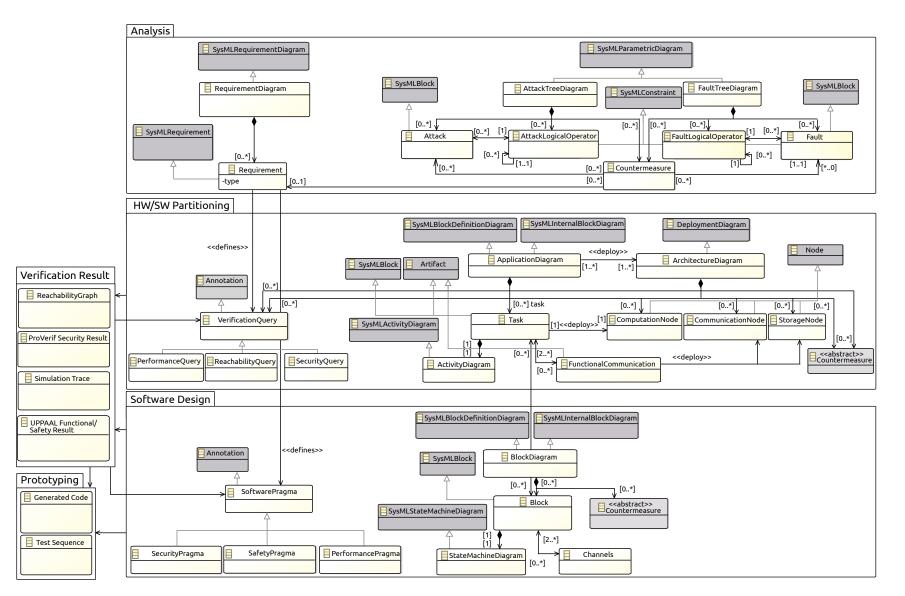

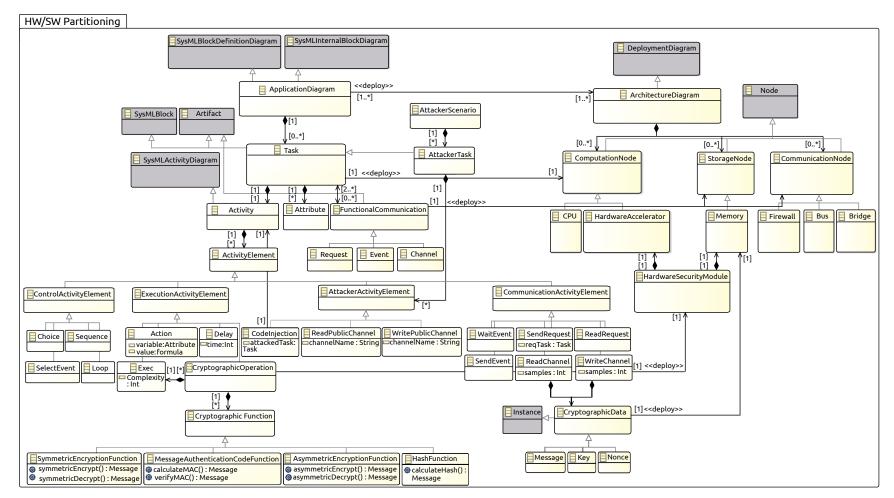

| 4-2  | Metamodel of Diagrams for SysML-Sec Methodology                                         | 65  |

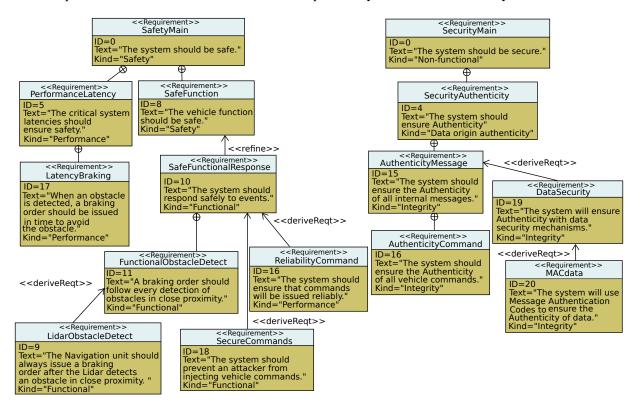

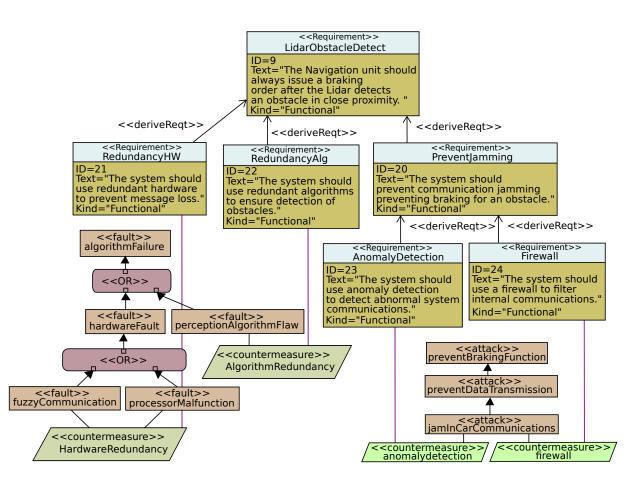

| 4-3  | Refinement of Requirements for Vehicle Safety and Security                              | 66  |

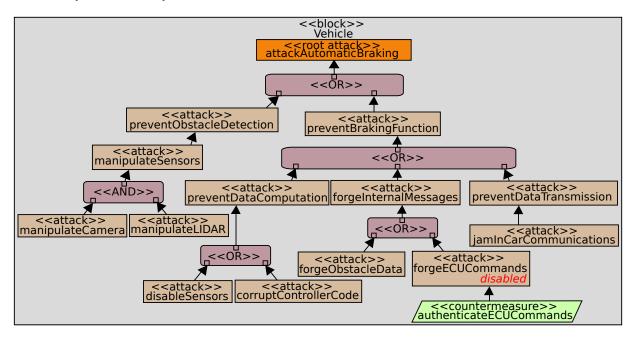

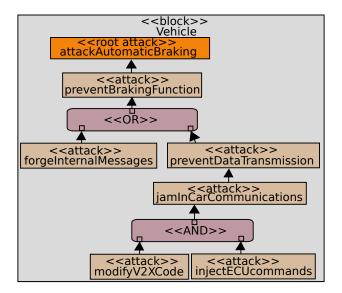

| 4-4  | Attack Tree for Obstacle Detection Failure                                              | 68  |

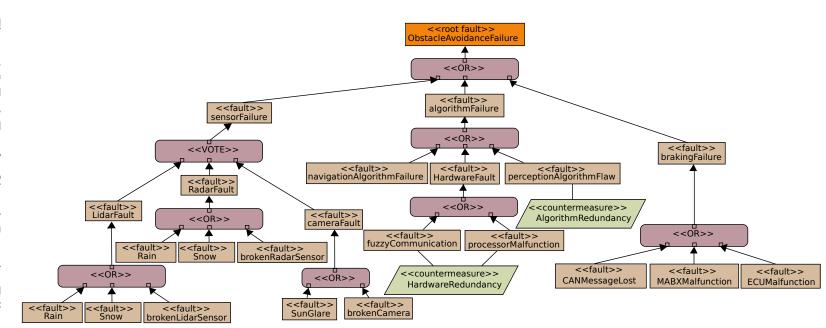

| 4-5  | Fault Tree for Obstacle Detection Failure                                               | 69  |

| 4-6  | Linking Attack and Fault Trees into Requirement Diagram                                 | 70  |

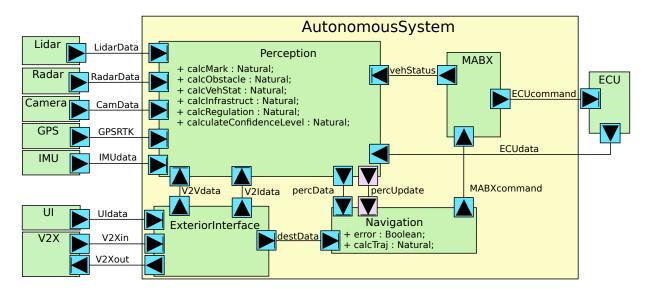

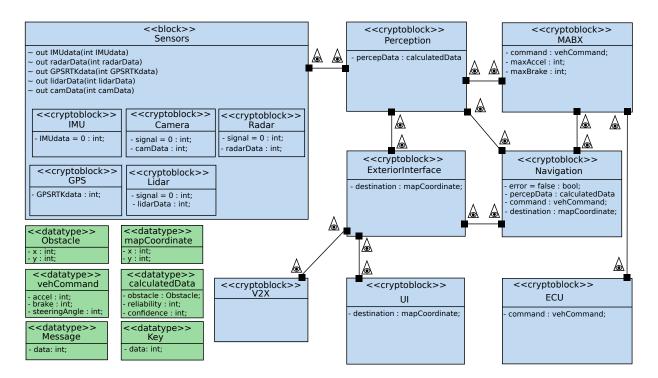

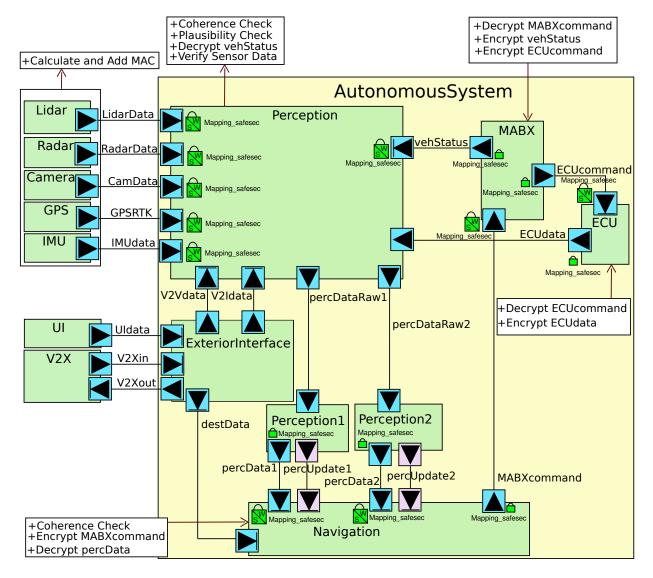

| 4-7  | Application Model for Autonomous Vehicle                                                | 72  |

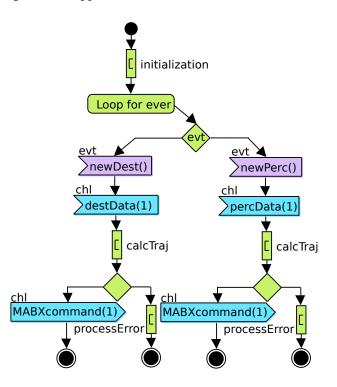

| 4-8  | Activity Diagram for Navigation in Autonomous Vehicle                                   | 72  |

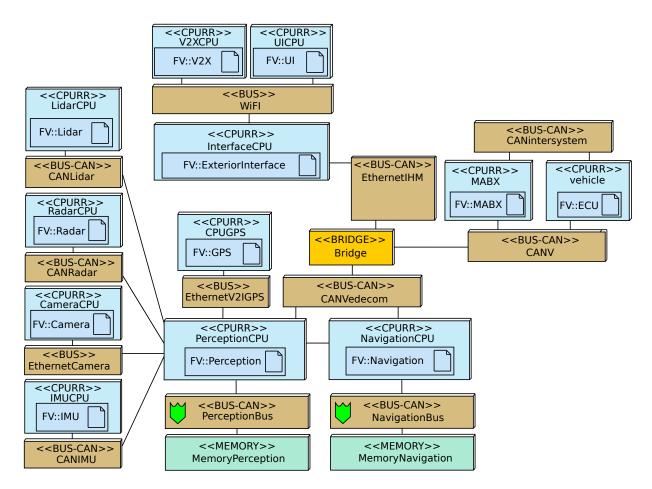

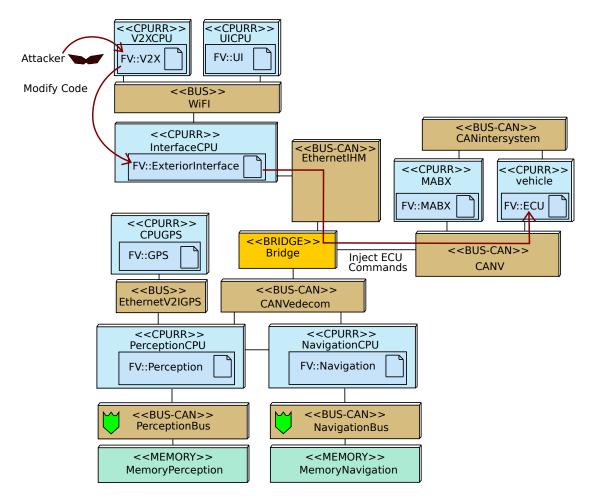

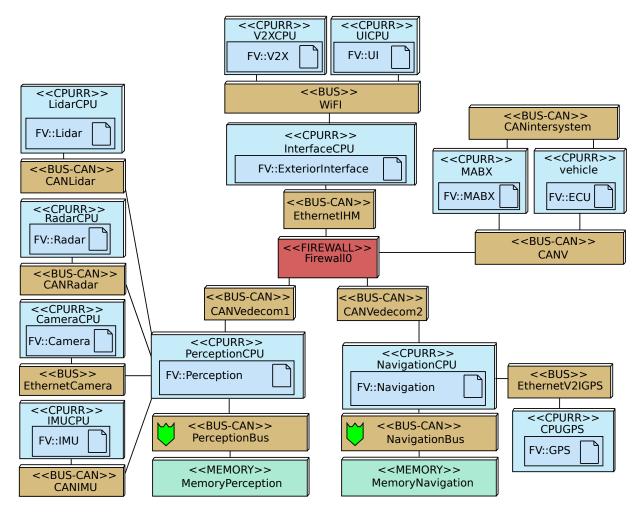

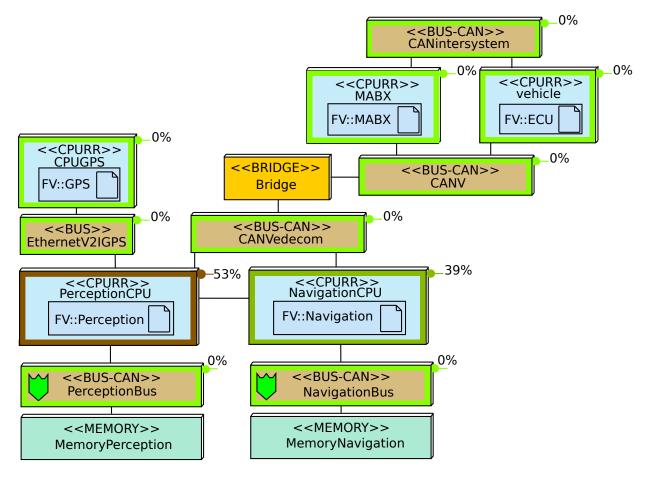

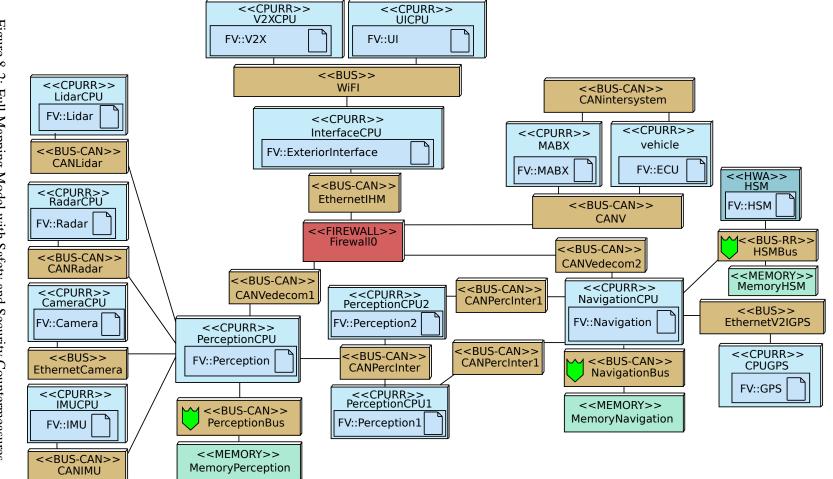

| 4-9  | Architecture/Mapping Model for Autonomous Car                                           | 73  |

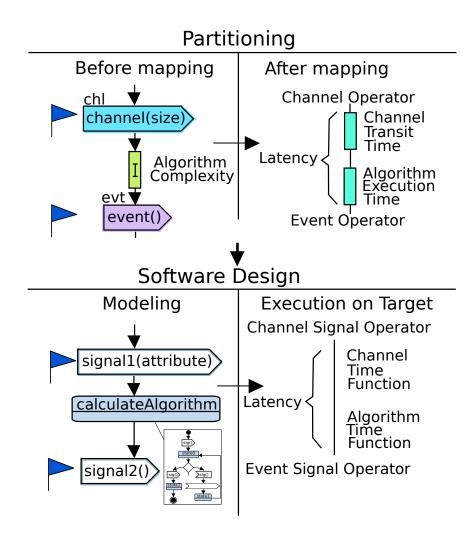

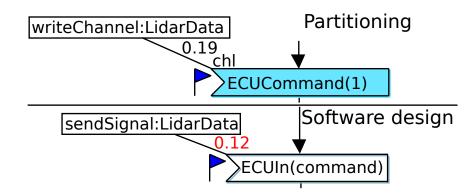

| 4-10 |                                                                                         | 75  |

| 4-11 | State Machine Diagram refined from HW/SW Partitioning Activity Diagram                  | 77  |

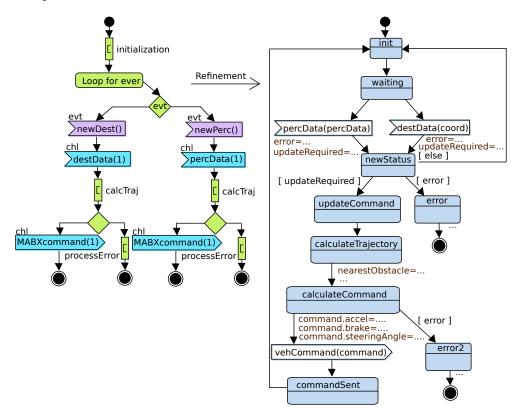

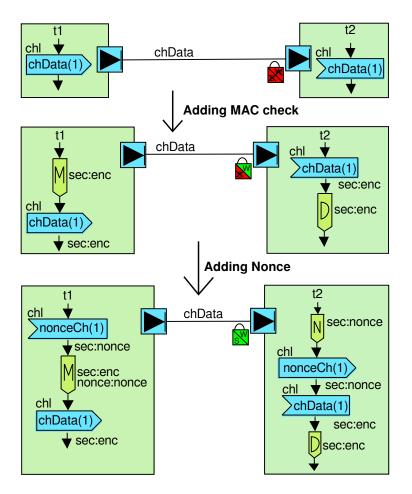

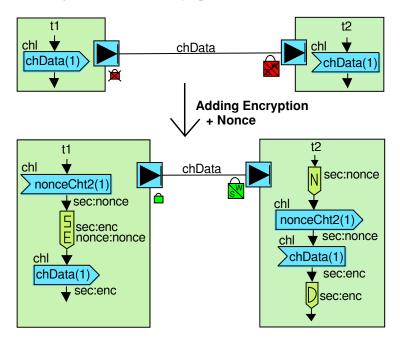

| 5-1  | Fixing Security Flaws across levels of abstraction                                      | 81  |

| 5-2  | Modeling data security without dedicated operators                                      | 81  |

| 5-3  | Security Modeling Metamodel                                                             | 83  |

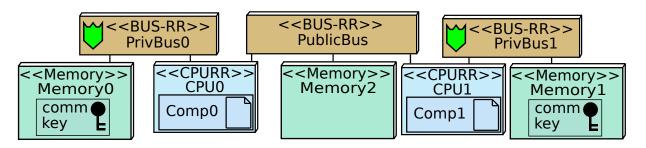

| 5-4  | Sample Architecture with Insecure Bus                                                   | 84  |

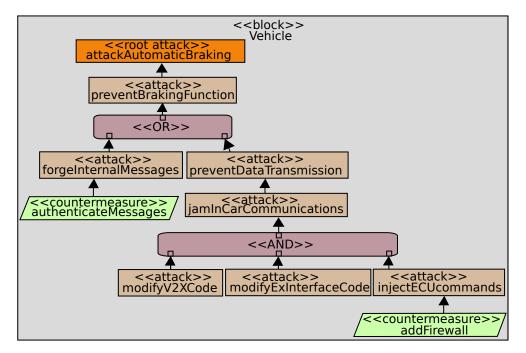

| 5-5  | Extract of Attack Tree for Attacker Scenario Model                                      | 85  |

| 5-6  | Attacker Scenario execution on hardware                                                 | 85  |

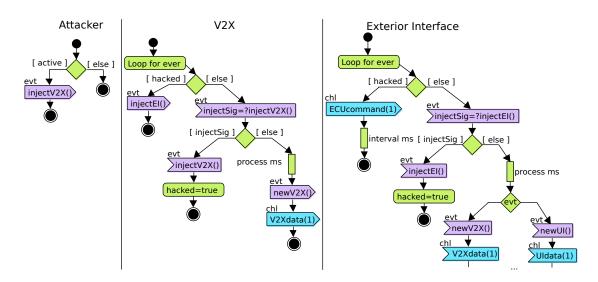

| 5-7  | Activity Diagrams of components in Attacker Scenario                                    | 86  |

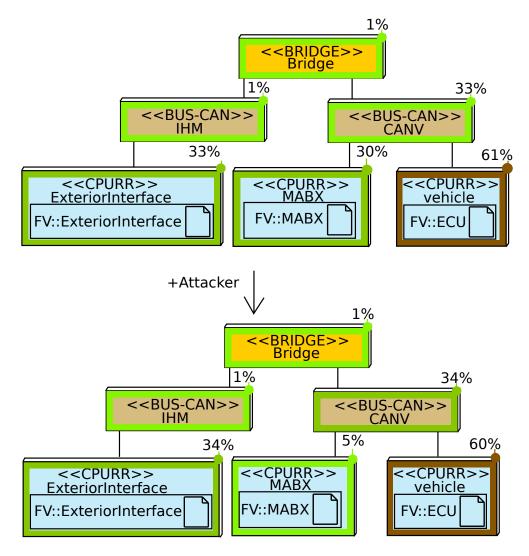

| 5-8  | Performance impact due to Addition of Attacker                                          | 87  |

| 5-9  | Specification of Cryptographic Configuration for Asymmetric Encryption and Decryption . | 88  |

| 5-10 | HSM in Architecture Diagram                                                             | 89  |

| 5-11 | Perception and HSM Activity Diagram                                                     | 90  |

|      | Firewall added to Architecture Diagram                                                  | 91  |

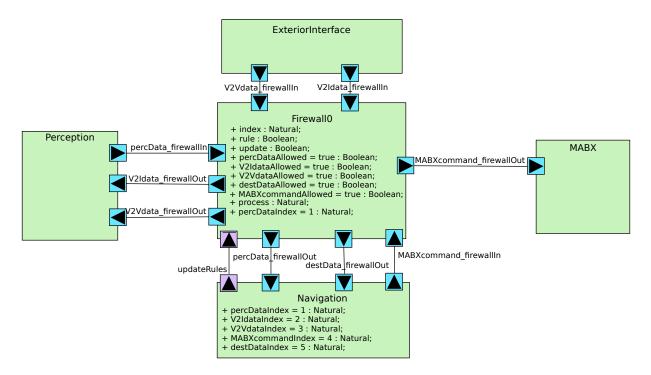

|      | Component Diagram with Firewall                                                         | 92  |

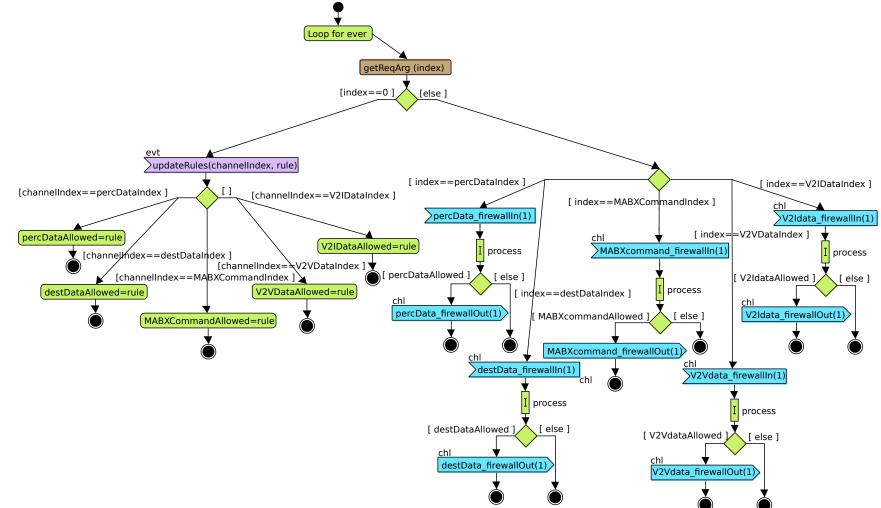

|      | Firewall Activity Diagram                                                               | 93  |

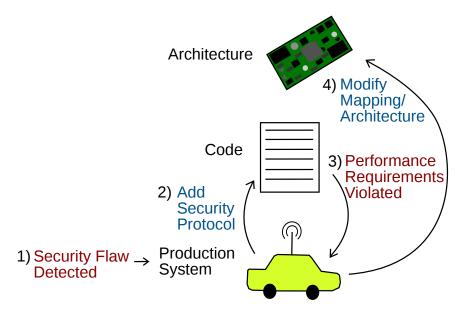

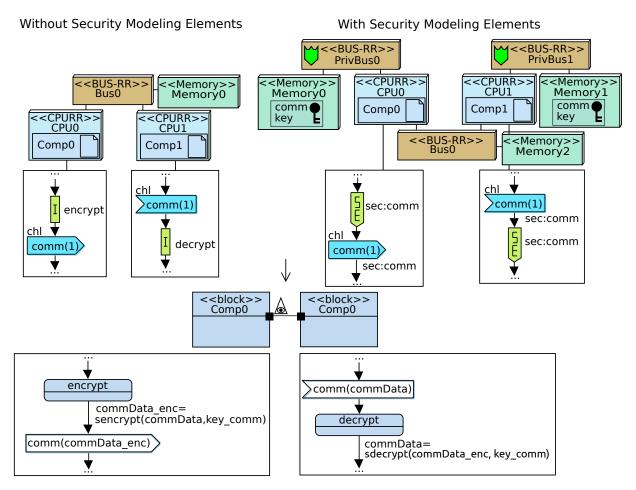

|      | Mapping Model with and without dedicated Security Operators                             | 94  |

|      | Modified Attack Tree with Countermeasures Added                                         | 95  |

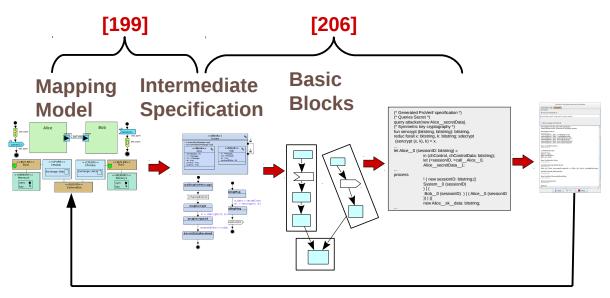

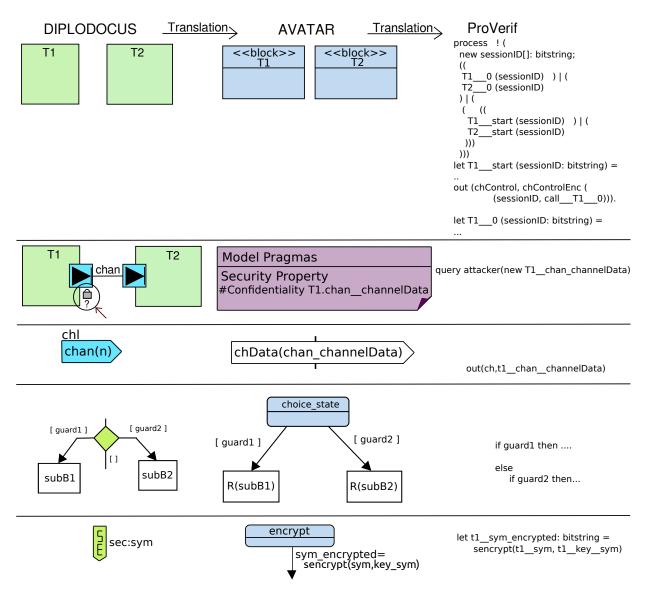

| 6-1  | DIPLODOCUS to ProVerif Translation process                                              | 103 |

| 6-2  | Functional Model Communication Behavior Formalization                                   |     |

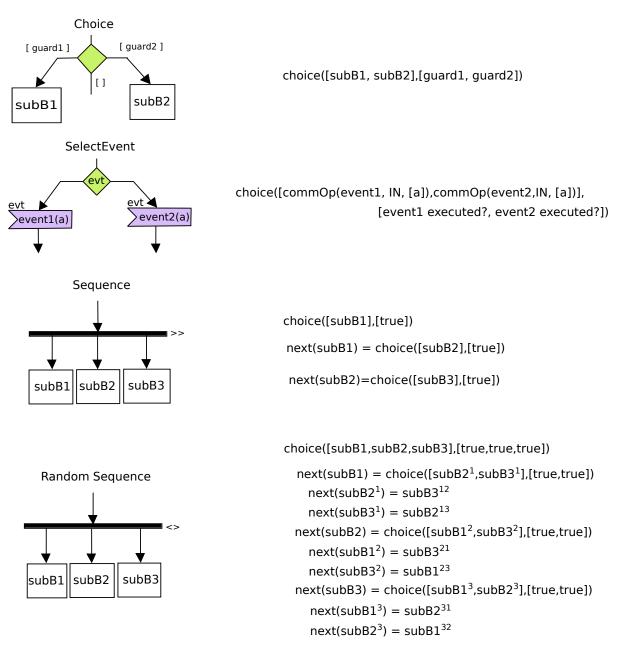

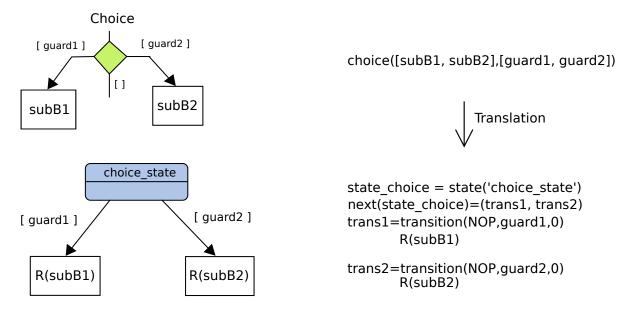

| 6-3        | Functional Model Choice Behavior Formalization                                              |

|------------|---------------------------------------------------------------------------------------------|

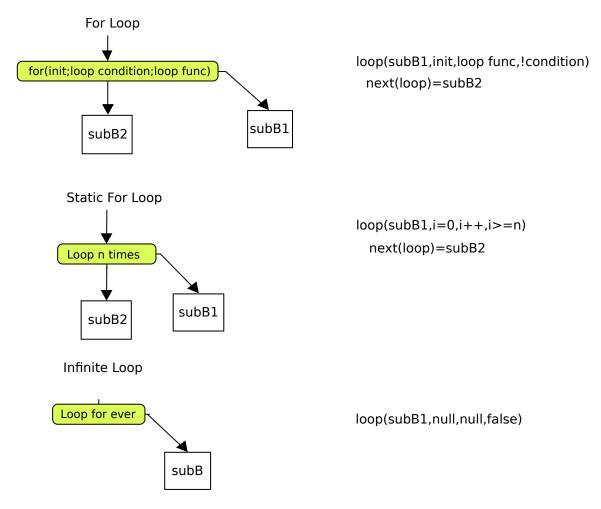

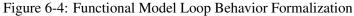

| 6-4        | Functional Model Loop Behavior Formalization                                                |

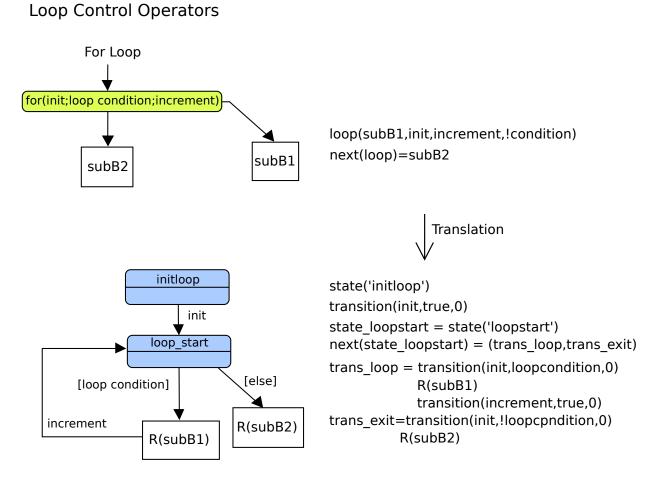

| 6-5        | Functional Model Complexity Behavior Formalization                                          |

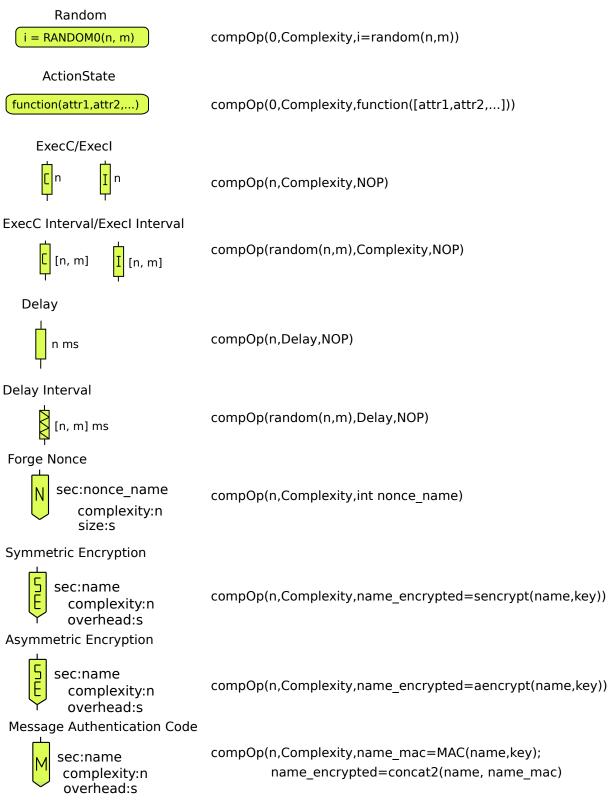

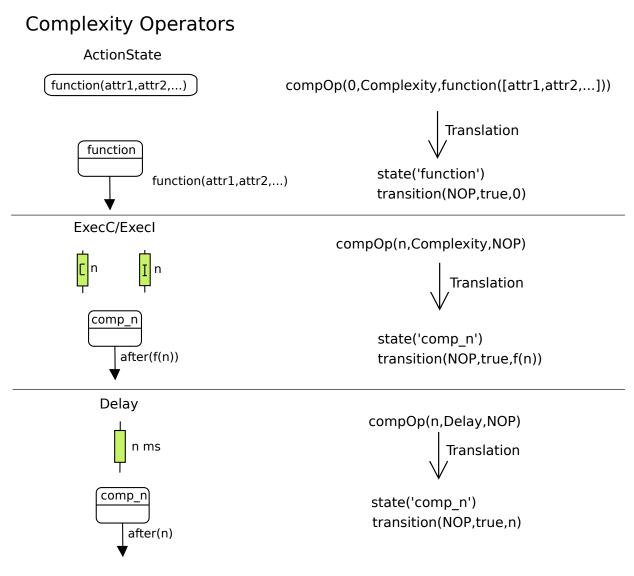

| 6-6        | Avatar Behavior Formalization                                                               |

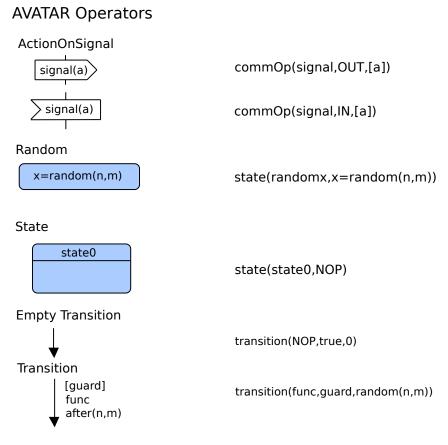

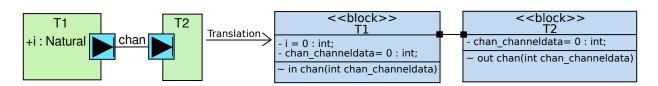

| 6-7        | Translation of Functional Communications to Software Design Communications 113              |

| 6-8        | Translation of DIPLODOCUS Tasks and Associated Attributes and Communications to             |

|            | AVATAR                                                                                      |

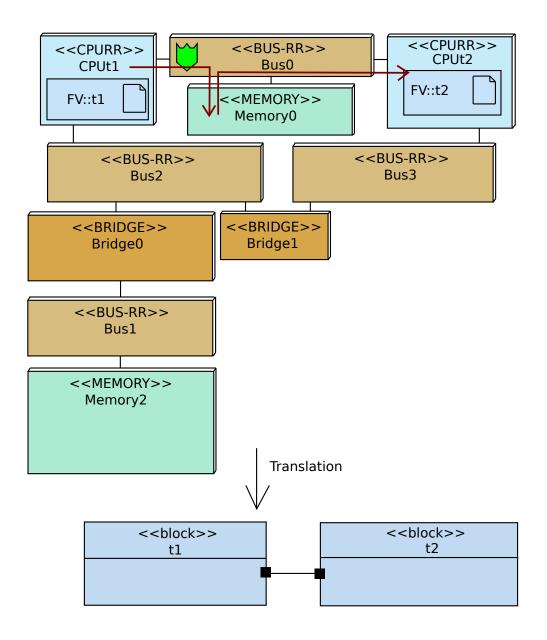

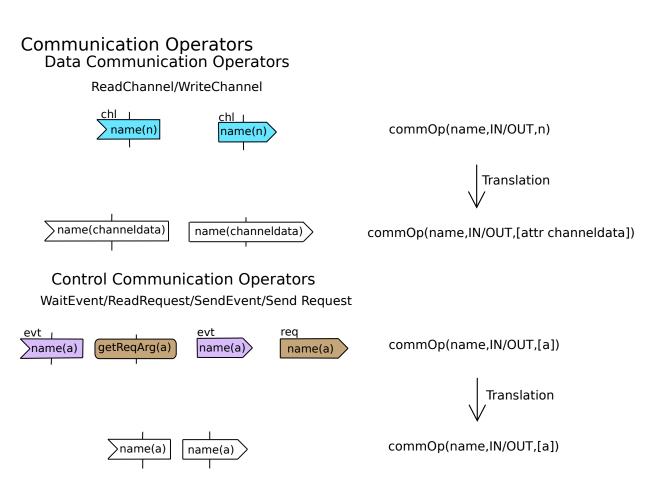

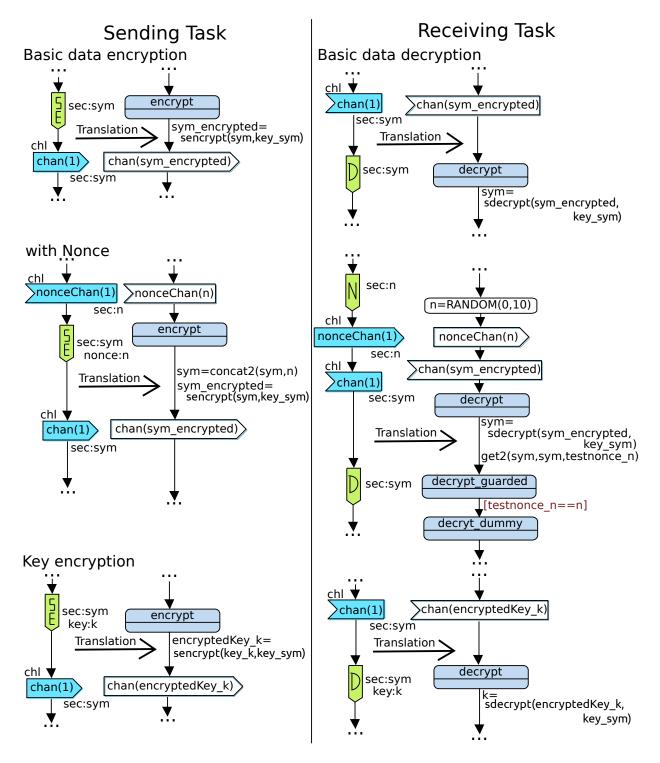

| 6-9        | Translation of Security of Channels - Secure Communication Mapping                          |

|            | Translation of Security of Channels - Insecure Communication Mapping                        |

|            | Translation of Functional Communication Behavior Elements to Software Design Behav-         |

| 0 11       | ior Elements                                                                                |

| 6-12       | Translation of Functional Choice Behavior Elements to Software Design Behavior Elements 119 |

|            | Translation of Functional Loop Behavior Elements to Software Design Behavior Elements 120   |

|            | Translation of Functional Complexity Behavior Elements to Software Design Behavior          |

| 0-14       | Elements                                                                                    |

| 6-15       | Translation of Symmetric Encryption Behavior Elements to Software Design Behavior           |

| 0-15       | Elements                                                                                    |

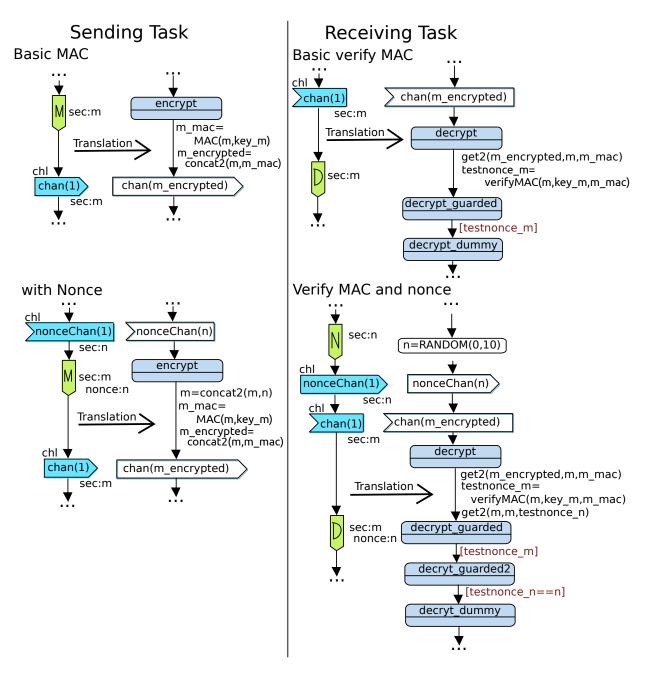

| 6 16       | Translation of MAC Cryptographic Configuration to Software Design Behavior 123              |

|            |                                                                                             |

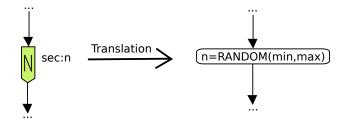

|            | Translation of Nonce Cryptographic Configuration to Software Design Behavior                |

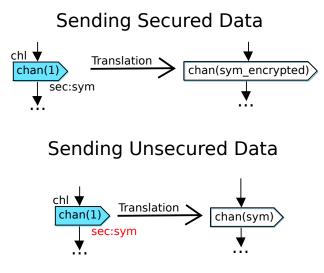

|            | Translation of Sending Secured vs Unsecured Data to Software Design Behavior 124            |

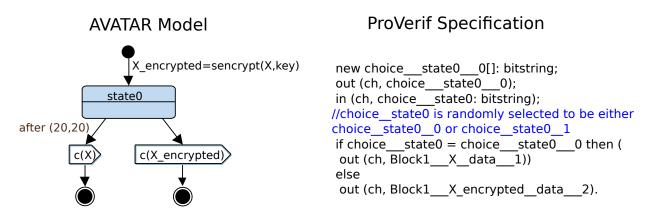

|            | Translation of DIPLODOCUS to AVATAR to ProVerif                                             |

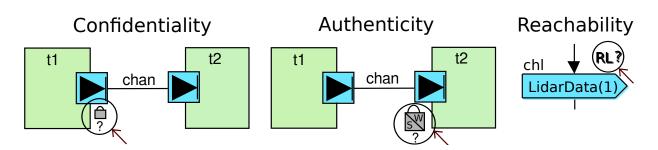

|            | Confidentiality, Authenticity, and Reachability Security Annotations                        |

|            | ProVerif Verification Results Output                                                        |

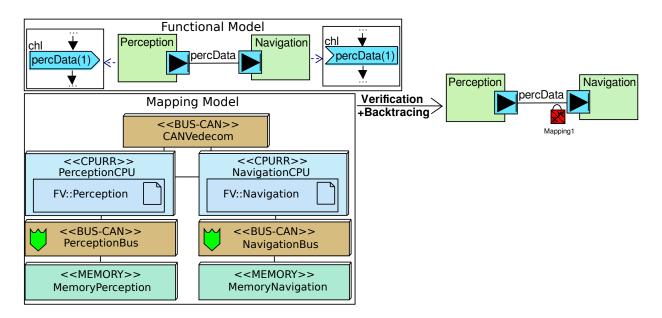

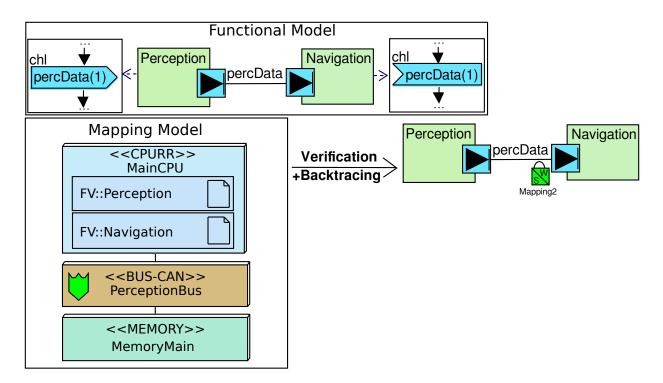

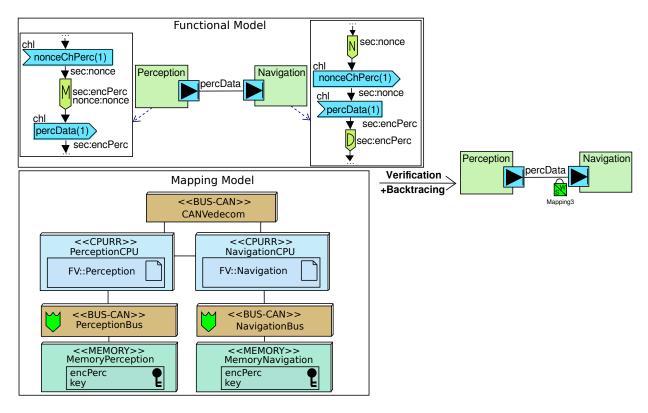

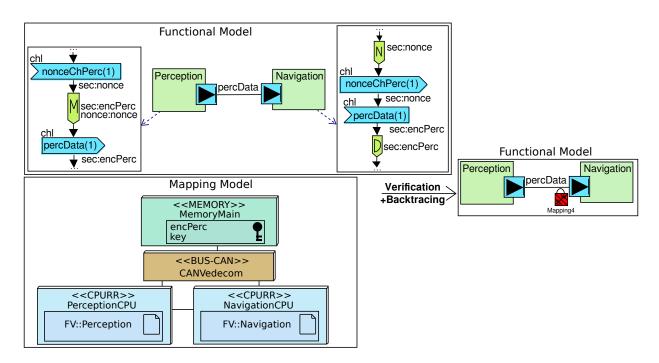

|            | Verification Results for Default Mapping                                                    |

| 6-23       | Verification Results for Modified Mapping with Perception and Navigation Tasks mapped       |

|            | to same CPU                                                                                 |

|            | Window for Automatic generation of security                                                 |

|            | Automatic generation of security operators to ensure confidentiality                        |

|            | Automatic generation of security operators to ensure Weak and Strong Authenticity 141       |

|            | Automatic generation of security operators to ensure Confidentiality and Authenticity 141   |

|            | Verification Results for Mapping with Security Operators added                              |

| 6-29       | Verification Results for Mapping with Security Operators and Insecure Memory Access 144     |

| 7-1        | Mapping Operators tagged with Latency Checkpoints                                           |

| 7-2        | Software Design Operators tagged with Latency Checkpoints                                   |

| 7-3        | Latency Measurement Panel                                                                   |

| 7-4        | Mapping Operator marked with latency measurement and linked Requirement 152                 |

| 7-5        | Performance Pragma with Latency results                                                     |

| 7-6        | Latencies across Mapping vs Software Design                                                 |

| , o<br>7-7 | Incoherence detected in latency measured between HW/SW Partitioning and Software De-        |

| /-/        | sign                                                                                        |

| 7-8        | Performance results for Mapping 1                                                           |

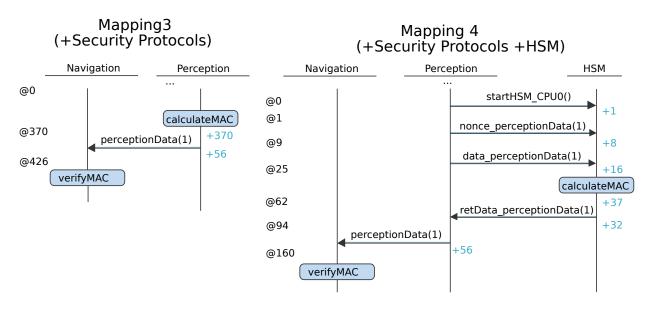

| 7-9        | Simulation Trace for Performing Security Operations in Perception task or HSM 157           |

|            |                                                                                             |

| 8-1        | Full Application Model with Safety and Security Countermeasures                             |

| 8-2        | Full Mapping Model with Safety and Security Countermeasures                                 |

| 8-3        | AVATAR Model translated incorrectly to ProVerif due to removal of time 165                  |

| 9-1 | SysML-Sec Méthodologie pour la Conception de Systèmes Embarqués Sûrs et Sécurisés .       | 176 |

|-----|-------------------------------------------------------------------------------------------|-----|

| 9-2 | Spécification de la "Cryptographic Configuration" pour le Chiffrement et le Déchiffrement |     |

|     | Asymétrique                                                                               | 179 |

| 9-3 | Résultats de vérification pour l'allocation par défaut                                    | 181 |

# **List of Tables**

| 2.1 | Table of Hazards of Autonomous/Connected Vehicles    31                   |

|-----|---------------------------------------------------------------------------|

| 2.2 | Table of Countermeasures    41                                            |

| 2.3 | Impact on Safety, Security, and Performance of Countermeasures            |

| 3.1 | Comparison of Related Works                                               |

| 7.1 | Performance Results over Mappings                                         |

| 8.1 | Performance Results Comparison of Default vs Safe and Secured Mapping 163 |

|     | Tableau de Risques dans les Voitures Autonomes/Connectées       172       |

| 9.2 | Résultats de Performance                                                  |

# **List of Abbreviations**

| AADL       | Architecture Analysis & Design Language                                         |

|------------|---------------------------------------------------------------------------------|

| AES        | Advanced Encryption Standard                                                    |

| API        | Application Programming Interface                                               |

| ASIC       | Application-Specific Integrated Circuit                                         |

| AVATAR     | Automated Verification of reAl Time softwARe.                                   |

| BDMP       | Boolean Logic Driven Markov Processes                                           |

| CAN        | Controller Area Network                                                         |

| CFT        | Component Fault Tree                                                            |

| CPU        | Central Processing Unit                                                         |

| DIPLODOCUS | DesIgn sPace exLoration based on fOrmal Description teChniques, Uml and SystemC |

| DSE        | Design Space Exploration                                                        |

| ECC        | Elliptic-Curve Cryptography                                                     |

| ECU        | Electronic Control Unit                                                         |

| EVITA      | E-safety vehicle intrusion protected applications (project)                     |

| FIFO       | First In First Out                                                              |

| FMVEA      | Failure Mode, Vulnerabilities and Effect Analysis                               |

| FPGA       | Field-Programmable Gate Array                                                   |

| GPS        | Global Positioning System                                                       |

| HAZOP      | HAZard and OPerability                                                          |

| HSM        | Hardware Security Module                                                        |

| HW/SW      | Hardware/Software                                                               |

| IoT        | Internet of Things                                                              |

| ISO        | International Organization for Standardization                                  |

| LIDAR      | Light Detection and Ranging                                                     |

| MABX       | Micro Auto Box                                                                  |

| MAC        | Message Authentication Code                                                     |

| MARTE      | Modeling and Analysis of Real Time and Embedded Systems                         |

| MCS        | Minimum Cut Set                                                                 |

| MDE        | Model-Driven Engineering                                                        |

| OBD        | On-board Diagnostics                                                            |

| NOP        | No operation                                                                    |

| OCL        | Object Constraint Language                                                      |

| RSA        | Rivest Shamir Adleman (algorithm)                                               |

| SMOLES     | Simple Modeling Language for Embedded Systems                                   |

| SOTIF      | Safety of the Intended Function                                                 |

| STPA       | Systems Theoretic Process Analysis                                              |

| SysML | Systems Modeling Language           |

|-------|-------------------------------------|

| TCU   | Telematic Control Unit              |

| TDMA  | Time-Division Multiple Access       |

| TPM   | Trusted Platform Module             |

| UML   | Unified Modeling Language           |

| VANET | Vehicular Ad hoc NETworks           |

| V2I   | Vehicle-to-Infrastructure           |

| V2V   | Vehicle-to-Vehicle                  |

| V2X   | Vehicle-to-Everything               |

| VHDL  | VHSIC Hardware Description Language |

| VIN   | Vehicle Identification Number       |

## **List of Publications**

#### **International Journals**

- Letitia W. Li, Daniela Genius, and Ludovic Apvrille. **Formal and Virtual Multi-level Design Space Exploration.** *International Conference on Model-Driven Engineering and Software Development.* Springer, 2017. (Accepted)

#### **Book Chapters**

- [16] Ludovic Apvrille and Letitia W. Li. Safe and Secure Support for Public Safety Networks. *Wireless Public Safety Networks 3*, Elsevier, ed. Daniel Camara and Navid Nikaein, pp 185 - 210, 2017

#### **National Journals**

- Ludovic Apvrille and Letitia Li. Security Concerns of Connected and/or Autonomous Vehicles. *MISC* (87) (Sep/Oct 2016) (in French)

#### **Conference Papers**

- [203] Letitia W. Li, Florian Lugou, and Ludovic Apvrille. **Evolving Attacker Perspectives for Secure Embedded System Design.** *Conference on Model-Driven Engineering and Software Development* (*Modelsward*'2018). Funchal, Portugal (Jan 2018)

- [119] Daniela Genius, Letitia W. Li, and Ludovic Apvrille. Multi-level Latency Evaluation with an MDE Approach. Conference on Model-Driven Engineering and Software Development (Model-sward'2018). Funchal, Portugal (Jan 2018)

- [202] Letitia W. Li, Florian Lugou, and Ludovic Apvrille. **Security Modeling for Embedded System Design.** *Fourth International Workshop on Graphical Models for Security*. Santa Barbara, CA, USA (Aug 2017).

- [200] Letitia W. Li, Ludovic Apvrille, and Annie Bracquemond. **Design and Verification of Secure Autonomous Vehicles.** *Intelligent Transport Systems.* Strasbourg, France (June 2017).

- [201] Letitia W. Li, Florian Lugou, and Ludovic Apvrille. Security-Aware Modeling and Analysis for HW/SW Partitioning. *Conference on Model-Driven Engineering and Software Development (Modelsward*'2017). Porto, Portugal (Feb 2017)

- [118] Daniela Genius, Letitia W. Li, and Ludovic Apvrille. **Model-Driven Performance Evaluation** and Formal Verification for Multi-level Embedded System Design. *Conference on Model-Driven Engineering and Software Development (Modelsward'2017)*. Porto, Portugal (Feb 2017) - Letitia Li, Ludovic Apvrille, and Daniela Genius. Virtual Prototyping of Automotive Systems: Towards Multi-level Design Space Exploration. Conference on Design and Architectures for Signal and Image Processing (2016)

- Ludovic Apvrille, Letitia Li, and Yves Roudier. **Model-Driven Engineering for Designing Safe and Secure Embedded Systems.** *Architecture-Centric Virtual Integration (ACVI)*. pp. 4–7. IEEE (2016)

- [209] Florian Lugou, Letitia W. Li, and Ludovic Apvrille, Ameur-Boulifa, Rabea. **SysML Models and Model Transformation for Security.** *Conference on Model-Driven Engineering and Software Development (Modelsward'2016).* Rome, Italy (Feb 2016)

#### **Under Review**

- Letitia W. Li, Florian Lugou, Ludovic Apvrille, and Annie Bracquemond. Model-Driven Design for Safe and Secure Embedded Systems. *Under review*

### Chapter 1

### Introduction

"The best thing for being sad," replied Merlin, beginning to puff and blow, "is to learn something. That's the only thing that never fails. You may grow old and trembling in your anatomies, you may lie awake at night listening to the disorder of your veins, you may miss your only love, you may see the world about you devastated by evil lunatics, or know your honour trampled in the sewers of baser minds. There is only one thing for it then - to learn. Learn why the world wags and what wags it. That is the only thing which the mind can never exhaust, never alienate, never be tortured by, never fear or distrust, and never dream of regretting. Learning is the only thing for you. Look what a lot of things there are to learn." –T.H. White, The Once and Future King

Communicating embedded systems/IoTs, are becoming increasingly prevalent in our daily lives [96]. These systems with both hardware and software components, contain a computer 'embedded' into the device, and are designed to perform a single dedicated function [25]. The omnipresent connectivity in these objects has improved our daily lives, from adding conveniences by allowing us to track appliances (such as fridges, detectors, etc) [263], adding conveniences and improving safety in our daily commutes (internet connectivity, car monitoring, emergency braking, etc) [342], monitoring our personal health (fitbits, glucose monitors) [77] or of children (Mimo, trackers) [277], to helping medical professionals with menial tasks, monitoring patients or administering treatment (delivery robot, insulin delivery, etc) [314]. For all the benefits due to these connected devices, malfunctions may lead to grave impacts on personal privacy or safety.

#### 1.1 Safety and Security Concerns in IoTs/Embedded Systems

Radiation therapy machines should help treat cancer, but the software bugs within the Therac-25 machine caused malfunctions which sickened or killed 6 patients from 1985 - 1986 [198], and the Cobalt-60 radiation machine sickened or killed 28 patients in 2000 [121]. The Nest Protect smoke and carbon monoxide detector could be turned off easily and unintentionally, and possibly fail to warn users of dangerous situations [6]. Numerous products have been recalled due to the ability to catch fire, such as hoverboards, smartphones, and children's fitness monitors [176]. Security flaws have also been found on medical appliances, such as the Hospira Symbiq drug pump [153]. Researchers have demonstrated how to gain control

of connected cars through cellular connectivity and wifi [67, 223], and drones through an insecure remote connection [268]. Attacks have also targeted important industrial systems, as demonstrated by the Stuxnet, Flame, and Duqu [219] attacks. All of these examples demonstrate the safety risks posed by flaws or vulnerabilities in connected embedded systems.

Safety is defined as avoidance of situations which can cause losses such as personal injury, illness, property damage, monetary damage, etc [197]. A system should be free of faults, which are defined as undesired system states due to either incorrect commands or the absence of the correct command, or a failure, which is defined as the inability of the system or system element to perform its intended function [62]. In our context, we divide system safety into multiple aspects: conventional safety involves avoiding malfunctions resulting in losses, such as the race conditions within the Therac-25 machine that could cause a fatal dose of radiation to be occasionally administered to patients, and safety of the intended functionality involves avoiding losses due to environmental conditions even in a system without faults, such as malfunctioning sensors in adverse weather conditions [31, 154, 198].

Real-time systems involve software continuously controlling physical components which operate within timing constraints for correct function [123]. In certain real-time systems, performance can also be critical to safety [64, 243]. Critical events should not be delayed due to bus or processor contention, as such delays can lead to potentially unsafe situations or inability to avoid possible damages to the system or users [9, 191].

Furthermore, the safety of a system depends on its security. According to security researcher Charlie Miller, who demonstrated the remote hack of a Jeep through the cellular network, "You cannot have safety without security" [128]. Even if a system was designed to be completely safe, should a hacker gain access to the system, he/she might be able to change the functionality entirely to one which ignores all safety controls.

#### **1.2 Design of Embedded Systems**

The design of safety-critical embedded systems is complicated by their many requirements, and the presence of both hardware and software components [145]. Not only must we assure that the system will always behave safely and is protected against attackers, we must also consider the real-time performance for timing-critical devices, memory, device lifetime, the cost and size of the architecture, reliability, and power consumption as many of these devices have limited battery life [25, 184].

Designing secure systems is complicated by the lack of security expertise in developers [20,284,306], and the fact that security mechanisms are often added as an afterthought [98]. At the same time, designing safe systems is complicated by the need to ensure both the software's functional correctness in a variety of environments, and the ability of the hardware to support that software function [144].

Many solutions to ensuring safety and security have been proposed, such as modeling, testing, various methodologies, and following rigorously discussed industry standards. While many safety and security standards exist [287], they are written in text, and it is uncertain if the designer has taken them into account, where quantitative verification is more formalized and uses objective analysis [275]. Formal and semi-formal specifications can be less ambiguous, and better support finding errors and translations for simulation/analysis [28]. Tools can check if formal requirements are consistent and complete as an ensemble, and also automatically check the satisfaction of some types of requirements [238]. We propose

that we can directly analyze if each standard is fulfilled if they are written as requirements that are refined until they can be directly tested (i.e. latency < value). To allow for objective evaluation, we must test a mathematical statement rather than a high-level idea such as "safety should be a consideration".

One solution, systematic modeling and formal verification, can help detect flaws earlier, specify the system, and better analyze the overall system, which individual tests cannot do [290]. Fixing software flaws earlier in the design process costs less than after mass production [137]. Formal verification and simulation can be performed on the more abstract models to validate the design [91], as full systems can be too large to model and take too long to verify, often described as the state explosion problem [61]. Designers then iteratively refine abstract models until the models include all important details [340]. Final models can then be automatically translated into generated code [192, 331], which ensures that the system and models correlate, and eases the software development process [290].

Graphical modeling languages, such as UML are also found to be more 'human-friendly', and easier to understand [291]. A supporting modeling tool should ease modeling and verification efforts, save time by demonstrating good user interface design, and perform automatic verification to clearly present the flaws in the model to the designer [114, 235]. Poor user interface may fail to indicate problems to the user, or provide misleading information. For example, in 1988, the USS Vincennes mistakenly shot down a civilian plane it thought to be hostile partially due to receiving measurements from a different plane and failure to determine if the plane was descending towards the ship to attack, mistakes which can be blamed on a difficult-to-use and uninformative user interface [301]. In the 1989 airplane crash at Kegsworth, the pilots failed to determine which engine was malfunctioning, and then shut down the functioning engine, partially due to a difficult-to-read indicator [43]. While modeling software cannot cause such catastrophic damage, it is still important to ensure our tool provides the correct information in a clear manner to the user to best facilitate the generation of correct designs meeting desired specifications.

#### **1.3 Problem Statement**

My thesis, sponsored by Institut Vedecom, the French research institute for the development of sustainable and autonomous vehicles, investigates how to design safe and secure embedded systems. The design of their autonomous vehicle must take into account a multitude of requirements, especially the safety of the occupants and other bystanders. One of the critical stages of development is to decide on the high-level hardware and software, and the mapping of software to hardware (determining the hardware components where functions are executed) [217, 236, 316].

As presented in this thesis, there exist various design methodologies and tools, each which focus on certain aspects of design or specific domains, but none that support all of the necessary verification tools and handle the security modeling required, especially during selection of an architecture and mapping. We therefore evolve the SysML-Sec Methodology and supporting toolkit TTool to better address these needs [13, 15]. As an advantage of our approach, keeping the entire modeling within a single toolkit better ensures that there is only one set of models, and minimizes the amount of rework at each change [157]. At the same time, we ensure the ease-of-use of our toolkit, an essential quality to ensuring its adoption by designers [235]. We discuss our efforts for clear presentation of verification results, to save the designer time by automatically identifying which requirements a model fails to meet.

#### **1.4** Contribution of this Thesis

The contribution of this thesis involves methods to ensure safe and secure design of connecting embedded systems, ultimately cumulating in new modeling and verification methodology. More specifically, the contributions include:

#### 1.4.1 Security modeling and verification in the mapping phase

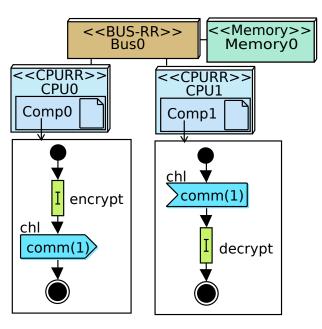

As to be discussed in Chapter 3, most security modeling describes the detailed implementation of security protocols, and takes place in the last phases of design. However, the choice of architecture should depend on its ability to support security features. When designing an architecture and mapping the functions to architecture, the selection of an optimal mapping relies on correct approximations of execution times of functions [141]. Therefore, the time to execute these security protocols should be considered when selecting an architecture/mapping.

However, placement of security functions depends on which data should be secured, which in turn depends on both the capabilities of the attacker to access the architecture, and which data can be accessed from those architectural locations. While previous works can take into account the performance overhead due to execution of security protocols, they lack the ability to check if an attacker can access or modify critical data [14, 288]. To be certain that security protocols are correctly placed and all security properties are satisfied, a formal security verification process should be used. To assist the designer, it could also be helpful to add security mechanisms automatically based on the verification results, and thus generate a new model fixing all the security flaws.

This thesis describes an approach on modeling attacker capabilities affecting the security of an architecture, and how to abstractly model the functional and architectural security mechanisms for secure communication, including encryption, Hardware Security Modules, and Firewalls [201]. Furthermore, we discuss how to translate mapping models to a formal specification to be analyzed by the security verifier ProVerif. Based on the verification results, the security flaws in the model could be fixed through the addition of various security mechanisms. To actualize these ideas, the security modeling and verification steps are implemented in our toolkit.

#### 1.4.2 Proof of Correctness of Model Transformation for Formal Security Verification

While some formal verification tools conveniently operate directly on program code or graphical models, most use a mathematical specification language that is complex, difficult to read, and unusable for actual design [41]. As we rely on graphical models for their ease of use, to formally analyze our models requires a model transformation process. The correctness of verification results, however, relies as much on correctness of the model transformation as it does the correctness of the model and formal verification tools [220, 328].

We prove the correctness of the model transformation to a formal specification that can be analyzed with a security prover, leveraging in part the proof and transformation process described in [208].

#### 1.4.3 Attacker Modeling

While attack steps can be modeled in Attack Trees, the description of each attack is usually limited to a few words, thus limiting their usage to documentation and not to formal evaluation. Simulations on attack trees can show possible sequences of attack steps, but they do not operate on the actual system, and therefore, the success of a simulated attack does not imply that the attack will succeed in real life. Penetration testing, on the other hand, operates directly on the actual production system, but at the final stages of the engineering process, and after most design has been completed. While successful attacks more definitively imply that security flaws exist in the system, more rework must be done than if the flaws had been detected in the design process, and additional hardware may need to be purchased if the repair requires a modification of the architecture.

We present attacker modeling at a level of abstraction in between attack trees and penetration testing, where the attacker actions can be directly executed on a system model. This thesis describes 'Attacker Scenarios', which explicitly model the attacker actions affecting a system [203]. Simulation examines the effect on the system, including the security property Availability, which could not be previously studied.

#### 1.4.4 Latency analysis

As previously mentioned, timing can be critical in real-time systems. Real-time systems may need to respond to external or system events within a set time frame [218]. For example, a sudden rise in core temperature should be controlled before components are damaged, and a moving system should change course before it collides with nearby objects. Even if a system will respond correctly in terms of function, it is insufficient if the response cannot be executed in time.

Therefore, the latencies between safety-critical events should be analyzed to determine if a system can behave safely [119]. We describe how our approach can automatically measure latencies, and how they can be related across the Mapping and Software Design phases as part of our work to assess if choices/ab-stractions made during the partitioning phase were correct [118].

#### 1.4.5 Proposition of a modified SysML-Sec Methodology

The modifications listed above result in new modeling elements and verification procedures. Integrating them into the current models involves additional methodology steps. Our additions also add new relations between diagrams that need to be captured in our methodology.

To address safety and security at the same time, it is thus necessary to develop a new methodology taking into account all the different modeling and verification steps. The new methodology better relates requirements and verifications across the different phases, and further integrates attacker models into the modeling and analysis methodology.

#### 1.4.6 Taxonomy for Safe and Secure Autonomous Vehicle Design

As this thesis was under the direction of Institut Vedecom, we present their Level 4 autonomous car in our case study. The VEDECOM Autonomous Car, as shown in Figure 1-1, is equipped with a Velodyne Lidar,

Figure 1-1: Vedecom Autonomous Car

radars, and one front and one rear Mobileye camera.

To prepare our case study, we present a survey of the related issues, such as published safety and security issues, and the possible approaches to solve these issues. However, some of the proposed solutions come with secondary effects. For example, as discussed previously, executing security protocols increases program execution time. We discuss the conflicts and downsides of these solutions in terms of how they affect the safety, security, and performance of a system. These concerns and solutions are then summarized in a taxonomy, on which our design and verification process is based.

#### 1.5 Organization of this Thesis

This thesis starts with presenting our motivation: Autonomous/Connected Cars, in Chapter 2. We describe the architecture of the Vedecom autonomous car, then the possible safety and security concerns, such as reported safety problems caused by software flaws, and demonstrated possible attacks on connected vehicles and their sensors, and then proposed solutions. The aspects of design are summarized in a taxonomy on autonomous vehicle safety and security. Chapter 3 presents the Related Work, regarding other methodologies and toolkits related to software design, design of embedded systems, and safety and security verification techniques.

Chapter 4 presents a proposal for an improved SysML-Sec methodology with the different phases applied to our Autonomous Vehicle case study. Chapter 5 presents the contributions to security modeling in HW/SW Partitioning, and Chapter 6 presents the security verification of mapping models with ProVerif,

and automatic generation of security mechanisms based on those results. Chapter 7 presents the contributions to measuring latencies between events, and how the requirements and latencies are related across different phases. Finally, Chapter 8 concludes this thesis and discusses potential future work.

### Chapter 2

### **Context: Autonomous Vehicles**

"Society tolerates a significant amount of human error on our roads. We are, after all, only human. On the other hand, we expect machines to perform much better. ... Humans have shown nearly zero tolerance for injury or death caused by flaws in a machine." –Gill Pratt, Toyota Research

The introduction of self-driving cars is expected to decrease accidents, ease traffic, decrease pollution, offer transport to the disabled, elderly, and children who cannot drive, and change the very fabric of our daily commutes [101]. Unlike conventional vehicles, autonomous vehicles will rely entirely on software and sensors, instead of potentially flawed human decision-making for control. To ensure the safety of passengers and other individuals in proximity, manufacturers must ensure the safe and secure function of the vehicle software. According to Guillaume Duc, professor at Telecom Paristech and chair of the Connected cars and cybersecurity project, "Autonomous cars will not exist until we are able to guarantee that cyber-attacks will not put a smart vehicle, its passengers or its environment in danger." [156].

As with other embedded devices, vehicles have not been free from design flaws as demonstrated through the years. Even worse, while the increased connectivity of vehicles has offered new conveniences, safety measures, and comforts for drivers, they have also created avenues for attack for hackers.

#### 2.1 Safety and Security Flaws

#### 2.1.1 Safety Flaws in Commercial Vehicles

Since the introduction of automobiles, there have been design flaws posing safety risks, some of which resulted in injuries and deaths of the occupants [120, 199]. Many involved mechanical failures which resulted in multiple injuries and deaths.

Due to its placement, the fuel tank of the Ford Pinto was found to susceptible to fires in the event of a rear-end collision, causing hundreds of deaths in the 1970s [343]. Even worse, it was proved that Ford was aware of the flaw and chose not to correct it, resulting in multiple lawsuits. Ford ultimately recalled 1.5 million vehicles.

In 2009, it was reported that Toyota vehicles were involved in multiple accidents due to uncontrollable sudden accelerations due to a stuck gas pedal [333]. Multiple fatalities resulted from accidents when vehicles accelerated despite the driver attempting to brake. Ultimately, Toyota recalled millions of vehicles. In 2017, BMW recalled 1 million vehicles due to a fire risk [272]. There were around 40 cases of parked cars catching on fire due to valve heater or wiring problems, in some cases resulting in fire damage to the owner's garage and house as well.

Software flaws have also prompted the recalls of vehicles. For example, in 2016, Hyundai recalled SUVs since the transmission control computer had an intermittent software problem which could prevent the vehicle from accelerating [232]. After at least 1 death and multiple injuries due to a software flaw that prevented airbags from deploying during accidents, in 2016, General Motors recalled millions of vehicles to be repaired.

These design flaws have caused injuries and death, and cost manufacturers millions in fines, lawsuits, or recalls.

#### 2.1.2 Survey of Hacks on Connected Vehicles

The authors of [159] presented privacy and security risks of a Tire Pressure Monitoring System. By monitoring RF signals from the sensors, the authors found the unique sensor ID for identification of the vehicle, and spoofed packets to send fake tire pressure warnings. This attack could force a driver to pull over thinking he had a flat tire, and also the ability to track cars by their wireless signals is a privacy concern.

Telematics units can be attached to cars, and often used for insurance purposes, have been an avenue of attacks on the operation of vehicles themselves. The authors of [188] performed an attack through the OBD-II port using the CAN-to-USB interface. The authors built a CAN packet sniffer/injector and determined how to control units, many commands discovered through fuzzing. Furthermore, the attack restarts the ECU and erases any evidence of the attack code. However, the attack required physical access to the OBD device.

Another minor attack [345] used a malicious application on a paired smartphone and a car with an OBD-II scan tool. When an OBD-II and smartphone with diagnostic application are connected through bluetooth, an attacker can send malicious CAN frames to the vehicle. While it required the user to accidentally install the malicious application and for the car to have a telematics unit installed, it demonstrates another avenue of attack.

The authors of [109] analysed the Metromile TCUs, an aftermarket device interfacing with the OBD-II port. The ssh keys were common to all TCUs and could be acquired by dumping the NAND flash. Updates to the TCU were sent through SMS messages, which the authors used to create a new console starting a remote shell to obtain access to the device through ssh. The authors note that the update did not have the vehicle verify the server's identity, which is a major vulnerability.

New phone apps allow users to control comfort settings. However, vulnerabilities in these apps, such as lack of authentication protocols, can be a problem. One such example is the WebAPI for the Nissan Leaf, which required only a VIN number to access certain climate control and status of a vehicle [150]. While they did not offer an avenue for attack on the car operation itself, except for draining the battery, researchers were able to recover driving history, which may be a privacy concern.

Most notably, Miller and Valasek's hack is completely remote and prompted a recall and change in Sprint's network [223]. The authors connected to the built-in telematics unit Uconnect's Diagnostics Bus, open to any 3G device using Sprint. They reprogrammed the unit with custom firmware to send CAN messages and control ECUs. This attack is unique as it could attack a vehicle anywhere on the Sprint network and did not require that the vehicle have more than the default setup.

In 2016, researchers from Tencent presented how to gain control of a Tesla that connected to their malicious wifi hotspot [67]. They reported that a vulnerability in the Tesla's browser would allow them to run code if it visited their page. The malicious code helped them gain access to the car's head unit, which they used to overwrite the gateway to the CAN bus, and subsequently inject their own commands onto the CAN bus. Tesla has reportedly responded by requiring that firmware of components writing to the CAN bus be code signed. However, during Defcon 2017, the same group of researchers demonstrated that they could again gain remote control of a Tesla via cellular data and wifi [337].

Recently, it has been demonstrated that Denial-of-service attacks against the CAN bus could disable safety features [246]. By sending multiple erroneous frames to a CAN node, the node could be completely turned off, preventing it from sending and receiving any more messages. In this case, the authors needed physical access to the vehicle to carry out the attack, but their attack could be combined with the previous remote attacks on the CAN bus.

In all of these attacks, connected features have exposed their users to potential privacy or safety risks.

#### 2.1.3 Safety Limitations of Autonomous Vehicles

Unlike conventional vehicles, autonomous vehicles rely on their sensors to perceive the world around them. Any failure in a sensor could lead to a grave impact on vehicle safety. However, it has been noted that these sensors are not always reliable.

The GPS is vital to determining the current vehicle location, which helps a vehicle determine not only it's trajectory, but also the nearby traffic lights, signs, and etc [66]. However, GPS signals can be easily blocked, in a tunnel or due to tree cover, for example. Its resolution is also not precise enough to navigate without other sensors.

In 2016, the Tesla Autopilot caused a fatal crash when its perception system failed to distinguish a white tractor-trailer against a bright sky [180]. In 2018, a driver again running Tesla autopilot died in a fatal crash after the vehicle drove into a concrete barrier on the freeway [300], likely due to confusing lane markings. The Tesla autonomous vehicle uses only radar and cameras, which other developers find insufficient, as radar fails to see detail and cameras can fail in problematic lighting conditions, such as the glare in this situation [295]. Lidars have been suggested to be vital, as they are more accurate than radar, and can provide a 3D image [90].