## Protection du contenu des mémoires externes dans les systèmes embarqués, aspect matériel

Salaheddine Ouaarab

### ▶ To cite this version:

Salaheddine Ouaarab. Protection du contenu des mémoires externes dans les systèmes embarqués, aspect matériel. Cryptographie et sécurité [cs.CR]. Télécom ParisTech, 2016. Français. NNT: 2016ENST0046. tel-02120616

## HAL Id: tel-02120616 https://pastel.hal.science/tel-02120616

Submitted on 6 May 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **Doctorat ParisTech**

## THÈSE

pour obtenir le grade de docteur délivré par

## **TELECOM ParisTech**

Spécialité « Electronique et Communication »

présentée et soutenue publiquement par

### Salaheddine OUAARAB

le 9 Septembre 2016

## Protection du contenu des mémoires externes dans les systèmes embarqués, aspect matériel

Directeur de thèse : Renaud PACALET

Co-encadrement de la thèse : Guillaume DUC

### Jury

M. Bruno ROUZEYERE, Professeur, Université de Montpellier, Montpellier

M. Bruno ROBISSON, Ingénieur de recherche, CEA, Gardanne

M. Jean-Luc DANGER, Directeur d'Etudes, Télécom ParisTech, Paris

M. Bernard KASSER, Directeur R&D sécurité, STMicroelectronics, Rousset

M. Gilles SASSATELLI, Directeur de Recherche CNRS, LIRMM, Montpellier

### TELECOM ParisTech

Rapporteur Rapporteur Examinateur Examinateur Examinateur

# Table des matières

| Re | Remerciements 11 |         |                                                       |      |  |

|----|------------------|---------|-------------------------------------------------------|------|--|

| In | Introduction 15  |         |                                                       |      |  |

| 1  | Élén             | nents d | e cryptographie                                       | 17   |  |

|    | 1.1              |         | tions                                                 | . 17 |  |

|    | 1.2              | Techni  | iques de chiffrement                                  | . 18 |  |

|    |                  | 1.2.1   | Chiffrement symétrique                                |      |  |

|    |                  |         | 1.2.1.1 Chiffrement de flux                           |      |  |

|    |                  |         | 1.2.1.1.1 Masque jetable ( <i>One Time Pad</i> , OTP) |      |  |

|    |                  |         | 1.2.1.1.2 Chiffrement de flux synchrone               | . 21 |  |

|    |                  |         | 1.2.1.1.3 Chiffrement de flux auto-synchrone          |      |  |

|    |                  |         | 1.2.1.2 Chiffrement par bloc                          |      |  |

|    |                  |         | 1.2.1.2.1 Structure du chiffrement par bloc           |      |  |

|    |                  |         | 1.2.1.2.2 Exemple : AES                               |      |  |

|    |                  |         | 1.2.1.2.3 Modes d'opération                           |      |  |

|    |                  |         | Electronic CodeBook (ECB)                             |      |  |

|    |                  |         | Cipher-Block Chaining (CBC)                           | . 26 |  |

|    |                  |         | Cipher FeedBack (CFB)                                 | . 27 |  |

|    |                  |         | Output FeedBack (OFB)                                 | . 28 |  |

|    |                  |         | Mode compteur                                         | . 29 |  |

|    |                  |         | 1.2.1.3 Conclusion                                    | . 31 |  |

|    |                  | 1.2.2   | Chiffrement asymétrique                               | . 31 |  |

|    |                  | 1.2.3   | Sécurité des techniques de chiffrement                | . 32 |  |

|    | 1.3              | Techni  | iques de vérification d'intégrité                     | . 33 |  |

|    |                  | 1.3.1   | Fonctions de hachage                                  | . 33 |  |

|    |                  |         | 1.3.1.1 Code de détection de modification             | . 34 |  |

|    |                  |         | 1.3.1.1.1 Exemple : SHA                               | . 34 |  |

|    |                  |         | 1.3.1.2 Code d'authentification de message            | . 35 |  |

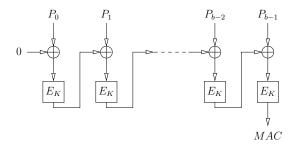

|    |                  |         | 1.3.1.2.1 Exemple : CBC-MAC                           | . 35 |  |

|    |                  | 1.3.2   | Paradoxe des anniversaires                            | . 36 |  |

|    |                  | 1.3.3   | Conclusion                                            | . 36 |  |

| 2  | Pan              |         | des techniques de protection                          | 37   |  |

|    | 2.1              | Modèl   | le de menace                                          |      |  |

|    | 2.2              | Métho   | odes de protection                                    | . 40 |  |

|   |       | 2.2.1<br>2.2.2 |                                                                      | 40<br>42  |

|---|-------|----------------|----------------------------------------------------------------------|-----------|

|   |       | 2.2.2          |                                                                      | 42        |

|   |       |                | 2.2.2.2 Méthodes de protection contre l'attaque par permutation spa- |           |

|   |       |                |                                                                      | 43        |

|   |       |                |                                                                      | 44        |

|   | 2.3   | Les arb        |                                                                      | 46        |

|   | 2.0   | 2.3.1          |                                                                      | 47        |

|   |       | 2.0.1          | <u> </u>                                                             | 47        |

|   |       |                |                                                                      | 48        |

|   |       |                |                                                                      | 48        |

|   |       | 2.3.2          | <u>,                                      </u>                       | 49        |

|   |       |                |                                                                      | 49        |

|   |       |                |                                                                      | 51        |

|   |       |                |                                                                      | 55        |

|   |       |                | ,                                                                    | 56        |

|   |       | 2.3.3          |                                                                      | 57        |

|   |       |                |                                                                      | 57        |

|   |       |                |                                                                      | 57        |

|   |       |                |                                                                      | 60        |

|   |       |                |                                                                      | 60        |

|   |       | 2.3.4          | 1                                                                    | 60        |

|   | 2.4   | Plates-        | •                                                                    | 61        |

|   |       | 2.4.1          | Best                                                                 | 61        |

|   |       | 2.4.2          |                                                                      | 62        |

|   |       | 2.4.3          | XOM                                                                  | 63        |

|   |       | 2.4.4          |                                                                      | 65        |

|   |       | 2.4.5          | CryptoPage                                                           | 66        |

|   |       | 2.4.6          | MESA                                                                 | 67        |

|   |       | 2.4.7          | PE-ICE                                                               | 67        |

|   | 2.5   | Conclu         |                                                                      | 68        |

|   |       |                |                                                                      |           |

| 3 | Les a | arbres d       | de Merkle creux et la gestion de la mémoire                          | <b>71</b> |

|   | 3.1   | Les art        | ores creux initialisés                                               | 73        |

|   |       | 3.1.1          | Opérations                                                           | 73        |

|   |       |                | 3.1.1.1 Initialisation                                               | 73        |

|   |       |                | 3.1.1.2 Vérification                                                 | 74        |

|   |       |                |                                                                      | 74        |

|   |       | 3.1.2          | Évaluation des performances                                          | 75        |

|   |       |                |                                                                      | 75        |

|   |       |                |                                                                      | 76        |

|   |       |                | 3.1.2.3 Écriture vérifiée                                            | 76        |

|   | 3.2   | Les art        | ores creux non initialisés                                           | 76        |

|   |       | 3.2.1          | Opérations                                                           | 77        |

|   |       |                |                                                                      | 77        |

|   |       |                | 3.2.1.2 Vérification                                                 | 77        |

|   |       |                |                                                                      |           |

|   |     |         | 3.2.1.3 Mise à jour                                                 |

|---|-----|---------|---------------------------------------------------------------------|

|   |     | 3.2.2   | Évaluation des performances                                         |

|   |     |         | 3.2.2.1 Initialisation                                              |

|   |     |         | 3.2.2.2 Lecture vérifiée                                            |

|   |     |         | 3.2.2.3 Écriture vérifiée                                           |

|   | 3.3 | Utilisa | tion d'un cache d'arbres de Merkle                                  |

|   | 0.0 | 3.3.1   | Stratégie ASAP                                                      |

|   |     | 3.3.2   | Stratégie ALAP                                                      |

|   |     | 3.3.3   | Cache d'arbre de Merkle ALAP et Write-Through                       |

|   |     | 3.3.4   | Cache d'arbre de Merkle ALAP et Write-Back-Allocate                 |

|   |     | 3.3.4   | 3.3.4.1 Les opérations élémentaires du cache                        |

|   |     |         | 1                                                                   |

|   |     |         | •                                                                   |

|   |     |         |                                                                     |

|   |     | 2.2.5   | 3.3.4.4 Correction fonctionnelle de la gestion du cache proposée 98 |

|   | 2.4 | 3.3.5   | Combinaison des arbres creux et du cache d'arbre                    |

|   | 3.4 | Conclu  | ısion                                                               |

| 4 | Cas | J2/4 Ja | e: projet SecBus                                                    |

| 4 | 4.1 |         | 1 0                                                                 |

|   | 4.1 |         | uction                                                              |

|   |     | 4.1.1   | Modèle de menace                                                    |

|   |     | 4.1.2   | Objectifs de sécurité                                               |

|   |     |         | 4.1.2.1 Confidentialité                                             |

|   |     |         | 4.1.2.1.1 Pages RO                                                  |

|   |     |         | 4.1.2.1.2 Pages RW                                                  |

|   |     |         | 4.1.2.2 Intégrité                                                   |

|   |     |         | 4.1.2.2.1 Pages RO                                                  |

|   |     |         | 4.1.2.2.2 Pages RW                                                  |

|   |     | 4.1.3   | Architecture et structures de données                               |

|   |     |         | 4.1.3.1 Politiques de sécurité                                      |

|   |     |         | 4.1.3.2 Paramètres de sécurité de page                              |

|   |     |         | 4.1.3.3 Arbre de MAC Maître (MMT)                                   |

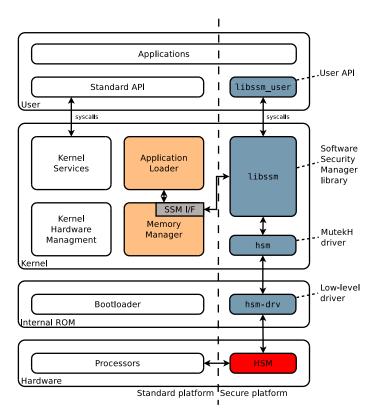

|   | 4.2 | Archite | ecture logicielle                                                   |

|   |     | 4.2.1   | Bootloader                                                          |

|   |     | 4.2.2   | SSM                                                                 |

|   |     |         | 4.2.2.1 Interface d'applications                                    |

|   |     |         | 4.2.2.2 Chargeur d'applications                                     |

|   |     |         | 4.2.2.3 Mémoire dynamique                                           |

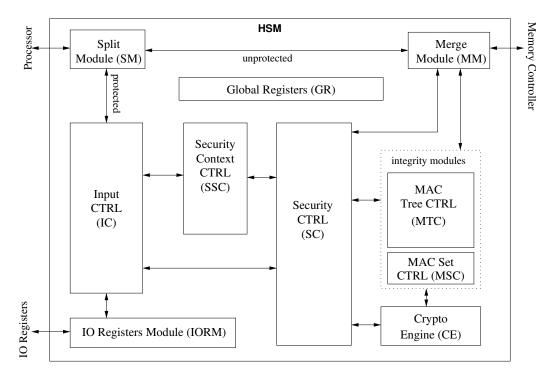

|   | 4.3 | Archite | ecture matérielle                                                   |

|   |     | 4.3.1   | Modules d'interface                                                 |

|   |     |         | 4.3.1.1 Split Module                                                |

|   |     |         | 4.3.1.2 Merge Module                                                |

|   |     |         | 4.3.1.3 Input Controller                                            |

|   |     |         | 4.3.1.4 IO Registers Module                                         |

|   |     | 4.3.2   | Modules de protection                                               |

|   |     | 1.5.2   | 4.3.2.1 Security Context Controller                                 |

|   |     |         | 4.3.2.1 Security Controller                                         |

|   |     |         | - T.J.4.4 - GCCUITTY CONTROLLS                                      |

|    |            |          | 4.3.2.3 Crypto Engine                                                                                         | 117 |

|----|------------|----------|---------------------------------------------------------------------------------------------------------------|-----|

|    |            |          | 4.3.2.4 MAC Set Controller                                                                                    |     |

|    |            |          | 4.3.2.5 MAC Tree Controller                                                                                   | 117 |

|    | 4.4        | Conclu   | asion                                                                                                         | 118 |

| 5  | Simi       | ulations | s et validations                                                                                              | 119 |

|    | 5.1        |          | le simulation des Arbres de Merkle                                                                            |     |

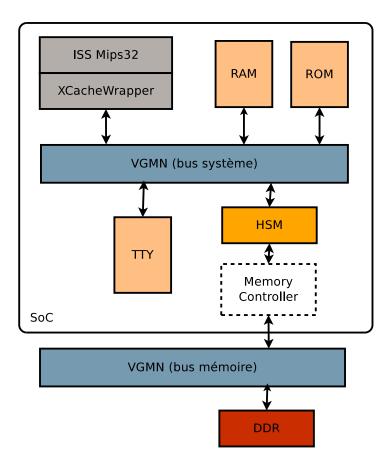

|    | 5.1        | 5.1.1    | Environnement de simulation                                                                                   |     |

|    |            | 5.1.1    | 5.1.1.1 Introduction de SoCLib                                                                                |     |

|    |            |          | 5.1.1.2 Plate-forme et application                                                                            |     |

|    |            |          | 5.1.1.2.1 Initialisation des arbres de Merkle                                                                 |     |

|    |            |          | 5.1.1.2.2 Configuration des paramètres de sécurité                                                            |     |

|    |            |          | 5.1.1.2.2 Configuration des parametres de securite :                                                          |     |

|    |            |          | 5.1.1.2.4 Paramètres de la simulation                                                                         |     |

|    |            | 5.1.2    | Résultats                                                                                                     |     |

|    |            | 5.1.2    | Conclusion                                                                                                    |     |

|    | 5.2        |          | tion fonctionnelle                                                                                            |     |

|    | 3.2        | 5.2.1    | Introduction                                                                                                  |     |

|    |            | 5.2.1    |                                                                                                               |     |

|    |            | 5.2.3    | Ce que l'on prouve $\dots$ . Quelques précisions sur la preuve de raffinement avec la méthode $\mathcal{B}$ . |     |

|    |            | 3.2.3    | 5.2.3.1 Des arbres abstraits aux arbres concrets                                                              |     |

|    |            |          |                                                                                                               | 129 |

|    |            |          | 5.2.3.2 De l'algorithme abstrait (fonctionnel récursif) au concret (impératif itératif)                       | 122 |

|    |            |          | ,                                                                                                             |     |

|    |            | 5.2.4    | 5.2.3.3 Preuve formelle                                                                                       |     |

|    |            | 3.2.4    | Quelques précisions sur la preuve d'équivalence avec <i>EasyCrypt</i>                                         |     |

|    |            |          | 5.2.4.1 Modèle                                                                                                |     |

|    |            |          | 5.2.4.1.1 Formalisation des constructions                                                                     |     |

|    |            |          | 5.2.4.1.2 Modèle calculatoire                                                                                 |     |

|    |            | 5.2.5    | 5.2.4.2 Preuve                                                                                                |     |

|    | <i>5</i> 2 | 5.2.5    | Conclusion                                                                                                    |     |

|    | 5.3        |          | ation des performance du module matériel HSM                                                                  |     |

|    |            | 5.3.1    | Introduction                                                                                                  |     |

|    |            | 5.3.2    | Coûts matériels                                                                                               |     |

|    |            | 5.3.3    | Augmentation de l'empreinte mémoire                                                                           |     |

|    |            | 5.3.4    | Configurations et résultats                                                                                   |     |

|    |            |          | 5.3.4.1 Configurations                                                                                        |     |

|    |            | 5 O 5    | 5.3.4.2 Résultats                                                                                             |     |

|    |            | 5.3.5    | Conclusion                                                                                                    | 153 |

| Co | onclus     | sions et | perspectives                                                                                                  | 155 |

| Ar | opend      | ices     |                                                                                                               | 157 |

# Table des figures

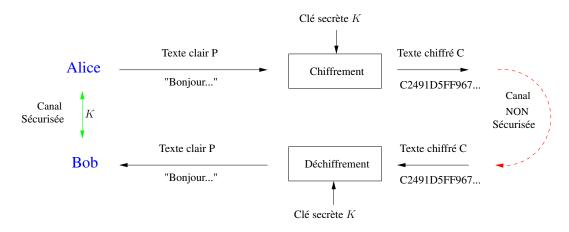

| 1.1  | Chiffrement symétrique                                                         | 19 |

|------|--------------------------------------------------------------------------------|----|

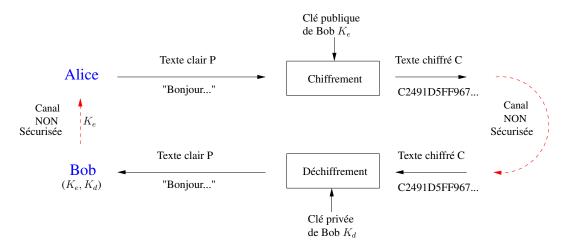

| 1.2  | Chiffrement asymétrique                                                        | 20 |

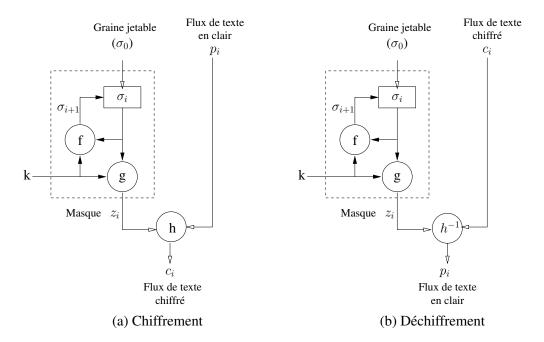

| 1.3  | Chiffrement de flux synchrone                                                  | 22 |

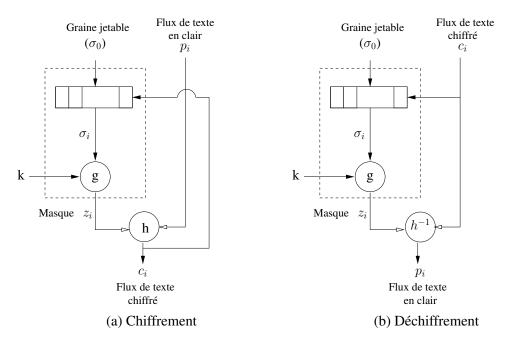

| 1.4  | Chiffrement de flux auto-synchrone                                             | 23 |

| 1.5  | Structure du chiffrement par bloc                                              | 24 |

| 1.6  | Chiffrement par bloc en mode ECB                                               | 25 |

| 1.7  | Chiffrement par bloc en mode CBC                                               | 27 |

| 1.8  | Chiffrement par bloc en mode CFB                                               | 28 |

| 1.9  | Chiffrement par bloc en mode OFB                                               | 29 |

| 1.10 | Chiffrement par bloc en mode compteur                                          | 30 |

| 1.11 | Fonction de hachage                                                            | 34 |

|      | Fonction de HMAC                                                               | 35 |

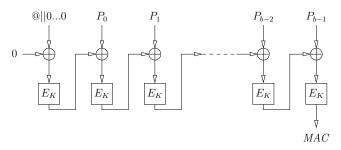

| 1.13 | Calcul de CBC-MAC                                                              | 35 |

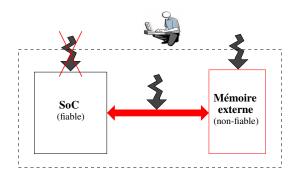

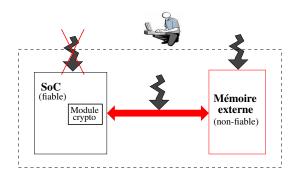

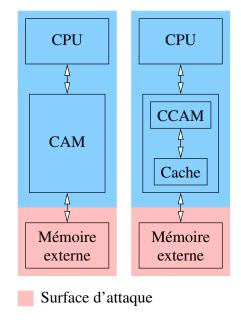

| 2.1  | Zones d'attaques considérées                                                   | 39 |

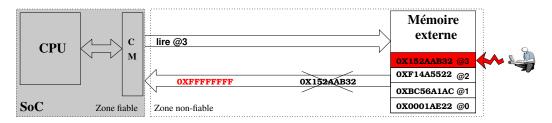

| 2.2  | Attaque par injection                                                          | 40 |

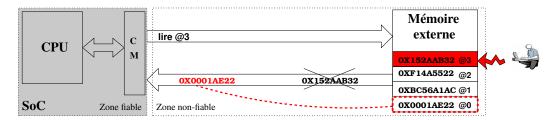

| 2.3  | Attaque par permutation spatiale                                               | 40 |

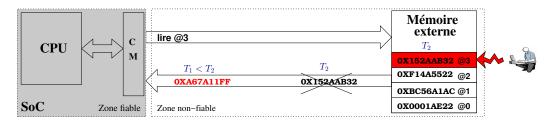

| 2.4  | Attaque par rejeu                                                              | 40 |

| 2.5  | Ajout du module cryptographique à l'intérieur du SoC                           | 41 |

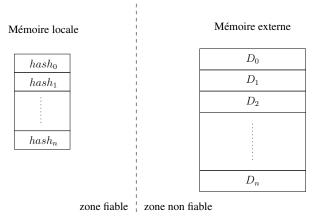

| 2.6  | Protection d'une zone mémoire contre les attaques par injection                | 43 |

| 2.7  | Protection d'une zone mémoire contre les attaques par injection                | 43 |

| 2.8  | Calcul du CBC-MAC avec adresse                                                 | 44 |

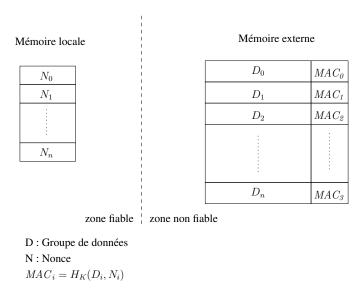

| 2.9  | Protection de la mémoire externe avec des MAC et nonce                         | 45 |

|      | Protection de la mémoire externe avec la technique AREA                        | 45 |

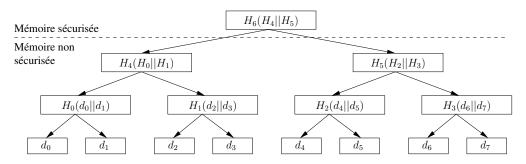

|      | Arbre de Merkle                                                                | 46 |

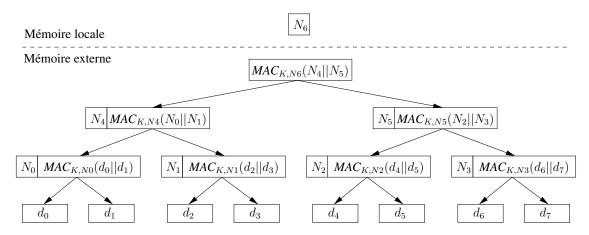

|      | Arbre de Merkle protégeant l'intégrité d'un ensemble de données                | 47 |

|      | Arbre de Merkle déséquilibré protégeant l'intégrité d'un ensemble de données . | 51 |

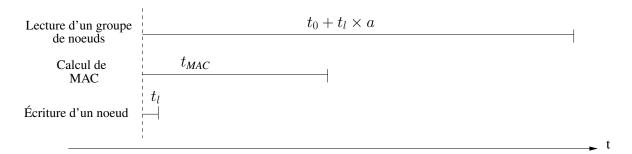

| 2.14 | Comparaison entre le temps pris pour une lecture d'un groupe de nœuds, un      |    |

|      | calcul de MAC et un écriture d'un nœud                                         | 52 |

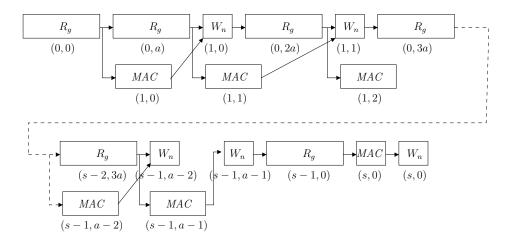

|      | Latences des différentes opérations de l'initialisation d'arbre                | 52 |

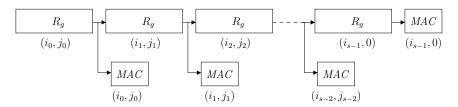

|      | Latences des différentes opérations d'une lecture vérifiée                     | 55 |

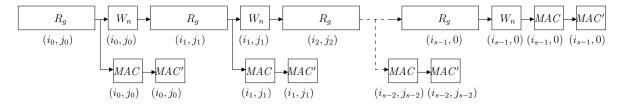

|      | Latences des différentes opérations d'une écriture vérifiée                    | 56 |

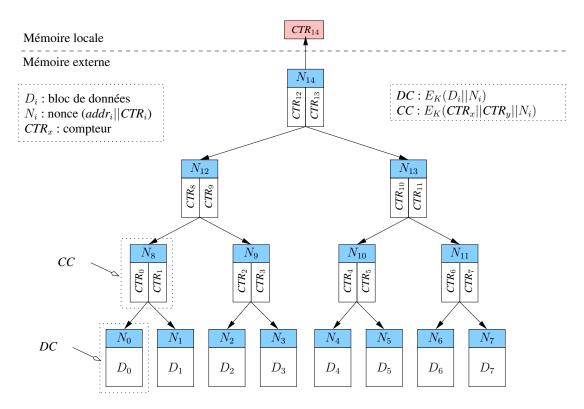

|      | Parallelizable Authentication Tree (PAT)                                       | 58 |

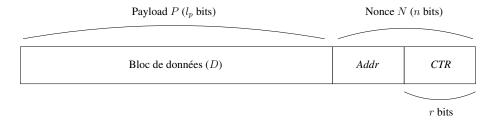

|      | Configuration d'un <i>DC</i> avant le chiffrement                              | 58 |

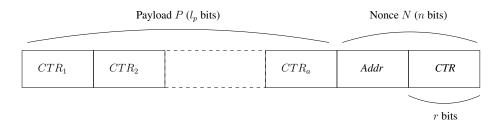

|      | Configuration d'un $CC$ avant le chiffrement                                   | 59 |

| 2.21 | Tamper-Evident Counter Tree (TEC-Tree)                                         | 59 |

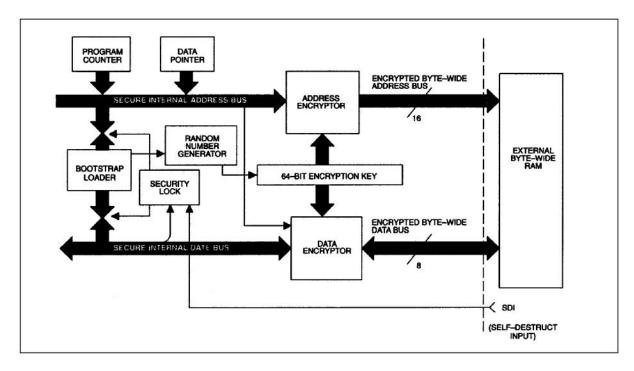

| 2.22 | Architecture de DS5002FP                                               | 62  |

|------|------------------------------------------------------------------------|-----|

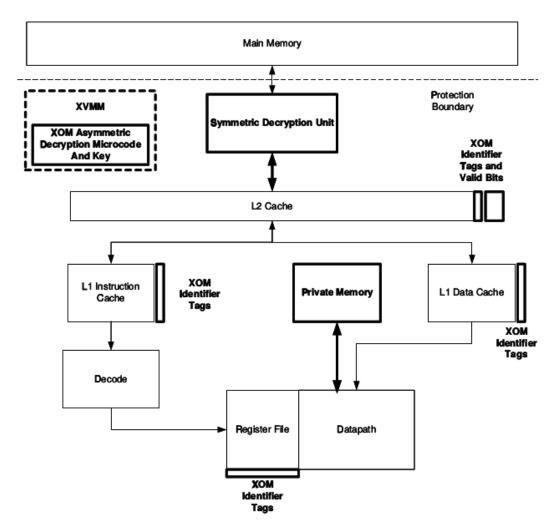

| 2.23 | Architecture de XOM                                                    | 64  |

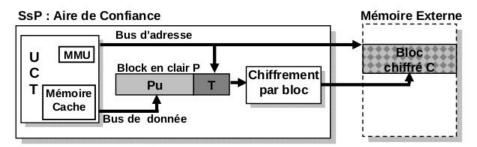

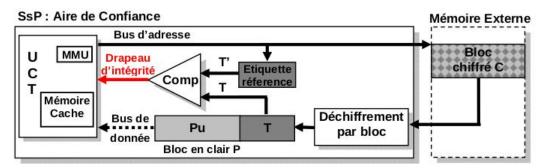

| 2.24 | Principe de fonctionnement de PE-ICE                                   | 68  |

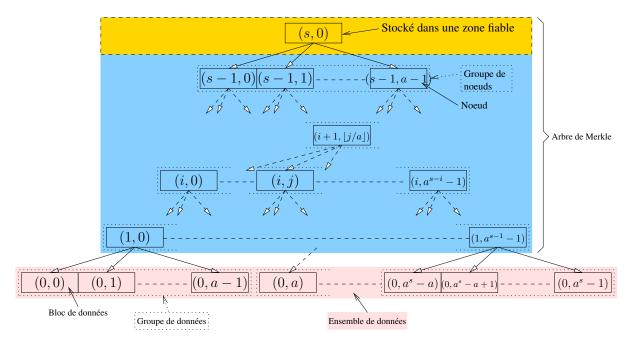

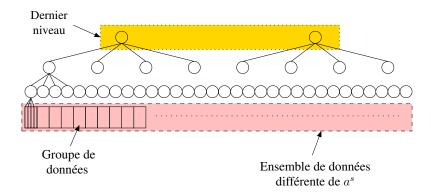

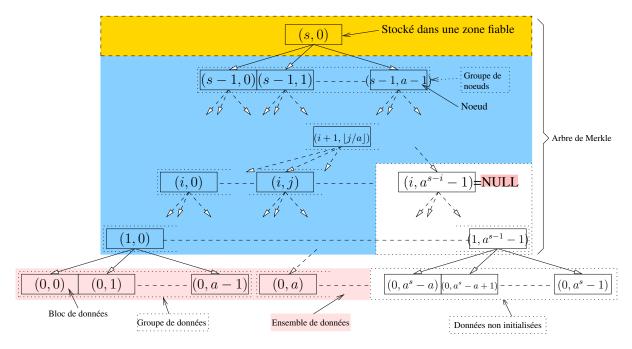

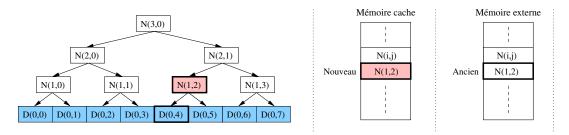

| 3.1  | AMC protégeant l'intégrité d'un ensemble de données                    | 72  |

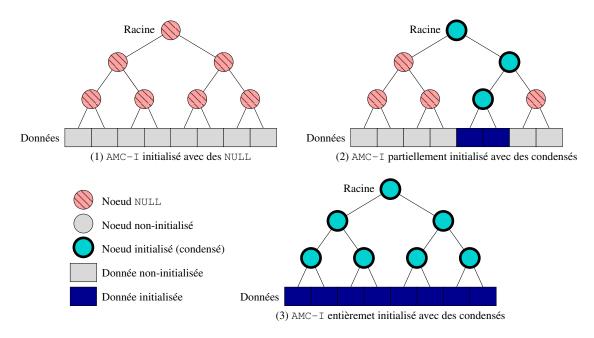

| 3.2  | Différents états d'un AMC-I                                            | 73  |

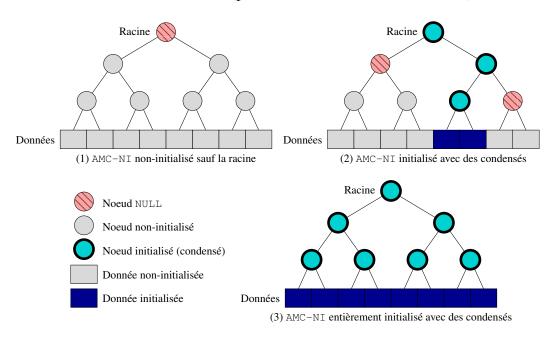

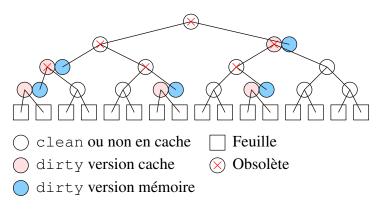

| 3.3  | Différents états d'un AMC-NI                                           | 77  |

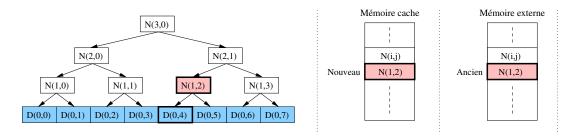

| 3.4  | Politique d'écriture Write-Through                                     | 83  |

| 3.5  | Politique d'écriture Write-Back                                        | 84  |

| 3.6  | Système étudié avec ou sans cache d'arbre de Merkle                    |     |

| 3.7  | AMCached CIP                                                           | 87  |

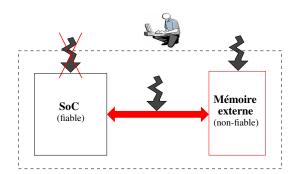

| 4.1  | Zones d'attaques considérées par SecBus                                | 103 |

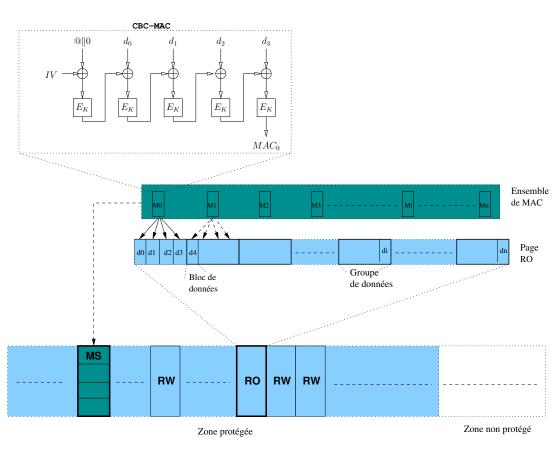

| 4.2  | Protection des pages RO en intégrité par des MAC                       | 106 |

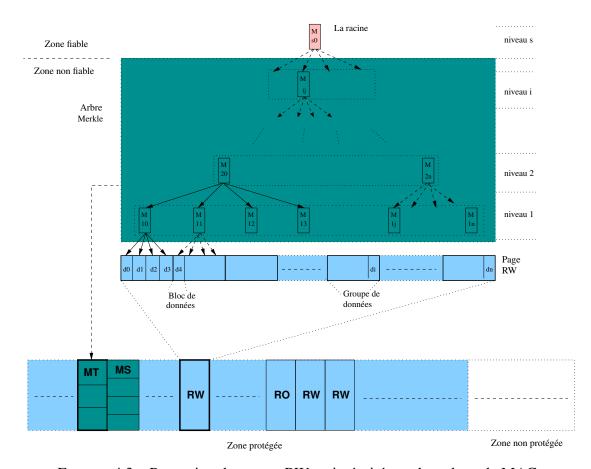

| 4.3  | Protection des pages RW en intégrité par des arbres de MAC             | 107 |

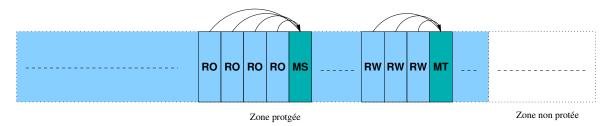

| 4.4  | Les différents types de pages mémoires                                 |     |

| 4.5  | Le HSM à l'intérieur du SoC                                            | 109 |

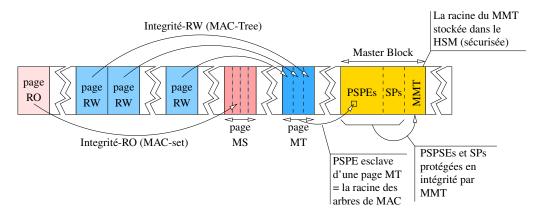

| 4.6  | Présentation de la mémoire externe avec les pages d'intégrité et le MB | 111 |

| 4.7  | Architecture logicielle de SecBus                                      | 113 |

| 4.8  | Architecture interne du HSM                                            | 115 |

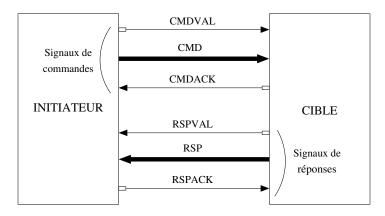

| 5.1  | Principe d'un protocole VCI                                            | 121 |

| 5.2  | Plate-Forme matérielle de SoCLib avec le HSM                           | 122 |

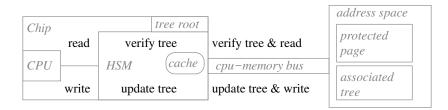

| 5.3  | Protection d'intégrité par des arbres de Merkle                        | 127 |

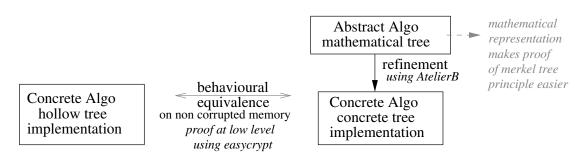

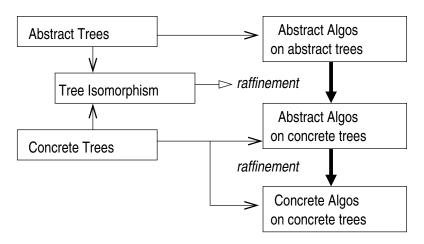

| 5.4  | Les deux étapes d'une preuve                                           |     |

| 5.5  | Modèle d'arbres                                                        | 129 |

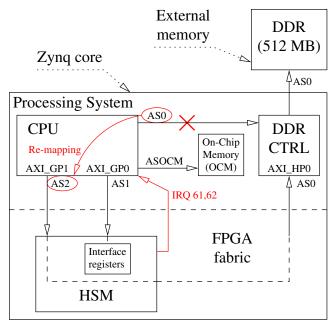

| 5.6  | Exemple d'un prototype HSM sur une carte ZedBoard à base de FPGA Zynq. | 144 |

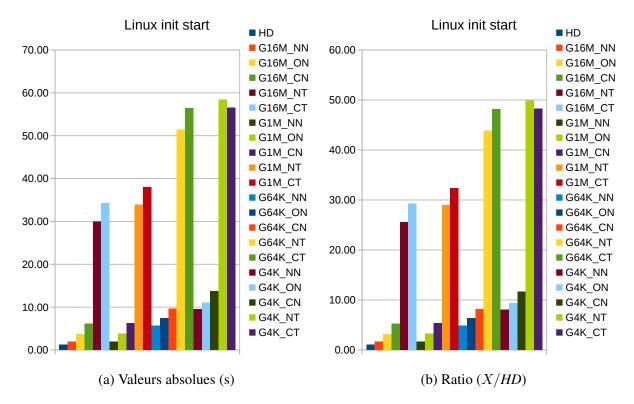

| 5.7  | Linux init start                                                       | 147 |

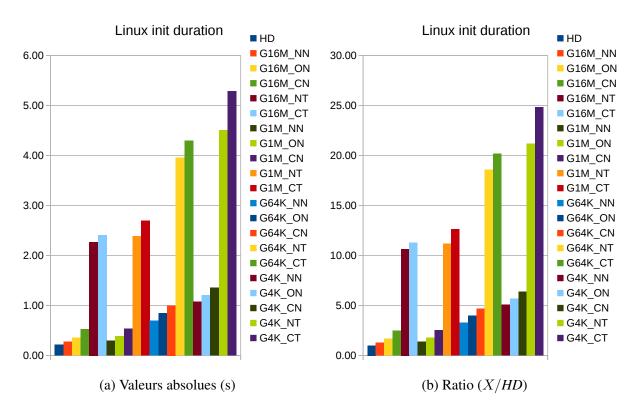

| 5.8  | Linux init duration                                                    | 148 |

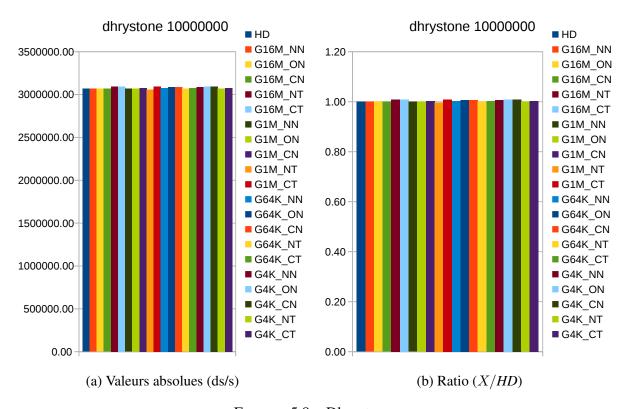

| 5.9  | Dhrystone                                                              | 148 |

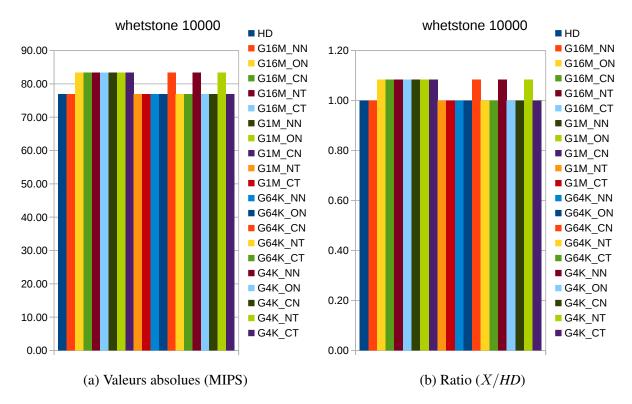

| 5.10 | Whetstone                                                              | 149 |

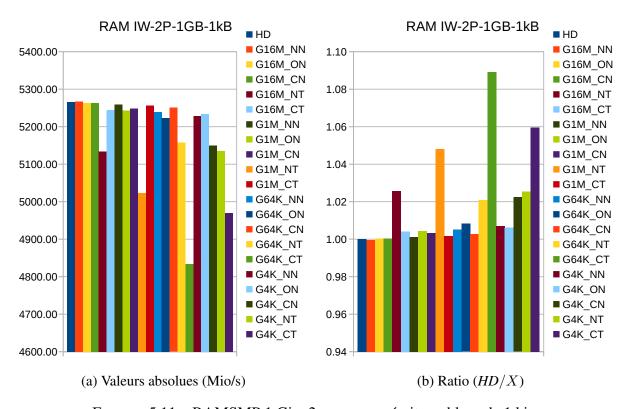

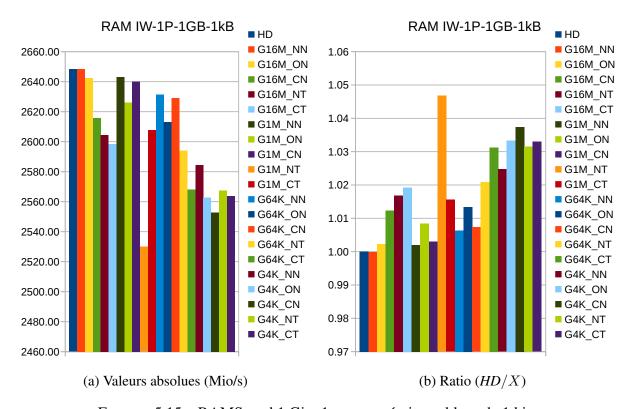

| 5.11 | RAMSMP 1 Gio, 2 processus, écriture, blocs de 1 kio                    | 149 |

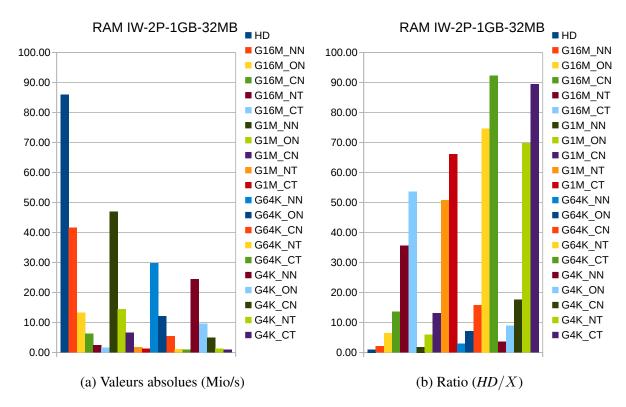

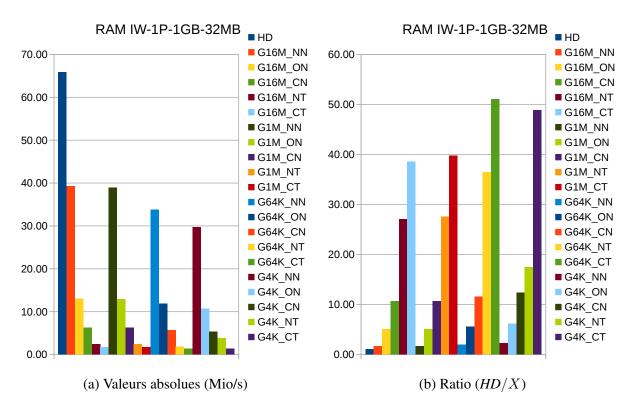

| 5.12 | RAMSMP 1 Gio, 2 processus, écriture, blocs de 32 Mio                   | 150 |

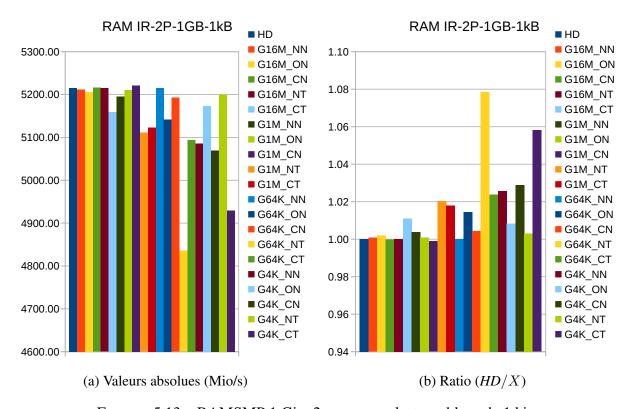

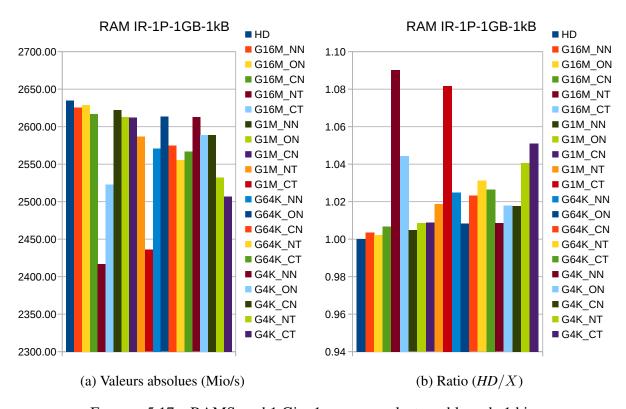

| 5.13 | RAMSMP 1 Gio, 2 processus, lecture, blocs de 1 kio                     | 150 |

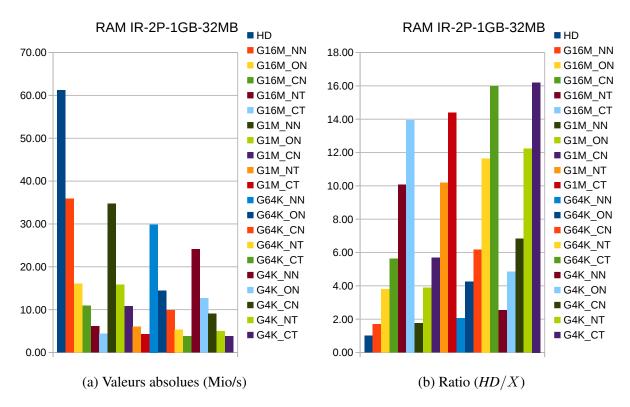

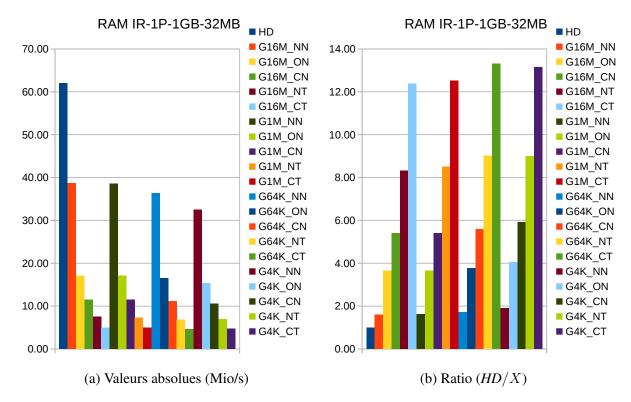

| 5.14 | RAMSMP 1 Gio, 2 processus, lecture, blocs de 32 Mio                    | 151 |

| 5.15 | RAMSpeed 1 Gio, 1 process, écriture, blocs de 1 kio                    | 151 |

| 5.16 | RAMSpeed 1 Gio, 1 processus, écriture, blocs de 32 Mio                 | 152 |

| 5.17 | RAMSpeed 1 Gio, 1 processus, lecture, blocs de 1 kio                   | 152 |

| 5.18 | RAMSpeed 1 Gio, 1 processus, lecture, blocs de 32 Mio                  | 153 |

# Liste des tableaux

| 2.1 | Résumé des propriétés des arbres existants [24]     | 51 |

|-----|-----------------------------------------------------|----|

| 5.1 | Résultats de la simulation sans cache               | 24 |

| 5.2 | Impactes du seuil sur les performances du cache     | 24 |

| 5.3 | Résultats de la simulation avec cache               | 24 |

| 5.4 | Résultats de la simulation sans cache               | 25 |

| 5.5 | Résumé de l'utilisation des ressources matérielles. | 44 |

## Remerciements

Je commence la présentation de ce travail par le remerciement de tous ceux qui ont aidé et facilité à sa réalisation. Je m'adresse à mes deux directeurs de thèse Monsieur Renaud PACA-LET et Monsieur Guillaume DUC pour leur signaler combien je suis sensible à leurs qualités. Monsieur Renaud PACALET, sa disponibilité, ses qualités humaines et ses compétences professionnelles resteront pour moi un exemple à suivre. Il m'a dirigé efficacement tout au long de ce travail, ainsi que dans bien d'autres circonstances. Monsieur Guillaume DUC, sa contribution, sa disponibilité, son sérieux et ses connaissances ont permis à mon travail d'avoir plus de valeur.

Je remercie Bruno ROUZEYERE, Bruno ROBISSON, Jean-Luc DANGER, Bernard KAS-SER, et Gilles SASSATELLI de me faire l'honneur de constituer mon jury de thèse.

Mes remerciements vont tout particulièrement à Jérémie BRUNEL, qui m'a aidé au début de la thèse à comprendre l'architecture de SecBus et à utiliser certains outils de travail, et aussi à Abdelmalek SI MERABET, pour son aide et ses conseils pertinents dans la partie d'expérimentations matérielles. Je remercie également, très chaleureusement, Rabea AMEUR-BOULIFA et Sophia COUDERT pour m'avoir aidé à réaliser la vérification fonctionnelle des algorithmes.

Je tiens à remercier tous mes collègues du département COMELEC à Paris et du laboratoire LabSoC à Sophia Antipolis, Sylvain GUILLEY, Yves MATHIEU, Laurent SAUVAGE, Tarik GRABA, Ludovic APVRILLE, Tullio TANZI, Daniel CAMARA, Andrea ENRICI, Hocine MOKRANI, Bassem OUNI, Xuan Thuy NGO, Zakaria NAJM, Youssef SUISSI, Taoufik CHOUTA, Annelie HEUSER, Shivam BHASIN, Houssem MAGHREBI, Sebastien THOMAS, Zouha CHERIF, Pablo RAUZy, Molka BEN ROMDHANE, et tous les membres de Secure-IC pour les différents échanges concernant mon sujet de thèse et pour l'intérêt qu'ils ont porté à mon travail. J'ai été très touché par leur disponibilité et leurs conseils précieux, pour leur dire que je vous serais sincèrement reconnaissant.

Durant ces années passées dans notre chère école, j'ai bénéficié d'un corps administratif toujours présent pour m'aider et me soutenir très chaleureusement. Ceci est l'occasion de leur présenter ma sincère et amicale considération. Je cite Mesdames Chantal Cadiat, Yvonne BANSIMBA, Florence Besnard, Chantal GUIZOL (Eurecom), Zouina Sahnoun, Nazha Essakkaki et Pascale CASTAING (Eurecom); et Messieurs Hamidou YAYA KONÉ, Bruno Thedrez, Philippe FOUBERT (Eurecom), Franck HEURTEMATTE (Eurecom) et Dominique ROUX.

Enfin, ces remerciements ne seraient complets sans mentionner les personnes que j'aime le plus au monde, ma mère Aicha et mon père Allali, qui ont toujours su me témoigner leur amour inconditionnel et leur soutien continu, et bien évidemment à mes frères et sœurs, Adil,

Btissam, Aziz et Wiam qui malgré la distance ont toujours marqué leur présence et leur soutien. Mes remerciements vont également à toute la famille OUAARAB et KHOUYA.

### Résumé

Ces dernières années, les systèmes informatiques (*Cloud Computing*, systèmes embarqués, etc.) sont devenus omniprésents. La plupart de ces systèmes utilisent des espaces de stockage (flash, RAM, etc.) non fiables ou non dignes de confiance pour stocker du code ou des données. La confidentialité et l'intégrité de ces données peuvent être menacées par des attaques matérielles (espionnage de bus de communication entre le composant de calcul et le composant de stockage) ou logicielles. Ces attaques peuvent ainsi révéler des informations sensibles à l'adversaire ou perturber le bon fonctionnement du système. Dans cette thèse, nous nous sommes focalisés, dans le contexte des systèmes embarqués, sur les attaques menaçant la confidentialité et l'intégrité des données qui transitent sur le bus de communication avec la mémoire ou qui sont stockées dans celle-ci.

Plusieurs primitives de protection de confidentialité et d'intégrité ont déjà été proposées dans la littérature, et notamment les arbres de Merkle, une structure de données protégeant efficacement l'intégrité des données notamment contre les attaques par rejeu. Malheureusement, ces arbres ont un impact important sur les performances et sur l'empreinte mémoire du système.

Dans cette thèse, nous proposons une solution basée sur des variantes d'arbres de Merkle (arbres creux) et un mécanisme de gestion adapté du cache afin de réduire grandement l'impact de la vérification d'intégrité d'un espace de stockage non fiable. Les performances de cette solution ont été évaluées théoriquement et à l'aide de simulations. De plus, une preuve est donnée de l'équivalence, du point de vue de la sécurité, avec les arbres de Merkle classiques.

Enfin, cette solution a été implémentée dans le projet SecBus, une architecture matérielle et logicielle ayant pour objectif de garantir la confidentialité et l'intégrité du contenu des mémoires externes d'un système à base de microprocesseurs. Un prototype de cette architecture a été réalisé et les résultats de l'évaluation de ce dernier sont donnés.

### **Abstract**

During the past few years, computer systems (*Cloud Computing*, embedded systems...) have become ubiquitous. Most of these systems use unreliable or untrusted storage (flash, RAM...) to store code or data. The confidentiality and integrity of these data can be threaten by hardware (spying on the communication bus between the processing component and the storage component) or software attacks. These attacks can disclose sensitive information to the adversary or disturb the behavior of the system. In this thesis, in the context of embedded systems, we focused on the attacks that threaten the confidentiality and integrity of data that are transmitted over the memory bus or that are stored inside the memory.

Several primitives used to protect the confidentiality and integrity of data have been proposed in the literature, including Merkle trees, a data structure that can protect the integrity of data including against replay attacks. However, these trees have a large impact on the performances and the memory footprint of the system.

In this thesis, we propose a solution based on variants of Merkle trees (hollow trees) and a modified cache management mechanism to greatly reduce the impact of the verification of the integrity. The performances of this solution have been evaluated both theoretically and in practice using simulations. In addition, a proof a security equivalence with regular Merkle trees is given.

Finally, this solution has been implemented in the SecBus architecture which aims at protecting the integrity and confidentiality of the content of external memories in an embedded system. A prototype of this architecture has been developed and the results of its evaluation are given.

## Introduction

À notre époque, les systèmes numériques sont devenus omniprésents dans notre vie quotidienne. Ils sont utilisés dans plusieurs domaines, comme le *Cloud Computing*, les systèmes embarqués ou les bases de données. Ces systèmes manipulent des informations sensibles qui sont stockées dans une zone mémoire non nécessairement fiable. Par conséquent, la protection de données résidant dans un espace de stockage non fiable ou non digne de confiance est un problème critique du point de vue de la sécurité.

Malheureusement, la sécurité de ces systèmes est vulnérable à certaines attaques telles que les exploitations logicielles et les attaques matérielles. Parmi les zones critiques de ces systèmes on peut citer le bus de communication entre le ou les composants de calcul (processeurs, SoC) et les composants de stockage (la mémoire vive, le disque dur, etc.). Un intrus accédant physiquement à ces systèmes, s'il parvient à espionner le bus de communication, peut récupérer le code exécuté et les données manipulées et obtenir ainsi de l'information potentiellement sensible (attaques passives). Il peut aussi modifier les informations qui transitent sur le bus ou le contenu des mémoires (attaques actives), ce qui peut perturber le bon fonctionnement du système.

Les utilisateurs de services en ligne, par exemple, s'attendent à ce que leurs données sensibles soient stockées et protégées dans un système informatique de confiance appartenant au fournisseur de services. Cependant, si cette hypothèse de confiance n'est pas fondée, et que des données sensibles sont divulguées, la réputation du fournisseur de services peut être sévèrement compromise. Le scandale provoqué par la vente sur eBay [1] d'un ordinateur ayant précédemment appartenu à une banque et contenant des données concernant des clients de la banque est une bonne illustration des conséquences possibles d'un défaut de protection de données sensibles.

À première vue, ceci semble être uniquement un problème de confidentialité et de contrôle d'accès aux données, que les techniques classiques de chiffrement, convenablement appliquées, devraient pouvoir résoudre. Cependant, lorsqu'un attaquant obtient un accès à un système informatique manipulant des données chiffrées, il peut faire plus qu'observer passivement le système. Il peut également altérer les données manipulées, même chiffrées et, dans certains cas, modifier ainsi le comportement du système afin de le forcer à révéler des informations sensibles. Dans [2], par exemple, un attaquant altère l'exécution du logiciel en modifiant à l'aveugle des instructions et des données chiffrées jusqu'à obtenir l'accès en clair à l'ensemble du système. Le chiffrement seul ne suffit pas toujours car il ne peut garantir que la confidentialité, pas l'intégrité.

Dans cette thèse, nous nous sommes focalisés sur les attaques menaçant la confidentialité et l'intégrité des données qui transitent sur le bus de communication avec la mémoire ou qui sont stockées dans celle-ci. Dans ce contexte, plusieurs plates-formes de calcul sécurisées (Best, XOM, AEGIS, SecBus etc.) ont été proposées afin de contrer ces menaces et d'assurer la confidentialité et / ou l'intégrité du contenu des mémoires dans les systèmes embarqués.

Comme nous le verrons, la protection de l'intégrité constitue le problème le plus difficile, essentiellement à cause de la dégradation des performances qu'elle entraı̂ne pour le système protégé. Les arbres de Merkle sont une solution bien connue pour tenter de réduire cet impact négatif en transformant un surcout linéaire (en la taille des données à protéger) en surcout logarithmique. Ils permettent de détecter les altérations de données causées par des attaques actives, y compris les attaques par rejeu, et sont utilisés, par exemple, pour protéger des bases de données ou des informations stockées sur disques durs. Cependant, appliqués dans leur version standard à la protection des mémoires externes d'un système informatique, ils dégradent tout de même significativement les performances. Nous avons étudié cette technique de contrôle d'intégrité et proposé des variantes afin de réduire l'impact sur les performances.

Cette thèse s'inscrit dans le cadre du projet SecBus, qui se différencie des autres platesformes de calcul sécurisées de la littérature par un certain nombre de principes fondateurs particuliers que nous présenterons. C'est donc l'architecture matérielle et logicielle SecBus qui nous servira de fil conducteur et d'exemple tout au long de ce manuscrit. Les contributions présentées, cependant, sont assez générales pour être adaptées aux autres architectures.

Dans un premier temps, nous présenterons les différents algorithmes de base de la cryptographie dont nous aurons besoin tout au long de ce manuscrit (chapitre 1). Nous introduirons ensuite le modèle de menace et les mécanismes de protection proposés dans la littérature, puis, nous étudierons en profondeur la méthode des arbres de Merkle et présenterons un panorama des plates-formes de calcul sécurisées intégrant des techniques de protection des mémoires externes (chapitre 2).

Dans un deuxième temps, nous proposerons une nouvelle méthode de protection basée sur les arbres de Merkle et étudierons l'impact d'utilisation de la mémoire cache sur la gestion de cohérence des arbres de Merkle (chapitre 3). Ensuite, nous présenterons l'architecture de SecBus qui intègre les contributions proposées (chapitre 4).

Enfin, dans le chapitre 5 nous présenterons les simulations effectuées pour vérifier que les méthodes de protection proposées fonctionnent correctement et pour les comparer, ainsi que les tests réalisés sur l'architecture de SecBus. Dans la deuxième partie du chapitre, nous appliquerons des techniques de modélisation formelle et de preuve sur les algorithmes utilisés dans la gestion des arbres de Merkle.

## **Chapitre 1**

# Éléments de cryptographie

## **Sommaire**

| 1.1 | Défini | tions                                  |

|-----|--------|----------------------------------------|

| 1.2 | Techn  | iques de chiffrement                   |

|     | 1.2.1  | Chiffrement symétrique                 |

|     | 1.2.2  | Chiffrement asymétrique                |

|     | 1.2.3  | Sécurité des techniques de chiffrement |

| 1.3 | Techn  | iques de vérification d'intégrité      |

|     | 1.3.1  | Fonctions de hachage                   |

|     | 1.3.2  | Paradoxe des anniversaires             |

|     | 1.3.3  | Conclusion                             |

La *cryptographie* est l'ensemble des techniques permettant de protéger des messages, c'està-dire de garantir certaines propriétés de sécurité tels que la confidentialité, l'intégrité, etc. À l'opposé, la *cryptanalyse* a pour objectif de casser ces propriété de sécurité. Ce sont deux disciplines de la *cryptologie*, la science du secret [3].

Dans ce chapitre, nous présenterons les différents algorithmes de base de la cryptographie dont nous aurons besoin par la suite tout au long de ce manuscrit.

### 1.1 Définitions

La cryptographie conçoit des primitives de sécurité afin de garantir quatre objectifs fondamentaux [4] : la confidentialité, l'intégrité, l'authentification et la non répudiation.

**Confidentialité** : garantir qu'une information n'est accessible qu'à ceux dont l'accès est autorisé.

**Intégrité** : empêcher une altération non autorisée (volontaire ou non) d'une information, ou être capable de détecter cette altération.

**Authentification**: vérifier l'identité des entités participant à un protocole afin d'autoriser l'accès à des ressources (réseaux, systèmes, applications, etc.).

Non répudiation : empêcher une entité de répudier une action déjà effectuée.

Auguste Kerckhoffs en 1883 [5,6] a énoncé plusieurs principes (connus maintenant sous le nom *principes de Kerckhoffs*) que doit respecter un bon système de chiffrement pour pouvoir être utilisé sur le terrain militaire :

- 1. Le système doit être matériellement, sinon mathématiquement, indéchiffrable ;

- 2. Il faut qu'il n'exige pas le secret, et qu'il puisse sans inconvénient tomber entre les mains de l'ennemi;

- 3. La clé doit pouvoir en être communiquée et retenue sans le secours de notes écrites, et être changée ou modifiée au gré des correspondants ;

- 4. Il faut qu'il soit applicable à la correspondance télégraphique;

- 5. Il faut qu'il soit portatif, et que son maniement ou son fonctionnement n'exige pas le concours de plusieurs personnes;

- 6. Enfin, il est nécessaire, vu les circonstances qui en commandent l'application, que le système soit d'un usage facile, ne demandant ni tension d'esprit, ni la connaissance d'une longue série de règles à observer.

Certains de ces principes, pourtant énoncés il y a plus d'un siècle, sont toujours d'actualité. Le principe numéro 2 est ainsi devenu un axiome de base dans la conception d'un bon algorithme de cryptographie : l'adversaire doit pouvoir connaître tous les détails de l'algorithme sans que la sécurité du système l'utilisant (reposant sur un secret nommé clé) ne soit remise en cause.

L'adversaire (aussi nommé attaquant ou cryptanalyste) essaie quant à lui de casser les propriétés de sécurité en menant des attaques. Ces attaques peuvent être passives (il écoute simplement les échanges et essaie de récupérer de l'information normalement secrète) ou actives (l'adversaire va altérer les échanges).

## 1.2 Techniques de chiffrement

Le *chiffrement* (noté E) est un processus qui transforme un message en clair (noté P) en un message chiffré (noté C) en utilisant un secret (nommé clé et noté  $K_e$ ):

$$E_{K_c}(P) = C (1.1)$$

Le déchiffrement (noté D) est l'opération qui permet de récupérer le message en clair à partir d'un message chiffré en utilisant une clé (notée  $K_d$ ):

$$D_{K_d}(C) = P (1.2)$$

Le message chiffré n'apporte aucune information sur le message en clair pour quelqu'un qui ne connaît pas le secret nécessaire pour le déchiffrer  $(K_d)$ . Le chiffrement est donc utilisé principalement pour garantir la confidentialité d'une information.

Il existe deux catégories d'algorithmes de chiffrement :

— Les algorithmes symétriques pour lesquels  $K_e = K_d = K$ . La clé unique K, souvent nommée clé secrète, est utilisée pour le chiffrement et le déchiffrement. Dans la figure 1.1, Alice et Bob veulent communiquer entre eux à travers une canal non sécurisée. Ils choisissent tout d'abord une clé secrète K. Ensuite, Alice chiffre le message en clair à l'aide d'un algorithme de chiffrement symétrique et la clé K, et envoie le message chiffré à Bob. Bob reçoit le message chiffré et utilise la clé K afin de retrouver le message en clair.

FIGURE 1.1 – Chiffrement symétrique

— Les algorithmes asymétriques pour lesquels  $K_e \neq K_d$ . Il y a donc deux clés différentes : une dite publique (qui peut être connue de tous) utilisée par l'algorithme de chiffrement  $(K_e)$ , et une dite privée (mathématiquement associée à la clé publique) utilisée par l'algorithme de déchiffrement  $(K_d)$ . Reprenons l'exemple d'Alice et Bob, présenté par la figure 1.2, où Alice veut envoyer un message confidentiel à Bob. Tout d'abord, Bob doit générer une paire de clés publique et privée  $(K_e, K_d)$  et transmettre la clé publique  $K_e$  à Alice à travers le canal non sécurisée. Ensuite, Alice chiffre son message avec  $K_e$  et l'envoie à Bob. Enfin, Bob utilise  $K_d$  pour déchiffrer le message.

Chacune de ces catégories a des avantages et des inconvénients que nous présenterons par la suite.

## 1.2.1 Chiffrement symétrique

Les algorithmes de chiffrement symétriques se décomposent en deux catégories : les algorithmes de chiffrement de flux et les algorithmes de chiffrement par bloc.

FIGURE 1.2 – Chiffrement asymétrique

#### 1.2.1.1 Chiffrement de flux

Le concept de chiffrements de flux a été introduit par Gilbert Vernam [7] en 1917. Ces algorithmes permettent de chiffrer un flot de symboles en clair (par exemple un flux d'octets ou même un flux de bits) en utilisant un flot de clés (préparé au préalable) de la même taille.

Le déchiffrement s'effectue de la même façon, symbole par symbole, pour récupérer le message en clair à partir du flux chiffré et du même flot de clés.

Un algorithme de chiffrement de flux est composé de deux parties : un générateur de flux de clés et un algorithme réalisant le chiffrement d'un symbole en clair à l'aide d'un symbole de clé (par exemple un simple opérateur *ou exclusif*). Le générateur de flux de clés fournit un flux de bits  $k_1, k_2, ..., k_n$ , et l'opérateur xor réalise l'opération de chiffrement en combinant les bits de la clé (appelées souvent masque) avec les bits du message en clair  $p_1, p_2, ..., p_n$ , pour donner les bits du message chiffré  $c_1, c_2, ..., c_n$ , c'est-à-dire :

$$c_i = p_i \oplus k_i \quad \forall i \in [1, n] \tag{1.3}$$

Dans ce cas, l'opération de déchiffrement s'effectue de la même manière :

$$p_i = c_i \oplus k_i \quad \forall i \in [1, n] \tag{1.4}$$

**1.2.1.1.1 Masque jetable** (*One Time Pad*, OTP) Le masque jetable est une technique du chiffrement de flux qui combine le message en clair avec une clé présentant les caractéristiques suivantes : sa taille doit être au moins aussi longue que le message en clair, elle doit être totalement aléatoire et elle ne doit être utilisée qu'une seule fois (d'où le nom de masque jetable).

Claude Shannon [8] a prouvé, en 1949, qu'en respectant ces trois règles concernant la clé, le système offre une sécurité théorique absolue. Par contre, la mise en œuvre du masque jetable est difficile en pratique. En effet, la génération de flux de clés réellement aléatoires nécessite

des moyens complexes. De même, la longueur et l'utilisation unique de la clé sont deux points difficiles qui rendent l'implémentation du masque jetable inabordable.

Dans la pratique, les algorithmes de chiffrement de flux s'inspirent du masque jetable en générant le flux de clés à l'aide d'un algorithme de génération de nombres pseudo-aléatoires utilisant une graine (clé) de petite taille. Cependant, ces algorithmes ne sont plus inconditionnellement sûrs vu que la clé n'est plus réellement aléatoire. Par la suite, nous distinguerons deux catégories d'algorithmes de chiffrement de flux : les algorithmes de chiffrement de flux synchrones et les algorithmes de chiffrement de flux auto-synchrones.

**1.2.1.1.2** Chiffrement de flux synchrone Un algorithme de chiffrement de flux synchrone est un algorithme où la génération du masque est indépendante du message en clair ou du message chiffré. Le masque est généré à partir d'une clé secrète  $k_i$  et d'un état interne  $\sigma_i$ , comme le montre les équations suivantes :

$$\sigma_{i+1} = f(\sigma_i, k) \tag{1.5}$$

$$z_i = g(\sigma_i, k) \tag{1.6}$$

où  $\sigma_0$  est l'état initial de l'algorithme qui peut dépendre de la clé k, f la fonction qui permet de calculer l'état suivant, et g la fonction qui calcule le masque  $z_i$ . L'opération de chiffrement est présentée avec l'équation suivante :

$$c_i = h(z_i, p_i) \tag{1.7}$$

où h est la fonction de sortie (en général l'opérateur *ou exclusif*) qui combine le masque et le message en clair  $p_i$  pour produire le message chiffré  $c_i$ . La figure 1.3 présente le schéma de chiffrement et de déchiffrement.

L'émetteur et le récepteur doivent être synchronisés. En effet, une perte de synchronisation (insertion ou suppression d'un bit par exemple dans le flux chiffré) empêche tout déchiffrement futur. En revanche, une modification d'un bit dans le texte chiffré n'affecte pas le déchiffrement des autres bits du message chiffré.

Un avantage de cette catégorie du chiffrement de flux concerne la propagation d'erreur. Si une erreur s'est produite dans un ou plusieurs bits durant la transmission, seul le résultat du déchiffrement des bits modifiés sera impacté. Malheureusement, d'un point de vue de la sécurité, cet avantage devient un inconvénient. En effet, un adversaire qui modifie des bits dans le message chiffré est capable de connaître l'impact sur le message en clair.

**1.2.1.1.3** Chiffrement de flux auto-synchrone Un algorithme de chiffrement de flux auto-synchrone est un algorithme où le masque est généré à partir d'une clé secrète  $k_i$  et d'un nombre

FIGURE 1.3 – Chiffrement de flux synchrone

fixe de bits des messages chiffrés précédemment. Les équations suivantes décrivent les opérations de chiffrement :

$$\sigma_i = (c_{i-t}, c_{i-t+1}, ..., c_{i-1}) \tag{1.8}$$

$$z_i = g(\sigma_i, k) \tag{1.9}$$

$$c_i = h(z_i, p_i) \tag{1.10}$$

où  $\sigma_0 = (c_{-t}, c_{-t+1}, ..., c_{-1})$  est l'état initial de l'algorithme, k est la clé, g la fonction qui calcule le masque  $z_i$  et h est la fonction de sortie (en général un opérateur *ou exclusif*) qui combine le masque et le message en clair  $p_i$  pour produire le message chiffré  $c_i$ . La figure 1.4 présente le schéma de chiffrement et de déchiffrement.

La synchronisation entre l'émetteur et le récepteur est automatique (d'où le nom d'algorithme auto-synchrone). En effet, durant le déchiffrement et après la réception de n bits du chiffré, le générateur de flux de clés sera automatiquement synchrone avec le générateur de flux de clés utilisé durant le chiffrement. L'évolution de l'état interne du générateur de flux de clés ne dépend que des n bits du texte chiffré précédemment et donc le déchiffrement est automatiquement correct au bout d'un laps de temps en cas de suppression ou d'insertion d'un bit dans le texte chiffré. De même, si une erreur s'est produite dans un ou plusieurs bits durant la transmission, seul le déchiffrement des bits modifiés sera impacté et donnera des résultats erronés (le nombre de bits impactés est égal au nombre de bits utilisés comme état interne).

FIGURE 1.4 – Chiffrement de flux auto-synchrone

### 1.2.1.2 Chiffrement par bloc

Un algorithme de chiffrement par bloc prend en entrées un message en clair de taille fixe, une clé et produit un message chiffré de taille fixe (en général de la même taille que celle du message en clair). La taille du message en clair et du message chiffré est un paramètre de l'algorithme, par exemple 64 bits pour DES, 128 bits pour AES.

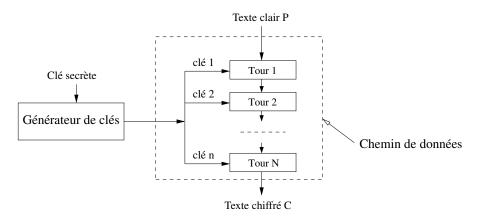

**1.2.1.2.1 Structure du chiffrement par bloc** Un algorithme de chiffrement par bloc est divisé en deux parties : le générateur de clés (*key schedule*) et le chemin de données (figure 1.5). Le chemin de données inclut deux opérations de base introduites par Shannon [8] qui sont la *confusion* (c'est-à-dire rendre la relation entre la clé et le texte chiffré le plus complexe possible) et la *diffusion* (c'est-à-dire permettre à chaque bit de texte clair d'avoir une influence sur une grande partie du texte chiffré). Ce chemin de données est le plus souvent composé d'une fonction (ou un ensemble de fonctions) appelée un tour (*round*) qui se répète un nombre fixe de fois. Il prend le texte en clair en entrée, et délivre en sortie le texte chiffré après le nombre fixe de tours.

Le générateur de clés traite une clé secrète et en déduit les sous-clés de tours utilisées à chaque tour du chemin de données. La dérivation de la clé est nécessaire pour ajouter de la confusion : elle augmente la dépendance de chaque bit du texte chiffré sur tous les bits de la clé secrète.

Le premier tour du chemin de données prend le texte en clair et la clé du premier tour comme entrées, puis les tours suivants prennent la sortie du tour précédent et la clé du tour correspondant comme entrées.

Le paragraphe suivant décrit l'algorithme de chiffrement par bloc le plus utilisé actuelle-

FIGURE 1.5 – Structure du chiffrement par bloc

ment et standardisé par le NIST (National Institute of Standard and Technology) : AES (Advanced Encryption Standard).

**1.2.1.2.2 Exemple : AES** L'algorithme Rijndael [9] a été développé par Joan Daemen et Vincent Rijmen suite à un appel de NIST afin de normaliser le chiffrement par bloc. Il a été adopté comme nouvelle norme après un processus de normalisation de cinq ans. Il a été ensuite appelé AES (*Advanced Encryption Standard*) et a remplacé le célèbre algorithme DES (*Data Encryption Standard*) [10] pour lequel la longueur de clé (56 bits) est devenue trop petite pour résister à une attaque par force brute [11] (cette attaque consiste à essayer successivement toutes les clés possibles).

L'algorithme AES traite des blocs de données de 128 bits en utilisant des clés de chiffrement de longueur de 128, 192 ou 256 bits. Un tour dans AES est défini par une série d'opérations (AddRoundKey, SubBytes, ShiftRows et MixColumns). Le nombre de tours utilisés dépend de la taille de la clé : 10 dans le cas d'une clé de 128 bits, 12 pour une clé de 192 bits et 14 pour une clé de 256 bits.

Un des objectifs d'AES était d'être implémentable efficacement aussi bien en logiciel qu'en matériel. De nombreuses implémentations matérielles ont été proposées aussi bien sur cible FPGA qu'ASIC. Par exemple, l'implémentation d'AES sur ASIC (technologie  $0.18\mu m$  CMOS), présentée dans [12], montre que le chiffrement d'un bloc de 128 bits est réalisé en 11 cycles d'horloges à une fréquence de 330 MHz, ce qui a donné un débit de 3.84 Gbits/s.

**1.2.1.2.3 Modes d'opération** Un mode d'opération décrit la construction permettant de chiffrer un message dont la taille est différente de celle de l'algorithme de chiffrement par bloc choisi. De nombreux modes d'opération existent [13]. Nous allons présenter les principaux : ECB, CBC, CFB, OFB et compteur.

Nous utiliserons les notations suivantes :

- n est la taille de bloc de l'algorithme choisi

- K est la clé secrète

FIGURE 1.6 – Chiffrement par bloc en mode ECB

- $E_K$  est l'opération de chiffrement d'un bloc avec la clé K

- $D_K$  est l'opération de déchiffrement d'un bloc avec la clé K

On suppose également que la longueur des messages à chiffrer est multiple de n. Si ce n'est pas le cas, un algorithme de remplissage (padding) est utilisé pour étendre le message.

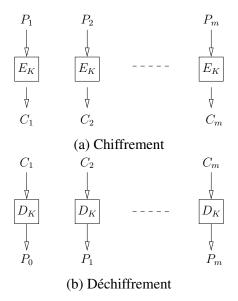

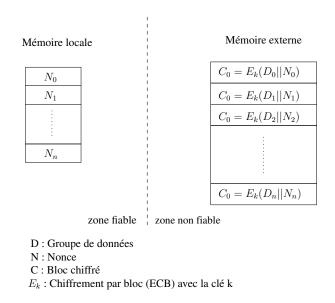

**Electronic CodeBook (ECB)** Le fonctionnement du mode ECB est simple. Le message en clair P est découpé en blocs  $P_1, P_2, ..., P_m$  de taille n (celle de l'algorithme de chiffrement). Chacun de ces blocs est chiffré indépendamment des autres. Le résultat du chiffrement donne les blocs chiffrés  $C_1, C_2, ..., C_m$  qui constituent le message chiffré C:

$$P = P_1 || P_2 || \dots || P_m \tag{1.11}$$

$$C = C_1 \| C_2 \| \dots \| C_m \tag{1.12}$$

pour l'opération de chiffrement :

$$C_i = E_K(P_i) \quad \forall i \in [1, m] \tag{1.13}$$

et pour l'opération de déchiffrement :

$$P_i = D_K(C_i) \quad \forall i \in [1, m] \tag{1.14}$$

La figure 1.6 présente les deux opérations de chiffrement et de déchiffrement du mode ECB.

Le principal inconvénient du mode ECB, d'un point de vue sécurité, est que le chiffrement de deux blocs identiques du message en clair, avec la même clé, produit des blocs chiffrés identiques. Un message contenant des motifs répétitifs ne doit pas être chiffré avec un tel mode

parce que l'adversaire peut en déduire lorsque la même information se produit deux fois. Une solution pour améliorer la sécurité du mode ECB est d'inclure des bits aléatoires dans chaque bloc du texte clair avant le chiffrement [4].

Dans ce mode, les opérations de chiffrement et de déchiffrement sont entièrement parallélisables, ce qui permet de rajouter autant de fonctions de chiffrement/déchiffrement que nécessaire, et donc d'augmenter les performances. Un autre avantage du mode ECB est que la propagation des erreurs est limitée. Si un bit du message chiffré est erroné, seul le déchiffrement du bloc chiffré correspondant est impacté. Par contre l'insertion ou la suppression d'un bit dans le message chiffré affectera toute la suite du message en clair.

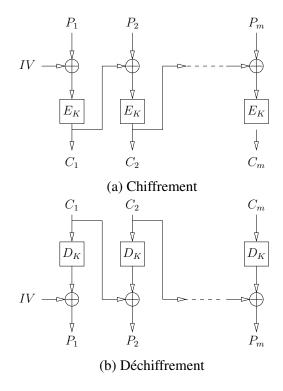

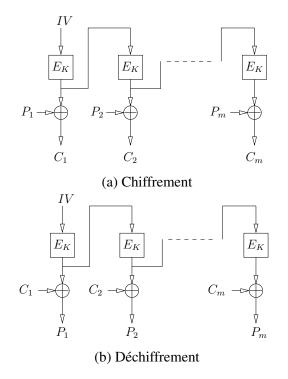

**Cipher-Block Chaining (CBC)** Dans le mode CBC, chaque bloc  $P_i$  du message en clair P est combiné avec le bloc chiffré précédent  $C_{i-1}$  (ou avec un Vecteur d'Initialisation (noté IV) choisi aléatoirement dans le cas du premier bloc  $(P_1)$ ) en utilisant l'opérateur xor, afin d'obtenir le bloc chiffré  $C_i$ , comme l'illustre l'équation suivante :

$$C_0 = IV (1.15)$$

$$C_i = E_K(C_{i-1} \oplus P_i) \quad \forall i \in [1, m]$$

$$\tag{1.16}$$

et pour le déchiffrement :

$$C_0 = IV (1.17)$$

$$P_i = C_{i-1} \oplus D_K(C_i) \quad \forall i \in [1, m]$$

$$\tag{1.18}$$

La figure 1.7 présente les deux schémas de chiffrement et de déchiffrement du mode CBC.

L'avantage principal du mode CBC par rapport au mode ECB est de rendre le chiffrement d'un bloc dépendant du chiffrement précédent. Cela permet de masquer les motifs présents dans le message en clair. Cependant, un message complet chiffré deux fois en mode CBC (en utilisant la même clé) produira le même message chiffré si le même IV est utilisé. Une façon de surmonter un tel inconvénient est de changer l'IV pour chaque message chiffré. Le vecteur d'initialisation doit donc être généré de manière aléatoire pour chaque message à chiffrer.

Deux blocs en clair identiques donneront un chiffré identique que si les chiffrés précédents sont identiques. Cette situation (collision, c'est-à-dire deux blocs chiffrés identiques permettant de savoir si les deux blocs en clair suivant immédiatement sont identiques ou non) est facilement détectable par l'adversaire. Les blocs chiffrés étant normalement indistinguables de blocs aléatoires, la probabilité de survenue d'une collision est donnée par le paradoxe des anniversaires et dépend directement de la taille d'un bloc (n). Cette probabilité est de 0,5 au bout de  $2^{n/2}$  blocs chiffrés. Il faut donc, lors de l'utilisation du mode CBC, changer la clé lorsque l'on s'approche de cette limite afin d'éviter la survenue d'une collision qui pourrait laisser fuir de l'information sur les messages en clair.

FIGURE 1.7 – Chiffrement par bloc en mode CBC

L'opération de chiffrement du mode CBC ne peut pas être parallélisé entre les différents blocs constituant un même message car le chiffrement d'un bloc dépend du résultat du chiffrement du bloc précédent. Par contre, l'opération de déchiffrement peut être parallélisée car toutes les informations nécessaires sont disponibles : les deux blocs chiffrés (courant et précédent) et la clé.

Le mode CBC a un effet limité dans la propagation des erreurs. Si un bit du message chiffré est erroné, il affecte le déchiffrement du bloc en question ainsi que du bloc suivant.

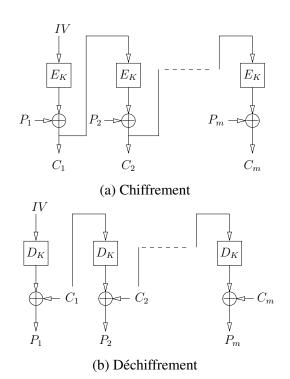

**Cipher FeedBack** (**CFB**) Le mode CFB permet d'utiliser un algorithme de chiffrement par bloc comme un algorithme de chiffrement de flux auto-synchrone. La sortie de l'algorithme est le bloc chiffré  $C_i$  et l'état interne  $(\sigma_i)$  est défini par le bloc chiffré précédent  $C_{i-1}$ . Un tel mode nécessite un IV (la graine jetable  $\sigma_0$ ) pour initialiser  $\sigma_i$ . Les équations suivantes définissent les opérations de chiffrement du mode CFB :

$$C_0 = IV (1.19)$$

$$\sigma_i = E_K(C_{i-1}) \quad \forall i \in [1, m] \tag{1.20}$$

$$C_i = \sigma_i \oplus P_i \quad \forall i \in [1, m] \tag{1.21}$$

FIGURE 1.8 – Chiffrement par bloc en mode CFB

et pour le déchiffrement :

$$C_0 = IV (1.22)$$

$$\sigma_i = D_K(C_{i-1}) \quad \forall i \in [1, m] \tag{1.23}$$

$$P_i = \sigma_i \oplus C_i \quad \forall i \in [1, m] \tag{1.24}$$

La figure 1.8 présente les deux schémas de chiffrement et de déchiffrement du mode CFB.

Le mode CFB bénéficie de la synchronisation automatique comme dans le chiffrement de flux auto-synchrone. Cette propriété permet de limiter la propagation des erreurs lors de la suppression ou de l'insertion d'un bit dans le message chiffré. De plus, la taille du message à chiffrer n'a pas besoin d'être un multiple de n contrairement aux modes ECB ou CBC.

Output FeedBack (OFB) Ce mode est similaire au chiffrement de flux synchrone et donc bénéficie des mêmes propriétés comme la non propagation des erreurs. Aussi, comme dans le mode CFB, la taille du message à chiffrer n'a pas besoin d'être un multiple de n.

Les équations suivantes définissent les opérations de chiffrement du mode OFB :

$$\sigma_0 = IV \tag{1.25}$$

FIGURE 1.9 – Chiffrement par bloc en mode OFB

$$\sigma_i = E_K(\sigma_{i-1}) \quad \forall i \in [1, m]$$

(1.26)

$$C_i = \sigma_i \oplus P_i \quad \forall i \in [1, m]$$

(1.27)

et pour le déchiffrement :

$$\sigma_0 = IV \tag{1.28}$$

$$\sigma_i = D_K(\sigma_{i-1}) \quad \forall i \in [1, m]$$

(1.29)

$$P_i = \sigma_i \oplus C_i \quad \forall i \in [1, m] \tag{1.30}$$

La figure 1.9 présente les deux schémas de chiffrement et de déchiffrement du mode OFB.

Dans le mode OFB, le calcul des masques peut être effectué en avance parce qu'il dépend uniquement du vecteur d'initialisation, et donc, une fois les masques calculés, le chiffrement ou le déchiffrement peuvent effectués très rapidement (l'opérateur *xor*).

**Mode compteur** Le mode compteur permet aussi, comme les modes CFB et OFB, d'utiliser un algorithme de chiffrement par bloc comme un algorithme de chiffrement de flux. Aussi, la taille du message à chiffrer n'a pas besoin d'être un multiple de n.

FIGURE 1.10 – Chiffrement par bloc en mode compteur

Le mode compteur est initialisé par un Nounce (nombre aléatoire, noté N) et incrémenté pour chaque bloc en clair. Les équations suivantes définissent les opérations de chiffrement du mode compteur :

$$\sigma_i = E_K(N+i) \quad \forall i \in [1, m] \tag{1.31}$$

$$C_i = \sigma_i \oplus P_i \quad \forall i \in [1, m] \tag{1.32}$$

et pour le déchiffrement :

$$\sigma_i = E_K(N+i) \quad \forall i \in [1, m] \tag{1.33}$$

$$P_i = \sigma_i \oplus C_i \quad \forall i \in [1, m] \tag{1.34}$$

La figure 1.10 présente les deux schémas de chiffrement et de déchiffrement du mode compteur.

Le mode compteur possède deux atouts principaux d'un point de vue des performances :

- le chiffrement ou le déchiffrement de deux blocs peuvent être parallélisés,

- la partie la plus longue de l'opération de chiffrement ou de déchiffrement (calcul de  $E_k(N=i)$ ) ne dépend pas du bloc en clair ou du bloc chiffré et peut donc être réalisé en amont.

#### **1.2.1.3** Conclusion

Comme il sera présenté dans la section 1.3, les algorithmes de chiffrement par bloc peuvent être utilisés comme bases pour construire d'autres algorithmes afin remplir d'autres objectifs de sécurité que la confidentialité, comme par exemple assurer l'intégrité et d'authentification de données.

Les algorithmes de chiffrement symétriques posent le problème du partage de secret (ici la clé). En effet, si deux entités veulent s'échanger des messages chiffrés, ces deux entités doivent disposer du même secret. Elles doivent donc s'être mises d'accord sur ce secret et se l'être échangé sur un canal sécurisé en amont de la communication. De plus le nombre de clés à gérer augmente de façon quadratique avec le nombre d'entités avec lesquelles on souhaite communiquer. Les algorithmes de chiffrement asymétriques permettent de palier ces deux problèmes.

### 1.2.2 Chiffrement asymétrique

Contrairement aux algorithmes de chiffrement symétriques, les algorithmes de chiffrement asymétrique utilisent deux clés différentes : la clé de chiffrement  $K_e$ , appelée clé publique car elle peut être transmise sur un canal non sécurisé et ne nécessite pas d'être gardée secrète, et la clé de déchiffrement  $K_d$ , appelée clé privée puisque qu'elle permet le déchiffrement et donc ne doit être connue que du destinataire du message chiffré (figure 1.2).

La notion du chiffrement asymétrique (ou cryptosystème à clé publique) a été introduite par Wilfred Diffie et Martin Hellman en 1976 [14]. Ces algorithmes sont basés sur la difficulté à résoudre certains problèmes mathématiques complexes et en particulier sur des fonctions à sens unique à trappe. Une fonction f(x) = y est considérée comme une fonction à sens unique si pour tout x appartenant à l'ensemble de définition de la fonction, il est simple de calculer f(x), alors qu'en pratique, connaissant y, il est difficile de trouver x tel que y = f(x) sans connaître une information supplémentaire : la trappe (secret).

Un exemple de problème mathématique complexe utilisé est la factorisation de grands nombres : il est facile de calculer la multiplication de deux grands nombres, mais la fonction inverse, la factorisation est très difficile. L'algorithme à clé publique le plus célèbre est RSA [15] (pour Rivest Shamir Adleman, les noms de ses inventeurs). Il est basée sur ce problème de factorisation.

Le principal avantage du chiffrement asymétrique par rapport au chiffrement symétrique est le fait qu'il n'a pas besoin de partager un secret avant d'établir la communication, la clé de chiffrement pouvant être publique. Néanmoins, il est nécessaire d'assurer l'authenticité de cette clé de chiffrement sinon une attaque de l'homme du milieu (man-in-the-middle) est réalisable. Dans une telle attaque, un adversaire qui surveille un canal non sécurisé, intercepte un message (M) et éventuellement certaines données (X) utiles à des fins de sécurité, les analyse et les échange par des données choisies (M', X').

Par exemple, Alice et Bob veulent échanger des données chiffrées sur un canal non sécurisé qui est écouté par Ève, l'adversaire. Bob envoie tout d'abord sa clé publique à Alice via ce

canal. Ève peut alors intercepter cette clé et la remplacer à la volée par sa propre clé publique. Alice chiffre alors ses messages avec ce qu'elle pense être la clé publique de Bob mais qui est en réalité la clé publique d'Ève. Cette dernière peut donc déchiffrer tous les messages (à l'aide de sa clé privée correspondante) et éventuellement les rechiffrer avec la vraie clé publique de Bob pour que ce dernier ne s'aperçoive de rien.

Ce problème peut être atténué à l'aide d'une infrastructure de gestion de clés (*Public Key Infrastructure*, PKI) qui émet des certificats pour valider l'authenticité de clés. Néanmoins, elle ne fait que déplacer le problème au niveau de l'authenticité de la clé ayant signé les certificats.

En outre, les algorithmes de chiffrement asymétrique sont très lents, car ils sont basés sur des problèmes mathématiques complexes. Par exemple, dans le déchiffrement matériel de RSA prend jusqu'à 260.000 cycles avec une fréquence de 100 MHz et une taille de clé de 1024 bits [16].

### 1.2.3 Sécurité des techniques de chiffrement

Les attaques menées contre un système de chiffrement peuvent avoir deux objectifs : la récupération de clé ou du message en clair.

L'objectif de la première attaque est de récupérer la clé secrète ou la clé privée utilisée respectivement dans un algorithme de chiffrement symétrique ou dans un chiffrement asymétrique. L'attaque la plus pratique est l'attaque par force brute. Elle consiste à essayer toutes les clés possibles jusqu'à trouver la bonne clé permettant de récupérer le texte en clair à partir de n'importe quel texte chiffré. Par conséquent, plus la taille de la clé est longue, plus la complexité de cette attaque est grande.

Le but des attaques de récupération de message est d'obtenir des informations sur les textes clairs en observant les textes chiffrés. Un cryptosystème est à l'abri contre la récupération du message s'il est sémantiquement sécurisé, ce qui signifie qu'un adversaire n'est pas en mesure de savoir si un texte chiffré donné est le chiffrement d'un texte clair ou d'un autre.

Les objectifs de l'adversaire, définis plus haut, sont pratiquement basés sur les attaques passives qui pourraient être classées en considérant les informations dont l'adversaire dispose. Les définitions suivantes sont issues de [4]:

- 1. Attaque par texte chiffré seul (*ciphertext-only attack*) : l'attaquant ne dispose que de messages chiffrés.

- 2. Attaque par texte clair connu (*known-plaintext attack*) : l'attaquant dispose d'une série de messages clairs et des chiffrés correspondants.

- 3. Attaque par texte clair choisi (*chosen-plaintext attack*) : l'attaquant peut obtenir les chiffrés des messages en clair qu'il veut.

- 4. Attaque par texte clair choisi adaptative (*adaptative chosen-plaintext attack*): identique à une attaque par texte clair choisi sauf que le choix des textes clairs par l'attaquant peut dépendre des textes chiffrés reçus précédemment.

- 5. Attaque par texte chiffré choisi (*chosen-ciphertext attack*) : l'attaquant a accès à une machine de déchiffrement. Il peut obtenir les messages en clair correspondants aux messages chiffrés qu'il veut (excepté le message qu'il essaie de déchiffrer).

- 6. Attaque par texte chiffré choisi adaptative (*adaptative chosen-ciphertext attack*): identique à une attaque par texte chiffré choisi sauf que le choix des messages chiffrés soumis à l'oracle de déchiffrement par l'attaquant peut dépendre des messages en clair qu'il a reçus précédemment.

La robustesse d'un système de chiffrement est évaluée en respectant le premier et le deuxième principe de Kerckhoffs qui indiquent qu'un algorithme doit être incassable en pratique (sinon en théorie est incassable) et qu'il doit être connu du public.

Bien utilisé, le chiffrement permet de garantir la confidentialité d'informations contre des attaques passives. Néanmoins, le chiffrement seul ne peut pas garantir l'intégrité et l'authentification des données. Il est donc insuffisant dès que l'adversaire est en mesure d'altérer les messages, notamment via des attaques actives.

## 1.3 Techniques de vérification d'intégrité

Les techniques de vérification d'intégrité permettent de détecter des altérations, volontaires ou non, sur des données. Pour assurer l'intégrité des données, il faut avoir la capacité de détecter toute manipulation (insertion, suppression ou modification) des données par des tiers non autorisés.

Les mécanismes de vérification d'intégrité utilisent des algorithmes principalement basés sur des fonctions de hachage. Par la suite nous présenterons ces fonctions et leurs caractéristiques.

## 1.3.1 Fonctions de hachage

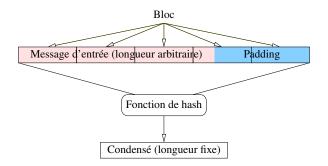

Une fonction de hachage h, également appelée une fonction de hachage à sens unique (*one-way hash function*), est une fonction qui possède au moins de deux propriétés :

- Compression (compression) : h calcule un condensé cryptographique (appelé hash) de longueur fixe à partir d'un message d'entrée de longueur arbitraire x.

- Facilité de calcul (ease of computation) : étant données h et une entrée x, il est facile de calculer h(x).

Les fonctions de hachage sont caractérisées par leur résistance à trois propriétés de sécurité [4] :

- **Résistance à la préimage** : étant donné un condensé cryptographique y, il est difficile de forger un message x tel que y = h(x).

- **Résistance à la seconde préimage** : étant donné un message x et son condensé cryptographique y = h(x), il est difficile de trouver un autre message  $x' \neq x$  tel que

FIGURE 1.11 – Fonction de hachage

$$h(x) = h(x') = y$$

.

— **Résistance aux collisions** : il est difficile de trouver deux messages différents x et x' ayant le même condensé cryptographique h(x) = h(x').

Les fonctions de hachage sont divisées en deux catégories :

- Codes de détection de modification (modification detection codes, MDC) basés sur des fonctions de hachage sans clé et dont l'objectif est de garantir l'intégrité d'un message.

- Codes d'authentification de message (message authentication codes, MAC) basés sur des fonctions de hachage avec clé et dont l'objectif est de garantir l'intégrité et l'authentification de la source d'un message.

#### 1.3.1.1 Code de détection de modification

Les fonctions de hachage sans clé possèdent une seule entrée de longueur quelconque, le message à hacher, et produisent un condensé de longueur fixe 1.11.

Ce type de fonctions est divisé en deux catégories :

- Fonctions de hachage à sens unique (*one-way hash function, OWHF*) qui sont caractérisées par les deux propriétés de compression et facilité de calcul, et deux propriétés de sécurité : résistance à la préimage et résistance à la seconde préimage.

- Fonctions de hachage résistant aux collisions (*collision resistant hash function*, *CRHF*) qui sont caractérisées par les deux propriétés de compression et facilité de calcul, et deux propriétés de sécurité : résistance à la seconde préimage et résistance aux collisions.

**1.3.1.1.1 Exemple : SHA** L'Agence de Sécurité Nationale américaine (NSA) a créé, en 2002, les fonctions SHA (*Secure Hash Algorithm*) [17] et qui ont été publiées par le NIST. Ces fonctions sont regroupées en une série de cinq fonctions de hachage (SHA-1, SHA-224, SHA-256, SHA-384 et SHA-512) résistantes aux collisions.

La fonction de hachage SHA-1 est l'une des fonctions de hachage les plus couramment utilisées. Par exemple, elle est utilisée dans des protocoles tels que SSL (Secure Sockets Layer), TLS (Transport Layer Security) et IPSec (Internet Protocol Security). SHA-1 prend en entrée un message M inférieur à  $2^{64}$  bits et traite des blocs de 512 bits et, produit en sortie un condensé de 160 bits.

FIGURE 1.12 – Fonction de HMAC

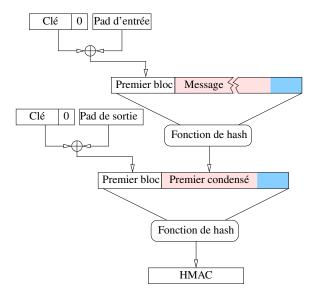

### 1.3.1.2 Code d'authentification de message

Un algorithme de MAC (code d'authentification de message), ou fonction de hachage à clé, est une famille de fonctions  $h_k$  paramétrés par une clé secrète k avec les propriétés suivantes :

- $h_k$  est une fonction de hachage (propriétés de compression et de facilité de calcul)

- étant donnés zéro ou plus couples messages-MAC  $(x_i, h_k(x_i))$ , il doit être impossible de calculer le MAC d'un message  $x \neq x_i$  sans connaître la clé k (propriété de résistance à la falsification)

Une fonction de hachage peut être transformée en MAC en combinant les messages d'entrée avec une clé secrète (comme par exemple avec la construction HMAC, figure 1.12).