## Novel memory and I/O virtualization techniques for next generation data-centers based on disaggregated hardware

Maciej Bielski

### ▶ To cite this version:

Maciej Bielski. Novel memory and I/O virtualization techniques for next generation data-centers based on disaggregated hardware. Hardware Architecture [cs.AR]. Université Paris Saclay (COmUE), 2019. English. NNT: 2019SACLT022. tel-02464021

## HAL Id: tel-02464021 https://pastel.hal.science/tel-02464021

Submitted on 2 Feb 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nouvelles techniques de virtualisation de la mémoire et des entrées-sorties vers les périphériques pour les prochaines générations de centres de traitement de données basés sur des équipements répartis déstructurés

Thèse de doctorat de l'Université Paris-Saclay préparée à Télécom ParisTech

Ecole doctorale n°580 Sciences et Technologies de l'Information et de la Communication (STIC) Spécialité de doctorat: Informatique

Thèse présentée et soutenue à Biot Sophia Antipolis, le 18/03/2019, par

### M. MACIEJ BIELSKI

#### Composition du Jury:

| Frédéric Pétrot |

|-----------------|

|-----------------|

Professeur, Université Grenoble Alpes, ENSIMAG, TIMA/SLS Rapporteur

Alain Tchana

Professeur, Université Côte d'Azur, CNRS/I3S Rapporteur

Vania Marangozova-Martin

Maîtresse de conférences, Université Grenoble Alpes, LIG Examinatrice

Melek Önen

Maîtresse de conférences, EURECOM Examinatrice

Laurent Pautet

Professeur, Telecom ParisTech Examinateur

Alvise Rigo

Ingénieur R&D, Virtual Open Systems Examinateur

Guillaume Urvoy-Keller

Professeur, Université Côte d'Azur, CNRS/I3S Examinateur

Renaud Pacalet

Directeur d'études, Telecom ParisTech Directeur de thèse

### Acknowledgments

The work presented in this dissertation was carried out by the author when he was an employee of Virtual Open Systems. This work was supported by the *dReDBox* project. This project has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement No. 687632. This work reflects only authors' view and the EC is not responsible for any use that may be made of the information it contains.

At the end of my doctorate I would like to acknowledge everyone who helped me to reach this stage of my education track.

I would like to thank teachers and professors who introduced me to science and engineering and somehow made me interested in exploring them on my own. In particular, I would like to thank Professor Renaud Pacalet for supervising my PhD and providing substantial help in improving the thesis manuscript. Several improvements was also suggested by Professor Frédéric Pétrot and Professor Alain Tchana, who spent their time on reviewing the manuscript for which I am immensely grateful. I would also like to thank fellow members of LabSoC, including Professor Ludovic Apvrille who actually brought me to the laboratory where I was making my first steps in hacking Linux kernel during my internship.

While working on my PhD I was employed by Virtual Open Systems and therefore I would like to thank Daniel Raho, CEO of the company, for offering me this opportunity. Moreover, I thank all colleagues I worked with, especially Alvise Rigo, who was my company supervisor for most of the time and helped me to solve many technical challenges.

Last but not least, my family and my friends deserve big words of thank for keeping me happy everyday. In particular, I would like to thank my parents who substantially supported my education from the very beginning. Although it required an effort and determination from myself, all of that could go for nothing without a solid foundation they provided.

Finally, I would like to especially thank my beloved Magda, a hero in the shadows who was accompanying me for all this time with a profound understanding and made me enjoy life more than ever before.

# **Contents**

| Li | st of ] | Figures                                           | 7  |

|----|---------|---------------------------------------------------|----|

| Li | st of ' | Tables                                            | 9  |

| Li | st of ' | Terms                                             | 11 |

| Li | st of l | Publications                                      | 13 |

| 1  | Intr    | oduction                                          | 15 |

|    | 1.1     | Data centers — current state                      | 17 |

|    | 1.2     | Clustered architecture                            | 21 |

|    | 1.3     | Virtualization role                               | 22 |

|    | 1.4     | Clustering drawbacks                              | 24 |

|    | 1.5     | Disaggregated architecture                        | 28 |

|    | 1.6     | Disaggregated systems and virtualization          | 31 |

|    | 1.7     | Focus and scope of this work                      | 32 |

| 2  | Rela    | nted work                                         | 35 |

|    | 2.1     | Memory disaggregation                             | 35 |

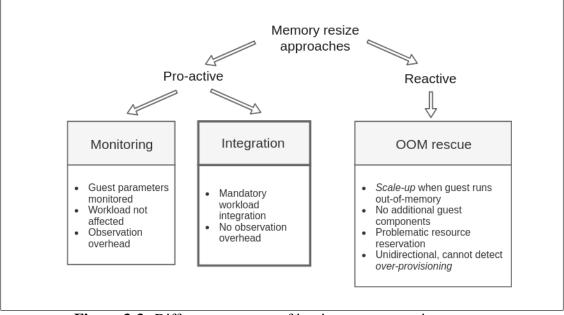

|    | 2.2     | VM memory provisioning and balancing              | 47 |

|    | 2.3     | Uniform address space                             | 53 |

|    | 2.4     | Inter-VM memory sharing and migration             | 54 |

|    | 2.5     | Devices disaggregation                            | 58 |

| 3  | Gue     | est memory provisioning in a disaggregated system | 65 |

|    | 3.1     | Chapter introduction                              | 65 |

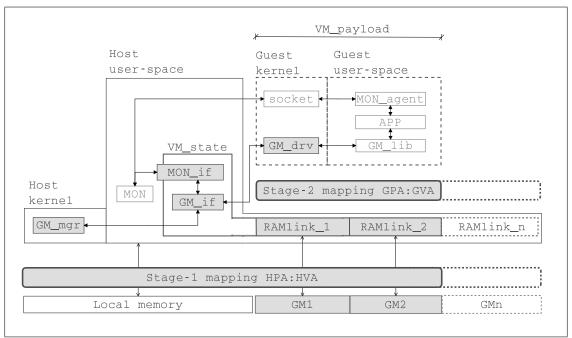

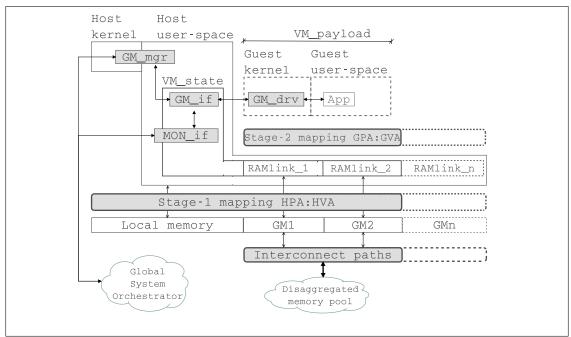

|    | 3.2   | Proposed system architecture                   | 66        |

|----|-------|------------------------------------------------|-----------|

|    | 3.3   | Resize volume                                  | 70        |

|    | 3.4   | Live VM balancing: guest parameters visibility | 72        |

|    | 3.5   | Explicit resize requests                       | 73        |

|    | 3.6   | Request path                                   | 75        |

|    | 3.7   | Resize granularity                             | 75        |

|    | 3.8   | Disaggregation context                         | 76        |

|    | 3.9   | Guest memory isolation                         | 76        |

|    | 3.10  | Chapter conclusion                             | 77        |

| 4  | VM    | memory sharing and migration                   | <b>79</b> |

|    | 4.1   | Chapter introduction                           | 79        |

|    | 4.2   | Memory sharing — overview                      | 80        |

|    | 4.3   | VM migration — overview                        | 81        |

|    | 4.4   | Software modifications                         | 82        |

|    | 4.5   | Proposed system architecture                   | 83        |

|    | 4.6   | Sharing disaggregated memory                   | 83        |

|    | 4.7   | VM migration                                   | 96        |

|    | 4.8   | Chapter conclusion                             | 101       |

| 5  | Disa  | ggregated peripherals attachment               | 103       |

|    | 5.1   | Chapter introduction                           | 103       |

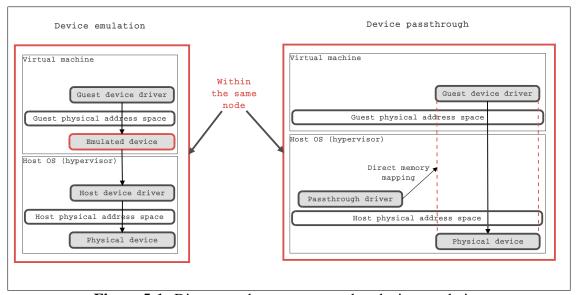

|    | 5.2   | Device emulation and direct attachment         | 104       |

|    | 5.3   | Disaggregated passthrough design               | 108       |

|    | 5.4   | Chapter conclusion                             | 108       |

| 6  | Impl  | ementation and evaluation                      | 109       |

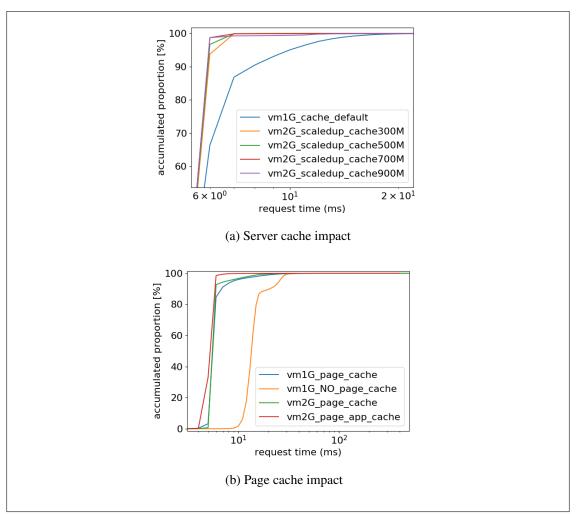

|    | 6.1   | Memory provisioning                            | 109       |

| 7  | Conc  | clusion                                        | 119       |

|    | 7.1   | Perspectives and future works                  | 121       |

| Aŗ | pendi | ices                                           | 131       |

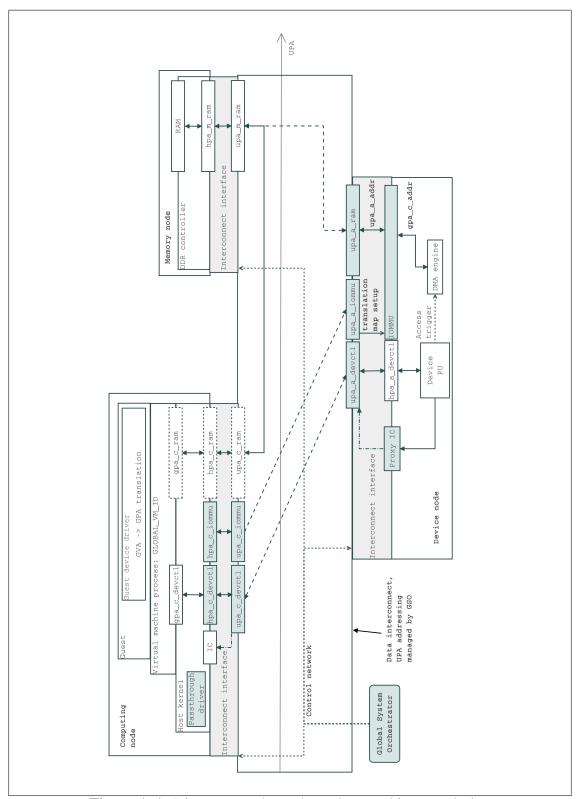

| A | Disa        | ggregated peripherals attachment - confidential part | 133 |

|---|-------------|------------------------------------------------------|-----|

|   | <b>A.</b> 1 | Disaggregated passthrough design                     | 134 |

|   | A.2         | Infrastructure setup in more details                 | 140 |

|   | A.3         | IOMMU maps update on guest RAM resize                | 145 |

|   | A.4         | Disaggregated device detachment                      | 146 |

# **List of Figures**

| 1-1 | Clustered system architecture                                     | 22  |

|-----|-------------------------------------------------------------------|-----|

| 1-2 | Disaggregated system architecture                                 | 28  |

| 2-1 | Categorization of works related to memory disaggregation          | 36  |

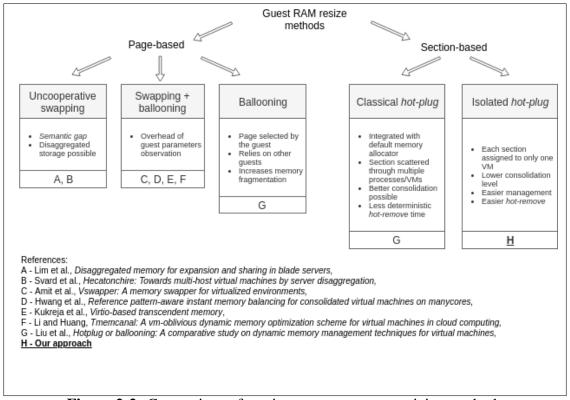

| 2-2 | Comparison of runtime guest memory resizing methods               | 47  |

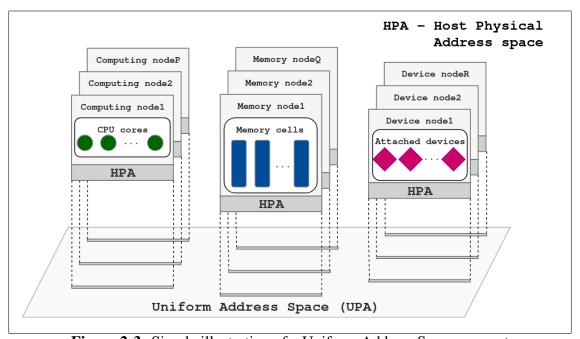

| 2-3 | Simple illustration of a Uniform Address Space concept            | 53  |

| 2-4 | Hardware-based remote device sharing methods                      | 58  |

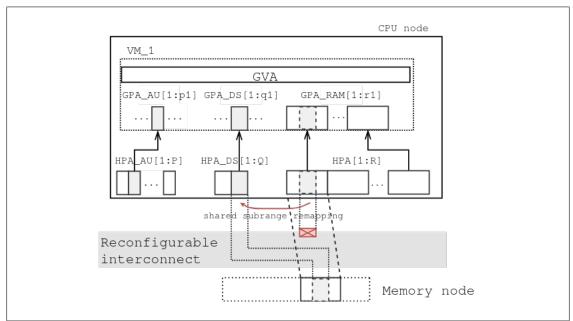

| 3-1 | Guest memory provisioning from isolated pool                      | 66  |

| 3-2 | Dynamic memory resize                                             | 71  |

| 3-3 | Different moments of issuing memory resize request                | 73  |

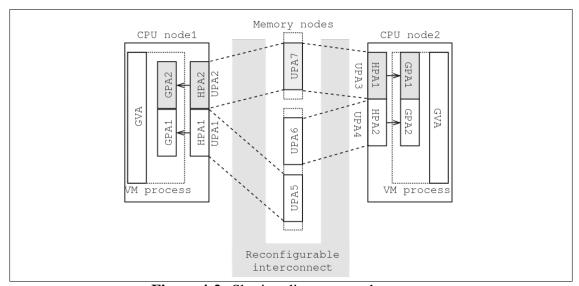

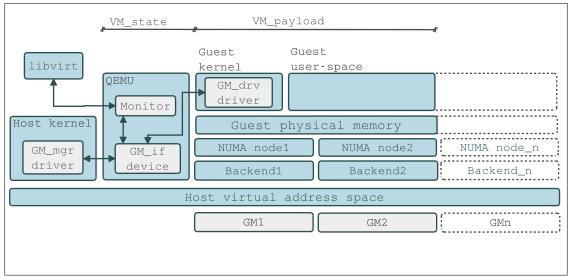

| 4-1 | Virtualization framework components                               | 84  |

| 4-2 | Sharing disaggregated memory                                      | 84  |

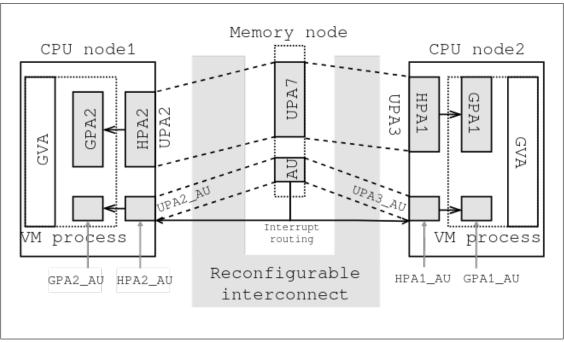

| 4-3 | Mapping a disaggregated arbitration unit located at a memory node | 90  |

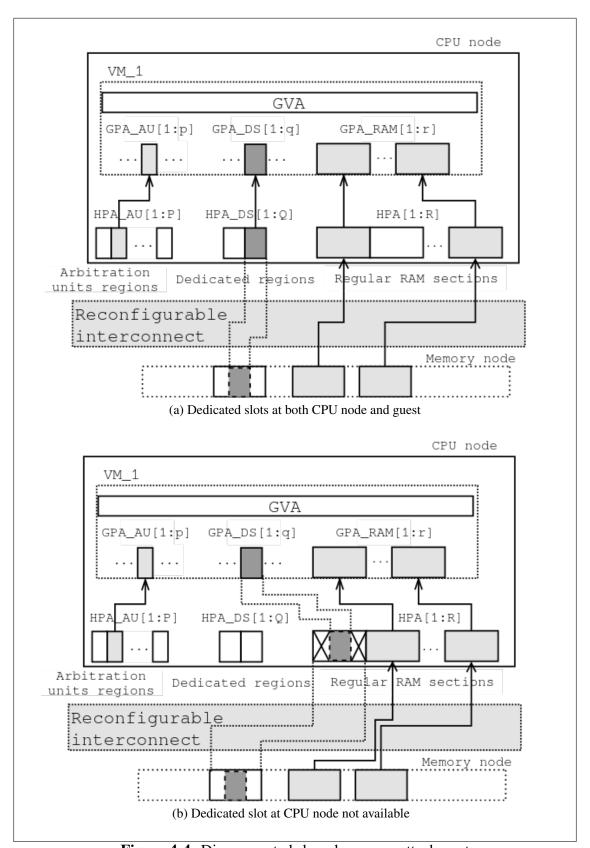

| 4-4 | Disaggregated shared memory attachment                            | 93  |

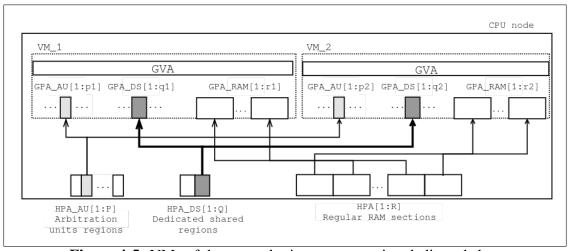

| 4-5 | VMs of the same sharing group reusing dedicated slots             | 95  |

| 4-6 | Dedicated slot initialization from an existing RAM                | 96  |

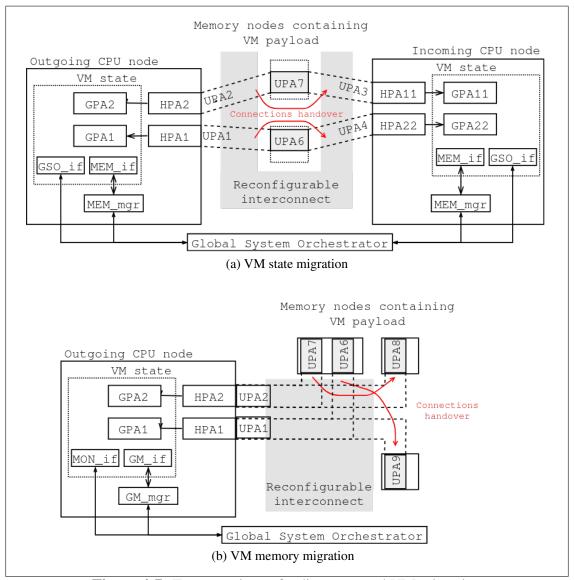

| 4-7 | Two meanings of a disaggregated VM migration                      | 97  |

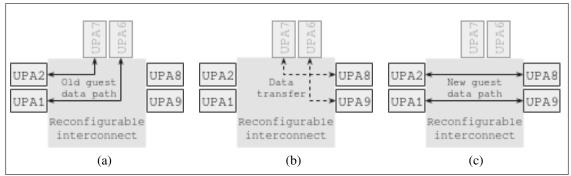

| 4-8 | Interconnect reconfiguration steps                                | 100 |

| 5-1 | Direct attachment compared to device emulation                    | 104 |

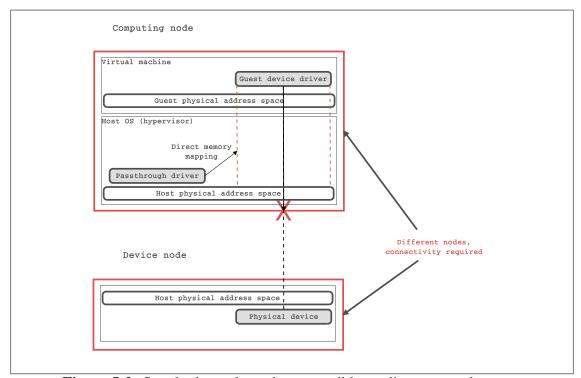

| 5-2 | Standard passthrough not possible on disaggregated system         | 105 |

| 6-1 | System prototype components                                       | 110 |

| 6-2 | Latency results from Redis-benchmark against the SimpleDB ap-     |     |

|     | plication                                                         | 117 |

| A-1 | Disaggregated passthrough — architecture design             | 135 |

|-----|-------------------------------------------------------------|-----|

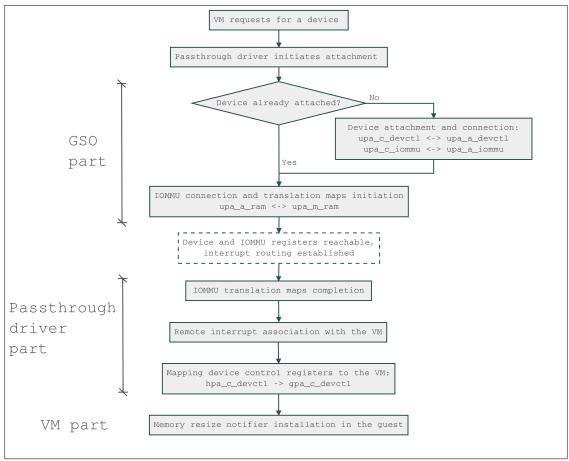

| A-2 | Direct attachment initialization                            | 137 |

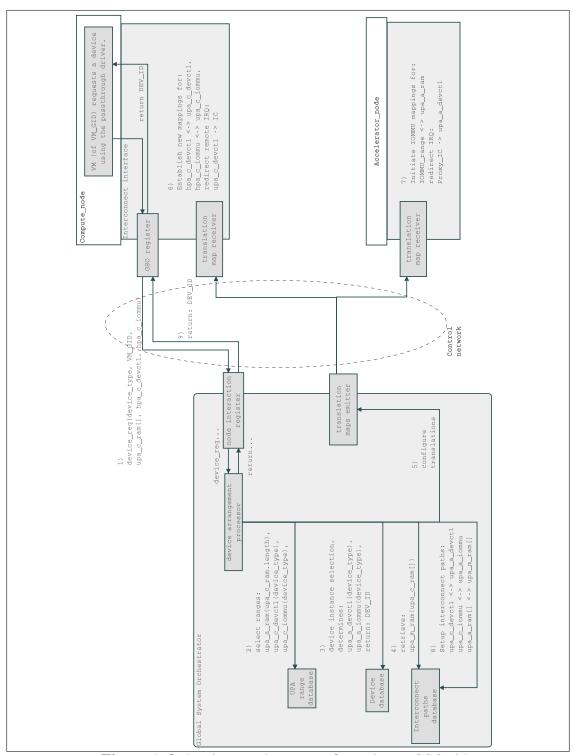

| A-3 | Device attachment configuration at GSO side                 | 141 |

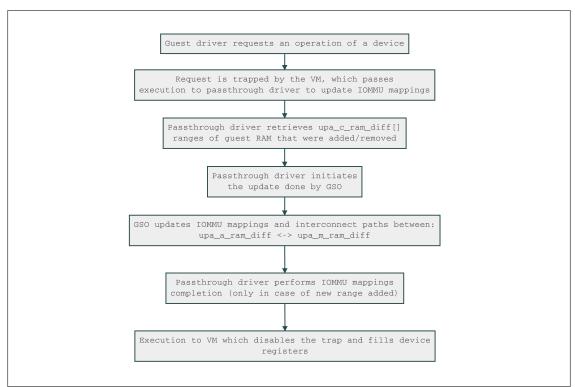

| A-4 | Updating directly attached device after guest memory resize | 145 |

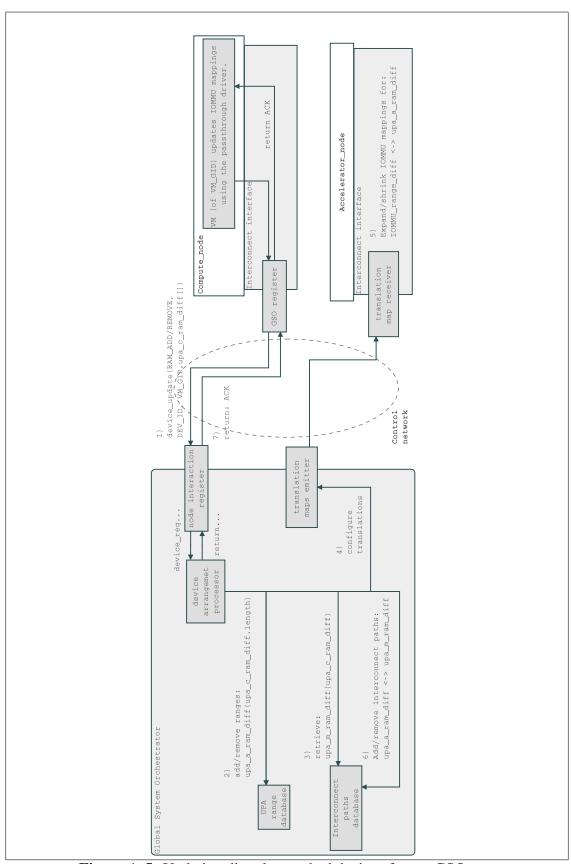

| A-5 | Updating directly attached device after — GSO part          | 147 |

# **List of Tables**

| 2.1 | Inter-VM memory sharing methods  |  |  |  |  |  |  | • |  |  | 55  |

|-----|----------------------------------|--|--|--|--|--|--|---|--|--|-----|

| 6.1 | Latencies of memory resize steps |  |  |  |  |  |  |   |  |  | 113 |

# **List of Terms**

**AU** Arbitration Unit, a module granting an access right to a region of memory shared between multiple virtual machines using it in a concurrent way.

BAR Base Address Register

**CPU** Central Processing Unit

**DRAM** Dynamic random-access memory

- **GPA** Guest Physical ADdress space, an address space created by a virtual machine and exposed to the guest OS, which will consider it as if it was a HPA.

- **GSO** Global System Orchestrator, a central (at least logically) management unit of a data-center handling configuration of all nodes and the interconnect to keep the system working. Holds the registry of all deployed VMs and their configurations at any given moment. Physically can be implemented as a single machine or in a distributed way.

- **GVA** Guest Virtual Address space, same as HVA but in the guest OS.

- **HPA** Host Physical Address space, used to describe a physical layout of resources available at each system node. Different ranges correspond to registers of different physical resources. This is a base addressing scheme determined during hardware production time.

- **HVA** Host Virtual Address space, maintained by an operating system by building translation maps (called *page tables*), usually traversed by the *memory management*

*unit* (MMU) for better performance. In fact, some operating system may not use virtual addresses, especially small embedded ones.

IC Interrupt Controller

**IOMMU** Input-output memory management unit, connects DMA-capable devices to the main memory, provides address translation between a device address space and the host physical address space and filters accesses to the memory at the same time.

MMU Memory Management Unit

MPI Message Passing Interface

**NVM** Non-volatile memory

**RDMA** Remote Direct Memory Address

**TCO** Total Cost of Ownership

**TLB** Translation Lookaside Buffer, buffer caching recent virtual-to-physical address mappings translated by the MMU.

**UPA** Uniform Physical ADdress space, a very large address space mapping a HPA of each system node as a distinctive range.

VM Virtual Machine, a software abstraction of a computer system hardware, optionally supported by hardware extensions in order to accelerate certain operations.

# List of publications

### **Conference papers:**

- M. Bielski, C. Pinto, D. Raho, R. Pacalet, Survey on memory and devices disaggregation solutions for HPC systems, 19th International Conference on Computational Science and Engineering (CSE 2016)

- D. Syrivelis, A. Reale, K. Katrinis, I. Syrigos, M. Bielski, D. Theodoropoulos, D.

N. Pnevmatikatos and G. Zervas, A Software-defined Architecture and Prototype for Disaggregated Memory Rack Scale Systems, International Conference on Embedded Computer Systems: Architectures, Modelling, and Simulation, (SAMOS XVII 2017)

- D. Theodoropoulos, A. Reale, D. Syrivelis, M. Bielski, N. Alachiotis, D. Pnevmatikatos, *REMAP: Remote mEmory Manager for disAggregated Platforms*, 29th International Conference on Application-specific Systems, Architectures and Processors, (ASAP 2018)

- M. Bielski, I. Syrigos, K. Katrinis, D. Syrivelis, A. Reale, D. Theodoropoulos, N. Alachiotis, D. Pnevmatikatos, G. Zervas, V. Mishra, A. Saljoghei, A. Rigo, M. Enrico, V. Mishra, A. Saljoghei, E. Pap, , O. González de Dios, Dionisios N, Pnevmatikatos, J. Fernando Zazo, S. Lopez-Buedo, M. Torrents, F. Zyulkyarov, dReDBox: Materializing a Full-stack Rack-scale System Prototype of a Next-Generation Disaggregated Datacenter, prototype demonstration and publication in Design, Automation and Test in Europe, (DATE 2018)

- M. Enrico, V. Mishra, A. Saljoghei, M. Bielski, E. Pap, I. Syrigos, O. González de Dios, D. Theodoropoulos, D. N Pnevmatikatos, A. Reale, D. Syrivelis, G. Zervas, N. Parsons, K. Katrinis, *Demonstration of NFV for Mobile Edge Computing on* an Optically Disaggregated Datacentre in a Box, Optical Fiber Communication Conference, (OFC 2018)

- A. Saljoghei, V. Mishra, M. Bielski, I. Syrigos, K. Katrinis, D. Syrivelis, A. Reale,

D. N. Pnevmatikatos, D. Theodoropoulos, M. Enrico, N. Parsons, G. Zervas,

dReDBox: Demonstrating Disaggregated Memory in an Optical Data Centre, Optical Fiber Communication Conference, (OFC 2018)

• M. Bielski, A. Rigo, R. Pacalet, *Dynamic guest memory resizing for disaggre-gated systems – paravirtualized approach*, 27th Euromicro International Conference on Parallel, Distributed, and Network-Based Processing (PDP 2019) [accepted]

#### **Patents:**

• M. Bielski, A. Rigo, M. Paolino, D. Raho, *Disaggregated computing architecture*, Owner: Virtual Open Systems, (proposal submitted)

### **Open source contributions:**

• M. Bielski, A. Reale, *Memory hotplug support for arm64*, Linux kernel patch, link: https://lkml.org/lkml/2017/11/23/182

# Chapter 1

# Introduction

This dissertation is positioned in the context of the system disaggregation - a novel architectural approach expected to gain popularity in the data center sector. In traditional clustered systems resources are provided by one or multiple machines characterized by a fixed amount of memory, CPU cores and set of available devices. Differently to that, in disaggregated systems resources are provided by discrete nodes, with each node providing only one type of resources. Instead of a machine, the term of a slot is used to describe a workload deployment unit. The crucial difference is that a slot does not provide a fixed amount of resources but it is dynamically assembled before a workload deployment by the unit called system orchestrator.

In the following sections of this chapter, we present the drawbacks of the clustering approach and motivate the architecture disaggregation. Furthermore, we add the virtualization layer to the picture as it is a crucial part of data center systems nowadays and it is expected to retain its position also in disaggregated ones. That is because virtualization provides an isolation between deployed workloads and a flexible resources partitioning. However, it needs to be adapted in order to take full advantage of disaggregation. Thus, the main contributions of this work are focused on the virtualization layer support for disaggregated memory and devices provisioning.

In the chapter 2 we present the state of the art analysis related to the subject of this dissertation. The analysis is divided into few sections, according to specific aspects of disaggregation like *Virtual Machine* (VM) memory provisioning, inter-VM memory sharing and remote device attachment.

Our first main contribution is described in Chapter 3. It presents the software stack modifications related to VM memory provisioning, which allow to adjust the amount of guest (running in a VM) RAM at runtime on a memory section granularity. From the software perspective it is transparent whether they come from local or remote memory banks.

In Chapter 4 we extend the proposals of Chapter 3 to allow inter-VM memory sharing and VM migration on a disaggregated architecture. That is the second main contribution of this dissertation. First, we present how regions of disaggregated memory can be shared between VMs running on different nodes. This sharing is designed in a way that involved guests are oblivious to the fact of being co-located on the same computing node or not. Additionally, we discuss different flavors of concurrent accesses serialization methods. We then explain how the VM migration term gained a twofold meaning. Because of resources disaggregation, a workload is associated to at least one computing node and one memory node. It is therefore possible that it is migrated to a different computing node and keeps using the same memory, or the opposite. We discuss both cases and describe how this can open new opportunities for server consolidation.

Chapter 5 provides our last main contribution related to disaggregated peripherals virtualization. Starting from the assumption that the architecture disaggregation brings many positive effects in general, we explain why it breaks the passthrough peripheral attachment technique (also known as a direct attachment), which is very popular for its near-native performance. To address this limitation we present a design that adapts the passthrough attachment concept to the architecture disaggregation. By this novel design, disaggregated devices can be directly attached to VMs, as if they were plugged locally. Moreover, all modifications do not involve the guest OS itself, for which the setup of the underlying infrastructure is not visible.

Chapter 6 presents a prototype that we used to evaluate the implementation of our ideas and provides preliminary results about flexible guest memory resizing.

Finally, Chapter 7 concludes the dissertation and proposes several directions of future works.

### 1.1 Data centers — current state

Perhaps the first image, derived from news media or movie scenes, that one associates with the term **data center** is a very large facility filled with multiple server cabinets and connected by hundreds of meters of cables. Typically thousands of blinking diodes and a constant noise produced by air-conditioning are the only indicators that there is actually something going on there. Such a description is only roughly accurate. Many data centers are indeed occupying a surface from hundreds up to millions of square meters and hosting huge and powerful installations called sometimes supercomputers (see the TOP500[8] list, ranking the most powerful computers in the world). But most of them are much smaller, for example private enterprise installations may occupy just one or few rooms but still provide enough resources to serve well a small- and medium-sized company or institution.

As of 2018, when talking about a data center we consider an installation hosting at least a dozen of *Central Processing Unit* (CPU) cores together with available memory in the order of at least several dozens of gigabytes. A crucial role in the system is also played by installed accelerators, which are off-loading CPUs from certain types of computations. Definitely, the volume of resources is much bigger than what is offered by personal computers or mobile devices nowadays.

As a consequence of the desired performance level and the number of components, these systems typically require significant investments in order to be deployed and consume a big amount of electrical energy. This is commonly described by the *Total Cost of Ownership* (TCO) term, which is one of the most important factors determining whether a given data-center technology will be successful or not. A system can also be characterized by *performance-per-dollar*, a ratio between the offered operational capabilities and the cost.

Not surprisingly, such large-sized installations are meant to be shared by multiple work-loads (or users) in order to maximize the utilization factor (and an associated profitability factor) and minimize energy consumption (and related heat production) per workload, while still keeping the offered performance aligned with modern applications requirements. Resource partitioning is usually done by virtualization techniques, which allow to abstract underlying physical resources so that they are provided in the form of a

*Virtual Machine* (VM), which is a workload deployment vehicle and, from a workload's perspective, creates an impression that it uses the system exclusively.

#### **Trends**

The fact of exporting both computations and data to an external data center is commonly known as *cloud computing*. Services offered by cloud system providers are usually falling into one of three basic models, namely *Infrastructure-/Platform-/System-as-a-Service* (*IaaS*, *PaaS* and *SaaS*, respectively) [3]. Without going into details and differences between them, which are not important here, a common incentive for users is to focus on their particular mission while moving the responsibility of computing resources provisioning to an external provider [34]. Additionally, it can be a way to optimize the operational costs since the subscription can usually be flexibly changed according to customer requirements at a given moment, instead of purchasing physical industry-grade and expensive hardware to fulfill the peak-usage scenario. Subscription fees, similarly to other goods available on the market, consist of two parts. The first one is governed by purely business factors like product popularity or market competition level — these are out of interest in this work. The second one, though, is determined by technical factors, like an amount of resources reserved for a given workload and therefore unavailable for other system users.

A very important aspect is that not all reserved resources may be effectively used by the customer. For example several machines may be necessary to provide the required amount of memory resources, but not all of associated CPUs may be needed. In consequence, the corresponding computational power will be wasted because, in a clustered architecture, there is no way to attach unused CPUs to other machines. This is clearly an inefficiency which a customer needs to pay for.

Important examples of data-center usage are computations typically categorized as *Big Data*, processing large amounts of data from various sources and for different analytics purposes. Tasks of this type are very often leveraging distributed/parallel processing algorithms and thus require significant processing power as well as storage for input and output data. For such use-cases the *cloud computing* model fits very well.

A recent literature study [34] provides real-world examples that help to create an image

of different computation volumes (these are numbers from 2014, they can be even higher in 2018). The Large Hadron Collider at CERN is expected to produce around 15 petabytes of data every year. A Boeing jet engine can generate up to 20 terabytes of data during one hour of operation. Facebook servers are processing about 500 terabytes of user log data and hundreds of terabytes of image data on a daily basis. Similarly, servers used by eBay are achieving a hundred of petabytes processed within the same period of time.

Browser requests, social media applications, customers profiling algorithms, personal health care monitoring, blockchain transactions or manufacturing chains — every day we are surrounded by myriad of situations in which data is produced, collected and analyzed. With the upcoming era of 5G communication and IoT (*Internet of Things*) this tendencies will likely get reinforced.

### **Global impact**

It has been estimated that the global data traffic grew 56 times from 2002 until 2009, while the computational power increased 16 times in the same period. By extrapolation, it was expected to take around 13 years for a 1000-fold increase in computational power — theoretically (as of 2014). However, hardware energy efficiency is not expected to grow more than 25-fold at the same time. Such divergence of trends indicates that data centers growth may imply a significant increase in a global energy consumption or non-sufficient energy supply may become an actual limit for the development of the sector [34]. Another publication reported that US data centers contributed to 2.2% of the country total electricity consumption in 2013, corresponding to 100 million metric tons of carbon pollution [44]. It was also predicted that between 2012 and 2020 the carbon footprint of the sector will globally grow by 7% year-to-year, which makes it the fastest growing ICT sector in this regard [49].

A conclusion that one may draw from the presented numbers is that there is definitely an urgent need for limiting the amount of energy consumed by data centers worldwide. One way to achieve this would be decreasing the number of data centers but the feasibility of it is questionable, to say the least. Another approach consists in improving the energy efficiency of data centers, with a two-fold meaning. Firstly, by making

them consume less energy for the same given amount of work. Secondly, by reducing the amount of wasted energy, that is, situations where some resources remain powered while they are not efficiently used. The latter is indeed reported as the easiest way to lower the total energy expenditure [60]. A characteristic associated to energy efficiency is the *server consolidation* term. It is not an absolute metric but it describes the ability of a server to execute a maximum amount of computations on a minimal amount of resources.

The need for more energy efficient data centers was already postulated in the literature and supported with real-world examples [27]. On a Twitter production cluster, for instance, it was measured that the aggregated CPU utilization is constantly lower than 20%, while the reservation is between 60% and 80%. This means that 40% to 60% of CPUs remain ready to perform computations but stay idle. With regard to memory utilization, between 40% and 50% is actively used, while around 80% is reserved, therefore 30% to 40% of the memory resource is wasted. In Google clusters, another example from the top-tier operators, it was observed that typically from 25% to 35% of CPUs are actively used, while 75% are reserved. This gives from 40% to 50% of computing power loss. And 40% of the memory resource is actively used, while 60% in average is reserved. Still, in both cases there is no information about non-reserved resources, the authors do not specify whether they are consuming any energy or not. In addition, the authors explain that the above numbers are representing only a small group gathering the biggest market players, accounting for 5% to 7% of the total number of installed servers. These major players can probably afford the adoption of standard and/or custom solutions in order to improve the energy efficiency of their servers. They might even be forced to do so because, for them, a limited energy supply at a given location may otherwise become a scalability issue. Other small- and medium-sized data centers have neither such incentives nor comparable resources. Moreover, they often stay conservative in terms of technology upgrades because of the risks related to modifying an already working infrastructure, even if it is sub-optimal [60]. Therefore, for the majority of the global data-center market, the energy effectiveness is probably even worse than the numbers presented above.

Another frequently mentioned problem is the correct estimation of resources. Ac-

cording to one study, 70% of workloads overestimate their required resources up to 10 times [27]. Exact numbers would vary for each workload but the most important message is the high level picture. It shows that workloads are either profiled with low accuracy or a substantial estimation margin is introduced by purpose to avoid potential performance issues.

It was suggested that, in a global perspective, it would be more efficient if the work-loads of multiple medium- and small- installations could be aggregated and deployed together on bigger systems offered by multi-tenant providers [30]. Such data centers are expected to offer a logical slice of resources to rent, according to customer needs. However, under the hood all workloads would run on the same physical hardware taking advantage of efficient balancing techniques for better utilization level. Moreover, such providers, which business is focused on infrastructure provisioning, are also supposed to enhance their technology more frequently in order to keep the energy efficiency level as high as possible. Especially, they could adopt architecture disaggregation, which underlies our work.

Regardless of whether one would consider only the financial aspect or also the environmental impact, the problem of low energy efficiency of the data centers sector should definitely not be neglected. In the following we discuss how the situation can be improved by switching to a novel, disaggregated hardware architecture.

### 1.2 Clustered architecture

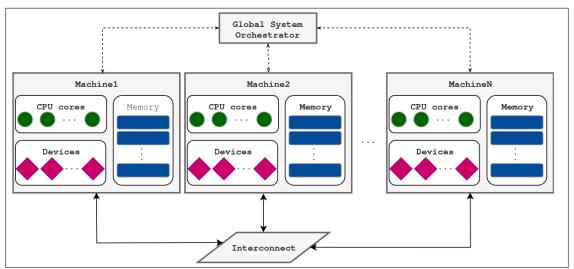

At present, the data-center sector is dominated by cluster systems that achieve their great capabilities by combining together multiple smaller machines, as illustrated on figure 1-1. Each machine, also referred by the term of a slot is built in a traditional way, in the sense of being composed of CPUs and operating memory banks, both physically bound to the same motherboard [28]. In addition, different types of devices attached may also be attached to the slot (e.g. hard disks, network interface cards, GPUs or accelerators).

The whole system is managed by the *Global System Orchestrator* (GSO). Different implementations may use different naming for this module but its purpose stays the same.

Amongst others, it decides on which machine a given workload will be deployed (load balancing), establishes intra-cluster connectivity, monitors various system parameters or manages machine upbringing and shutdown. This is also the unit which usually provides an administrative interface for system configuration.

The interconnect provides a high-speed connectivity between all machines so that they are capable of passing messages as well as exchange data. Typically, this is used by distributed programming frameworks (like OpenMPI, an open-source implementation of the MPI standard [19]) in order to partition a computational problem into smaller chunks that can be processed in parallel on multiple machines with proper synchronization.

Figure 1-1: Clustered system architecture

### 1.3 Virtualization role

An essential part of nowadays data-center systems is the virtualization layer, provided by the software stack component called *hypervisor*. The hypervisor is tightly coupled with an operating system kernel and it is responsible for management of VMs. Virtualization benefits the system in several ways:

1. Virtualization abstracts the underlying physical resources and makes (usually a slice of) them accessible to the user in a convenient way — as a logical unit called *Virtual Machine* (VM). A user needs to know neither the physical system

architecture nor the actual location of the components. According to a variable system load a VM could be migrated to a different slot and such operation, ideally, should be barely noticeable from the workload perspective (in practice, a temporary performance drop is possible). Without the virtualization layer each workload would either need to support migration in its own specific way or it would simply need to be terminated and spawned on a different slot.

- 2. Physical resources partitioning performed by the hypervisor allows to allocate them in an optimal way to perform a maximum amount of computations on a given amount of resources. With respect to the utilization factor, it is much more efficient than the bare-metal deployment of each workload on a separate machine. Such allocation flexibility applies to both an initial VM setup as well as to runtime resource resizing. The situation is the most straight-forward in the case of device sharing: an accelerator can be attached by a VM either periodically or all the time but in a shareable manner. Regarding the amount of CPU cores used by a VM, it can be changed as long as there are enough resources available on a given machine. Concerning the amount of RAM attached to a VM, a very negative phenomenon is the memory overprovisioning. That is when the amount of RAM reserved for a VM exceeds the needs of a workload for most of its execution time and only during rare peak usage moments all memory resources are effectively used. It is the role of a virtualization layer to support the dynamic resize of VM memory volume in order to limit memory overprovisioning (although the situation is still far from good, as mentioned in section 1.1).

- 3. Multiple VMs are running independent workload-specific software stacks, including their own *guest operating systems*, which provides a strong isolation between VMs hosted by the same data-center. This feature is a great advantage weighted in favor of virtualization in terms of system security. For example, a critical error within an application executed in one VM may cause a system crash but it will not affect other workloads running in different VMs. The latter could be the case without virtualization, if all workloads were executed as a separate processes of the same operating system.

4. Regarding the guest OS, a strongly desired characteristic provided by virtualization is the ability of VMs to host standard operating systems, optionally equipped with additional installable software modules. From a potential user perspective this greatly facilitates the migration from a workstation to the cloud as the original working environment can stay almost unmodified and the compatibility between an OS and customer's software is not threatened.

Eventually, having enumerated multiple reasons for virtualization adoption, it is critically important that this convenient abstraction does not incur significant performance overhead. The key point here is that the heaviest operations performed by the hypervisor are accelerated by the underlying hardware (e.g. nested paging [7]).

## 1.4 Clustering drawbacks

In a clustered system, resource provisioning is performed on a slot basis. While slots may be divided into groups of different resource proportions, these proportions are fixed and therefore a given amount of workloads deployed on a given slot may consume completely one type of resources while leaving the others underutilized.

For example, the memory of a slot, which CPUs are powered-off, cannot be easily shared with other slots. Although distributed algorithms are capable of involving multiple machines providing different resources, all worker slots need to communicate with a root slot in order to synchronize the execution or transfer data. Even if one machine in a cluster has a certain amount of memory available, it still needs at least one CPU core in addition, to execute the synchronization code.

Therefore, the crucial problem of clustering is that underutilized resources of one slot cannot be easily attached to another one while they remain powered-on. This leads to an inefficient utilization at a single machine level and further magnified at scale as typically data center installations are composed of numerous slots. The powered-on and non-used resources contribute to the system total energy footprint as well as they produce additional heating — which boils down to yet additional chunk of energy spent in order to dissipate the heat. All in all, clustered systems are marked by the energy proportionality issue, in the sense that the total system power consumption is

not proportional to the load. Instead, the power consumption is determined by the number of machines that have to be kept active in order to meet the load requirements. Assuming that a fraction of resources within each machine is likely underutilized, the sum of associated power consumed by all such fractions yields the disproportion [45]. Additionally to allocation inefficiency, recent observations and predictions suggest that the way how resources are provided in clustered architectures does not fit requirements of current workloads. The number of CPU cores per socket is expected to grow up to two times every two years. At the same time, the observed number of VMs per core is also increasing, as is the memory footprint per VM. This means that there is a large demand for bigger and bigger amount of memory to be available per CPU socket. In contrast, the growth of the memory capacity per socket is projected to be much slower and it is stated that an inadequate memory supply may become a scalability limitation (which phenomenon is referred as the *memory capacity wall*). Together with this observation there is postulated a need for new architectural approaches that would allow to expand the available memory independently from the computing resources [39]. Currently, the recommended amount of supplied resources differs depending on the performance benchmarking suite used (High Performance Linpack [6], used to rank the TOP500 list [8] vs. High Performance Conjugate Gradients [4]), however it has been estimated that a modern system should offer at least 0.5GB of main memory per core for the optimal system performance [65]. For example, the first machine on the TOP500 list as of June 2018 is the IBM Summit with a ratio of 1.23 GB of RAM per core [18]. Going further, clustering suffers from yet another drawback related to the availability of accelerators, especially of specialized ones with a relatively high price tag. They are used to accelerate particular types of computing operations (e.g. GPUs for vector or matrix operations), and thus to save CPU clocks, but it is usually not required to have them attached permanently to all machines; many applications might not be able to make use of them. Therefore, it has been noticed that it is in general good to have few of them globally accessible to accelerate some workloads [30].

Efficient peripherals sharing between different slots in a cluster is not straightforward. When a workload needs to use a peripheral which is not available from its current machine, and assuming it runs in a virtualized environment, it must be migrated. This

incurs a significant operation downtime because of the volume of data to be transferred (typically several gigabytes). Additionally, a limited availability of the powerful accelerators may constrain the slot selection algorithms in such a way that the selection will become sub-optimal with regard to the overall server consolidation level. For example, in order to be able to use an accelerator, a workload may have to be deployed on a machine that could otherwise remain powered-off. But once deployed it may not effectively use all the available computing power or RAM, which, in such a case, will be wasted.

Finally, the machine-centered architecture is characterized by a low flexibility of modifications at hardware components level. As the memory banks and CPUs of a machine are physically attached to a common motherboard, the possibilities of upgrading independently only one of those resources may be limited, if not impossible, because of hardware compatibility constraints. This may even lead to *vendor lock-in* situations and impose significantly higher costs for such hardware upgrades, even in the case of commodity systems. This actually limits market competition, which is another negative aspect.

The aforementioned inefficiencies and limitations stem from the presented system architecture. In order to thoroughly address them, there is a need for a novel solution bringing a transparent resource allocation across machines, breaking the fixed proportionality limitation and therefore redefining the notion of a slot [39]. It has been proposed to significantly reshape the hardware topology and improve the overall system heterogeneity such that different types of resources may be reserved separately, according to a workload profile, regardless of the motherboard they are plugged into. This new approach is called *disaggregation* and opens for an improved consolidation level of data-center systems, an increased resources utilization, improved energy proportionality and lower maintenance costs. This is because the new approach assumes that what is currently considered a slot will no longer mean a physical machine of fixed resource proportions but a dynamically assembled instance with different types of resources provided according to workload requirements.

Furthermore, in order to stamp a meaningful mark, such technological shift is expected from commodity-grade products used by small- and medium-sized as well as corporate

data centers, which represent the majority of the sector players (for example, in 2011 their market share in U.S. was estimated to 70% in terms of number of servers and 76% with respect to electricity consumption [60]). Otherwise, a heavily customized technology would be affordable only to a small number of top-tier providers and therefore it wouldn't have a chance to significantly change the situation in a global perspective.

## 1.5 Disaggregated architecture

#### **Motivation**

As discussed in the previous chapter, the data center sector is currently facing several problems which induce both economical and environmental effects on a global scale. To wit, an accurate estimation of the required workload resources is very difficult and they are usually over-provided to satisfy the worst-case scenario [47]. Furthermore, resource sharing flexibility is limited and for that reason a certain fraction of them is not used, except for burst periods of maximum demand. On top of that, within a single machine different types of resources are attached to a common motherboard. Therefore, underutilized resources still remain powered-on and the associated chunk of consumed energy is wasted, which is an *energy proportionality* issue.

In order to address these problems, a new *disaggregated architecture* has been proposed which structure and characteristics are the subject of this chapter.

### **Design**

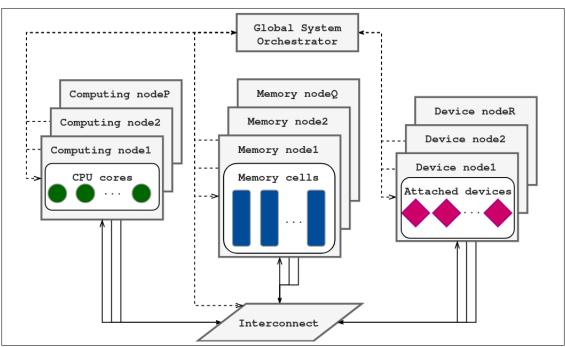

Figure 1-2: Disaggregated system architecture

Data-center resources may be divided into three main groups: CPUs, memory and peripherals [1, 35]. Instead of being contributed by a number of conventional monolithic

machines (as illustrated on figure 1-1), in a disaggregated architecture they are provided independently and form pools of resources. Each pool may consist of one or multiple nodes of a given type and all system nodes are attached to a reconfigurable interconnect, as shown on figure 1-2. It is therefore possible to update only one type of resources, for example by attaching more memory nodes. This is not a one-time improvement (like, for example, plugging more DIMM modules into vacant slots of a motherboard): such a flexible resource proportionality holds at scale. Figure 1-1 is a general illustration of the concept, in a particular implementation compute nodes may also be equipped with a limited amount of local RAM. This may be necessary to bring up a host operating system containing software modules responsible for registering the node to the system. What was being considered a machine in the context of conventional architectures essentially becomes a CPU node with the amount of other resources adjusted in a dynamic manner. As a result, the aforementioned notion of a slot no longer describes a monolithic unit characterized by a fixed resources proportionality. Instead, the slot is dynamically assembled now, with the amount of resources following requirements of a given workload. This requirements can vary over time, thus the slot capabilities can be also adjusted at runtime, for example by adding or removing devices or memory.

Thus, because of disaggregation, different types of resources can be reserved independently. For example, the problem of *memory capacity wall* (described in section 1.4) is bypassed as the amount of RAM required for a workload does not impose the amount of CPUs anymore because they are not physically bound to the same motherboard. Therefore, there are no CPUs which have to be reserved (and powered-on) only because of physical dependencies. In a disaggregated system the amount of reserved CPUs is only determined by the requirements of a workload. In this way disaggregation aims to improve the energy efficiency of the system by reducing energy wastes.

Such flexibility in resources allocation is a crucial novelty of the design that opens for more efficient balancing, less defensive estimation and finally increased utilization level, that means reduced energy losses. At the same time, reduced hardware dependencies make potential hardware upgrades (or failure recovery) easier and cheaper because a replacement of one type of resource does not enforce any changes to other resources.

#### Resource scheduler role

The relaxation of dependencies between resources is a crucial trait of the novel architecture for the aforementioned reasons. Nevertheless, it also makes the logic of the system scheduler more complex and the following section explains why.

Referring to figure 1-2, the scheduler is a submodule of the *Global System Orchestrator* (GSO). Being at heart of the system, the GSO is the only system component connected to all nodes via the *control network*, in order to pair selected nodes by establishing *interconnect* links. Additionally, it performs system-wide power management and provides a system administration interface.

With conventional architectures the scheduler has only to select a machine (of a fixed resource proportionality) and potential losses of underutilized resources are inescapable. This is changed due to disaggregation: instead of selecting a physical slot, the scheduler needs to dynamically define it by composing different resources together. At first, the scheduler has to select a computing node (an equivalent step to machine selection), on which a workload will be executed, and subsequently determine which memory and peripheral nodes should be attached to it, in order to meet the workload requirements. After computing node selection it may happen that other required peripherals are already attached. Otherwise, a proper new connectivity needs to be established between selected nodes. As a result, system resources may be used more efficiently but the scheduler logic is more complex. This is because the number of possible configurations is much higher (compared to a cluster of machines) and increases together with the number of nodes. However, in practice, there might exist boundaries limiting the number of combinations, related, for example, to a maximum allowed distance between two nodes or a maximum number of adjacent nodes that a CPU node can attach to.

Furthermore, because of the variability of the data-center load, new workloads can be deployed over time and others can terminate or get killed. Such fluctuations change values of parameters considered by the scheduler logic. In addition to proper resources arrangement at a workload deployment time, the scheduler has to monitor workload termination events in order to be able to dynamically reconfigure the system and keep the resource utilization factor at an acceptable level. For example, it may happen that after several applications terminated, there is only a few left running on a given CPU

node and it would be optimal to migrate them to another node and to power-off the now unused one. However, As this could temporarily slow down a workload execution, such a reconfiguration can probably not be performed too often: the utilization level benefits could be overshadowed by the operation overhead.

### 1.6 Disaggregated systems and virtualization

So far, this chapter discussed how the clustered system architecture looks like and what is the role of a virtualization layer in such systems. Furthermore, it was described what are disadvantages of the clustered approach and how the system architecture was disaggregated in order to eliminate them. Then, the question addressed in this section is whether the virtualization layer is still needed in a disaggregated system or not. Indeed, it is, and there are several good reasons to keep the additional level of abstraction between deployed workloads and the physical hardware.

The main assumption is that such a radical architectural shift as disaggregation is, while benefiting a system provider in many ways, should affect the way how the system is used as little as possible. From the user standpoint, the most important (in authors' subjective opinion) aspects of a cloud-computing service are: secure and stable workload execution (related to proper isolation between different workloads) and the lowest costs possible. As discussed in section 1.1, the costs are derivative of the utilization factor, which is further related to resource resizing flexibility. The improved resource arrangement flexibility, brought by disaggregation, encourages users to avoid overprovisioning and leverage the *pay-as-you-go* resource reservation model. The point is that users do not care about the system architecture; whether it is clustered or disaggregated, ideally they should be able to deploy their workloads the same way in both cases, in order to avoid additional engineering effort.

Therefore, similarly to clustered systems, virtualization is also an important layer of disaggregated ones. It abstracts underlying hardware and software infrastructure and provides a workload deployment unit that users are familiar with, that is a VM. For users, the crucial difference between clustered and disaggregated systems is that parameters of a VM (like memory volume or attached devices) can be adjusted more

flexibly or service price can become more competitive (no overprovisioning means less energy wasted).

Additionally, the level of a workload execution security should be at least the same as above. As mentioned in section 1.3, different workloads deployed as separate VMs are well isolated. A crashing workload within one VM is not be able to disturb others. Moreover, each VM runs its own software stack, for example with a customized operating system kernel. Such software dependencies are definitely an important decision factor for users considering migration of their business environments to the cloud. Finally, as described in section 1.5, the job of a resource scheduler is more complex, in comparison with clustered systems. Nevertheless, thanks to the virtualization layer, the scheduler is able to perform resource management on a per workload basis. For example, a VM parameters definition allows to determine the optimal workload placement. Moreover, until a certain extension, a VM itself is able to perform a runtime monitoring of a workload execution. It can effectively support resources management across the system in a way, which does not require any modifications at the workload side. Similarly, the whole workload can be migrated to other system node simply by moving its enclosing VM. Otherwise, without the abstraction that virtualization brings, a system-specific support for migration would need to integrated in each workload, which would be an additional engineering effort at a user side.

## 1.7 Focus and scope of this work

This chapter introduced the context of this work, that is data-center systems. It presented the status of the sector and observed trends, with respect to workload characteristics. There were discussed inefficiencies of nowadays systems (like overprovisioning and low energy efficiency) and why they are related to clustered hardware architecture. In turn, there was presented a new architectural approach, which was postulated as a solution for aforementioned problems. Finally, this chapter justified why the virtualization layer is a crucial part of the clustered systems and why it will remain its important role also on disaggregated ones.

The point is that the virtualization layer needs to be modified in order to make the best

use of disaggregation benefits. Therefore, the main focus of this work is the adaptation of the virtualization layer to a disaggregated system, divided into several parts. They all depend on the assumption that there is a way to attach disaggregated memory to the host OS as well as there exists an interface to communicate with GSO in order to request for operations that affect other nodes of the system (like requesting for a chunk of disaggregated RAM, attaching a device or obtaining a shared memory lock). This work is associated to the project *dReDBox* and its scope presents only a fraction of all efforts conducted in the project[35].

The contributions described in the next chapters are related to flexible VM memory provisioning, inter-VM memory sharing, migration and disaggregated devices attachment. In order to position this work amongst related works from recent literature, respective analysis was performed and is presented in the next chapter. Although building the hardware and software components related to disaggregated memory provisioning at the host OS level is out of scope of this work, it is an important part which virtualization enhancements are built on top of. Therefore, this aspect is also present in the *state-of-the-art* analysis.

With respect to the term of *disaggregation*, the memory provisioning design presented in this work assumes that a VM is executed on a single computing node only (refer to figure 1-2). Although a VM can be migrated, this work is not dealing with VMs distributed over multiple computing nodes. It should be noted when comparing with other approaches, which assume the latter to be true[53].

# Chapter 2

# **Related work**

This chapter presents various works related to the subjects of disaggregated systems and virtualization. The presented positions are outcomes of the state-of-the-art analysis carried out by the author by putting in his best effort. The whole chapter is divided into five sections, according different topics, as indicated by the title of each section.

## 2.1 Memory disaggregation

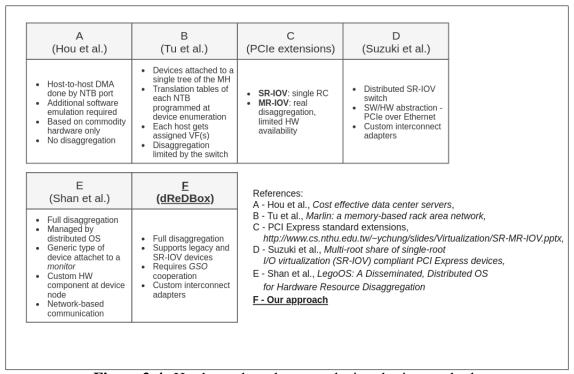

This section presents in a high-level how the disaggregated memory is provided in the *dReDBox* prototype and how it compares to other solutions addressing the same problem. It presents methods allowing a CPU of one node to access the memory attached to another node. This ability is required to implement a disaggregated system but it can also be used in order to make use of underutilized memory in clustered one. In general, the survey of the recent literature indicates that remote memory attachment may be done by software or hardware means. Orthogonally, a system may have either a traditional clustered architecture, or a disaggregated one, where different types of resources are provided by independent nodes. With respect to these two factors, all works discussed in the following part of this section were collated on figure 2-1.

|               | Page swapping                                                   | Direct access                                                 |

|---------------|-----------------------------------------------------------------|---------------------------------------------------------------|

| Disaggregated | <ul><li>Velegrakis2</li><li>Lim1</li><li>Shan</li></ul>         | <ul><li> Velegrakis1</li><li> Lim2</li><li> dReDBox</li></ul> |

| Clustered     | <ul><li>Hou2</li><li>Samih</li><li>Svard</li><li>Nitu</li></ul> | <ul><li>Montaner</li><li>Hou1</li></ul>                       |

Figure 2-1: Categorization of works related to memory disaggregation

The labels correspond to names of first authors of discussed publications. In few cases the names are also followed by a digit indicating a variant of the presented approach (if there are multiple ones), in the order aligned with the description.

The presented approaches are assessed especially with regard to the level of system heterogeneity between computational and memory resources, the required hardware or software modifications as well as the support for virtualization they offer.

# Velegrakis: "Operating System Mechanisms for Remote Resource Utilization in ARM Microservers"

Velegrakis [58] presented a small prototype, built with two nodes<sup>1</sup> connected by an FMC cable and a custom FPGA block called *Chip2Chip*. The custom hardware expands an on-chip interconnection in order to forward memory access transactions from the CPU of a node to the memory of the other (the disaggregated memory). The access can be performed in two ways.

The first one consists in reaching the remote memory through the CPU cache and it can be done using the cache of a local or remote CPU. The principle is similar to what is normally done for a local RAM, with one caveat that the cache can be remote. This access method is completely transparent for the host operating system, which only needs to know the physical address ranges associated to the disaggregated

<sup>&</sup>lt;sup>1</sup>Avnet Zedboards, based on Xilinx Zynq cores that embed an ARM CPU and an FPGA fabric in the same chip.

memory. Once the host OS is notified about address ranges, the remote memory can be initialized as any other memory, although the author suggests that remote memory should be only used when the locally available one is full because of the performance overhead (latency, bandwidth). Zhang et al. took the same approach of attaching the remote memory at the on-chip interconnection level and accessing it at the cache-line granularity [64].

In our work the disaggregated memory is also attached transparently to the host OS and represented by physical address ranges but we took an alternative approach at the host OS level: the disaggregated memory ranges are initialized in a distinctive way. They are kept separate from the local RAM and not used by the default memory allocator in order to have a better control over the allocation of the disaggregated memory sections. The same author also presented a second method of accessing the remote memory, which is using it as a swap partition. With this approach, the disaggregated resources are automatically used by an operating system to evict pages in case of high memory pressure. The most important difference is that disaggregated memory pages are not directly addressed but they are transferred back into local RAM by an I/O operation managed by the kernel swapping thread. Other works also use this technique. They are discussed in the following.

An interesting feature of this prototype is that the remote memory comes from a different node than the CPU node and the memory access can be handled completely in hardware (the first method). However, the prototype does not allow to test how the routing of the memory transactions would perform at scale, when a system would consist of multiple disaggregated memory nodes.

Although no specific virtualization support is mentioned, the system could be well integrated with the virtualization layer. It would be the easiest with the first access method, where the remote memory access is performed by the hardware, however the second one (swap device) is reported to perform better. In order to partition such a swap device amongst all deployed VMs, each one would need to obtain some amount of local RAM at first, where the data would be rotatively swapped-in. Although the author suggests that this is the way how disaggregated memory should be used (as a secondary resource), the work presented in this dissertation has been demonstrated on

a prototype (described in the following) based on different assumptions. To wit, in our work the deployed VMs are supposed to use only disaggregated memory, so the swapping technique cannot be used for the lack of local RAM.

# Lim et al.: "Disaggregated memory for expansion and sharing in blade servers"

In [39], Lim et al. present a prototype of a system consisting of a disaggregated memory blade (equipped with a large volume of memory cells) connected to several compute nodes by a fast communication fabric. A distinctive feature of this design is that the virtualization layer is a complementary part of it. Each compute node runs a hypervisor that cooperates with the blade's management software in order to get assigned with segments of disaggregated memory. Subsequently, a hypervisor maps ranges of disaggregated RAM into its own physical address space, next to the local memory. Similarly to the previous work, two methods of remote memory provisioning are presented.

The first one is a hypervisor-level page fetching that copies remote data into local memory. It assumes that remote memory pages are marked as "poisoned" in the guest page table, in order to enforce a trap to the hypervisor on each access, trigger the remote data transfer and map the VM page to the fetched one. This method is reported to perform relatively well on average when a page fetching delay is distributed over multiple sequential accesses within its boundaries. If the memory access pattern is more random, the average performance decreases due to following reasons:

- More frequent page fetching require more exits to hypervisor, and more I/O operations that are expensive.

- Newly fetched data overwrite previous data, pointed to by some guest address. Therefore, a translation between the guest and hypervisor addresses has to be marked as "poisoned" again, because the same hypervisor page will now be reused to back a different address of the guest. This step requires an address translation table update as well as discarding the invalidated mapping from a translation cache, if it was there.

This approach would benefit from increasing the size of a local memory buffer assigned

to each VM but, with a given amount of RAM available in the hypervisor, the larger the buffer, the less VMs can run in parallel without overwriting each other's data. Moreover, in order to make use of disaggregated resources, this approach still needs locally available memory buffers, into which data can be fetched. A strong advantage of this approach, from an adoption effort point of view, is that it can be deployed with standard compute nodes; the only new component is the memory blade.

The second remote memory provisioning method presented is the remote access at cache-block granularity, which requires a custom hardware component in each compute node, redirecting *cache fill* requests to the memory blade. In return, no hypervisor modifications are necessary in order to access the remote memory: data fetching is performed by the hardware. Nevertheless, each access contributes a fixed delay to reach the memory blade. This is similar to local RAM accesses and therefore performance would greatly improve if the custom hardware component supported caching.

This work is very interesting because it presents a fully disaggregated system prototype with an integrated virtualization support. The system is composed of heterogeneous compute nodes and a common memory blade. Since the latter is a central element of the architecture, it can affect the system scalability in the most profound way, for example a maximum limit of addressable memory determines how many VMs can be feasibly deployed.

# Montaner et al.: "A practical way to extend shared memory support beyond a motherboard at low cost"

A prototype by Montaner et al. [43] is also capable of expanding memory beyond the local motherboard by reserving subranges from other system nodes. A distinctive feature of this method is that it is based on the AMD HyperTransport technology [15], which supports a distributed (within a single motherboard) memory architecture out of the box. Each CPU has part of the physical memory available through a local controller and the rest is attached to other CPUs, all linked by a common interconnect. This work extends the interconnect in order to reach out to other system nodes. In addition to local memory controller(s), each node is also equipped with an additional controller used to redirect non-local memory accesses to remote nodes. Moreover, all of them

are assumed to be connected for the purpose of a memory reservation phase. While the reservation is handled by software, further accesses are performed completely in hardware. The high-level concept is similar to one presented by Velegrakis [58], Zhang et al. [64] and the *dReDBox* prototype [56], that is to perform memory transactions redirection at the on-chip interconnect level, with the help of a custom hardware. But differently to them, this work presents a system that is not disaggregated, in the sense that changing the amount of available memory entails changing the number of CPUs, as they are provided together by each system node.

Except for that, this work presents a system that helps to improve global memory utilization level by sharing non-used memory regions between different nodes. Although it is not discussed in the paper, this system design does not prevent virtualization layer integration. Only the memory reservation phase is performed by software and it could be performed at VM boot time. Then, further accesses to remote memory are completely transparently from the software perspective. Perhaps the only indication of reaching the remote memory may be a lower access performance.

### Hou et al.: "Cost effective data center servers"

Hou et al. proposed a system leveraging the PCIe SR-IOV<sup>2</sup> in order to share memory across nodes[30]. The prototype consists of one *root* node connected to a PCIe switch through a *transparent bridge* (TB) port and four other *leaf* nodes attached through *non-transparent bridges* (NTB). The root node serves as a *root complex*, in terms of the PCIe standard. Each node runs an OS with a custom driver responsible for initializing address translation mappings in NTB ports and exposing a simple interface to applications, providing remote\_alloc and remote\_free calls. A given memory region can be accessed by exactly one node at any given time and the access can be performed in two ways.

The first one consists in direct relaying of each load/store instruction. At first it happens at the local memory controller and further the instruction is dispatched by the PCIe switch. The performance of this method is reported as not good due to the configurations steps performed by software as well as the lack of data caching.

<sup>&</sup>lt;sup>2</sup>Single-Root I/O virtualization, an extension of the PCI Express standard

Alternatively a batch transfer may be configured, using the DMA engine located at the NTB port. It copies the data and emits an interrupt to the sender on completion. In this mode, the remote memory is exposed as a virtual block device, which can be used as a swap partition in order to extend the local RAM. This configuration offers much better performance, in comparison with the first method. This is another hybrid approach, combining both local and remote memory to be used by a host process (for example a VM).

A primary objective of this work was to design a system offering effective resource sharing built with commodity equipment, no custom hardware components were used. In terms of scalability, the *root* node may impose a maximum number of attached system nodes. Although the virtualization aspect is not discussed in this work, similarly to the work presented by Montaner et al., a swap space could be partitioned between all VMs deployed on a given host and the remote memory reservation phase integrated with the virtualization layer. Also, this approach allows to share memory resources between different system nodes but they are not disaggregated, the proportionality between computing and memory resources is fixed as they are provided together by each system node.

# Samih et al.: "A collaborative memory system for high-performance and cost-effective clustered architectures"

Samih et al. presented a work, in which nodes of a cluster collaborate together in order to share memory across each other [51]. There is a software management layer distributed across the system, which leverages a dynamic negotiation protocol. It allows a node to request for memory from other nodes as well as offer its own memory for them. A node can also perform none of this and stay in a neutral state. As mentioned, it is a dynamic protocol and therefore the state of a node may evolve at runtime, according to the current memory pressure.

When reserved, the remote memory is exposed to the host OS as a swap partition and the underlying data transfers between nodes are performed as DMA operation. In this aspect, this the same approach as the batch transfers approach of the work by Hou et al.[30]. The difference is that the interconnect type is Ethernet and the communication

protocol is TCP/IP, however the system could be as well based on InfiniBand or PCIe. With regard to the virtualization and disaggregation criteria, the same comments apply as for the previous work [30]. Moreover, with regard to scalability, it should be noted that the convergence time of the negotiation protocol may increase with the number of system nodes.

# Svärd et al.: "Hecatonchire: Towards Multi-host Virtual Machines by Server Disaggregation"

Similarly to previous works ([30] and [51]), the system proposed by Svärd et al. also supports remote memory sharing between nodes based on DMA transfers. However, differently from them, it is well integrated with the virtualization layer [55]. The memory from other nodes is provided to the host (hypervisor) as a block device but it is then abstracted in the VM by a guest address space. Upon guest's access, if the accessed page is not already present locally, a page fault is generated. Subsequently, a custom host module handles it by fetching the page from the remote location and mapping it properly to the guest. Thus, this approach is very similar to the one presented by Lim et al. [39] and holds the same characteristics.

# Nitu et al.: "Welcome to zombieland: practical and energy-efficient memory disaggregation in a datacenter"

In the paper by Nitu et al. there is presented another approach dedicated for clustered systems, which allows to access memory of another machine by leveraging RDMA technique, here over Infiniband. Each machine can consume memory resources of other machines or donate its own RAM. It can also make an exclusive use of its own RAM and not expose it to others. Such roles are assigned by a global management layer and can be changed dynamically. Pages of remote memory are provided as a swap in two variants, either to hypervisor or directly to a VM. In the second case a page is also swapped to a VM-local disk as a fault tolerance mechanism. In a high-level of description, so far this work seems to be similar to the previous one by by Svärd et al. [55]. Indeed, in some aspects it is. However, a distinctive trait of the paper is the focus

on energy efficiency.

Authors stress that the shift to a disaggregated architecture is a fundamental change at the bottom of the system. Therefore, they proposed a solution that can be successfully adapted to traditional clustered systems as a half-way solution. Instead of enforcing a physical hardware disaggregation they suggest to disaggregated memory and CPUs logically, at the power supply level. It means that the power management logic can handle both types of resources independently and reduce energy wastes in this way. They developed a novel "zombie" state of a power management framework, in which the whole board is powered-off except for its memory banks and part of network. Thanks to that, the memory can be accessed by other system nodes while consuming much less energy, comparing to the situation when all board components are active. This paper provides a nice way of improving energy efficiency in already deployed systems. Moreover, it points out an important matter, that is applicability. Large-scale systems are expensive installation, thus changing radically the architecture may not always be affordable. In such situations evolutionary modifications seem to be preferable, not revolutionary ones.

# Shan et al.: "LegoOS: A Disseminated, Distributed OS for Hard-ware Resource Disaggregation"

Shan et al. predict that future data centers will adopt the concept of hardware resource disaggregation and propose a dedicated operating system for them called *LegoOS* [53]. In a high-level description, it is composed of multiple single-purpose nodes installed, meaning that each node provides only one type of resources. There are processing, memory and storage nodes, interconnected with a network in order to build up a fully functional system. Similarly to other mentioned positions, there is a global management layer orchestrating the whole architecture.

The operating system, proposed by the authors, has a *splitkernel* structure, which means that it is distributed over multiple heterogeneous modules called monitors, with names associated to managed hardware nodes. A monitor acts locally to perform its purpose-specific tasks as well as it exchanges messages with others in order to use remote resources. From a workload perspective resources are visible as a virtual server. Each

virtual server can be composed of multiple different monitors, as well as each monitor can be used by more than one virtual server.

Comparing to all other works presented, a distinctive feature of this design is that one process, for example a VM cannot know on which processing node it will run. Different processes of the same application may be executed by different computing nodes. Such transparency stands out this paper as the one of the highest degree of disaggregation. Other literature positions described in this chapter present how to leverage remote memory or devices but with execution of a workload always bound to a single processing node (except for explicitly distributed application which in this sense can be seen as separate workloads). Therefore, the work by Shan et al. being a reference, it should be stated that all other publications mentioned in this chapter do not present the same level of disaggregation. Nevertheless, usually such information is not explicitly specified and can be only derived from the description, thus the categorization may be slightly ambiguous. All in all, instead of abstracting the hardware by VMs bound to a single processing nodes, the *LegoOS* proposes concept of virtual nodes split over multiple hardware components. Provided the network performance will significantly improve in future, such approach is a very interesting alternative to traditional virtualization.

# Syrivelis et al.: "A Software-defined Architecture and Prototype for Disaggregated Memory Rack Scale Systems"

The *dReDBox* project [56], which this dissertation is associated with, applies concept of memory disaggregation similar to the one found in the works by Velegrakis [58] and Zhang [64].

Reaching the remote memory is similarly done by forwarding on-chip interconnection transactions to remote nodes. This is transparent to the software stack; from its perspective the disaggregated resources are directly accessible as ranges of physical address space. The *dReDBox* paper [56] presents the first prototype version, equipped only with one compute node and one memory node. However, at the time of writing, the system is ready to receive multiple nodes of each type. This makes it much different from the other referred works, in the sense that it presents a fully-disaggregated and scalable system with resources provided independently to each other. Moreover, in

addition to the startup configuration, sections of disaggregated memory can also be added or removed at runtime in a *hot-plug* manner. The connections between the nodes are established dynamically by the system orchestration logic.