# Automatic Source-to-Source Optimizations using Machine Learning

Maksim Berezov

#### ▶ To cite this version:

Maksim Berezov. Automatic Source-to-Source Optimizations using Machine Learning. Robotics [cs.RO]. Université Paris sciences et lettres, 2022. English. NNT: 2022UPSLM098. tel-04307172

# HAL Id: tel-04307172 https://pastel.hal.science/tel-04307172

Submitted on 25 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PSL

Préparée à Mines Paris-PSL

L'automatisation des optimisations source-à -source de programmes en utilisant des techniques de Machine Learning

# Automatic Source-to-Source Optimizations Using Machine Learning

Soutenue par

Maksim Berezov

Le 06 Decembre 2022

École doctorale nº621

ISMME

Spécialité

Informatique temps réel, robotique et automatique

Composition du jury:

Frédéric MAGOULÈS Présidente du jury,

Rapporteur

Université Paris Saclay – Centrale Supélec

Cédric BASTOUL Rapporteur

Université de Strasbourg

François IRIGOIN Examinateur

MINES Paris - PSL Université

Guillaume Iooss Examinateur

Inria Grenoble

Thiago Teixeira Examinateur

Stanford University: Palo Alto, CA, US

Corinne ANCOURT Directrice de thèse

MINES Paris - PSL Université

# **Contents**

| 1   | $\mathbf{Intr}$ | oductio       | on 5                                          |

|-----|-----------------|---------------|-----------------------------------------------|

|     | 1.1             | Motiv         | ation                                         |

|     | 1.2             | Resea         | rch challenges                                |

|     | 1.3             |               | rch directions                                |

|     |                 | 1.3.1         | Data mining                                   |

|     |                 | 1.3.2         | Tiling transformation                         |

|     |                 | 1.3.3         | Feature space design                          |

|     |                 | 1.3.4         | Iterative search acceleration                 |

|     | 1.4             | Thesis        | s structure                                   |

| f 2 | Rela            | ated wo       | ork 13                                        |

|     | 2.1             | Introd        | luction                                       |

|     | 2.2             |               | collection                                    |

|     |                 | 2.2.1         | Existing benchmarks                           |

|     |                 | 2.2.2         | Data mining                                   |

|     |                 | 2.2.3         | Synthetic data generation                     |

|     |                 | 2.2.4         | Conclusion                                    |

|     | 2.3             |               | etion of optimization parameters              |

|     |                 | 2.3.1         | Loop tiling transformation                    |

|     |                 | 2.3.2         | Static approach for optimization              |

|     |                 | 2.3.3         | Dynamic approach for optimization             |

|     |                 | 2.3.4         | Conclusion                                    |

|     | 2.4             | _             | re space design                               |

|     |                 | 2.4.1         | Static code features (without code profiling) |

|     |                 | 2.4.2         | Dynamic features                              |

|     |                 | 2.4.3         | Feature learning approaches                   |

|     |                 | 2.4.4         | Conclusion                                    |

|     | 2.5             |               | ne Learning methods                           |

|     | 2.0             | 2.5.1         | Supervised Learning                           |

|     |                 | 2.5.1 $2.5.2$ | Unsupervised Machine Learning                 |

|     |                 | 2.5.2 $2.5.3$ | Reinforcement learning                        |

|     |                 | 2.5.3 $2.5.4$ | Deep Learning                                 |

|     |                 | 2.0.4         | - Deeb rearming                               |

|   |      | 2.5.5 Active Learning                                             |  |  |  |  |  |  |

|---|------|-------------------------------------------------------------------|--|--|--|--|--|--|

|   |      | 2.5.6 Conclusion                                                  |  |  |  |  |  |  |

|   | 2.6  | Chapter conclusion                                                |  |  |  |  |  |  |

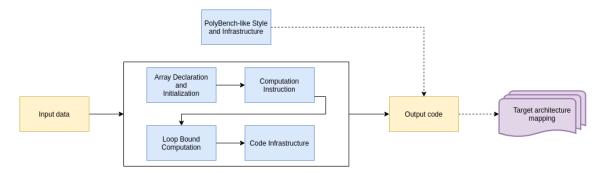

| 3 | Synt | ynthetic data generator 3                                         |  |  |  |  |  |  |

|   | 3.1  | Motivation                                                        |  |  |  |  |  |  |

|   | 3.2  | Guidelines for the generator                                      |  |  |  |  |  |  |

|   | 3.3  | Code Generator Design                                             |  |  |  |  |  |  |

|   |      | 3.3.1 Output Code and Input Data                                  |  |  |  |  |  |  |

|   |      | 3.3.2 Array Declaration and Initialization                        |  |  |  |  |  |  |

|   |      | 3.3.3 The shape of the initialized arrays 4                       |  |  |  |  |  |  |

|   |      | 3.3.4 Array size selection in automatic mode 4                    |  |  |  |  |  |  |

|   | 3.4  | Computation Instructions                                          |  |  |  |  |  |  |

|   | 3.5  | Loop Bound Computation                                            |  |  |  |  |  |  |

|   | 3.6  | Code Infrastructure                                               |  |  |  |  |  |  |

|   | 3.7  | PolyBench-like Style and Infrastructure                           |  |  |  |  |  |  |

|   | 3.8  | Domain-Specific Language                                          |  |  |  |  |  |  |

|   |      | 3.8.1 Grammar                                                     |  |  |  |  |  |  |

|   |      | 3.8.2 High-Level Specification                                    |  |  |  |  |  |  |

|   |      | 3.8.3 DSL Concept                                                 |  |  |  |  |  |  |

|   | 3.9  | Conclusion                                                        |  |  |  |  |  |  |

| 4 | Data | augmentation and optimal experimental design 4                    |  |  |  |  |  |  |

|   | 4.1  | Motivation                                                        |  |  |  |  |  |  |

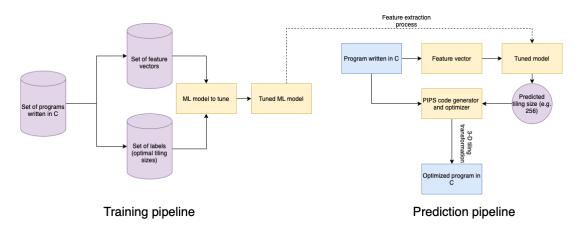

|   | 4.2  | Machine Learning modeling                                         |  |  |  |  |  |  |

|   |      | 4.2.1 Machine Learning pipeline                                   |  |  |  |  |  |  |

|   |      | 4.2.2 Machine Learning models                                     |  |  |  |  |  |  |

|   |      | 4.2.3 Metrics                                                     |  |  |  |  |  |  |

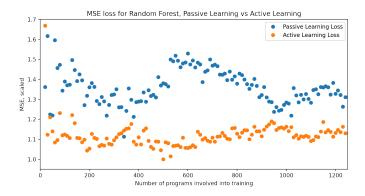

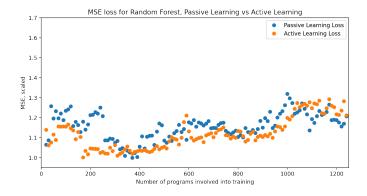

|   | 4.3  | Active Learning                                                   |  |  |  |  |  |  |

|   |      | 4.3.1 Experimental statement                                      |  |  |  |  |  |  |

|   |      | 4.3.2 Generating strategy                                         |  |  |  |  |  |  |

|   |      | 4.3.3 Passive Learning Training Set                               |  |  |  |  |  |  |

|   |      | 4.3.4 Data labelling                                              |  |  |  |  |  |  |

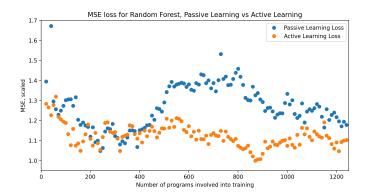

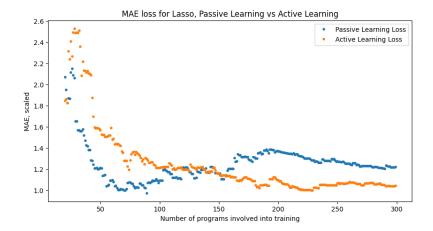

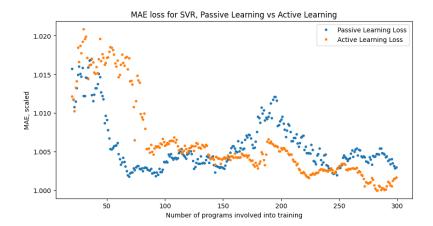

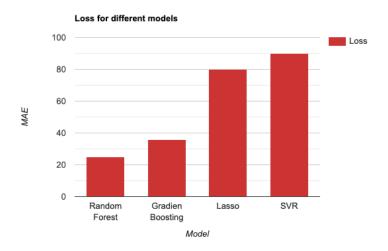

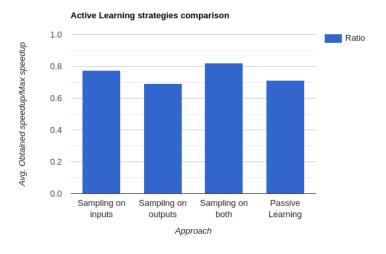

|   |      | 4.3.5 Experimental results                                        |  |  |  |  |  |  |

|   | 4.4  | Conclusion                                                        |  |  |  |  |  |  |

| 5 | Loo  | Tiling transformation. Its parameters and experimental insights 6 |  |  |  |  |  |  |

| 9 | 5.1  | Loop Tiling Parameters                                            |  |  |  |  |  |  |

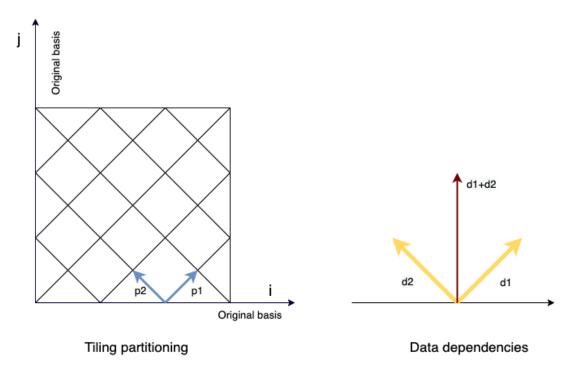

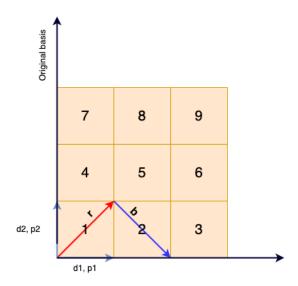

|   | 0.1  | 5.1.1 Tile partitioning                                           |  |  |  |  |  |  |

|   |      | 5.1.2 Tile sizes                                                  |  |  |  |  |  |  |

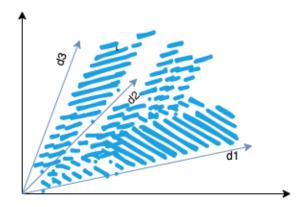

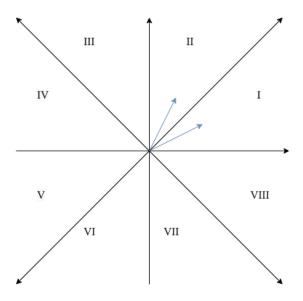

|   |      | 5.1.3 Scanning directions for tiles and its elements 6            |  |  |  |  |  |  |

|   |      | 5.1.4 Kernels of interest                                         |  |  |  |  |  |  |

|   |      |                                                                   |  |  |  |  |  |  |

|   |      | 5.1.5   | Parallel code generation                                         | 69  |

|---|------|---------|------------------------------------------------------------------|-----|

|   |      | 5.1.6   | Conclusion                                                       | 71  |

|   | 5.2  | Exper   | imental insights about tiling transformation                     | 71  |

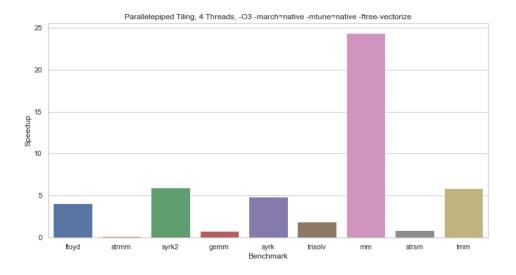

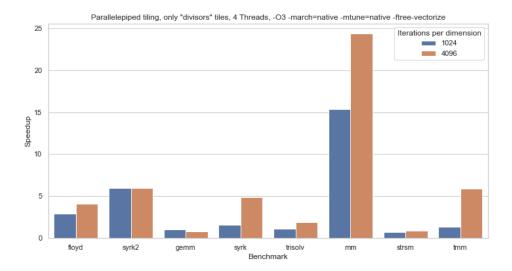

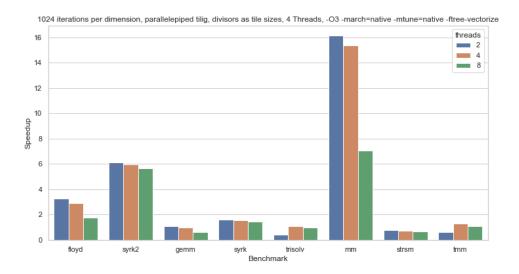

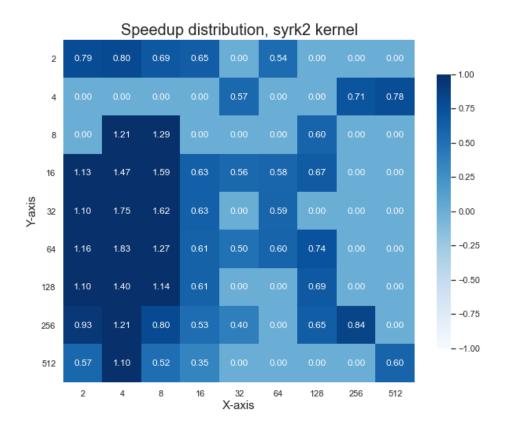

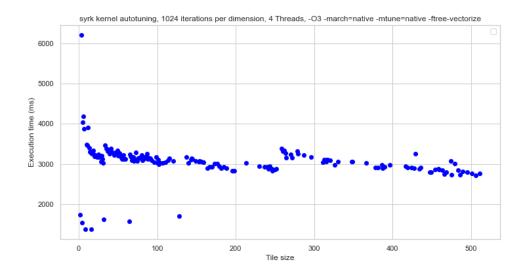

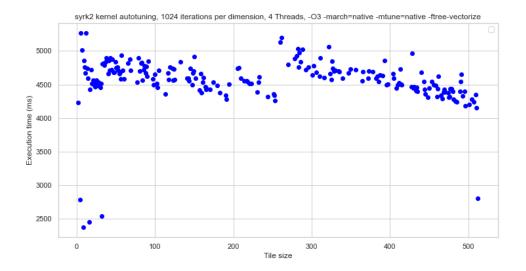

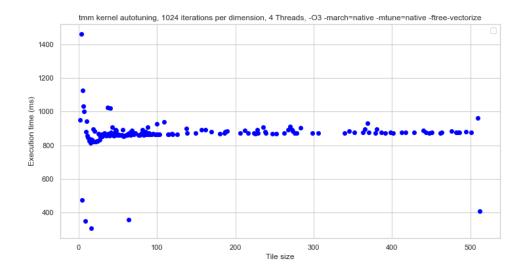

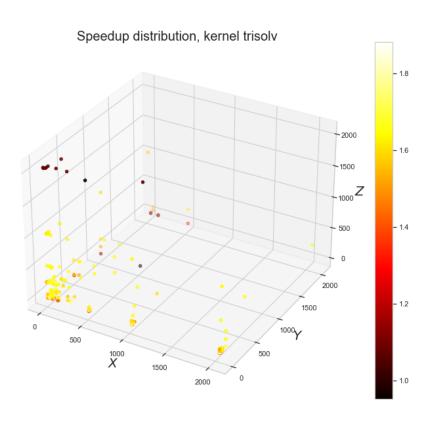

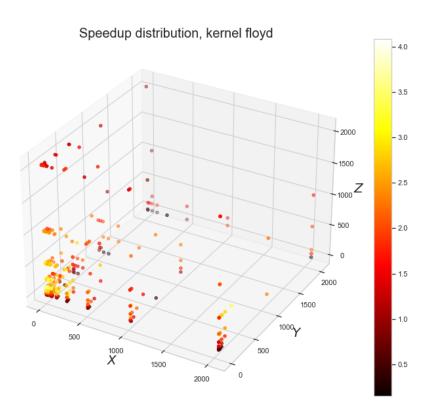

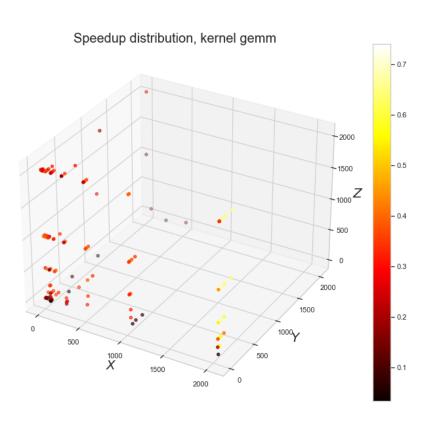

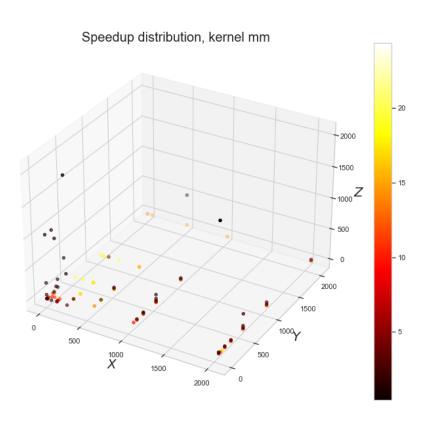

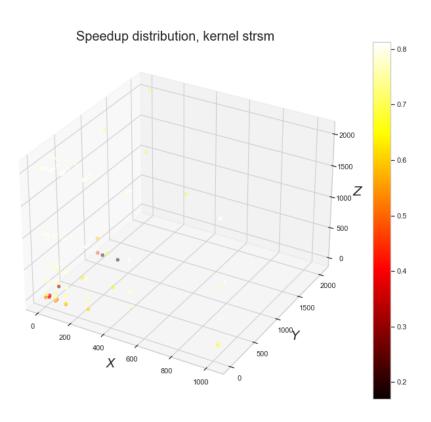

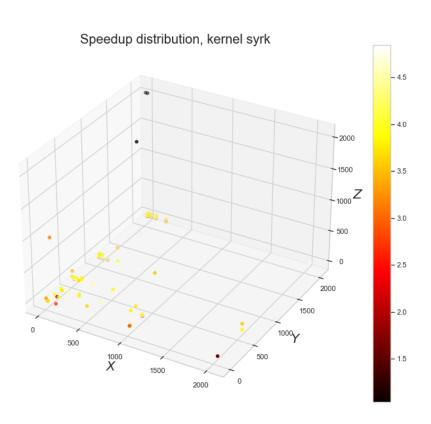

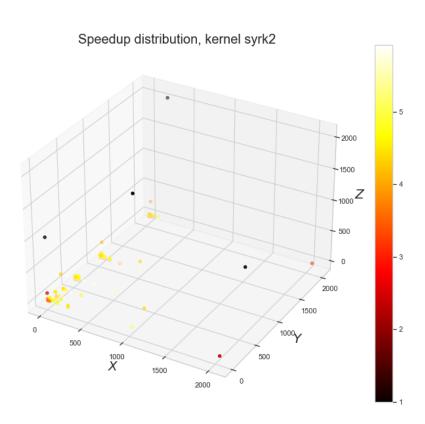

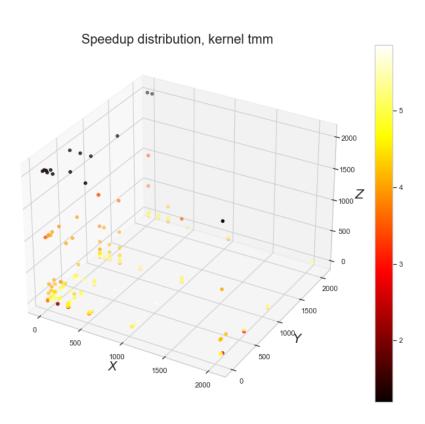

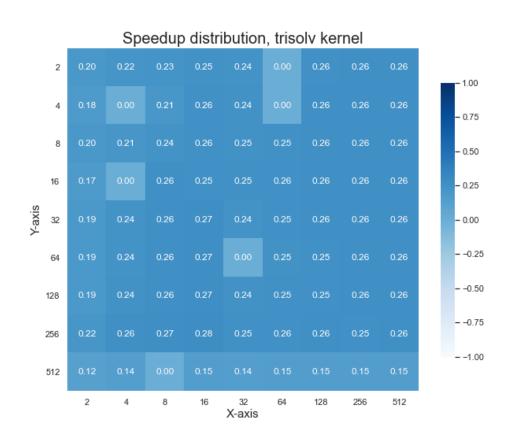

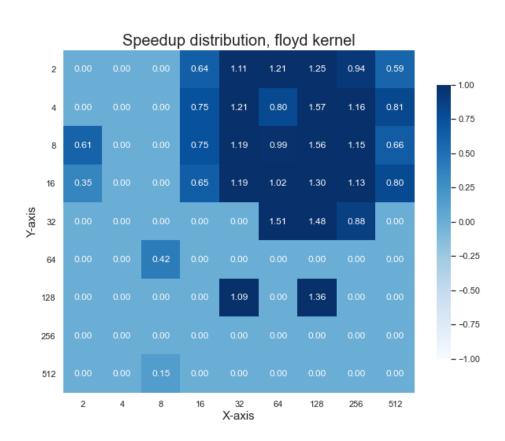

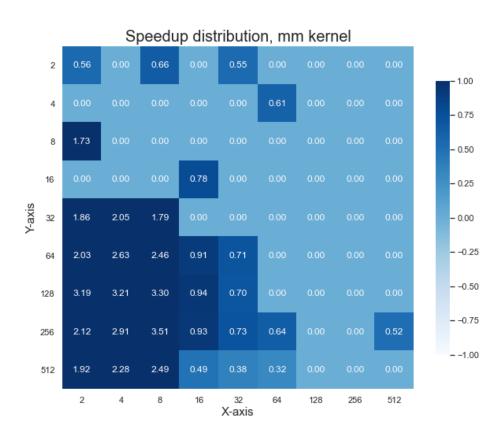

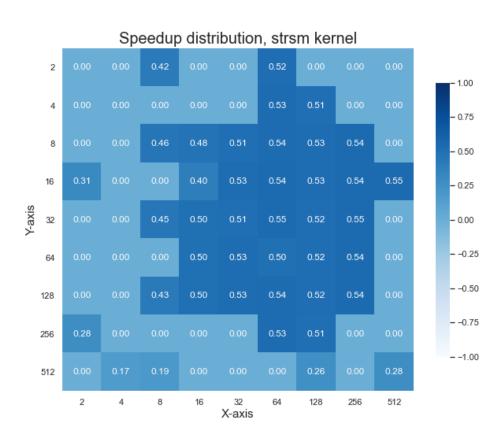

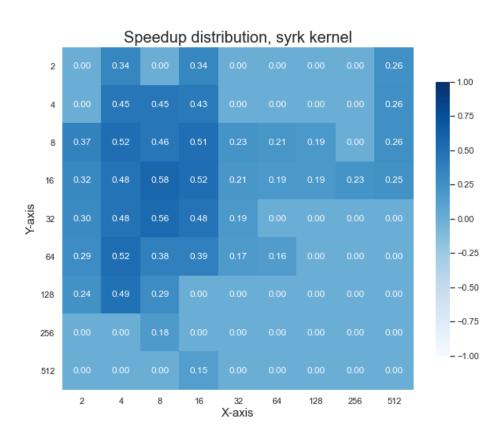

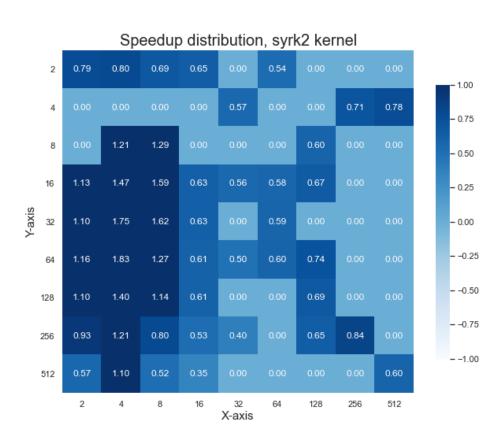

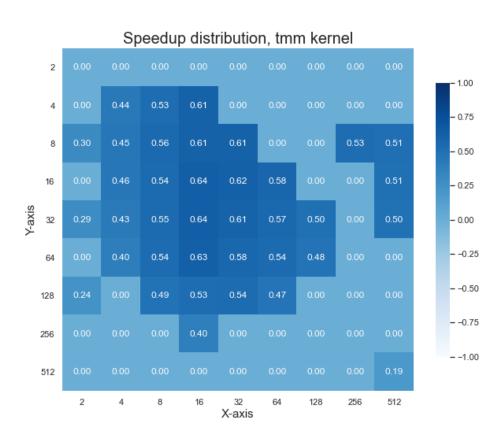

|   |      | 5.2.1   | Loop tiling speedups                                             | 72  |

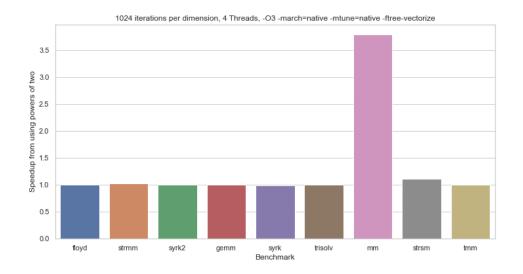

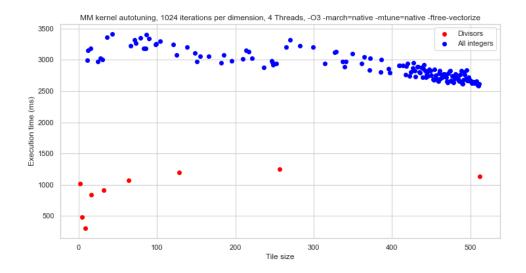

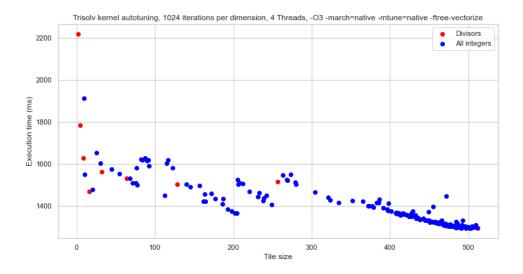

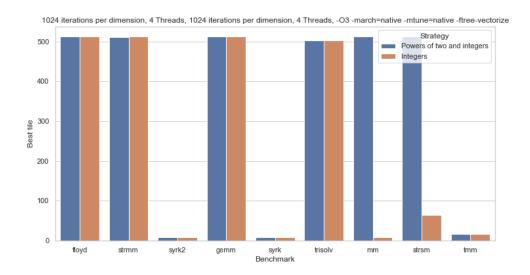

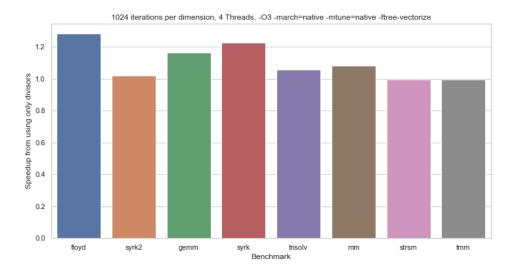

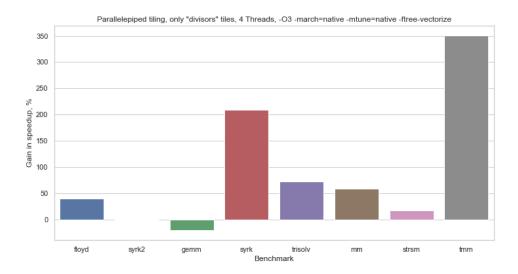

|   |      | 5.2.2   | Loop bound divisors vs. all integers in the domain as tile sizes | 74  |

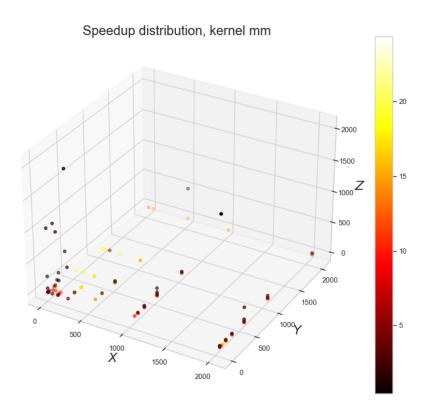

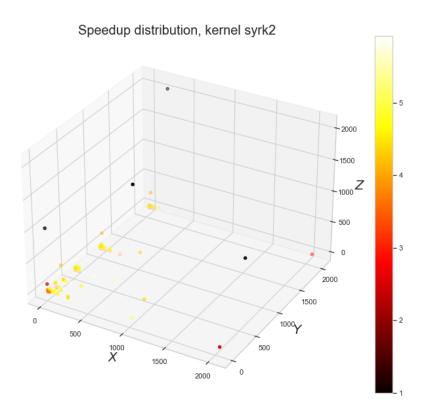

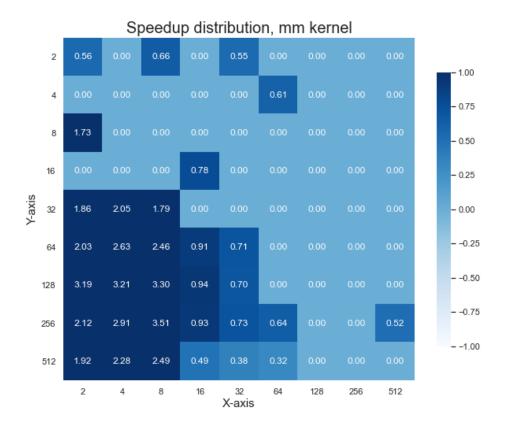

|   |      | 5.2.3   | Impact of the size of the iteration domain                       | 77  |

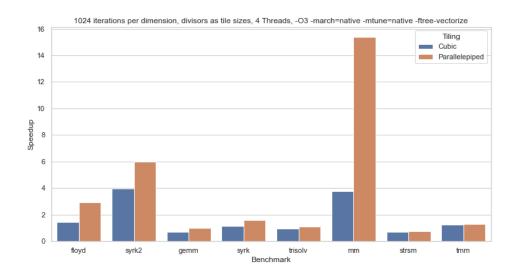

|   |      | 5.2.4   | Cubic or Parallelepiped Tiling?                                  | 78  |

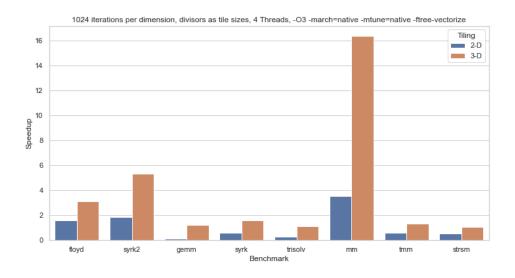

|   |      | 5.2.5   | 2-D or 3-D Tiling?                                               | 79  |

|   |      | 5.2.6   | Number of threads                                                | 79  |

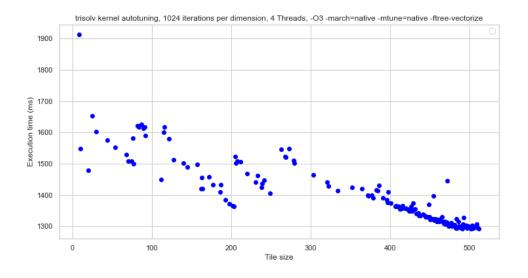

|   |      | 5.2.7   | Tile size selection                                              | 81  |

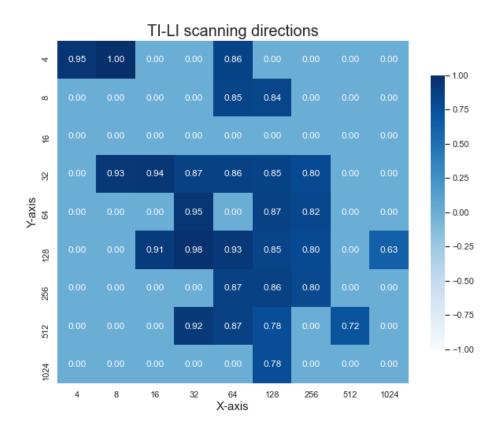

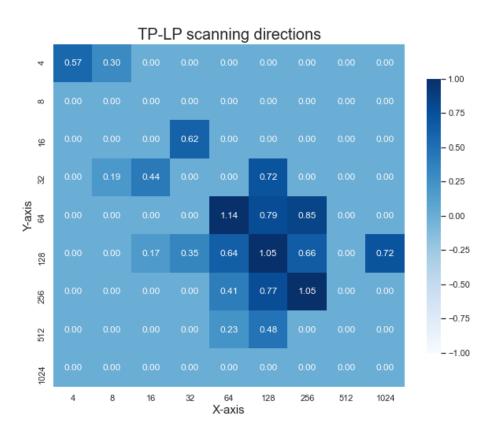

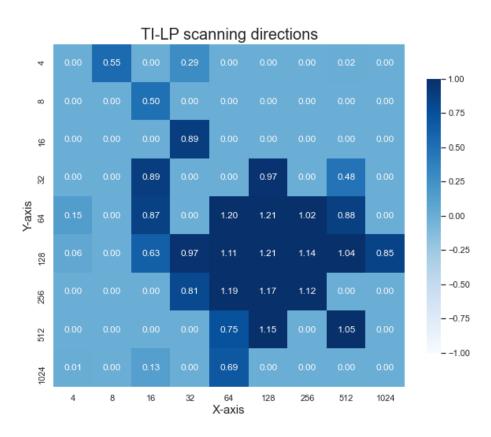

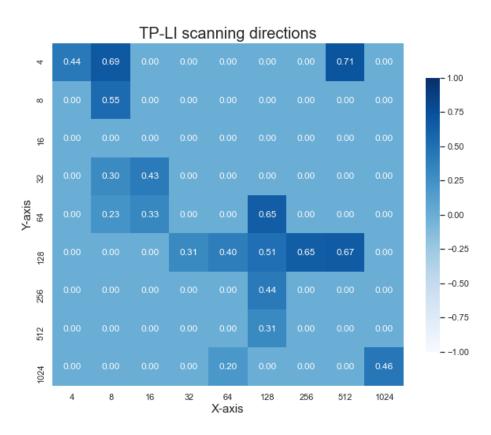

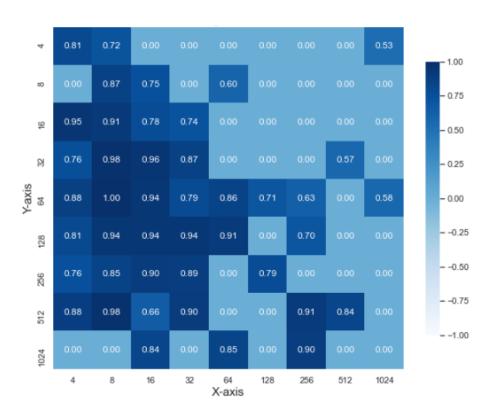

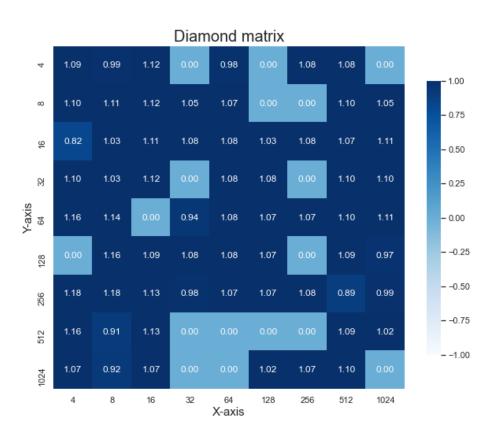

|   |      | 5.2.8   | Tile matrices and scanning directions                            | 82  |

|   | 5.3  | Concl   | usion                                                            | 85  |

| 6 | Tili | ng para | meter prediction                                                 | 93  |

|   | 6.1  | Proble  | ems of interest                                                  | 94  |

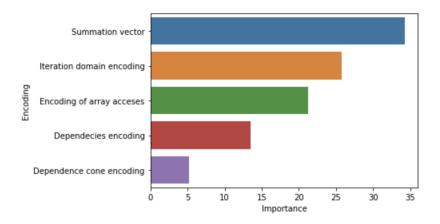

|   | 6.2  | Featur  | re space design                                                  | 95  |

|   |      | 6.2.1   | Encoding of dependencies                                         | 95  |

|   |      | 6.2.2   | Encoding of the iteration domain                                 | 98  |

|   |      | 6.2.3   | Generalization for 3-D case                                      | 98  |

|   |      | 6.2.4   | Encoding of array accesses                                       | 99  |

|   |      | 6.2.5   | Note on the feature space design                                 | 99  |

|   |      | 6.2.6   | Encoding CFG et DDG                                              | 99  |

|   | 6.3  | Tiling  | predictions                                                      | 102 |

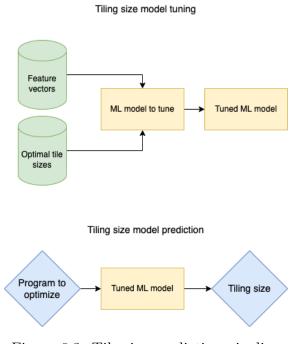

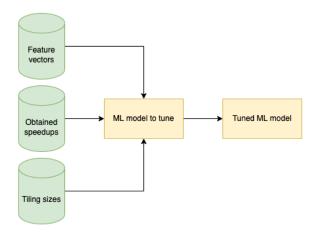

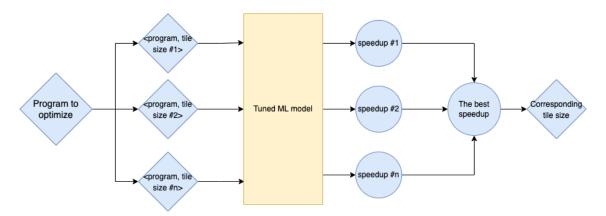

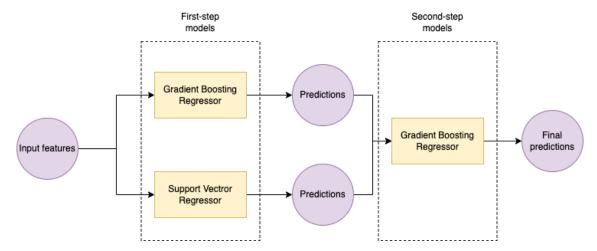

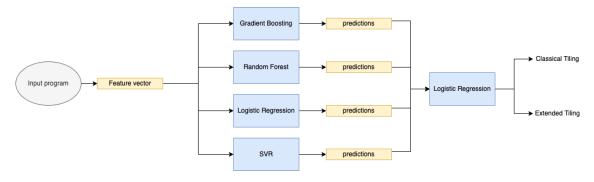

|   |      | 6.3.1   | Machine Learning modeling                                        | 103 |

|   |      | 6.3.2   | Machine Learning models                                          | 103 |

|   |      | 6.3.3   | ML metrics                                                       | 105 |

|   |      | 6.3.4   | Experimental setup                                               | 107 |

|   |      | 6.3.5   | Training/Validation/Test sets                                    |     |

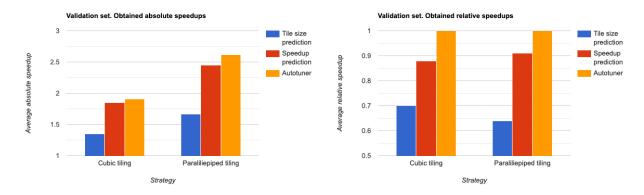

|   |      | 6.3.6   | Validation set results                                           | 108 |

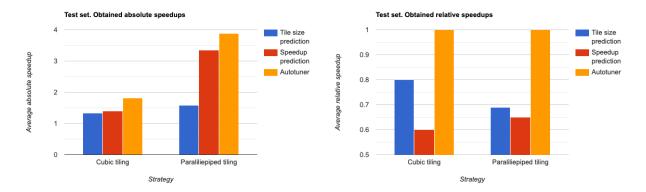

|   |      | 6.3.7   | Test set results                                                 | 109 |

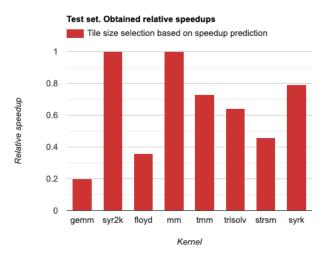

|   |      | 6.3.8   | Test set representativeness                                      | 109 |

|   |      | 6.3.9   | Conclusion on our tiling predictions                             | 111 |

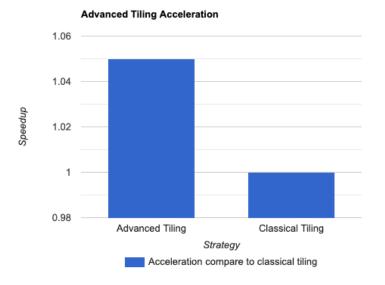

|   | 6.4  | Advar   | nced tiling                                                      | 112 |

|   |      | 6.4.1   | Data collection                                                  | 112 |

|   |      | 6.4.2   | Machine Learning modeling                                        | 114 |

|   |      | 6.4.3   | Conclusion on predictions for Advanced Tiling transformation     | 119 |

|   |      | 6.4.4   | Technological stack                                              | 119 |

|   |      | 6.4.5   | Conclusion                                                       | 120 |

| 7            | Autotuning acceleration using Machine Learning |                                            |       |  |  |  |  |

|--------------|------------------------------------------------|--------------------------------------------|-------|--|--|--|--|

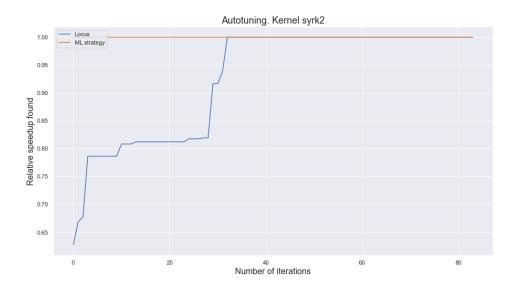

|              | 7.1                                            | Locus Autotuner                            | . 122 |  |  |  |  |

|              | 7.2                                            | Point Ranking Strategy                     | . 122 |  |  |  |  |

|              | 7.3                                            | Acceleration of more complex search spaces | . 125 |  |  |  |  |

|              | 7.4                                            | Conclusion                                 | . 126 |  |  |  |  |

| 8            | Conclusion                                     |                                            |       |  |  |  |  |

|              | 8.1                                            | Introduction                               | . 129 |  |  |  |  |

|              | 8.2                                            | Thesis Contributions                       | . 130 |  |  |  |  |

|              | 8.3                                            | Future work and improvements               | . 132 |  |  |  |  |

| A            | Ker                                            | nel Autotuning                             | 149   |  |  |  |  |

| В            | Para                                           | Paralelipiped tiling. Speedup distribution |       |  |  |  |  |

| $\mathbf{C}$ | Rectangular tiling. Speedup distribution       |                                            |       |  |  |  |  |

| D            | Advanced tiling example. TP-LP scanning        |                                            |       |  |  |  |  |

| ${f E}$      | Glos                                           | esary                                      | 173   |  |  |  |  |

# Acknowledgements

My doctoral thesis was a fascinating journey that took four years. I've met many people I would like to express my deep gratitude to.

I am grateful to my supervisor, Corinne Ancourt. She was always supportive and helpful in all my activities. Her guidance was encouraging and motivating in the scientific field. I am grateful for the warmth, kindness, and care that she had toward me during my Ph.D.

I am beholden to the colleagues I had the luck to work and collaborate with during their period at CRI. Big thanks to Justyna Zawalska and Maryna Savchenko. Their impressive work totally changed the vector of my research. I am thankful to Chermen Tsgoev for productive discussions about tiling and for being an amazing friend.

I am grateful to the members of my jury: Cedric Bastoul for deep and interning discussion on my thesis; Frederic Magoules for being so a great president of my jury; Thiago Teixeira for the tools that I've used during my work and his help and collaboration; François Irigoin for creating so pleasant atmosphere at CRI laboratory, it was a pleasure to work there; Guillaume Iooss for navigating me during the first year and giving me many precious pieces of advice.

I express my gratitude to all the people that I have met at CRI. It was an honor to work together: Fabien Coelho, Laurent Daverio, Emilio Gallego, Olfa Haggui, Olivier Hermant, Pierre Jouvelot, Claire Medrala, Bruno Sguerra, Lucas Sguerra, Laila Bouhouch, Guillaume Genestier, Hassib Abdouli, Adilla Susungi, Claire Medrala, Claude Tadonki. Highly likely, I forgot to mention many people, I'm really sorry.

I say thanks to my dear friends Patryk, Monica, and Gabriella for their support, interesting discussions, and a lot of fun together.

Finally, I send love to my parents: Natalia and Yuri, who did everything for me to get an education. Without their support, I would not finish the Ph.D. They were always near, not physically but morally.

# Chapter 1

# Introduction

#### Résumé

Les codes informatiques sont partout, dans nos appareils mobiles, les rovers Mars Perseverance [27], en passant par les jeux et les équipements critiques (médicaux, systèmes autonomes, aérospatial, etc.). Tous les calculs qu'ils impliquent nécessitent de grandes ressources de mémoire, énergétiques et du temps. Pouvoir appliquer des transformations de code qui permettront de réduire ces temps d'exécution, voire de réduire le besoin en ressources mémoire et énergétique, est essentiel, surtout en cette période de consommation raisonnée des ressources.

Cette thèse se place dans le contexte des transformations de programme sourceà-source. Cela signifie qu'ayant un programme écrit dans un langage de programmation source (dans notre cas le langage C), nous voulons obtenir un programme transformé dans le même langage de programmation qui est plus efficace. La fonction de coût qui guide l'optimisation peut varier : temps d'exécution, temps de compilation, consommation mémoire, combinaison de différentes métriques, etc. De plus, cette thèse tire parti des techniques d'apprentissage automatique.

L'apprentissage automatique est une classe de méthodes d'intelligence artificielle, dont une caractéristique distinctive n'est pas une solution directe au problème, mais l'apprentissage par évaluation de solutions sur de nombreuses tâches similaires. L'objectif principal de cette thèse est de définir une recette appropriée de transformations source-à-source de programme pour améliorer une fonction de coût choisie (temps d'exécution, empreinte mémoire, etc.) pour une architecture homogène en utilisant le Machine Learning.

#### Introduction

Computer codes are everywhere, from our mobile devices to Mars Perseverance rovers [27], games, and critical equipment (medical, autonomous systems, aerospace, etc.). All the calculations they involve require execution time and large memory and power resources. Being able to apply code transformations that will reduce

their execution times, or even reduce the need for memory and energy resources, is essential, especially in this period of rational resource consumption.

Code optimizations could be applied at very different levels. For instance, one may propose an algorithm that would have lower asymptotic computational time complexity, and the other - a compiler - might generate code that runs faster. This thesis takes place in the context of source-to-source program transformations. This means that having a program written in a source programming language (in our case C language), we want to obtain a transformed program in the same programming language which is more efficient. By transformation, we mean an action that changes the source code but does not change the semantics of the program after transformation.

The cost function that guides the optimization can vary: execution time, compile time, memory consumption, a combination of different metrics, etc. The most significant and used in the context of this Ph.D. is the execution time and memory consumption.

In particular, we focused on nested loop transformations, because typically loops are the most consuming part of a program. As experiments show, [1], [29], [32] appropriate transformations can greatly improve performance.

The common source-to-source loop transformations targeted in this thesis are:

- Loop unrolling

- Loop tiling

- Loop interchange

Loop tiling is the core transformation in the context of this thesis. We show that this transformation has many parameters to predict that were not properly investigated in literature. Loop interchange is connected with loop tiling, it is necessary to apply it before tiling in order to either to enable the loop parallelism or to improve the locality of array accesses. Loop unrolling is a classical transformation that provides gains in performance for many kernels of our interest. Although, we considered three transformations, our methodology allows the addition of arbitrary transformations (e.g. loop fusion/fission) for Machine Learning modeling. They would follow the same steps that we applied for the other transformations.

It is very difficult to predict the execution time of a program (or any other metric) even after a single transformation. Indeed, many factors (e.g. temporal and spatial locality, computational loop overhead, instruction-level parallelism) underlie performance, and transformations can make each of them worse or better.

The performance also depends on the architecture. Nowadays, more and more new architectures emerge. They are more productive and efficient, but also more complex, which undoubtedly makes program optimization more difficult. Moreover, find a good optimization for one architecture is not enough, since the performance is not portable.

1.1. MOTIVATION 7

In addition, this thesis takes advantage of machine learning techniques. Machine learning is a class of artificial intelligence methods, a distinctive feature of which is not a direct solution to the problem, but learning in applying solutions to many similar tasks. These methods are widely used in fields such as banking, computer vision, speech recognition, bioinformatics, and many others. The main objective of this thesis is to define an appropriate recipe of source-to-source program transformations to improve a chosen cost function (execution time, memory footprint, etc.) for a homogeneous architecture using Machine Learning.

#### 1.1 Motivation

Choosing the best parameters of loop transformations is not an easy matter. The main difficulty is that the number of possible parameters of the transformations can be very large. For instance, if we would like to apply parallelepiped tiling on a kernel that multiplies  $4096 \times 4096$  matrices, this gives us 68.7 billion potential partitioning matrices. Adding the fact that we would like to investigate simultaneously the loop unrolling and loop interchange transformations, this gives us 395 billion potential options.

Many heuristics of discrete optimization (e.g. genetic algorithms for autotuning, simulated annealing, or just random sampling) can be integrated into a compiler. They work quite well and help to find acceptable solutions. But they do not generalize the knowledge about previous "bad" and "good" executions. Machine Learning could potentially do that. This is the main motivation for the techniques we used in this thesis: the search in a large optimization space could be accelerated with a smart generalization technique, and it can also be considered as a form of extrapolation.

The other motivation to use Machine Learning is that many factors affect performance. Some optimization combinations can improve one factor and worsen others. As mentioned before, temporal and spatial locality, computational loop overhead, and instruction-level parallelism could be considered. Creating heuristics for each factor does not seem like the best strategy. Moreover, what if we do not know about the existence of some factors that affect performance? The sources of data that can provide information on these factors are of different natures. It can be information obtained during static analyzes or dynamic analyses, or it can be some graphs describing the code. All this interaction cannot be represented as an explicit function. As experiments show, machine learning successfully copes with such tasks.

# 1.2 Research challenges

The challenges we faced during our study are common for almost all Machine Learning pipelines. We use Machine Learning as a tool, hence we see our main impact

not on improving the ML techniques but on integrating existing techniques for our problems. The most crucial challenges are listed below.

• Data collection: Since this thesis takes place in the context of Machine Learning, it is crucial to have appropriate training and validation sets to train properly and draw reasonable conclusions. There are many options on how to mine data for training (e.g. open-source code parsing, synthetic code generation, using existing benchmarks). Data collection becomes the main research challenge before creating the ML itself. We argue that this is the most important step since the ML model just captures patterns observed in the training set. We started our investigation with known existing benchmarks and then shifted to the field of synthetic code generation.

#### • Machine Learning modeling:

Machine Learning is a very general concept. It aggregates many different ideas and approaches inside. For instance, we can distinguish sub-fields such as supervised learning, unsupervised learning, reinforcement learning, and many many others. On the other hand, the code optimization domain also aggregates a lot of different sub-fields. It was a challenge to find their proper interaction, where the code optimization domain benefits the most from ML techniques.

To address this challenge, we have proposed solutions to the following problems:

- Synthetic code generation.

- Determination of the optimal parameters for certain transformations such as tiling, unrolling, and interchange.

- Choosing the best way to encode the meaningful code properties in fixed numerical vectors.

As the most appropriate sub-fields of ML, we used supervised ML (regression methods + classification methods) and Active Learning methods for the code generation. The key difference between supervised and unsupervised learning is that we have training labels for learning in supervised process. It serves better when it is crucial to predict the outcomes for the new data (the goal of this thesis).

• Feature space design: When the training set is collected and the problem statement is fixed, it is the step of feature representation of the data that we operate. Chapter 2 highlights the whole evolution process toward the feature space design in code optimization. Shortly speaking, the use of ML started with the use of handcrafted features created by experts. Then the

focus shifted to the automatic collection of specific features that are compilerrelated. The current trend is to use embeddings (vector representation of some concepts) which have been obtained during representation learning with some deep neural networks. It is a challenge to define what kind of features fit the most for our problems. In this thesis, we work with handcrafted features mainly, but also endow the search with a more abstract code representation that does not rely on any potentially biased knowledge. In the scenario of more abstract code representation, we allow the system itself to choose which features to take from raw data for better performance.

### 1.3 Research directions

This thesis targets the applicability of Machine Learning models to the code optimization domain. We investigated four main research questions during this thesis.

- Question 1: Can we collect enough training data for Machine Learning models that would be representative of all the transformations that we are targeting?

- Question 2: Are we able to make our predictions automatically for the different options of the Tiling transformation?

- Question 3: Can we propose alternative ways to encode the code properties that would be invariant for the code transformations?

- Question 4: Can our predictions help to accelerate the iterative search of the best parameters?

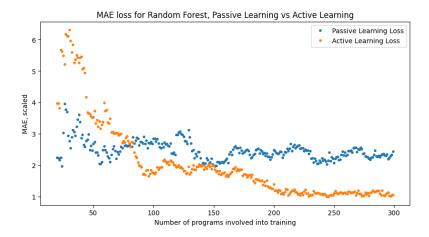

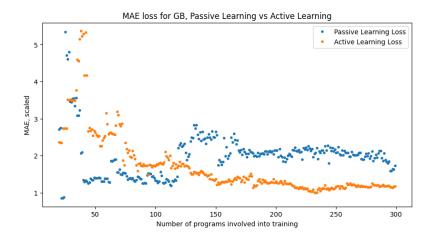

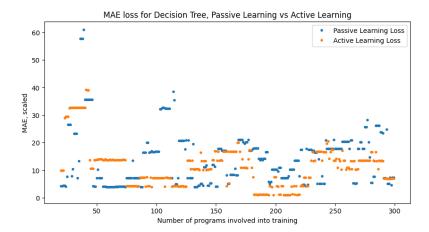

# 1.3.1 Data mining

Chapters 3 and Chapter 4 aim to answer **Question 1**. We believe that creating our synthetic code generator is the most reasonable option to solve the problem of lack of data. Chapter 3 provides the main building block and guidelines for the generator. We define the associated domain-specific language to describe the desired properties of the generated code. Chapter 4 provides the way how to generate just the most representative data that maximizes the performance of the ML model. It relies on the idea of Active Learning that not all data samples are equally important, and the model can choose the best match by itself.

#### 1.3.2 Tiling transformation

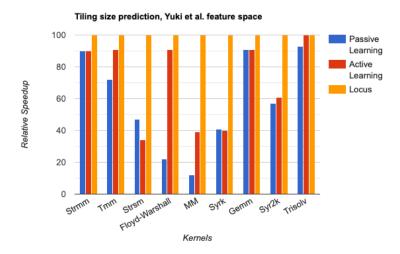

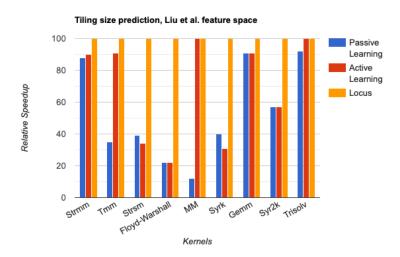

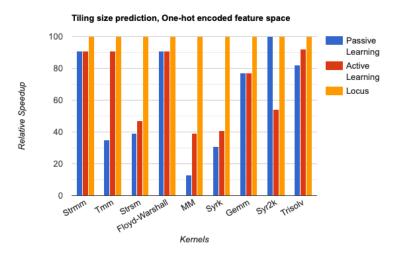

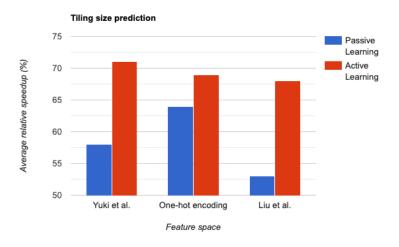

The state-of-the-art Machine Learning models that target tiling transformation aim to make predictions only with cubic/parallelepiped tiling. To answer **Question 2**, we try to show that other tiling options and hyperparameters impact a lot on performance. Chapter 5 shows that different tiling shapes, scanning directions, and hyperparameters are crucial components of well-tuned code. In Chapter 6, we build the predictions of such tiling options as 1) Inter-tile scanning directions 2) Intra-tile scanning directions 3) Tile shape 4) Tile size. Moreover, we give a comparison of existing pipelines to predict the optimal tile size and define the best way to do that.

#### 1.3.3 Feature space design

The majority of well-performing ML models in the field of code optimization rely on handcrafted code characteristics proposed by an expert. Our research therefore also extends the research in this direction. We propose a representation to encode data dependencies in chapter 6. It allows for characterizing data dependencies with a fixed-size data structure, precise enough to be exploited by ML techniques. However, we do not only consider handcrafted features. Chapter 6 tries to answer **Question 3** by proposing some other alternative feature spaces. We consider the encoding of the data-dependence graph and the control-flow graph into vectors of fixed size and use them as features for the ML model. Close vectors correspond to the graphs which "look similar". For instance, code with many data dependencies will be different from code without dependencies. The main advantage of our features is that they could be used for the prediction of any transformation.

#### 1.3.4 Iterative search acceleration

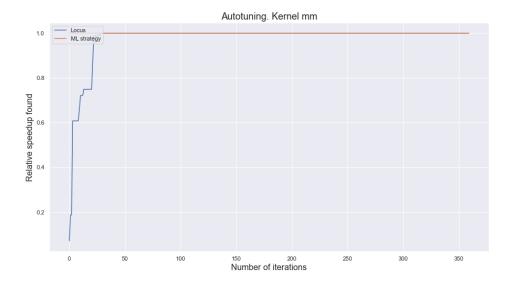

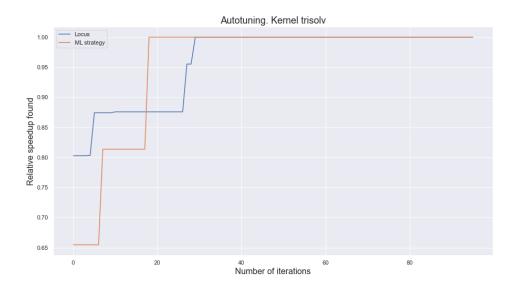

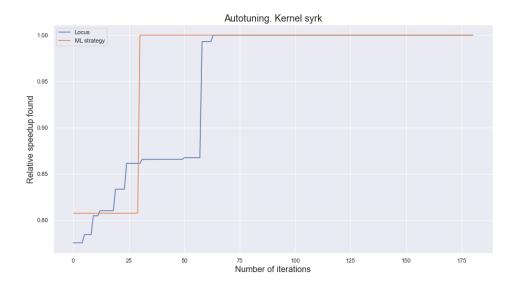

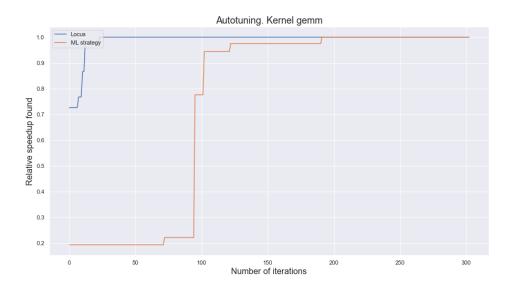

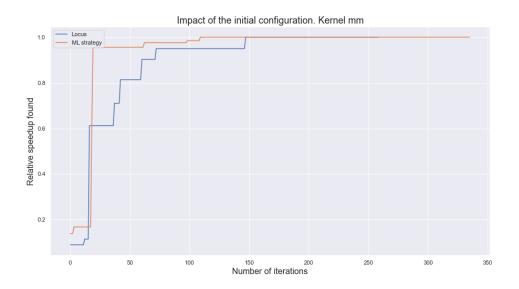

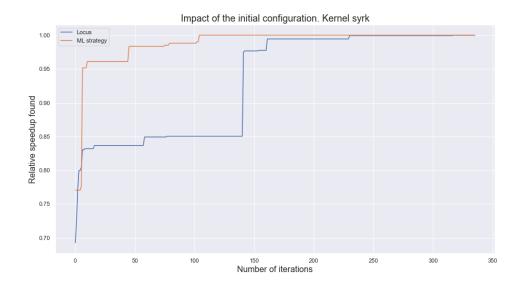

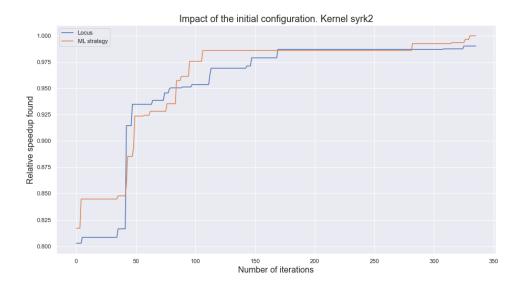

State-of-the-art Auto-tuners are very sensitive to the initial parameters of the search. Poorly chosen parameters could lead to a longer search and not optimal found configuration of the optimal parameters. This is a very common case for Autotuners since the search is task-agnostic. The search engine knows nothing about the problem of interest and could choose the not optimal first solution. Chapter 7 tries to answer to **Question 4**. We used the predictions of our models as the initial seed for the Autotuner. Moreover, we investigate the ability of the model to perform the iterative search by itself.

11

### 1.4 Thesis structure

This thesis is organized as follows. Chapter 2 presents the related work towards 4 different fields: 1) Data collection 2) Prediction of optimization parameters 3) Feature space design 4) Machine Learning methods. Chapter 3 and 4 present our synthetic code generator that would be used for the collection of the training set for each ML model. Chapter 4 presents our strategy on how to select the most representative data generated by our generator given time constraints. Chapter 5 investigates the impact of different tiling parameters on code performance. Chapter 6 attempts to predict all these parameters that are crucial for efficient code generation and evaluates two modeling pipelines to predict the tile size. Chapter 7 evaluates how the one-shot prediction of the tile sizes used as an initial seed for the Autotuner could accelerate the search process. We also evaluate the applicability of our prediction ranking in the autotuning process.

# Chapter 2

# Related work

#### Résumé

Cette thèse adresse deux domaines : l'optimisation de code et l'apprentissage automatique. Ce chapitre met en évidence les travaux connexes dans les deux domaines et également leur interaction. Nous considérons l'apprentissage automatique comme un outil pour résoudre certaines tâches concrètes, et l'optimisation du code comme le domaine d'applicabilité de cet outil. Nous pensons qu'il est raisonnable de fournir des travaux connexes pour chaque phase du pipeline d'apprentissage automatique. Le pipeline typique de Machine Learning pourrait être décomposé de plusieurs phases :

- Collecte de données

- Formulation du problème et modélisation ML

- Modélisation de l'espace des caractéristiques

- Machine Learning formation/prédiction/évaluation des résultats

Nous présentons des travaux connexes pour chaque phase. La section 2.2 résume la manière dont les données sont collectées et extraites dans les pipelines d'optimisation de code. La deuxième phase en section 2.3 met en évidence les problèmes d'optimisation du code lorsque l'apprentissage automatique est utilisé. La troisième section 2.4 cible les caractéristiques concrètes du code requises pour la modélisation des problèmes et celles utilisées dans l'état de l'art traitant de la conception de l'espace des fonctionnalités. La dernière section 2.5 fournit des travaux connexes concernant les techniques et les pipelines d'apprentissage automatique existants.

### 2.1 Introduction

This thesis takes place in two domains: code optimization and machine learning. This chapter highlights related work in both domains and also in their interaction. We consider machine learning to be a tool to solve some concrete tasks, and code optimization to be the domain of applicability of this tool. We believe it is reasonable to provide related work for each phase along the machine learning pipeline. The typical Machine Learning pipeline could be decomposed into several phases:

- Data collection

- Problem formulation and ML modeling

- Feature space modeling

- Machine Learning training/prediction/result evaluation

We provide related work for each phase. Subsection 2.2 summarizes how data is collected and mined in the code optimization pipelines. The second phase in Subsection 2.3 highlights code optimization problems when Machine Learning is used. The third subsection 2.4 targets concrete code characteristics required for problem modeling and how the authors of existing research deal with feature space design. The last subsection 2.5 provides related work in the scope of existing machine learning techniques and pipelines.

# 2.2 Data collection

Quality of data is a crucial component in ML pipelines. The training data must be as indicative as possible and reflect similar characteristics to those on which ML techniques are applied. This section summarizes common approaches to collecting training and validation sets for ML issues in the code optimization domain.

# 2.2.1 Existing benchmarks

There are various known benchmarks for the C programming language that address specific aspects. For instance, BEEBS Benchmarks [51], Embench<sup>™</sup> [42], MiBench [43] address performance analysis on embedded platforms. PolyBench 4.2 [46], Livermore loops (LFK) [49], LCALS v1.0.2, TSVC, [47], LORE [66] focus mainly on compiler optimizations and performance analysis. However, these benchmarks contain a limited number of typical kernels. For instance, TSVC contains 151 perfectlynested loops, PolyBench 4.2 contains 30 computational kernels (kernel may contain several loop nests), Livermore loops (LFK) have 30 loop nests, and LCALS v1.0.2

contains 32 loop nests, LORE aggregates loops from other benchmarks and contains 2499 loops in C.

This amount of data may not be enough when the code optimization domain actively integrates with the machine learning domain [36]. The strength of Machine Learning techniques often comes from the use of a large training set. For instance, MNIST [34] a benchmark for image processing contains 70.000 images, LibriSpeech [39] for speech recognition includes 1000 hours of speech, Enron corpus [40] for natural language processing aggregates 500,000 messages.

Therefore, there are much less benchmark data available in the code optimization domain than in fields where ML shows state-of-the-art performance. There is not enough training data to properly cover the feature space of parameters for complex transformations such as loop tiling, loop unrolling, loop interchange, etc. Note further that different transformations have different feature spaces from a machine-learning perspective. One training set could capture better features for one transformation, another - for another. It becomes challenging to create a universal training set. Thus, synthetic code generation is a crucial component of the proper use of Machine Learning for code optimization.

The possible data collection can be organized in two ways: data mining from open sources or synthetic data generation.

#### 2.2.2 Data mining

The advantage of data mining is that we collect programs directly from the real world. These are exactly the programs that we want to optimize. Also, modern hosting services provide countless amounts of data. For instance, there are at least 10 million GitHub repositories. There is a whole line of research in this direction [53], [56], [55], [54]. However, there are some drawbacks, such as the correctness of the data, their completeness, difficulties arising from parsing, the lack of input data necessary for their execution, the diversity of the types of collected programs, and much more.

# 2.2.3 Synthetic data generation

The alternative direction that tries to get rid of the drawback of the previous approach is synthetic code generation. Some researchers have decided to create or synthesize their own benchmarks.

**Deniz et al.** [57] propose a MINIME-GPU benchmark synthesis framework for GPU using OpenCL. Joshi et al. [58] propose the BenchMaker framework where microarchitecture-independent characteristics are used to describe the required workload. Code synthesizing for some particular problems was introduced in [59], [60]. However, the closest to our work are projects such as GENESIS and CLgen.

Chiu et al. [37] introduce GENESIS, a language for Generating Synthetic Programs. The main idea is that the user can annotate the code template with the parameters that she/he wants to vary. The generation works based on the known pre-defined statistical distribution of the parameters. It helps to obtain reliable data for known domain-specific problems. Statistical distributions depend on the domain knowledge of the expert who tunes them. It makes it complicated to imitate not investigated domains.

Cummings et al. [38] [21] propose a slightly different approach. Their code generator CLgen has a deep learning model as the core of their pipeline. It helps to capture statistical distributions over training codes and imitate new domains without expert knowledge. The disadvantage of this approach is that it requires a huge training set for the deep learning model.

#### 2.2.4 Conclusion

Our work in Chapter 3 presents our original contribution to this related work. We have developed tools to automatically generate synthetic data because the existing solutions do not fully reflect the patterns (uniform and non-uniform data-dependencies, loop index permutations, different patterns of array accesses) we are interested in.

# 2.3 Prediction of optimization parameters

This section focuses on how Machine Learning can help in the selection of optimization parameters. By optimization parameters, we mean a huge scope of things. It can be parameters of program transformations, compilation flags, paths, and many other things. One of the main contributions of this thesis targets the loop tiling transformation. We consider it reasonable to provide related work for this program transformation separately.

# 2.3.1 Loop tiling transformation

Research related to tiling parameter prediction can be classified into three main groups.

- Static analytical models handcrafted by an expert,

- Iterative auto-tuners,

- Static analytical models derived by Machine Learning algorithms.

The earliest approaches [72], [71], [78], [75] [73], [76], [74], [79], [77] [24] related to the tile size selection problem refers to analytical models that capture architectural, program and compiler characteristics. These models attempt to analytically disentangle all the complexity of their interactions and provide the optimal size. However, the interaction of so many concepts can be a very complex problem. Therefore, analytical solutions will lead to not fully satisfactory results. Moreover, new analytical models need to be re-analyzed for every single architecture or compiler and require a huge expert time to maintain the up-to-date versions of the analytical solution. The exact opposite is the approach using auto-tuners [32], [88], [84], [87], [86], [85], [83]. The idea is to explore a grid of transformation parameters iteratively by finding better and better solutions. The majority of existing auto-tuners are limited to cubic tiling, which may not be the best option. This approach provides good results but requires a lot of time to execute potential points, and it does not provide any insights about the final choice.

Our study relates to the third group, we use Machine learning techniques to make predictions and generalizations about the tiling transformation. The most related papers to our study are [1], [45], [81], [44].

Yuki et al. [1] investigate the problem of automatic tiling selection using machine learning approaches. The authors consider cubic tiling on three nested loops with 2D data. The authors describe each loop nest based on the array references inside the loop nest. Each array reference can either take advantage of the spatial locality given by the prefetcher or not, or be constant in the innermost loop. Yuki et al. also mark each reference as a read or write reference.

Liu et al. [45] propose a slightly similar approach. The key difference is that the construction of the feature space can potentially contain loops of any fixed depth and data of any dimensionality.

Malik [44] uses dynamic hardware performance characteristics to determine the optimal tile size. The drawback of this approach is that hardware performance does not provide any insights about the code at the source level. Moreover, Malik considers cache interaction just for the L1 cache.

Rahman et al. [81] propose an alternative to iterative compilation. Their method predicts execution time based on given input tile sizes. This approach helps to learn the distribution of beneficial tile sizes for a given kernel and to determine the limits of convergence for random empirical search. However, this model does not provide any insights into the factors that impact this distribution.

We consider our work to be closest to [1] and [45]. However, all related work focuses on the prediction of just one parameter - the tile size.

The originality of our approach is that we consider several tile shapes and provide a way to predict the optimal scanning directions of tiles and tile elements during their execution. Moreover, we consider data dependencies to be a piece of meaningful information to make this choice and encode them in a feature vector for Machine Learning problems.

#### 2.3.2 Static approach for optimization

This subsection highlights related work for code optimization where parameters are predicted statically. It means that code execution is not required for the optimization decision.

#### Transformation parameters prediction

Monsifrot et al. [52] make a binary decision on whether to unroll a loop or not. They identify 5 classes of features that have an impact on the result: memory access class, arithmetic operations, size of the loop body, control statements in the loop, and number of iterations. For binary classification, the authors use the Random Forest(+ boosting technique). The above features are the input of the algorithm. The disadvantages of this approach include the fact that the authors do not predict how many times this loop should be unrolled.

**Stephenson et al.** [134] try to predict the optimal unrolling factor. They consider this problem as a multiclass classification with 8 possible values of the unrolling factor  $\{1,2,3...8\}$ . To solve it, they use NN and SVM. For this classification, the authors used 38 handcrafted features. Stephenson et al. conclude that this technique predicts optimal/near-optimal unrolling factors in 68% / 79% of cases.

Magin et al. [128] addresses a problem of thread-coarsening transformation. (merging the code that is executed by different threads into one thread). This paper is interesting because the authors used a complex machine-learning model consisting of cascade-connected neural networks to predict the optimal value of thread-coarsening. However, the input for the model was not raw code, but meaningful features. This creates limitations for further generalization of the results to other transformations. Nevertheless, the authors come to the conclusion that this model shows the best results of their popular heuristics. In particular, they achieved an average speed from 1.11x to 1.33x depending on the GPU architecture.

Fursin et al. [132] proposes MILEPOST Framework. This work is the first attempt to create an open-source compiler that uses machine learning.

The authors conclude that this compiler is able to show competitive performance and can improve existing baselines on the benchmarks tested. The main goal of Machine Learning is to predict optimal optimization passes. For ML, the authors use models of two classes:

- Probabilistic Model. The probabilistic distribution for the training set of programs is first studied. Then, for the new program from the test set, we find its closest neighbor from the training set.

- Transductive Model. Supervised Machine Learning problem, decision tree model was used to obtain predictions.

Park et al. [114] propose a new approach to represent programs and capture the most relevant information for Machine Learning models called graph-based characterization (they test on SVM in order to predict optimization sequences). This approach can work in both iterative mode and non-iterative mode. The authors conclude that on the tested benchmarks, this representation shows better performance (73% of the maximum) than the existing concepts (53%).

#### Compiler flags prediction

Cavazos et al. [109] investigate the possibility of using machine learning tools in order to select optimal compilation flags. They represent each program as a 26-dimensional vector. Then, using a logistic regression-based strategy, the authors obtain the required flag vector for this program. Depending on the benchmark, the authors get a decrease in the execution time by 25% and 51% compared with baselines.

#### Phase-ordering prediction

Kulkarni et al. [107] investigate the problem of phase-ordering prediction for Jikes RVM JIT compiler. The idea is to predict the best next single optimization (or predict stop of prediction), then re-evaluate the characteristics of the code and predict the best next optimization. The authors use a neuro-evolution approach to derive ANN, which will be used. Kulkarni et al. conclude that this approach is effective and the first of this kind.

#### Other predictions

Shivan et al. [129] predict which compiler will generate the fastest code for a loop nest. Namely, the optimization of serial code to be auto-parallelized was observed. There are 4 code optimizers: clang (LLVM), GCC (GNU), ICC (Intel), and Polly. The goal is to predict the optimal optimizer for a given code. Performance counters were used as features and for classification, the Random Forest algorithm was applied. The performance gain from the ML predictions is up to 1.42x for the serial code and up to 1.71x for the auto-parallelized code across two multi-core architectures.

# 2.3.3 Dynamic approach for optimization

The alternative approach to code optimization is a dynamic one. We execute a program to optimize and collect essential information about its performance.

In this subsection, we provide an overview of strategies used in dynamic search space exploration. We will highlight the most influential articles on each approach and attempt to understand the big picture of how each strategy has evolved and its prospects.

#### Iterative compilation without Machine Learning

The iterative compilation is a technique for optimizing programs, where each new iteration generates a new version of a program according to a certain criterion. The most popular iterative search techniques are:

- Genetic algorithms

- Random search

- Simulated annealing

- Grid search

- Window search

After several steps, we can get a well-optimized program. In the general case, this approach is very expensive, but for some applications (e.g. embedded applications), this cost is amortized. The opposite direction is a strategy based not on program profiling, but on collecting some of its static indicators and directly predicting the optimization of the target.

#### **Space exploration**

Bodin et al. [98], Kisuki et al. [115] and Fursin et al. [125] conclude that iterative compilation overperforms existing static methods for program optimization, and it can achieve high optimization level of optimization for a small number of steps. The authors considered the optimization set of loop unrolling and tiling and/or array padding. To focus on iterative search, they applied heuristic strategies.

Cooper et al. [151] consider iterative compilation in terms of reducing code size. The authors translate the source code to ILOC (low-level intermediate language). After that, Cooper et al. explore iloc-to-iloc transformations. The search space contains 10 non-parametrized transformations and allows to the generation of sequences of arbitrary length with repetitions.

**Triantafyllis et al.** [116] present the Optimization-Space Exploration (OSE) technique based on the search space pruning strategy and use of static heuristic, which reduces the number of iterations.

Pan et al. [113] propose an orchestration heuristic algorithm in order to find effective compilation settings. The key idea is to iteratively eliminate options with a negative effect on a cost function according to a proposed heuristic algorithm. The authors claim that this approach requires less time to tune than existing methods.

**Ding et al.** [105] present a two-level machine learning approach in order to predict the most optimal optimization strategy for iterative compilation depending on a given input.

Almagor et al. [153], [103] address the problem of order in compilation sequence. This article attempts to answer 3 questions: (1) What percentage of theoretically possible sequences reach a specified level of performance relative to the absolute maximum? (2) Is there a pattern in the distribution of "good" sequences? (3) Understand the distribution of local minimums. Their frequency will influence the choice of the optimal search strategy. The authors consider sequences of length 10 with 5 optimizations: peeling one iteration of a loop, partial redundancy elimination, peephole optimization over logical windows, register coalescing via graph coloring, and dead code elimination. The optimization space has 5<sup>10</sup> points.

Almagor et al. conclude that (1) about 15% of sequences are in 10% of the maximum, and 30% of all sequences are in 20% of the maximum. (2,3) The authors managed to find one large cluster of good solutions (2.6% of the maximum) and many isolated local minimum clusters. The authors also investigate the possibility of iterative search using genetic algorithms in the search space with  $13^9$  points, and conclude that this approach overperforms baselines.

#### Iterative compilation navigated by Machine Learning

Studies based on heuristic search strategies have several shortcomings. The main one is that the knowledge obtained from previous experiments is not generalized for future experiments. This leads to an increase in the number of iterations to achieve the desired level of optimization and to the deterioration of performance. Using machine learning techniques can help overcome these shortcomings.

Agakov et al. [118] propose a methodology using machine learning to identify areas of the transformation space that are most likely to improve performance. The idea is to use an Independent identically distributed model or Markov Model [23] to better target Genetic Algorithms or Random Search. The new program must go through the stage of feature extraction and mapping to the 5-D space (after PCA), where we find its "nearest neighbor" (for which we have learned probability distribution).

The authors consider the following set of transformations: Loop unrolling (1-4), loop flattening, for-loop normalization, non-perfectly nested loop conversion, break load constant instructions, common subexpression elimination, dead code elimination, hoisting of loop invariants, move loop-invariant conditionals, copy propagation. That is, 9 are not parametrized transformations and 1 is parametrized. The output is the sequence of non-fixed length. The authors conclude that this method shows highly efficient results.

Cavazos et al. [130] try to generalize the behavior of programs at a lower level, namely, they profile each program 3 times in order to collect relevant hardware

performance counters. Next, the authors use a model based on logistic regression to find a mapping between performance counters and optimal optimization sequences. For the program for which we want to find the optimal optimization sequence (121 flags were selected in order to construct the search space), the input is only 3 times measured performance counters. The output is a distribution, which **Cavazos et al.** use to draw optimization sequences. The authors claim that by using this technique they are able to achieve a certain level of optimization much faster than the current state-of-the-art techniques.

Park et al. [100] considers three ways of modeling the prediction of optimization sequence: Sequence Predictor, Speedup Predictor, and Tournament Predictor. Tournament Predictor is a novel approach and the authors investigate its applicability. The authors consider 7 optimization phases (45 unique optimizations, there are a lot of optimizations related to loop nest optimization phases). The input of this model is performance counters and two optimization sequences, the output is the prediction of the best sequence. Prediction models are based on SVN or Linear Regression. The authors claim that Tournament Predictor overperforms Sequence and Speedup Predictor and generally shows its viability on a variety of different benchmarks.

**Ashouri et al.** [108] present COBAYN a compiler autotuning framework based on Bayesian Networks. The authors use hybrid features in order to characterize programs in their model. Bayesian Networks were chosen as an intellectual core because of their capability to capture the probability distribution of available features.

The authors consider 7 optimizations: optimizations for floating-point arithmetic, unrolling of all loops, -O2 optimization level, not guessing of branch probabilities disabling loop optimizations on trees, disabling optimizations that inline all simple functions, and disabling induction variable optimizations on trees. The authors claim that they overperform existing state-of-the-art iterative and non-iterative compilation techniques.

Ogilvie et al. [123] emphasize that not all samples of points in the decision space provide useful information. And if we can use just the most "useful" measurements, we will significantly reduce the iteration compilation overhead. The authors use sequential analysis and active learning to solve this problem.

Ashouri et al. [106], Martins et al. [104] and Nombre et al. [99] focus on Design Space Exploration approaches in order to solve the phase ordering problem.

Ashouri et al. [106] propose a methodology based on predicting modeling. It has classical phases of data collection, training, and prediction. The final model is able to predict immediate speedup for a given optimization. This model implements 2 search strategies for the optimal sequence: DFS Search Heuristic and Exhaustive Search Heuristic.

The authors observe 13 different optimizations for LLVM (such as -loops simplify -lcssa -branch-prob). These 13 optimizations form 4 different genes (sequences) of compilation. The goal is to predict the next-gen. Ashouri et al. conclude

that these heuristics overperform LLVM by 4% and 2%.

Martins et al. [104] also address the problem of phase ordering for LLVM optimizations. The proposed methodology consists of encoding, clustering, and arrangement of pass stages. In order to generate clusters, Martins et al. use approaches such as Normalized Compression Distance, Neighbor-Joining, and a new ambiguity-based clustering algorithm.

The authors come to the conclusion that this approach achieves around 20x speedup in search space exploration compared to genetic algorithms and a 1.41x speedup over baseline in terms of the execution time.

**Dubach et al.** [135] propose a methodology based on the predictive model in order to predict optimization sequence. It requires 64 runs (with different optimizations) of a program to be optimized. Then the obtained execution times and the feature representation of the program (4 classes of features: cycles, memory accesses, operations executed, and operations presented in the source code) are used to predict a speedup for each possible optimization. ANN and Linear regression were used to construct a predictor.

The authors consider source-to-source transformations, namely, loop unrolling (with factors 1-4) and 9 non-parameterized optimizations like dead code elimination or move loop-invariant conditionals. This feature space yields 88000 invariants. The authors test their method in larger optimization space: 10<sup>34</sup> points. Dubach et al. conclude that the proposed methodology manages to reduce the cost of search and gives predictions with a high correlation coefficient.

#### **Frameworks**

Many frameworks have been created for iterative compilation issues. For instance, Chen et al. [112] introduce their loop transformation framework CHiLL. The authors conclude that this framework finally fills the gap between the best hand-tuned codes and compiler optimizations for loops. Based on CHiLL and Active Harmony [111] Tiwari et al. [88] propose a framework that is able to perform both fully automatic code transformations and transformations under user assistance (static sequence defined by the user) and then search for the optimal parameters.

**COLE Framework** [87] considers multi-objective space exploration while all previous studies on iterative compilation considered only single-objective exploration.

Ansel et al. [86] propose framework for building domain-specific multi-objective program autotuners. This framework contains such search techniques as AUC Bandit Meta Technique, Nelder-Mead search, Torczon hillclimbers, and many others.

**Baghdadi et al.** proposes a polyhedral compiler framework called TIRAMISU. The distinct features of this work are four-level intermediate representation of a code and special scheduling language allowing targeting different architectures. The authors claim that their approach over performs existing state-of-the-art tools and hand-tuned codes.

As will be indicated in Chapter 4, I collaborated with the author of Locus framework [32] by Teixeira et al., so I pay special attention to its description.

Locus is a system and a language to orchestrate the optimization of applications. In particular, Locus allows us to deal with source-to-source transformations. The distinctive feature is that we can define transformation sequences separately from the source code. This preserves the clarity and readability of the code. The idea behind Locus is that in the source code we specify the sections that we want to optimize. Then an optimization program written in a DSL (domain-specific language) defines transformations over the specified code segment. Parameters of transformations can be specified either explicitly or in the form of intervals. To apply transformations and find their optimal parameters, Locus integrates several modules:

- Transformation modules: Locus integrates multiple transformation models, namely, the source-to-source compilers PIPS and RoseLocus, Pragmas, and BuiltIn,

- Search modules: In order to perform a search in the optimization space, Locus integrates modules such as OpenTuner and HyperOpt.

The authors used various benchmarks to test performance and compare it with Pluto. They examined 856 loop nests with execution longer than 10<sup>4</sup> CPU cycles. The best code generated by Locus archives a 1.15x average speedup, while Pluto (with pre-defined parameters) reaches 1.05x. Moreover, Locus is able to transform 822 loop nests out of 856 (versus 397 for Pluto).

#### 2.3.4 Conclusion

Our results presented in Chapter 6 bring contributions relative to this subsection. Our contributions target static approaches. We have focused on optimizing the loop tiling transformation and defined a set of parameters to predict that has not been covered in previous existing studies.

# 2.4 Feature space design

The proper choice of features is one of the key points in the performance of almost every machine-learning algorithm. Therefore, it is important to understand what data we can collect and use to train our models. Below we give a classification of possible features based on their essence.

Note that this section does not try to compare and determine which type of features is worse or better, and does not try to bring the most recent research with mentioned features. The main goal is to show the immediate advantage of different features for solving various problems relative to our work. The most illustrative studies are given as examples.

#### 2.4.1 Static code features (without code profiling)

This subsection highlights the features that could be extracted during the phase of static code analysis without compilation and execution.

**Handcrafted features.** The simplest idea is to let the experts decide which features in the programs are important for a certain optimization and which are not. Relying on their rich experience and intuition, we can get a fairly representative set of values that describe in detail the distinctive characteristic of this program.

Below we give an example of two studies that use handcrafted features in order to predict the unrolling loop factor.

Monsifrot et al. [52] predict a binary decision whether to unroll a loop or not. The authors distinguish 5 classes of handcrafted features that can influence performance. These classes are "Memory access" features, "Arithmetic operations count", "Size of the loop body" and "Number of iterations". The authors claim that this approach overperforms compiler optimization (-O3).

**Stephenson et al.** [133] solve multi-class classification problems to predict the optimal unrolling loop factor. The authors distinguished 38 handcrafted features for Nearest Neighbours and SVN algorithms. They achieve a 5-9% (depending on the benchmark) improvement over existing methods.

Generated features. Although handcrafted features intuitively well describe the essence of the program, they have a number of shortcomings. The main thing is that the space of possible features is infinite and we have no control if these features are important or not. But experts choose from this infinite set only some limited list based on their intuition. It may potentially be biased and not optimal.

Leather et al. [120] propose an approach based on a combination of genetic algorithms and machine learning. The authors choose productions from the internal representation using genetic algorithms in order to construct feature space. Then the machine learning algorithm is trained on these features (productions) and consistently we get a better set of features. Leather et al. test their approach on loop unrolling. They achieve 76% of the maximum performance available, while state ML (using handcrafted features) achieves only 59%.

Namolaru et al. [121] propose a general method for systematically generating numerical features from a program. The authors view the program as a set of relationships between its entities and infer new ones and extract features from them. The authors evaluate this approach to the optimization flag selection.

They achieve 74% of the potential speedup obtained through iterative compilation on a wide range of benchmarks and four different general-purpose and embedded architectures.

Adams et al. [4] propose a mode to schedule Halide programs. The authors distinguish two types of features: schedule-specific features (either count events of various types, or characterize memory footprints) and algorithm-specific features (histograms of the operations performed). Then these features go through specific architecture of a Neural Network. The Neural Network produces schedules that are on twice faster than existing Halide auto-scheduler.

Representation Learning using Deep Learning. The approaches described above have deeper drawbacks. They, as a rule, are suitable only for predicting one specific heuristic (for example, loop unrolling). But if we want to predict something else, then we need to extract new features by ourselves (for handcrafted features), or apply the whole methodology from scratch and repeat many expensive experiments. In other words, these methodologies cannot generalize to many different optimizations (although they can generalize many different programs across the same optimization). Moreover, they are deeply embedded into the compiler (very dependent on the used AST). The use of neural networks looks very promising and powerful direction to overcome these limitations.

Cummings [126] developed a deep neural network that learns heuristics over the raw code, entirely without using code features. Their model consists of source re-writer, language model, LSTM (long short-term memory) [91] and neural network.

They test their model on 2 tasks: heterogeneous device mapping and thread coarsening. The authors claim that this approach overperforms state-of-the-art ML approaches with handcrafted features. Namely, in 89% of the cases, the quality is not worse than the Machine Learning models and the average speedup is 16% for heterogeneous device mapping and 12% for thread coarsening.

**Baghdadi et al.** [102] present a new cost model to predict program speedup. This cost model is a regression that takes special code embeddings as input. The authors introduce a program characterization in the form of an ordered tree of computation vectors. This concept includes 1) loop nest representation; 2) assignment representation; 3) loop transformation representation. This essential information helps to create representative code embeddings.

**Graph-based Features.** Many important relations in a program are usually represented as graphs. So, for example, it can be a dependency graph or a control flow graph. Undoubtedly, this information is important for more accurate

prediction and can be used by machine learning algorithms. The use of information in the form of a graph is reflected in [114]. To represent a program the authors use graph-based intermediate representation, which is based on CFG (Control-Flow Graph).

The authors conclude that such a feature presentation gives good results in the iterative compilation scenario (achieves 88% of maximum speedup in 5 iterations), and in the non-iterative scenario (achieves 74% of maximum speedup and overperforms state-of-the-art techniques).

#### 2.4.2 Dynamic features

Dynamic features cannot be obtained directly without code profiling. As a rule, we can highlight three levels of abstraction to which dynamic features belong: application level, operation system level, and hardware level.

- Application. Roughly speaking, this level works at the same level of abstraction as static code analysis. Sometimes the data collected during static code analysis is not enough (some features cannot be counted, for example, the number of iterations may depend on user input). But we can count them after code profiling.

- Operation System. As the name implies, at this level we can track features that are defined at the operating system level. This, for example, is all about input/output or CPU loads.

- Hardware. These features work at the lowest level of abstraction. They track the relevant information about the application performance on a given hardware. Only at this level we can, for example, find out the number of different cache misses because the cache sizes are determined by hardware.

An example of using such features is [130] where Cavazos et al. use performance counters in order to predict appropriate compiler optimizations. The authors conclude that this approach overperforms existing static code methods since it is able to capture a lot of relevant information about hardware performance.

# 2.4.3 Feature learning approaches

Deep Learning methods have the unique ability to reconstruct data distribution from raw data. This ability allows them to gradually enter into all spheres of our life, like text processing or banking. Not surprisingly, they are gaining more and more popularity in compiler optimizations.

Cumming et al. [126] developed a deep neural network that learns heuristics over raw code, entirely without using code features. The authors evaluated their

approach to heterogeneous device mapping and GPU thread coarsening. The key components of this model are:

- Source rewriter. The main tasks are parsing the AST, removing conditional compilation, then rebuilding the input source code using a consistent code style and identifier naming scheme.

- **Sequence encoder.** Code to a sequence of integers

- The order to apply transformations can be 1) not predetermined (we must find it by ourselves) 2) predetermined in accordance with best practices

- **Embedding.** Each token (integer value) to a real 64-dim vector (Similar tokens (int, float) to vectors with small distance)

- **LSTM.** Long short-term memory [91] (special kind of recurrent neural network).

- Auxiliary inputs. To maintain system flexibility, it allows you to add features that cannot be obtained from code.

- **Heuristic model** consists of Batch Normalization and Neural Network. The idea is that the neural network, based on the code representation and auxiliary inputs, makes predictions about the optimization parameter values.

The authors conclude that in 89% of the cases, the performance of this approach matches or surpasses the state-of-the-art predictive models that use handcrafted features. The average speedup is 16% for heterogeneous mapping and 12% thread coarsening factor prediction The main contribution of this article is that with the help of this model we can generalize over different transformations (we should not develop everything from scratch) and over different programs.

Chen et al. [127] propose a framework to iteratively optimize tensor operator programs for a given platform. It consists of Exploration Module, Code Generator, Cost Models, and History data

The authors paid great attention to the formalization of the problem, which became the theoretical basis for their invariant code generator. They also proposed two cost models (based on gradient-boosted trees and on TreeGRU), which allow the exploration module to select candidates to query on Hardware. The authors created a transferable representation for both their cost models that is invariant to the source and target domains. It means that transfer learning becomes possible.

Results on deep learning workloads show this framework overperforms Tensor-Flow, ARMComputeLib, TensorFlow XLA, TensorFlow Lite, and MXNet from 1.2× to 3.8× over tested frameworks. Although this paper contains a methodology of iterative search, it is interesting for us from the point of view of the presented cost models and the proposed data representation.

[38] by Cummings et al. addresses an important problem of generating data using deep learning models. The fact is that any machine learning/deep learning algorithm relies on the data on which it was trained. Deficiencies in the training data, such as their unrepresentativeness can have a negative impact on the training of the model. Hence, we get poor predictions that do not correspond to the real state.

The authors propose a methodology using deep learning architectures to generate a set of representative programs. They conclude that the state-of-the-art predictive model trained on data generated by this method speedups by 27%.

#### 2.4.4 Conclusion

This section gives us a detailed overview of how the information about code characteristics is captured now and what we can improve. This information targets explicitly chapter 6. We see the drawbacks of the existing feature spaces and overcome them.

# 2.5 Machine Learning methods

Machine learning is a class of artificial intelligence methods. A distinctive feature is that these algorithms can be trained on a set of similar tasks to solve the given problem. Typically, they deal with tasks where it is not possible to establish the mapping function between input and output in an explicit, human-readable form.

Since Machine Learning acts only as a tool for obtaining results in the context of this Ph.D., we will only give a brief description of the classes of possible algorithms to give an idea of what results can be obtained.

# 2.5.1 Supervised Learning

The basic idea is that we have a labeled data set. Each sample consists of a labeled target variable and a set of independent variables (predictors). Predictors are also called features, they represent some characteristics, some values that describe the essence of a phenomenon being observed. Based on this labeled data set (training set), a machine learning algorithm tries to find an optimal mapping function between features and the target variable. When this function is found, we can use it to predict a target variable for new samples of data.

The values of the target variable can be discrete or continuous. In the first case, we are dealing with a classification problem, and in the second with a regression problem.

• Common classification algorithms are Support Vector Machines (SVM), K-nearest neighbours, Decision trees, and Random Forest, Naive Bayes, and

Log. regression, Gradient Boosting

• Common regression algorithms are Linear Regression, LASSO (least absolute shrinkage and selection operator), Ridge regression, and Elastic Net.

#### 2.5.2 Unsupervised Machine Learning

In unsupervised Learning, we have no target variable to predict. Our data are not designed in such a way as to get directly from them some kind of correct answer. Instead, we can use existing feature representation to solve such problems as

- Clustering grouping objects into some clusters. Objects within one cluster are more similar than objects outside this cluster. Common algorithms: K-Means, distribution-based clustering, hierarchical clustering,

- Associations roughly speaking, to find interesting dependencies/relations in our data. Common algorithms are the Apriori algorithm, Eclat algorithm, and FP-growth algorithm.

- Autoencoders compressing the initial data into some code, and then recovering data from this code only.

### 2.5.3 Reinforcement learning

Reinforcement learning is one of the methods of machine learning, during which the software agent is trained by interacting with a certain environment and getting rewards for its actions.

Common algorithms are Q -learning, Deep Q-learning, Actor-Critic, Policy Gradients, and Proximal Policy Optimization.

# 2.5.4 Deep Learning

Deep Learning is a subset of Machine Learning, which deserves special attention. A distinctive feature of deep learning models is that they are able to construct data representations automatically, not relying on extracted features. Thus, these models can be trained entirely on raw data. By raw data, we understand the data without any pretreatment. For example, it may be a set of image pixels or a source program code. The deep learning model usually refers to some subsets of neural networks (deep neural networks), which may have very different architectures and different parameters.

Common neural network architectures are Feed-forward networks, Convolutional NN, Residual NN, Generative Adversarial Networks, Recurrent NN, and many others.

#### 2.5.5 Active Learning

Active learning is a sub-field of Machine Learning. The crucial idea is that the model itself decides which data to use for more effective training. It finds thought in areas where data annotation is relatively expensive or maybe not feasible. We would like to highlight this section because it finds deep reflection in the context of this thesis.

#### Sampling scenarios

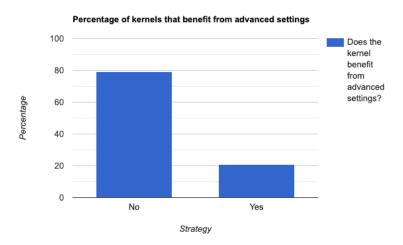

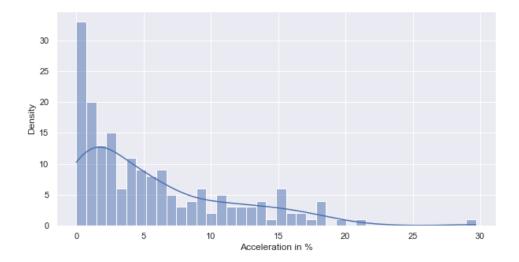

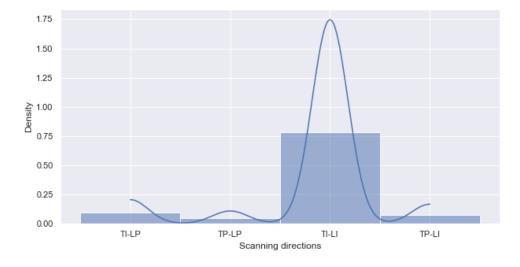

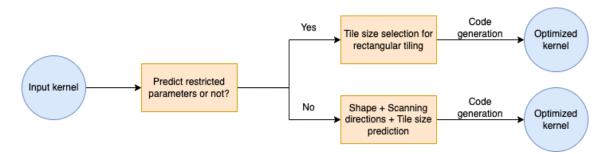

Active learning pipelines [28] work under several scenarios: pool-based scenario [64], stream-based selective sampling [63] and membership query synthesis [62]